# **ARTICLE**

1

https://doi.org/10.1038/s41467-020-16766-9

OPFN

# Oxidation-boosted charge trapping in ultrasensitive van der Waals materials for artificial synaptic features

Feng-Shou Yang<sup>1,2,9</sup>, Mengjiao Lio <sup>1,9 ⋈</sup>, Mu-Pai Lee<sup>1,3</sup>, I-Ying Ho<sup>1,2</sup>, Jiann-Yeu Chen<sup>4</sup>, Haifeng Ling<sup>5</sup>, Yuanzhe Li<sup>5</sup>, Jen-Kuei Chang<sup>1</sup>, Shih-Hsien Yang<sup>1</sup>, Yuan-Ming Chang<sup>1</sup>, Ko-Chun Lee<sup>1</sup>, Yi-Chia Chou <sup>3</sup>, Ching-Hwa Ho <sup>6</sup>, Wenwu Lio <sup>1,7 ⋈</sup>, Chen-Hsin Lien<sup>2 ⋈</sup> & Yen-Fu Lin <sup>1,4,8 ⋈</sup>

Exploitation of the oxidation behaviour in an environmentally sensitive semiconductor is significant to modulate its electronic properties and develop unique applications. Here, we demonstrate a native oxidation-inspired InSe field-effect transistor as an artificial synapse in device level that benefits from the boosted charge trapping under ambient conditions. A thin  $InO_x$  layer is confirmed under the InSe channel, which can serve as an effective charge trapping layer for information storage. The dynamic characteristic measurement is further performed to reveal the corresponding uniform charge trapping and releasing process, which coincides with its surface-effect-governed carrier fluctuations. As a result, the oxide-decorated InSe device exhibits nonvolatile memory characteristics with flexible programming/erasing operations. Furthermore, an InSe-based artificial synapse is implemented to emulate the essential synaptic functions. The pattern recognition capability of the designed artificial neural network is believed to provide an excellent paradigm for ultra-sensitive van der Waals materials to develop electric-modulated neuromorphic computation architectures.

<sup>&</sup>lt;sup>1</sup> Department of Physics, National Chung Hsing University, Taichung 40227, Taiwan. <sup>2</sup> Department of Electrical Engineering and Institute of Electronic Engineering, National Tsing Hua University, Hsinchu 300, Taiwan. <sup>3</sup> Department of Electrophysics, National Chiao Tung University, Hsinchu 300, Taiwan. <sup>4</sup> Research center for Sustainable energy and Nanotechnology, National Chung Hsing University, Taichung 40227, Taiwan. <sup>5</sup> Institutes of Advanced Materials (IAM), Nanjing University of Posts&Telecommunications, Nanjing 210023, China. <sup>6</sup> Graduate Institute of Applied Science and Technology, National Taiwan University of Science and Technology, Taipei 106, Taiwan. <sup>7</sup> Engineering Research Center for Nanophotonics and Advanced Instrument (MOE), Technical Center for Multifunctional Magneto-Optical Spectroscopy (Shanghai), School of Physics and Electronic Science, East China Normal University, Shanghai 200241, China. <sup>8</sup> Institutes of Nanoscience, National Chung Hsing University, Taichung 40227, Taiwan. <sup>9</sup>These authors contributed equally: Feng-Shou Yang, Mengjiao Li. <sup>™</sup>email: mengjiaoli@email.nchu.edu.tw; wwli@ee.ecnu.edu.cn; chlien@ee.nthu.edu.tw; yenfulin@nchu.edu.tw

he sustainable increase in the number of integrated basic components on a chip is becoming a significant challenge for the advancement of the internet of things (IoT) technology, especially in the post-Moore era. In terms of the scaling down limitation of silicon-based materials, two-dimensional van der Waals semiconductors have aroused widespread interest for the next generation of nanoelectronics owing to the atomic-scale thickness, large area development, and good charge transport behaviour<sup>1-6</sup>. These attractive characteristics endow van der Waals semiconductor-based electronics with an immunity to short-channel effects, gate controllability, or tunable polarity of conductivity, which facilitate promising potential uses in transistors, sensors, and memory<sup>7-12</sup>. Nevertheless, despite the abovementioned advantages, compared with traditional silicon materials, most members of the environmentally sensitive semiconductor family encounter very noticeable oxidation upon exposure to ambient atmosphere. The representative examples are black phosphorus (BP), indium selenide (InSe), hafnium sulfide (HfS<sub>2</sub>), molybdenum ditelluride (MoTe<sub>2</sub>), and the layered organics like Ruddlesden-Popper perovskites (RPP), which exhibit discernible surface morphological variations even over a few minutes<sup>7,12–18</sup>. In addition, the carrier transport in devices based on these semiconductors would be randomly disturbed and lead to severe degradation effects in electrical or optical performance, which are acknowledged as the most critical obstacles for their successful practical application. To address such a poor stability of layered semiconductors, several protection strategies have been introduced into the structural design to achieve effective passivation, such as encapsulation methods, surface doping, interfacial engineering, and ionic liquids<sup>19–21</sup>. However, achieving both the long-term stability and excellent device performance is still challenging; therefore, a determination as to how to reasonably use the unavoidable oxides in environmentally sensitive semiconductors seems to be another alternative to control the inner charge transport characteristics and is meaningful for developing both charge trapping memory and artificial synaptic systems. A synapse, which is the basic building block of a neural network in human brains, functions as the junction between the pre-neuron and post-neuron to realize information transmission, learning, and storage<sup>22–25</sup>. Various orders, such as emotions and actions, can be solved in parallel by a neural network under ultra-low power consumption and fault tolerance, which is considered as the natural paradigm for the innovation of brain-inspired neuromorphic computing technology in the modern information industry because of the physical limitation of separated memory and central processor in the classic von-Neumann computation architecture<sup>26–29</sup>. Previously, tens of silicon-based transistors were employed to mimic the synaptic functions, which was hindered by the circuit complexity and huge energy consumption for large-scale integrations<sup>30,31</sup>. Ionicgating-modulated transistors were recently proposed to emulate the information transmission in biological synapses based on the reversible electrochemical proton doping process, although the device repeatability remains out of control<sup>32,33</sup>. In this regard, the use of a sensitive van der Waals materials-based transistor, which will benefit from its native oxidation effect and tunable charge trapping behaviour, is believed to possess innate advantages to achieve design-simplified synaptic devices<sup>34</sup>. Therefore, there is more motivation to conduct an in-depth investigation of the charge trapping mechanism in environmentally sensitive van der Waals materials for mimicking operation-controllable artificial synapses.

In this work, we experimentally demonstrate an oxidation-boosted artificial synaptic device, for the first time, based on a typical sensitive van der Waals semiconductor, InSe. As a representative of the III-VI group materials, InSe possesses small

effective electron mass and excellent intrinsic charge transport characteristics. Its acknowledged air-instability and large surface to volume ratio, resulting in severe performance degradation and hysteretic behaviour, attract much researchers' attention on how to protect it from contact with air for steady electrical properties. including our team. To put this in perspective, the environmental sensitivity provides itself favourable conditions for introducing into oxidation layer; thus quantitatively analyzing and comprehending carrier traps in this thin oxide layer is of great significance in particular for van der Waals materials to further limit its negative impact, even utilize it for enhancing the performance and applications of electronic devices 14,35-40. Intriguingly, the microscopic structure observation of InSe FET has confirmed that the native oxide formed at the bottom of the InSe channel under ambient conditions is capable of serving as a unique charge trapping layer to modulate the charge transport behaviour. The dynamic charge trapping and releasing process is visually delineated by low-frequency noise analysis according to the surface effect dominated carrier fluctuations, which is responsible for its nonvolatile data storage characteristics with reliable programming/erasing operations. Furthermore, the basic synaptic functions, which include short-term plasticity (STP) of paired-pulse faciliation (PPF) and the long-term plasticity (LTP) of spiketiming-dependent plasticity (STDP), are successfully mimicked by this oxidation-inspired InSe artificial synaptic device, as well as the system-level pattern recognition based on the artificial neural network (ANN). Consequently, the ingenious use of the oxidation layer in the InSe FET offers a new opportunity for air-unstable layered semiconductors to bulid a simpler configuration in the field of data storage and next-generation neuromorphic computation.

## Results

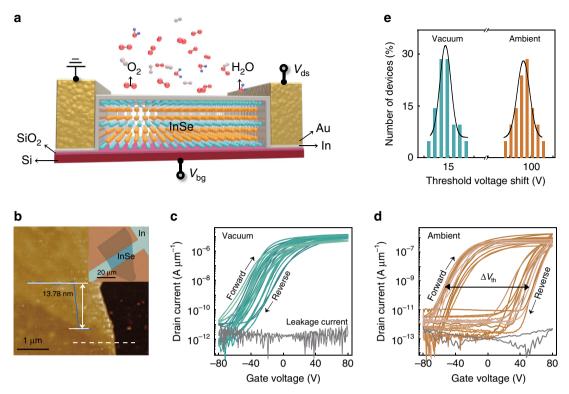

Characteristics of InSe FET under different conditions. Here, the demonstration of the InSe artificial synaptic features in device level was inspired by the specific electrical behaviour of the surface-doped InSe FET under an ambient atmosphere, and its schematic structure is shown in Fig. 1a. Note that the electrical characteristics for InSe FETs with/ without surface doping effect were provided in Supplementary Fig. 1 for comparison<sup>38</sup>. The exfoliated InSe flake was intentionally selected as 10-20 layers under optical microscopy (OM) for improved device properties<sup>41</sup>. Its typical thickness was examined to be around 13.8 nm by the topographic scan profile of atomic force microscopy (AFM) (Fig. 1b). In consideration of the ultrahigh sensitivity to moisture and oxygen for InSe, first, we characterized the basic electrical performance of the fabricated InSe FET to explore the underlying charge transfer differences between ambient (InSe A-FET) and vacuum (InSe V-FET) conditions. All of the statistical transfer curves and the gate leakage in Fig. 1c and d for 15 representative InSe FETs under two conditions indicated the typical electronconduction behaviour in the InSe channel. Along the sweep directions of gate voltage varying between -80 and +80 V, the recorded transfer curves for InSe V-FET exhibited weak electrical hysteresis loops. Such a slight positive shift of the threshold voltages below 20 V in backward gate sweeping can be attributed to the charge transfer effect instead of capacitive gating effect due to the few interface states between the channel and dielectric layer or fabrication-induced defects<sup>42–46</sup>. While immersing the same 15 devices in ambient conditions, the observed transport windows were consistently enlarged, which indicated the boosted electrical hysteresis phenomena. Figure 1e shows the corresponding statistical threshold voltage shift under different conditions based on 25 InSe FETs. Its average value in the InSe A-FET approached 100 V, hinting at the existence of unique charge trapping and

**Fig. 1 Structure schematic and basic electrical properties of InSe FET. a** Schematic diagram of the InSe FET exposed to ambient conditions, in the presence of several gas molecules (such as  $H_2O$  or  $O_2$ ). The Si substrate serves as the gate electrode and the covered In film acts as the surface dopant. **b** AFM image and the corresponding height profile of the InSe channel. The inset shows the typical OM image of the InSe FET, where the length and width of the InSe channel are 13 and 31 μm, respectively. **c**, **d** Transfer characteristics and the gate leakage curves at drain voltage  $V_{ds} = 0.1 \, \text{V}$  for the 15 representative InSe FETs under the vacuum and ambient conditions, respectively. Note that the arrows mark the directions of the gate voltage sweep and  $\Delta V_{th}$  means the threshold voltage shift. **e** Histogram of the threshold voltage shift for InSe V- and A-FETs and the Gaussian fit (solid lines) based on the statistical database.

releasing events in the InSe channel owing to the possible native oxidation of InSe under ambient conditions, which will not occur under vacuum conditions. To preliminary verify the hypothesis of the native oxidation event, the specific experiments were intentionally designed to detect the variation of the transfer curves for InSe FET depending on the exposing time and immersing conditions<sup>47</sup>. On the one hand, Supplementary Fig. 2 shows the evolution of transport windows along with the exposing time under ambient conditions. Initially, a narrow window in the transfer curve for InSe FET can be observed under vacuum conditions. With the increase of the exposing time under ambient conditions, the obtained hysteresis loop gradually enlarged and then saturated with a window of about 90 V. Moreover, such a wide hysteresis loop under ambient conditions over 2 h can still be well-retained without obvious variation, even when storing it back to vacuum conditions again, which minimizes the impact of the physical absorption of gas molecules<sup>48</sup>. On the other hand, when storing a fresh sample in the nitrogen (N<sub>2</sub>) or argon (A<sub>r</sub>) atmosphere for around 30 minutes, the measured transport windows are almost fully consistent with that of InSe V-FET (Supplementary Fig. 3). While in the case of dry air, it presents an enlarged hysteresis loop, even being stored back to the vacuum conditions, suggesting the weak influence of the hydrolysis effect on the InSe channel. In consequence, it is believed that the enhanced hysteretic behaviours in InSe A-FET are dominated by the native oxide layer under ambient conditions. It is worth noting that the excellent electrical properties of InSe A-FET, which include high on current, on-off current ratio, and good Ohmic contact (see the corresponding output curves in Supplementary Fig. 4), were maintained compared with those in InSe V-

FET, without obvious electrical degradation. In terms of the above, such an intriguing electrical hysteresis behaviour in the InSe A-FET not only motivates more efforts in exploring the underlying charge trapping mechanisms but also suggests its potential use in memory systems<sup>49,50</sup>.

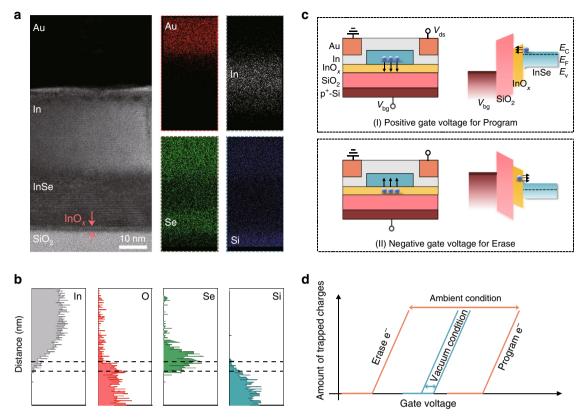

For visually examining the occurrence of the native oxidation event, we performed the microscopic structure observation of the InSe A-FET using high-resolution-transmission electron microscopy (HRTEM). The cross-sectional image and the corresponding energy-dispersive X-ray spectroscopy (EDS) element mapping distinctly present the components of the device are shown in Fig. 2a, which include the Au contact electrode, In doping layer, InSe channel, and SiO<sub>2</sub> dielectric layer. The highly crystalline lattice of the InSe channel was approximately 16 layers, which agreed well with the height profile obtained from AFM analysis. Intriguingly, a thin amorphous layer inserted between the InSe and SiO2 was evidently observed. We then conducted EDS line scan analysis along the cross-section region of InSe A-FET to identify the composition and thickness of this amorphous layer. The profiles of In, Se, and Si elements in Fig. 2b clearly outlined the interfacial region between InSe and SiO2. In particular, the intensities of elemental O could be ignored at the region of InSe layer while they underwent a sharp increase at the top side of SiO<sub>2</sub>, which signified the existence of an amorphous 2-nm-thick  $InO_x$  layer at the interfacial region. It is worth mentioning that the thin InO<sub>x</sub> layer was not detected for the devices of InSe V-FET<sup>38</sup>. Therefore, the native InO<sub>r</sub> formed under ambient environment was believed to be a vital layer to boost the charge trapping and releasing behaviour between the InSe channel and  $InO_x$  layer to result in the enlarged transport window in transfer

**Fig. 2 Observation of the native oxidation layer by microscopic structure analysis. a** Cross-sectional HRTEM image and the corresponding EDS element mappings of a typical InSe A-FET. The arrows highlight the existence of the  $InO_x$  layer. **b** EDS line scan profiles of In, O, Se, and Si elements along the cross-section region of the device. Note that the dash lines label the region of  $InO_x$ . **c** Energy band structure of the charge trapping and releasing process of Program and Erase operations for InSe A-FET under different gate voltages ( $V_{bg}$ ). The Program and Erase operations are defined as the charge trapping process by  $InO_x$  and charge releasing process from  $InO_x$ , respectively. **d** Schematic diagram of boosted threshold voltage variation for InSe A-FET compared with that for InSe V-FET.

characteristics. Then, we determined the energy band and the corresponding operation states under the modulation of gate voltage to better understand the charge trapping and releasing process in InSe A-FET. The (I) part of Fig. 2c defines the Program operation by applying a positive gate voltage. In this process, the electrons in InSe channel were trapped by the InO<sub>x</sub> layer, which leads to a positive shift of  $V_{th}$  and the low current level in InSe A-FET. While under a negative gate voltage (the (II) part of Fig. 2c), the trapped electrons were released from InO<sub>x</sub> because of the tilted energy of the trapping layer on another side, thus bringing about the threshold voltage shift towards a negative gate voltage and triggering the Erase operation in InSe A-FET with a high current level. Therefore, one can conclude that the charge trapping behaviour in InSe FET have been enhanced under ambient condition, compared with that of vacuum condition, and benefits from the native oxidation (Fig. 2f), which provides an ideal configuration to extend the promising opportunity in the field of charge trapping-based memory as well as artificial synaptic devices.

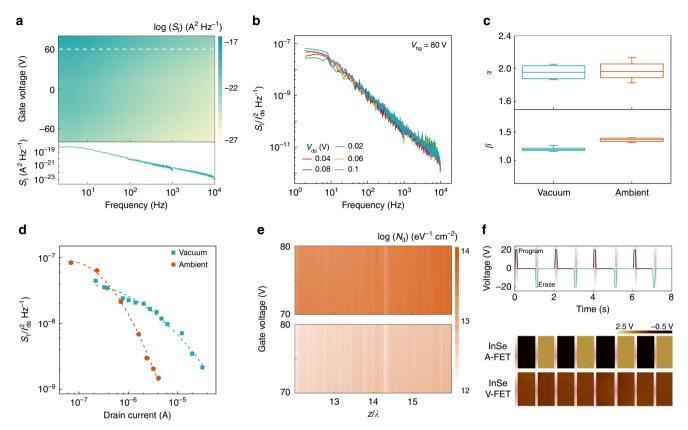

To understand the mechanism of the electric fluctuations versus device signal for building sensitive materials-based electronics toward practical applications, the systematical dynamic characteristic measurement for InSe FETs under different conditions was conducted  $^{51,52}$ . The noise power spectra map of current fluctuations ( $S_{\rm I}$ ) for InSe A- and V-FET as the frequency ranged from 2 to 10 kHz are shown in Fig. 3a and Supplementary Fig. 5. With increasing the applied gate voltage, the measured  $S_{\rm I}$  was incrementally augmented, and exhibited the high consistency of the ideal 1/f signal (a representative curve

below the map). Figure 3b profile the drain current normalized S<sub>I</sub> demonstrated its independent characteristic of drain voltage, which revealed that the electric noise signal was largely driven by the InSe conducting channel instead of the contact barrier effect between the channel and source/drain electrodes. This phenomenon observed from InSe A-FET was attributed to the In dopant induced good Ohmic contact behaviour because of the lower work function of In metal than that of Au electrode<sup>43</sup>. In detail, the degree of the 1/f dependence in the measured noise power spectra was determined based on the empirical formula  $S_I \propto I_{ds}^{\alpha}/f^{\beta}$ , where  $\alpha$  and  $\beta$  represent the scaling exponents for the current and frequency, respectively. As provided in Fig. 3c, the derived values of  $\beta$  were approximately 1.36  $\pm$  0.01 and 1.21  $\pm$ 0.01 for InSe A- and V-FET, respectively. This suggested a uniform distribution of charge trapping or scattering states both in space and energy under the two conditions. Furthermore, both the fitted values of the exponent  $\alpha$  for the ambient and vacuum conditions were near to 2, which revealed that the 1/f electric noise behaviour in InSe FETs could be assigned as the resistor fluctuation<sup>53</sup>.

Considering that the extracted scaling exponents showed high similarity between InSe A- and V-FET, we further discuss the nature of the 1/f characteristics under the two conditions by combining the carrier number fluctuation and correlated mobility fluctuation in terms of the dynamic carrier trapping behaviour and the surface scattering<sup>54–56</sup>. The detailed descriptions are provided in the Supplementary Note 1. To discriminate the governing mechanisms of the noise source in the InSe devices under different environments, Fig. 3d plots the log-log scaled

**Fig. 3 Governing mechanisms of the carrier transport in InSe FET.** a Recorded  $S_l$  as a function of frequency and gate voltages for InSe A-FET. Note that a  $S_l$  curve at  $V_{\rm bg} = 60$  V based on the white dash line (upper) is profiled a representative of 1/f noise (under). **b** Drain current normalized  $S_l$  depending on  $I_{\rm ds}$  for InSe A-FET at several  $V_{\rm ds}$ . **c** Box-plots of the fitted  $\alpha$  (upper) and  $\beta$  (lower) values for InSe V- and A-FET. Note that the center line, the upper, and the lower bars correspond to the average, the maximum, and the minimum values, respectively. **d** Normalized  $S_l$  by  $I_{\rm ds}^2$  (discrete dots) versus  $I_{\rm ds}$  on a log-log scale for InSe FET under different conditions. The dashed lines are the well-fitted results based on the correlated mobility fluctuation. **e** The extracted values of effective interface trap density for InSe V- and A-FET as a function of  $z/\lambda$  and gate bias. **f** The dynamic variations of the surface potential (under read states) of InSe channel by in situ KPFM depending on the scanning time, for InSe A- and V-FET, respectively. The program and erase operations were defined by applying a +20 V and a -20 V gate voltage pulse (5 s) for 4 cycles.

$S_I/I_{

m ds}^2$  as a function of drain current. The evolution of  $S_I/I_{

m ds}^2$  for InSe A-FET tended to depend on the change of  $I_{ds}^{-2}$ , which indicated that the surface effect dominated the carrier transport. This phenomenon validated the existence of charge trapping/ releasing events at the InSe channel and dielectric interface, which was high-consistency with the HRTEM analysis. However, the observed  $S_I/I_{\rm ds}^2$  for InSe V-FET is inclined to mainly obey the variation of  $I_{\rm ds}^{-1}$ . The corresponding  $\alpha_{\rm SC}$ , a mobility fluctuation related Coulomb scattering coefficient, was fitted to be  $2.69 \times 10^4$ V s C<sup>-1</sup> for InSe V-FET, which was ~100 times higher than that for InSe A-FET  $(2.95 \times 10^2 \,\mathrm{V}\,\mathrm{s}\,\mathrm{C}^{-1})$ , indicating the bulk condition mainly governed carrier transport and fluctuations in InSe V-FET. Furthermore, the effective trap densities,  $N_{it}$ , which is composed of all the trap states from both the bottom interface and the top surface of the InSe channel in the present device configurations, were evaluated to visualize the process of charge transport in InSe FETs under the two conditions<sup>57</sup>. For a better comparison, the extracted values of  $N_{\rm it}$  as a function of  $z/\lambda$  and gate voltages under two conditions are shown in Fig. 3e, where z and  $\lambda$  represent the trap depth and tunnelling distance parameter, respectively<sup>51</sup>. The  $N_{\rm it}$  values were independent of  $z/\lambda$  under each applied gate voltage, which further portrayed the observed in the 1/f behaviour. The overall value of  $N_{it}$  for InSe A-FET was near 1014 eV-1 cm-2, at least an order of magnitude at least higher than that in the vacuum condition. Such a big difference of  $N_{it}$ values between the two conditions is believed to make the boosted

charge trapping/detrapping events between the InO<sub>x</sub> interfacial layer and InSe channel in InSe A-FET, shedding more light on the evident surface effect under ambient conditions because of the formation of 2-nm-thick native InO<sub>x</sub> layer. On the other hand, we further conducted the in situ KPFM measurements to visually verify the charge trapping effect of  $InO_x$  via examining the dynamic variation of the surface potential of InSe channel in InSe A- and V-FET (Fig. 3f). In the case of InSe A-FET, the recorded potential of InSe channel exhibits distinct difference under the read states ( $V_{bg} = 0 \text{ V}$ ) after the program and erase pulses, as well as a good reproducibility in 4 successive cycles, which shed light on the occurrence of the charge trapping/detrapping events in InSe A-FET during the program/erase process. In contrast, the potential difference in InSe V-FET could almost be ignored under several read states, hinting at its weak charge transfer behaviour. Thus we could determine the dominant role of the InO<sub>x</sub> layer in trapping/detrapping electrons in the proposed devices, which paves the way for the demonstration of memory and artificial synaptic features.

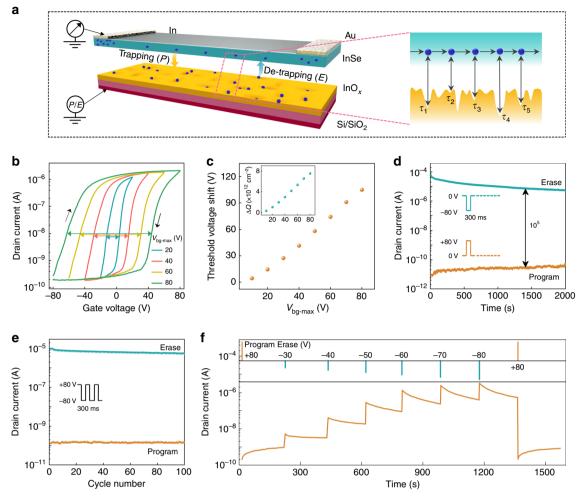

The nonvolatile memory properties based on InSe A-FET. The clear charge transport mechanisms in InSe A-FET revealed by the structure and dynamic characteristics analysis inspired more exploration of charge trapping-based memory systems. Figure 4a shows the 3D schematic of InSe A-FET, in which the thin  $InO_x$  layer formed under the bottom of the InSe channel provided the

**Fig. 4 Performance characterizations of the InSe A-FET based memory device. a** 3D schematic of InSe A-FET with the existence of InO<sub>x</sub> to achieve the charge trapping/ de-trapping under applied operation voltage. The inset on the right side delineates the uniform distribution of trapping states for the dynamic fluctuation process between the InSe channel and InO<sub>x</sub> layer. Note that  $\tau$  means the time constant for different traps. **b** Transfer characteristics of InSe A-FET with the  $V_{\rm bg-max}$  (the maximum value of the swept range of gate voltage). The drain voltage is set as 0.1 V and the colourful arrows mark the increasing threshold voltage shift. Note that the arrows indicate the directions of hysteresis loops. **c** Variation of the threshold voltage shift depending on  $V_{\rm bg-max}$ . Inset shows the extracted amounts of trapped charges under various  $V_{\rm bg-max}$ . **d** Retention performance of InSe A-FET based memory. The currents were separately read under Program and Erase states with  $V_{\rm ds} = 0.1 \, \text{V}$  and  $V_{\rm bg} = 0 \, \text{V}$ . **e** Endurance characteristics of the memory device. Program and Erase operations were carried out under cyclic voltage pulses. The Read state was operated under  $V_{\rm ds} = 0.1 \, \text{V}$ . **f** Evolution of read current of the memory device under various operation states, which indicates its multiple data storage characteristics.

innate situation for demonstrating memory operations. Accordingly, a concrete process of the dynamic charge trapping and releasing events between the InSe channel and  $InO_x$  layer is delineated in the right illustration. To gain insight into the charge retention ability of the InO<sub>x</sub> layer, to the best of our knowledge, this is the first basic performance evaluation of InSe A-FET based memory. The transfer characteristics of InSe A-FET under consecutive voltage sweeps are illustrated in Fig. 4b. As marked by the arrows, a bigger  $V_{\rm bg,\ max}$  resulted in a wider hysteresis window. The extracted values of threshold voltage shift in Fig. 4c were positively proportional to the applied  $V_{

m bg,\ max}$ , which indicated that the charge trapping behaviours in InSe A-FET could be effectively modulated by varying the sweep range of gate voltage. Furthermore, the amounts of trapped charges ( $\Delta Q$ ) as a function of  $V_{\rm bg}$  were estimated to be around  $10^{-12}\,{\rm cm}^{-2}$  (inset of Fig. 4c) based on the capacitance model of  $\Delta Q = \Delta V_{\text{th}} C_{\text{ox}}/q$ , where  $C_{\text{ox}}$ and q are the capacitance of a 300-nm  $SiO_2$  dielectric layer and the elementary charge, respectively<sup>58</sup>. This result was slightly smaller than the difference value of  $N_{\rm it}$  between InSe A- and V-FET (Fig. 3f), where the underestimated trapping sites here possibly stemmed from both the non-saturated states under current Program/Erase operations and additional origins, such as the fabrication-induced defects or interface states between the channel and dielectric layer.

Generally, excellent charge retention ability and durability are of great significance to the practical use of energy-efficient memory systems. Figure 4d shows the reliable retention performance of InSe A-FET based memory with a high Program/Erase ratio above 105, for which the read currents exhibited negligible degradation even after  $2 \times 10^3$  s. Note that the Program and Erase states here were defined by the application of a positive and a negative gate voltage pulse, respectively, to excite the initial charge trapping states in InSe A-FET. Besides, the two distinctive Program and Erase states could be well-maintained over 104 s without obvious degradation (Supplementary Fig. 6), satisfying the industry standard of 10-years data retention. Such the excellent nonvolatile charge storage capability of InSe A-FET was mainly attributed to the boosted charge trapping and releasing process owing to the native oxidation of the InSe channel. The cycle endurance of the memory device was assessed by switching the Program and Erase

states between a low current level and high current level. As shown in Fig. 4e, the steady read currents as a function of cycle number illuminate its good reproducibility. Besides, Fig. 4f outlines the dynamic multilevel storage behaviour of InSe A-FET based memory by modulating the amplitudes of the erasing voltage pulses. Initially, the device was excited under a programming pulse of  $+80~\rm V$  to store numerous electrons in the InO $_x$  trapping layer. Then the incremental read currents were clearly distinguished over almost five orders of magnitude under the application of 6 erasing voltage pulses, which resulted from the controllable amount of erased charges.

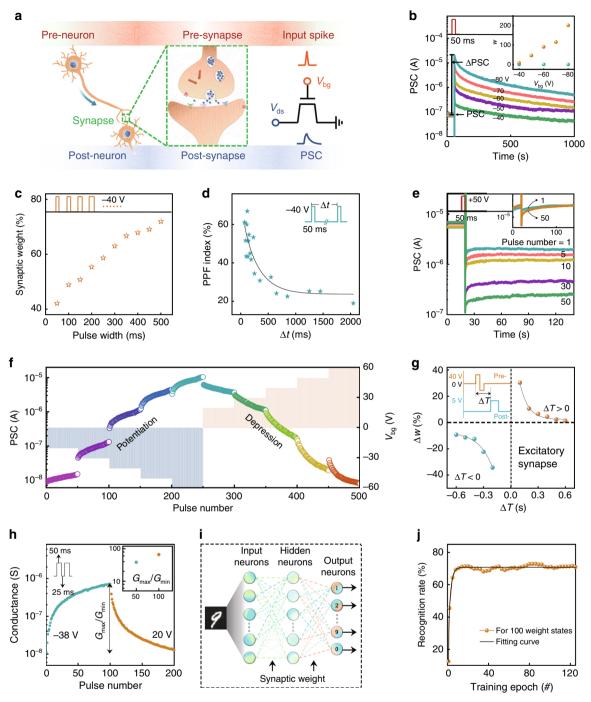

Artificial synaptic features based on InSe A-FET. Inspired by the charge trapping dominated memory characteristics of InSe A-FET discussed above, we then investigated its basic synaptic functions for application as an artificial InSe synaptic device. For a fair comparison, the retention capacity evaluation and the synaptic behaviour emulation were also implemented on InSe V-FET device to further confirm the important role of the native oxidation effect for the efficient application of environmentally sensitive semiconductors (Supplementary Fig. 7). In Fig. 5a, the biological synapse serves as an important media to deliver information by sending chemical neurotransmitters from preneuron to post-neuron 59-64. A suitable external stimulus from a pre-synaptic neuron would open the voltage-controlled Ca<sup>2+</sup> channel and lead to the released neurotransmitters passing through the synapse and arriving at the receptor on the postsynaptic neuron. Then, a sufficient number of neurotransmitters would trigger the opening of a chemical-controlled channel on the post-synaptic neuron and realize the signal transportation. Correspondingly, this phenomenon can be analogized as the gating-modulated carrier transport process in the InSe artificial synaptic device (the right side of Fig. 5a), in which the electrical input signal from the gate electrode is considered as the input spike in the pre-neuron to trigger the postsynaptic current (PSC), and the corresponding conductance in the InSe channel resembles the synaptic weight  $(w)^{65}$ . Note that the generated PSC can be assigned as excitatory PSC (EPSC) or inhibitory PSC (IPSC), which is determined by the synaptic weight of the two connective neurons. To mimic the information transmission in a biological synapse between two neighbouring neuron cells, the EPSC responses of the InSe artificial synaptic device under several presynaptic  $V_{\text{bg}}$  pulses with various amplitudes were first examined. As shown in Fig. 5b, all of the recorded EPSC curves for InSe A-FET underwent a rapid increase and a slow decay period when a presynaptic spike was applied. With the increase of the spike amplitude, they cannot return back to the initial current, signifying that the conductance of the InSe channel exhibited a memory feature at ambient conditions. The peak value of EPSC gradually increased along with the increase of the applied spike pulse from -40 to -80 V, which corresponded to the excitatory synaptic behaviour. While in the case of InSe V-FET, the sharp drop can be evidently observed from the measured current curves, offering self-consistent evidence for the worse retention characteristics of InSe V-FET (Supplementary Fig. 7a and b). The inset of Fig. 5b provides the calculated synaptic weight ( $\Delta$ PSC/PSC) depending on the spike amplitudes under two conditions. It is expected that the value of the voltage spike can be largely reduced to realize low energy consumption by matching a thinner dielectric layer or other dielectric materials. Figure 5c displays the variation of w along with increasing the pulse width from 50 to 500 ms. Another dynamic evolution of the recorded IPSC responses is shown in Supplementary Fig. 8, which explained that more electrons were trapped in the  $InO_x$  layer for a longer pulse duration.

The performance of learning and forgetting operations in a human brain relies on its capability to manage the synaptic weight, that is, the synaptic plasticity, which can be classified as STP and LTP according to the retention ability<sup>66</sup>. PPF is considered as a typical STP feature of a synapse, which is closely related to the synaptic activity for executing complicated neuronal tasks<sup>67</sup>. It describes the process when a neuron cell receives two consecutive actions, more neurotransmitters in synaptic vesicles will be released to result in the enhanced postsynaptic response. This phenomenon can be successfully implemented in our artificial synapse by simply applying a pair of presynaptic spikes and recording the corresponding variation of EPSC. The obtained PPF index depending on the time interval between two input spikes is shown in Fig. 5d. The value of the PPF index gradually decreased from 68 to 18% with the increasing time interval because of the enhanced releasing process of electrons from the InO<sub>x</sub> trapping layer, which could be well fitted by the double exponential function<sup>68</sup>. Note that the extracted relaxation time constants ( $t_1 = 10 \text{ ms}, t_2 = 320 \text{ ms}$ ) coincide with the reported values in biological synapses, and the details can be found in Supplementary Fig. 9. In addition, Fig. 5e and Supplementary Fig. 10 exhibit the extracted IPSC as a function of retention time by varying the number of input spikes. If the input voltage is sufficiently large (+50 V), the recorded IPSC sharply decreased and then could not climb back to the initial state over the measurement periods even after undergoing few spike training, which illuminated the emulation of the LTP behaviour. Compared with that for InSe A-FET, the PPF index for InSe V-FET slightly changes near 0% with the increasing time interval (Supplementary Fig. 7c), instead of the exponential variation. Also, the recorded current curves under several sequential gate voltage pulses almost overlapped with each together, even under 50 sequential pulses (the inset of Fig. 5e), failing to demonstrate the LTP. These results obviously indicate that the synaptic features cannot be mimicked in the InSe V-FET system owing to the absence of the InO<sub>x</sub> interfacial layer to effectively boost the charge transport behaviour. Furthermore, sequential voltage pulses were executed as the presynaptic input signals to examine the dynamic potentiation and depression behaviour of the InSe artificial synaptic device. The monitored EPSC in Fig. 5f stepwise increased to  $1.94 \times 10^{-5}$  A by varying the 50 pulse sequences of the negative voltage, and then dropped back to  $7.9 \times 10^{-9}$  A by applying the positive voltage pulse sequences. The extracted synaptic weight changes depending on the sequential input pulses were provided in Supplementary Fig. 11. All of the positive and negative exponentially varied PSC responses showed the flexible plasticity of the InSe artificial synaptic device, corresponding to the sustained Erase and Program operations of electrons between the InSe channel and  $InO_x$  trapping layer, respectively.

As one of the representative characteristics of LTP, STDP is of significance to the Hebbian synaptic learning and memory functions, in which the synaptic weight can be adjusted by the time interval and the spike order between the pre- and postsynaptic stimulations<sup>13</sup>. If the presynaptic spike arrives before that of the postsynaptic, that is  $\Delta T > 0$ , it will result in long-term potentiation. If  $\Delta T < 0$ , it will lead to long-term depression. In our work, the STDP behaviour of the InSe artificial synaptic device was built by applying the separated pre- and postsynaptic spikes from the back gate terminal and drain terminal, respectively. As shown in Fig. 5g, the changes of synaptic weight under  $\Delta T > 0$  and  $\Delta T < 0$  respectively indicated the potentiation and depression responses in our artificial synaptic device. The fitted curves based on the exponential functions located in the first and third quadrants were highly consistent with the excitatory feature in the typical biological synapse<sup>69</sup>.

**Fig. 5 Emulation of the synaptic functions by the InSe artificial synaptic device. a** Schematic illustration of a biological synapse and the InSe artificial synaptic device. **b** EPSC generated by applying several input spikes with different voltage amplitudes under the potentiation condition of -80, -70, -60, -50, and -40 V, respectively. The drain voltage is set as 0.1 V under the Read operations. The change of PSC after the input spike (ΔPSC) is labelled by arrows. Inset shows the calculated w for the case of InSe A- (Brown) and V-FET (Turquoise) devices. **c** Variation of w under different pulse widths. **d** Extracted PPF index ( $(A_2 - A_1)/A_1$ ) versus spike time interval  $\Delta t$ , where  $A_1$  and  $A_2$  are the first and second EPSC peak, respectively. The solid line is the fitted curve based on the double exponential function. **e** The plot of IPSC changes over 120 s after stimulating by various numbers of the input pulse. The inset shows the corresponding changes after 1 and 50 pulses in InSe V-FET. **f** Monitored PSC under several sequential voltage pulses with various amplitudes (pulse width of 50 ms, time interval of 100 ms), which correspond to dynamic depression and potentiation behaviours in PSC. **g** Changes of synaptic weight ( $\Delta w$ ) depending on the Time interval ( $\Delta T$ ) to emulate the STDP behaviour and the corresponding fitted curves based on the exponential functions. Note that the  $\Delta w$  is defined as ( $\Delta PSC_2 - \Delta PSC_1$ )/ $\Delta PSC_1$ , where  $\Delta PSC_1$  and  $\Delta PSC_2$  represent the obtained changes of PSC response after the pre- and postsynaptic simulations, respectively. The fitted lines are provided as a guide to the eye. The inset shows the schematic of the separated input signals from two terminals with the pulse width of 200 ms. **h** The potentiation and depression weight states of the conductance (G) extracted from InSe A-FET device under 100 successive input pulses. The inset shows the  $G_{max}/G_{min}$  (conductance margin) under 50 pulses (38.1) to 100 pulses (65.3), respectively

Furthermore, we constructed a learning platform based on a three-layer perceptron network model and the above InSe artificial synaptic devices to simulate the system-level pattern recognition<sup>70</sup>. As shown in Fig. 5i, the designed ANN consists of 784 input neurons, 150 hidden layer neurons, and 10 output neurons. The binarized images (28 × 28 pixels) in the MNIST (Modified National Institute of Standards and Technology) handwritten database and the obtained digitals (0-9), serving as the image data vector and output vector, were assigned to the input and output layers, respectively. The variable weight connections among these neurons, as the synaptic weight vector, correspond to the potentiation and depression conduction states of InSe synaptic devices, which were experimentally extracted under successive input spikes (Fig. 5h). To perform the recognition tasks for digital images, 60000 images were used from the MNIST database during the learning process; the vector conversion via the sigmoid activation function and the weight update via the back-propagation learning algorithm were involved in. Note that the cycle-to-cycle weight update variation ( $\sigma$ ) was set to 1%. Figure 5j shows the obtained recognition rates of the digitals (Supplementary Fig. 12 for 50 weight states) after 125 training epochs, with each epoch size of 8000 images. The overall accuracy rate improves from 45 to 70% with the increasing conductance margin, hinting at the positive effect of higher conductance margin on the recognition rate for MNIST patterns. On the other hand, compared with the previous works for the 2D materials-based electronic devices, the proposed InSe A-FET device presents three vital advantages: (1) The interfacial native charge trapping layer has little impact on electrical properties or stability; (2) The current on-off ratio and high mobility of InSe shows the potential for developing high-speed electronics; (3) The low power consumption systems can be expected through improving high-k dielectric materials or diminishing the channel length to deduce the spike duration time, spike voltage, as well as the response current. Thus we believe that the emulation of synaptic functions in device level and the simulation of pattern recognition in system-level in this work further demonstrate the important availability of native oxide-inspired van der Waals devices for designing promising neuromorphic architectures.

## **Discussion**

In summary, we developed a native oxide-inspired synaptic device based on the boosted charge trapping behaviours in a typical environmentally sensitive 2D material, InSe. Combining the HRTEM analysis and dynamic characteristic measurements showed that the thin layer of InO<sub>x</sub> located at the bottom of the InSe channel is responsible for the controllable charge trapping and releasing behaviour in InSe A-FET, which corresponds to surface dominated carrier fluctuations. Thus, the unique configuration is believed to provide innate opportunity to demonstrate reliable memory operations with multiple storage characteristics. Furthermore, synaptic functions at the device level based on the InSe artificial synaptic device by emulating the flexible plasticity of PPF and STDP at the device level, and the pattern recognition simulation at the system level based on the InSe artificial synaptic device, were successfully achieved, which pioneer a new opportunity for ultrasensitive van der Waals electronics, such MoTe2, HfS2, or BP, to effectively control their native oxidation events towards establishing processing-efficient neuromorphic computing systems.

### Methods

**Fabrication of the InSe devices**. The few-layered InSe flake was mechanically exfoliated from the InSe crystal with the aid of polydimethylsiloxane (PDMS) films for better electrical performance, and then transferred onto the  $SiO_2/Si$  substrate. The thickness of the  $SiO_2$  dielectric layer was selected to be 300 nm to benefit the analysis of the thickness of the InSe channel. Then, a 32-nm-thick In layer was

deposited on the top of the InSe channel to achieve the excellent contact condition and high carrier mobility. Finally, a pair of 50-nm-thick Au electrodes were deposited by thermal evaporation at a pressure below  $3\times 10^{-6}$  Torr to form the source-drain contacts with the InSe channel. The AFM scan was implemented to examine the thickness of the exfoliated InSe flakes.

Characterization of the electrical properties of the InSe devices. The electrical performance of InSe A-FET and the emulation of synaptic functions were characterized under the ambient environment using a Lakeshore probe station equipped with a B1500A semiconductor parameter analyser. The electrical characteristics of InSe V-FET were also determined under vacuum environment for a better comparison. To examine the formation of the native oxidation InO. layer, the crosssectional analysis of InSe A-FET was conducted using focused ion beam (FIB) systems and HRTEM technology, equipped with EDS. To explore the dominant mechanism of the carrier transport behaviour in the InSe V- and A-FET, the dynamic characteristic measurements were performed based on an in situ KPFM (Dimension Icon, Bruker) and a programmable point probe noise measurement system (3PNMS). For in situ Kelvin Probe Force Microscopy (KPFM) measurement (Bruker Dimension Icon SPM system), the conductive AFM probe (Pt/Ir) (AppNano, ANSCM-PA, 40 N/m, 300 kHz) was set as ground and the bias pulses (±20 V) were applied from the backgate terminal via an external precision source unit (Keysight B2912A). The surface potential difference between tip and sample were detected under the tapping mode and the 2nd interleave scanning with the tip lift height 30 nm. The scanning range and resolution were 2 µm and 512 by 128 pixels respectively. The system noise floor is about  $1 \times 10^{-27}$  A<sup>2</sup> Hz<sup>-1</sup>. The source-drain current fluctuations were recorded at a certain gate voltage and source-drain voltage to analyze the dynamic carrier transport behaviour under ambient and vacuum conditions, respectively. Besides, for minimizing the external electrical interference to the monitored charge fluctuations, all the measurements were performed in a grounded metal cavity on an isolated table under the dark conditions.

### **Date availability**

The data that support the findings of this study are available from the corresponding author upon request.

Received: 7 November 2019; Accepted: 15 May 2020; Published online: 12 June 2020

# References

- Novoselov, K. S. et al. Two-dimensional gas of massless Dirac fermions in graphene. Nature 438, 197–200 (2005).

- Luo, W. et al. Carrier modulation of ambipolar few-layer MoTe<sub>2</sub> transistors by MgO surface charge transfer doping. Adv. Funct. Mater. 28, 1704539 (2018).

- Chuang, H. J. et al. Low-resistance 2D/2D ohmic contacts: a universal approach to high-performance WSe<sub>2</sub>, MoS<sub>2</sub>, and MoSe<sub>2</sub> transistors. *Nano Lett.* 16, 1896–1902 (2016).

- Xiang, D. et al. Two-dimensional multibit optoelectronic memory with broadband spectrum distinction. Nat. Commun. 9, 2966 (2018).

- 5. Yang, Z. & Hao, J. Recent progress in black-phosphorus-based

- heterostructures for device applications. Small Methods 2, 1700296 (2018).

Wu, E. et al. Dynamically controllable polarity modulation of MoTe<sub>2</sub> field-effect transistors through ultraviolet light and electrostatic activation. Sci. Adv. 5, eaav3430 (2019).

- Yang, S.-H. et al. Multifunctional full-visible-spectrum optoelectronics based on a van der Waals heterostructure. Nano Energy 66, 104017 (2019).

- 8. Tran, M. D. et al. Two-terminal multibit optical memory via van der waals heterostructure. *Adv. Mater.* **31**, 1807075 (2019).

- Wang, S. et al. A MoS<sub>2</sub>/PTCDA hybrid heterojunction synapse with efficient photoelectric dual modulation and versatility. Adv. Mater. 31, 1806227 (2019).

- Sangwan, V. K. et al. Multi-terminal memtransistors from polycrystalline monolayer molybdenum disulfide. Nature 554, 500–504 (2018).

- Yang, C. S. et al. A synaptic transistor based on quasi-2D molybdenum oxide. Adv. Mater. 29, 1700906 (2017).

- Chang, Y. M. et al. Reversible and precisely controllable p/n-type doping of MoTe<sub>2</sub> transistors through electrothermal doping. Adv. Mater. 30, 1706995 (2018).

- Tian, H. et al. Anisotropic black phosphorus synaptic device for neuromorphic applications. Adv. Mater. 28, 4991–4997 (2016).

- Ho, P. H. et al. High-mobility InSe transistors: the role of surface oxides. ACS Nano 11, 7362–7370 (2017).

- Chae, S. H. et al. Oxidation effect in octahedral hafnium disulfide thin film. ASC Nano 10, 1309–1316 (2016).

- Ashari-Astani, N. et al. Ruddlesden-Popper phases of methylammoniumbased two-dimensional perovskites with 5-ammonium valeric acid

- $AVA_2MA_{n-1}Pb_nI_{3n+1}$  with n=1, 2, and 3. J. Phys. Chem. Lett. 10, 3543–3549 (2019).

- Wood, J. D. et al. Effect passivation of exfoliated black phosphorus transistors against ambient degradation. Nano Lett. 14, 6964–6970 (2014).

- Mleczko, M. J. et al. HfSe2 and ZrSe2: two-dimensional semiconductors with native high-k oxides. Sci. Adv. 3, 1700481 (2017).

- Li, Q., Zhou, Q. H., Shi, L., Chen, Q. & Wang, J. L. Recent advances in oxidation and degradation mechanisms of ultrathin 2D materials under ambient conditions and their passivation strategies. *J. Mater. Chem. A* 7, 4291 (2019).

- Ryder, C. R. et al. Covalent functionalization and passivation of exfoliated black phosphorus via aryldiazonium chemistry. Nat. Chem. 8, 597–602 (2016).

- Kang, K. et al. Graphene-assisted antioxidation of tungsten disulfide monolayers: substrate and electric-field effect. Adv. Mater. 29, 1603898 (2017).

- Gkoupidenis, P., Schaefer, N., Garlan, B. & Malliaras, G. G. Neuromorphic functions in PEDOT:PSS organic electrochemical transistors. *Adv. Mater.* 27, 7176–7180 (2015).

- Sherrington, C. The Integrative Action of the Nervous System. CUP Archive Cambridge (1952).

- Bi, G.-Q. & Poo, M.-M. Synaptic modifications in cultured hippocampal neurons: dependence on spike timing, synaptic strength, and postsynaptic cell type. J. Neurosci. 18, 10464 (1998).

- Abbott, L. F. & Regehr, W. G. Synaptic computation. Science 431, 796–803 (2004).

- Yang, R. et al. Synaptic plasticity and memory functions achieved in a WO<sub>3-x</sub>-based nanoionics device by using the principle of atomic switch operation. Nanotechnology 24, 384003 (2013).

- Yao, P. et al. Face classification using electronic synapses. Nat. Commun. 8, 15199 (2017).

- Yu, S. Neuro-inspired computing with emerging nonvolatile memory. Proc. IEEE 106, 260–285 (2018).

- Burgt, Y. et al. A non-volatile organic electrochemical device as a low-voltage artificial synapse for neuromorphic computing. *Nat. Mater.* 16, 414–418 (2017).

- Indiveri, G., Chicca, E. & Douglas, R. A VLSI array of low-power spiking neurons and bistable synapses with spike-timing dependent plasticity. *IEEE Trans. Neural Netw.* 17, 211–221 (2006).

- Fusi, S., Annunziato, M., Badoni, D., Salamon, A. & Amit, D. J. Spike-driven synaptic plasticity: theory, simulation, VLSI inplementation. *Neural Comput.* 12, 2227 (2000).

- Jiang, J. et al. 2D MoS<sub>2</sub> neuromorphic devices for brain-like computational systems. Small 13, 1700933 (2017).

- Zhu, J. D. et al. Ion gated synaptic transistors based on 2D van der Waals crystals with tunable diffusive dynamics. Adv. Mater. 30, 1800195 (2018).

- Ahmed, T. et al. Optically stimulated artificial synapse based on layered black phosphorus. Small 15, 1900966 (2019).

- Hamer, M. et al. Gate-defined quantum confinement in InSe-based van der Waals heterostructures. Nano Lett. 18, 3950–3955 (2018).

- Li, Z. J. et al. High-performance photo-electrochemical photodetector based on liquid-exfoliated few-layered InSe nanosheets with enhanced stability. Adv. Funct. Mater. 28, 1705237 (2018).

- Bandurin, D. A. et al. High electron mobility, quantum Hall effect and anomalous optical response in atomically thin InSe. Nat. Nanotechnol. 12, 223 (2017).

- Li., M. J. et al. High mobilities in layered InSe transistors with indiumencapsulation-induced surface charge doping. Adv. Mater. 30, 1803690 (2018).

- Tsai, T.-H. et al. High-Mobility InSe transistors: the nature of charge transport. ACS Appl. Mater. Interfaces 11, 35969–35976 (2019).

- Chang, Y.-R. et al. Surface oxidation doping to enhance photogenerated carrier separation efficiency for ultrahigh gain induim selenide photodetector. ACS Photonics 4, 2930–2936 (2017).

- Huang, Y. et al. Reliable exfoliation of large-area high-quality flakes of graphene and other two-dimensional materials. ACS Nano 9, 10612–10620 (2015).

- Late, D. J. L., Ramakrishna Matte, H. S. S., Dravid, V. P. & Rao, C. N. R. Hysteresis in single-layer MoS<sub>2</sub> field effect transistors. ACS Nano 6, 5635–5641 (2012).

- 43. Lee, J. et al. Monolayer optical memory cells based on artificial trap-mediated charge storage and release. *Nat. Commun.* **8**, 14734 (2017).

- Seo, S. et al. Artificial optic-neural synapse for colored and color-mixed pattern recognition. Nat. Commun. 9, 5106 (2018).

- Wang, H., Wu, Y., Cong, C., Shang, J. & Wu, T. Hysteresis of electronic transport in grapheme transistors. ACS Nano 4, 7221 (2010).

- Tian, H. et al. A dynamically reconfigurable ambipolar black phosphorus memory device. ACS Nano 10, 10428 (2016).

- 47. Strand, J. et al. Intrinsic charge trapping in amorphous oxide films: status and challenges. *J. Phys.: Condens. Matter* **30**, 233001 (2018).

- Hoffman, A. N. et al. Exploring the air stability of PdSe<sub>2</sub> via electrical transport measurements and defect calculations. *npj 2D Mater. Appl.* 3, 50 (2019).

- Chen, M. et al. Multibit data storage states formed in plasma-treated MoS<sub>2</sub> transistors. ACS Nano 8, 4023–4032 (2014).

- Chen, M. et al. Abnormal multiple charge memory states in exfoliated fewlayer WSe<sub>2</sub> transistors. ACS Nano 11, 1091–1102 (2017).

- Lin, Y. F. et al. Origin of noise in layered MoTe<sub>2</sub> transistors and its possible use for environmental sensors. Adv. Mater. 27, 6612–6619 (2015).

- Xu, Y., Minari, T., Tsukagoshi, K., Chroboczek, J. A. & Ghibaudo, G. Direct evaluation of low-field mobility and access resistance in pentacene field-effect transistors. J. Appl. Phys. 107, 114507 (2010).

- Wu, W. R. et al. Mobility fluctuation-induced low-frequency noise in ultrascaled Ge nanowire nMOSFETs with near-ballistic transport. *IEEE Trans. Electraon Devices* 65, 2573 (2018).

- Jang, D. et al. Low-frequency noise in strained SiGe core-shell nanowire pchannle filed effect transistors. Appl. Phys. Lett. 97, 073505 (2010).

- Balandin, A. A. Low-frequency 1/f noise grapheme devices. Nat. Nanotechnol. 8, 549 (2013).

- Na, J. et al. Few-layer black phosphorus field-effect transistors with reduced current fluctuation. ACS Nano 8, 11753–11762 (2014).

- Renteria, J. et al. Low-frequency 1/f noise in MoS<sub>2</sub> transistors: relative contributions of the channel and contacts. Appl. Phys. Lett. 104, 153104 (2014).

- Choi, M. S. et al. Controlled charge trapping by molybdenum disulphide and graphene in ultrathin heterostructured memory devices. *Nat. Commun.* 4, 1624 (2013).

- Yan, X. B. et al. Vacancy-Induced synaptic behavior in 2D WS<sub>2</sub> nanosheet-based Memristor for low-power neuromorphic computing. Small 15, 1901423 (2019).

- Wang, Z. et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. Nat. Mater. 16, 101 (2017).

- Tian, H. et al. Graphene dynamic synapse with modulatable plasticity. Nano Lett. 15, 8013–8019 (2015).

- Voelker, M. & Fromherz, P. Signal transmission from individual mammalian nerve cell to field-effect transistor. Small 1, 206–210 (2005).

- Wang, Z. et al. Capacitive neural network with neuro-transistors. *Nat. Commun.* 9, 3208 (2018).

- Shi, J., Ha, S. D., Zhou, Y., Schoofs, F. & Ramanathan, S. A correlated nickelate synaptic transistor. *Nat. Commun.* 4, 2676 (2013).

- Gkoupidenis, P., Koutsouras, D. A. & Malliaras, G. G. Neuromorphic device architectures with global connectivity through electrolyte gating. *Nat. Commun.* 8, 15448 (2017).

- Du, C., Ma, W., Chang, T., Sheridan, P. & Lu, W. D. Biorealistic implementation of synaptic functions with oxide memristors through internal ionic dynamics. Adv. Funct. Mater. 25, 4290–4299 (2015).

- Jo, S. H. et al. Nanoscale memristor device as synapse in neuromorphic systems. *Nano Lett.* 10, 1297–1301 (2010).

- Zucker, R. S. & Regehr, W. G. Short-term synaptic plasticity. Annu. Rev. Physiol. 64, 355 (2002).

- Song, Sen, Miller, K. D. & Abbott, L. F. Competitive Hebbian learning through spike-timing-dependent synaptic plasticity. *Nat. Neurosic* 3, 919 (2000).

- Chen, P.-Y, Peng, X. & Yu, S. NeuroSim+: An integrated device-to-algorithm framework for benchmarking synaptic devices and array architectures. 2017 IEEE International Electron Device Meeting 6.1.1-6.1.4. (CA: San Francisco, 2017).

## Acknowledgements

This work was financially supported by the National Key Research and Development Program of China (Grant No. 2016YFB0501604), the Natural Science Foundation of China (Grant Nos. 61774061 and 61504043), the NSAF Foundation of China (Grant No. U1830130), Natural Science Foundation of Shanghai (Grant No. 19ZR1473400), and the Taiwan Ministry of Science and Technology (Grant Nos. MOST 108-2112-M-005-012-MY3 and MOST-109-2636-M-009-002).

## **Author contributions**

F.-S.Y., M.J.L., S.-H.L. and Y.-F.L. designed the experiments and analyzed the data. F.-S.Y., M.-P.L. and I.-Y.H. contributed to the device fabrication. F.-S.Y. and M.J.L. performed the electrical characterizations. J.-Y.C., J.-K.C., S.-H.Y., Y.-M.C., K.-C.L. and Y.-C.C. contributed to the properties investigation of the materials. The InSe material was prepared by C.-H.H. H.F.L., Y.Z.L. and W.W.L. conducted the digit recognition simulation of the artificial neural network. M.J.L., F.S.Y. and Y.-F.L. prepared and revised the manuscript. All authors have discussed the results and commented on the manuscript.

## **Competing interests**

The authors declare no competing interests.

## **Additional information**

Supplementary information is available for this paper at https://doi.org/10.1038/s41467-020-16766-9

$\begin{tabular}{ll} \textbf{Correspondence} \ and \ requests \ for \ materials \ should \ be \ addressed \ to \ M.L., \ W.L., \ C.-H.L. \ or \ Y.-F.L. \end{tabular}$

**Peer review information** *Nature Communications* thanks Tania Roy and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. Peer reviewer reports are available.

Reprints and permission information is available at http://www.nature.com/reprints

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing,

adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit <a href="http://creativecommons.org/licenses/by/4.0/">http://creativecommons.org/licenses/by/4.0/</a>.

© The Author(s) 2020