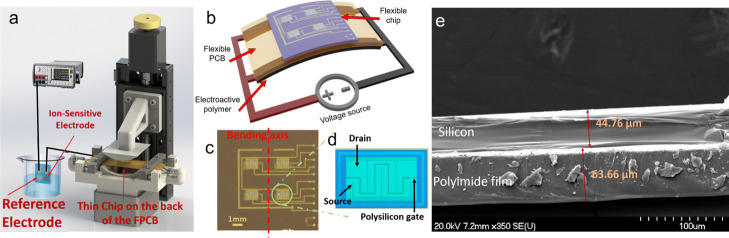

Figure 2.

Experimental setup and the fabricated thin chips. (a) Schematic of the experimental setup showing the fabricated ion-sensitive gate and RE connected with the transistor on the FPCB in an extended-gate configuration. The PCB is mounted on the custom-made automated 3D-printed bending setup. (b) Schematic representation of an alternative way to bent chip using an electroactive polymer embedded on the backside of the FPCB. (c) Fabricated chip (1 × 1 cm2) with four n-channel transistors and the bending axis. (d) Designed fingers of the transistor with a channel dimension of W/L = 2000 μm/12 μm. (e) Scanning electron microscopy image of the cross section of thin chip on the polyimide-based FPCB showing the thickness of the chip and FPCB.