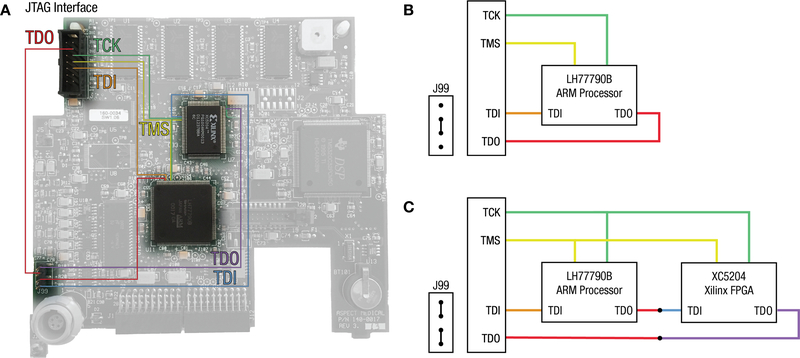

Figure 3:

(A) Functional layout of the JTAG Interface, involving the LH77790B ARM Microprocessor, the Xilinx FPGA, and the circuit board jumper J99. The major JTAG control lines are TDI (Test Data In), TDO (Test Data Out), TCK (Test Clock) and TMS (Test Mode Select).

(B) Debugging must be enabled by placing a jumper on J99. Connecting the middle two pins of J99 completes the continuity of the TDO line from the ARM Microprocessor to the JTAG Interface port, allowing external debugging to begin.

(C) JTAG allows multiple devices to be queried in sequence from one interface bus. Connecting the pins of J99 in pairs, as shown, additionally loops in the JTAG circuitry of the Xilinx FPGA by daisy-chaining the TDI/TDO communication path.