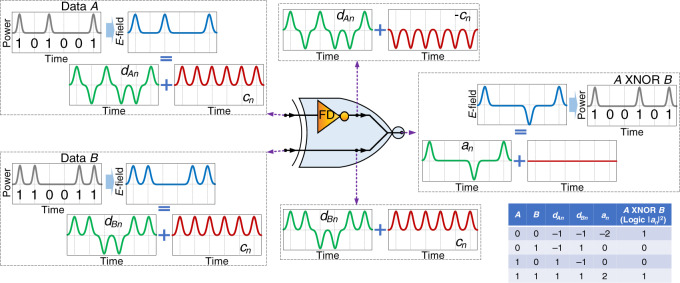

Fig. 2. The operation principle of the proposed frequency-domain zero switching-energy logic XNOR gate.

Conceptual illustration of how a frequency-domain (FD) passive NOT gate and a combiner can be used to implement an ultrafast passive XNOR operation. The FD NOT gate inverts the clock of Data A (red), which when summed with Data B at the combiner destructively cancels the clock of Data B. The resulting output field, an, is simply the sum of the data field amplitude of Data A, dAn, with the data field amplitude of Data B, dBn, an = dAn + dBn. The output intensity, |an|2, gives the XNOR operation. The corresponding truth table is shown in the lower right-hand corner.