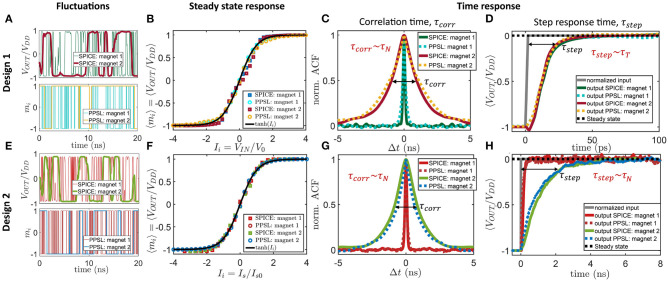

Figure 2.

Autonomous behavioral model for p-bit: (A–D) Behavioral model for the autonomous hardware with design 1 (Figure 1B) is benchmarked with SPICE simulations of the actual device involving experimentally benchmarked modules. The behavioral model (labeled as “PPSL”) shows good agreement with SPICE in terms of capturing fluctuation dynamics (A), steady-state sigmoidal response (B), and two different time responses: autocorrelation time of the fluctuating output under zero input condition labeled as τcorr (C), which is proportional to the LBM retention time τN in the nanosecond range, and the step response time τstep (D) that is proportional to transistor response time τT, which is few picoseconds and much smaller than τN. The magnet parameters used in the simulations are mentioned in section 2. (E–H) Similar benchmarking for p-bit design 2 (Figure 1C). In this case, τstep is proportional to τN. For (B,F), each point for the SPICE simulation was obtained by averaging mi over 1 μs. The step response time for (D,H) is obtained by averaging over 2,000 ensembles where Ii = −5 at t < 0 and Ii = 0 at t > 0.