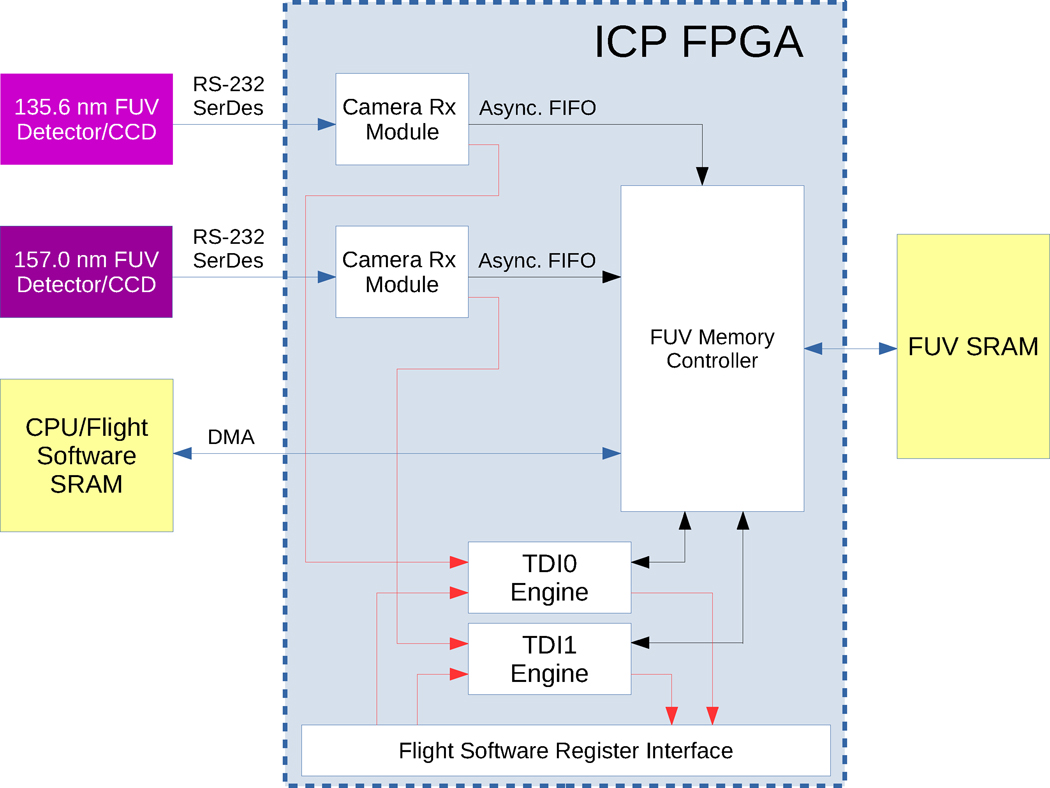

Fig. 7.

High-level view of the ICON FUV digital data acquisition and processing sub-system. The relationships between the TDI engines and other sub-system components are shown. Black and blue arrows represent digital data paths in the directions of the arrows, where blue wires represent data paths crossing I/O boundaries. Red arrows indicate control signals and status flags. Asynchronous First-In First-Out (FIFO) buffering is used to transfer data from the CCD readout electronics to ICON’s payload Instrument Control Package (ICP) FPGA. A priority-based memory controller arbitrates access to FUV memory. Direct memory access (DMA) is used to transfer processed images and LUTs from FUV memory to flight software CPU memory and vice versa. FUV memory is used to store incoming FUV camera frames, TDI integration buffers, and active operational LUTs. Flight software requests DMA transfer of processed TDI image buffers where completion of TDI processing is indicated by the TDI engines through the register interface.