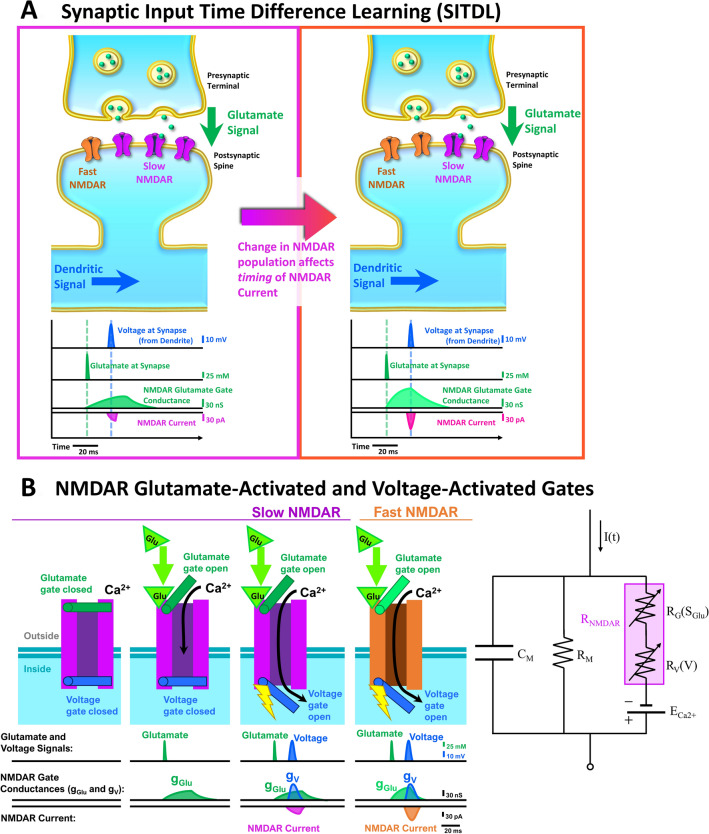

Figure 1.

The SITDL hypothesis: An example of how activity-dependent changes in NMDAR population can affect synaptic current timing. (A) Left: A developing silent synapse starts with a majority of slow NMDARs with slower glutamate gate activation than fast NMDARs. The synapse receives a glutamate signal followed later by a dendritic voltage signal, causing a difference in activation of NMDARs’ voltage and glutamate gates. Right: As the synapse develops and experiences the same timing between voltage and glutamate signals, its NMDAR population may change, caused by the difference in glutamate and voltage gate activation. In this case, fast NMDARs replace slow NMDARs until the gate conductance difference is minimized, thus aligning the overall NMDAR current peak with the peak of the voltage signal. This allows the developing synapse to learn the timing difference between the voltage and glutamate signals by encoding it in the NMDAR population’s glutamate gate activation time. (B) Left: Each NMDAR has a glutamate gate and a voltage gate that can be activated independently, with corresponding gate conductances shown. Coincident activation of both gates allows influx of Ca2+ (NMDAR Current). A slow NMDAR has a slower glutamate gate activation, therefore experiencing slower change in glutamate gate conductance than a fast NMDAR. Right: Circuit diagram of a post-synaptic spine containing only NMDARs. An NMDAR (RNMDAR) is shown as variable serial resistances of its glutamate gate (RG) and voltage gate (RV) that depend on the glutamate signal (SGlu) and dendritic spine’s voltage (V), respectively. CM denotes the membrane capacitance, RM the membrane resistance, ECa2+ the cell’s Nernst potential for Ca2+, and I(t) the external input.