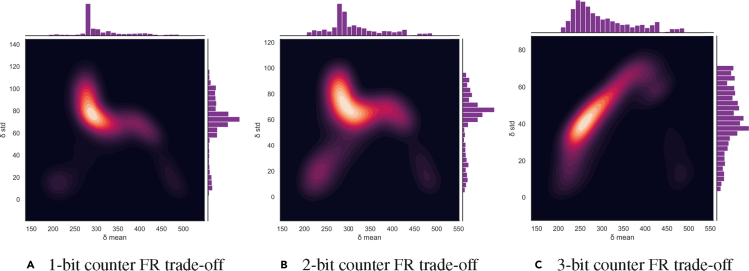

Figure 13.

Feasibility vs. robustness (FR) trade-off comparison between the 1-bit counter, the 2-bit counter, and the 3-bit counter

For all simulated synthetic gates, we plot a 2D density graph with contours for δ mean vs. δ-std. The plots help identify the preferred region for designing new synthetic gates. The contour lines represent different levels of probability density for data points. The darker, the higher probability it represents. Right, middle, and left plots show, respectively, the contours for 1-bit, 2-bit and 3-bit counters. For the single-bit counter, the best region for designing a synthetic gate is around δ-mean = 300 and δ-std = 75. For the 2-bit counter, the best region for designing a synthetic gate is δ-mean from around 260 to 350, and δ-std can range from 60 to 90. For the 3-bit counter, the best region for designing a synthetic gate is around 240 to 320, and δ-std can range from 20 to 70.