Qi Li <sup>1</sup>, Junchen Dong <sup>2</sup>,\*, Dedong Han <sup>1</sup>,\* and Yi Wang <sup>1</sup>

- <sup>1</sup> Institute of Microelectronics, Peking University, Beijing 100871, China; 1901111209@pku.edu.cn (Q.L.); imewangyi@pku.edu.cn (Y.W.)

- <sup>2</sup> School of Information & Communication Engineering, Beijing Information Science & Technology University, Beijing 100101, China

- \* Correspondence: jcdong@bistu.edu.cn (J.D.); handedong@pku.edu.cn (D.H.)

**Abstract:** InSnO (ITO) thin-film transistors (TFTs) attract much attention in fields of displays and low-cost integrated circuits (IC). In the present work, we demonstrate the high-performance, robust ITO TFTs that fabricated at process temperature no higher than 100 °C. The influences of channel thickness ( $t_{ITO}$ , respectively, 6, 9, 12, and 15 nm) on device performance and positive bias stress (PBS) stability of the ITO TFTs are examined. We found that content of oxygen defects positively correlates with  $t_{ITO}$ , leading to increases of both trap states as well as carrier concentration and synthetically determining electrical properties of the ITO TFTs. Interestingly, the ITO TFTs with a  $t_{ITO}$  of 9 nm exhibit the best performance and PBS stability, and typical electrical properties include a field-effect mobility ( $\mu_{FE}$ ) of 37.69 cm<sup>2</sup>/Vs, a V<sub>on</sub> of -2.3 V, a SS of 167.49 mV/decade, and an on–off current ratio over 10<sup>7</sup>. This work paves the way for practical application of the ITO TFTs.

Keywords: ITO TFTs; channel thickness; electrical characteristics; stability

# 1. Introduction

Metal-oxide thin-film transistors (TFTs) are recognized as a promising alternative to conventional hydrogenated amorphous silicon (a-Si:H) TFTs because of high performance, feasibility for flexible display, and good process compatibility with the a-Si:H TFTs [1–3]. Despite of these advantages, mobility and stability of metal-oxide TFTs need to be further improved to meet the increasing demands for advanced displays of fast frame rate, ultrahigh resolution, and large area [4–6].

InSnO (ITO) is a kind of highly conductive material with a wide bandgap (3.5~4.3 eV) and high optical transmittance (~90%), which generally serves as transparent electrodes in electron devices [7–9]. High conductivity of the ITO films origins from a facile pathway for electron conduction that is introduced by a large overlap of 5 s orbits of In and Sn elements [10]. Recently, ITO has been utilized as channel material of TFTs. Park et al. explored high-pressure annealing (HPA) treated ITO TFT with a saturation mobility ( $\mu_{sat}$ ) of 25.8 cm<sup>2</sup>/Vs [11]. Liang et al. demonstrated ITO TFTs with a high  $\mu_{sat}$  of 34.9 cm<sup>2</sup>/Vs as well as excellent stability [12]. Thereby, the ITO TFTs show immense potential in the field of display. However, the underlying mechanisms of ITO thickness ( $t_{ITO}$ ) on device performance of the ITO TFT are still not fully understood.

In this work, ITO TFTs with a  $t_{\rm ITO}$  of 6, 9, 12, and 15 nm are fabricated. To analyze the dependence of device performance and stability on channel thickness, a systematic study on ITO films and ITO TFTs is conducted. The ITO TFTs with a  $t_{\rm ITO}$  of 9 nm exhibit the best performance, the typical properties include a filed-effect mobility ( $\mu_{\rm FE}$ ) of 37.69 cm<sup>2</sup>/Vs, a turn-on voltage ( $V_{on}$ ) of –2.3 V, an on–off current ratio ( $I_{on}/I_{off}$ ) over  $10^7$ , and a subthreshold swing (SS) of 167.49 mV/decade. Moreover, the ITO TFTs show excellent positive bias stress (PBS) stability, and threshold voltage shift ( $\Delta V_{\rm TH}$ ) is 0.46 V under 1000 s, +1 MV/cm stress.

Citation: Li, Q.; Dong, J.; Han, D.; Wang, Y. Effects of Channel Thickness on Electrical Performance and Stability of High-Performance InSnO Thin-Film Transistors. *Membranes* 2021, *11*, 929. https://doi.org/ 10.3390/membranes11120929

Academic Editor: Feng-Tso Chien

Received: 31 October 2021 Accepted: 24 November 2021 Published: 26 November 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

### 2. Experiment

# 2.1. Fabrication of ITO TFTs

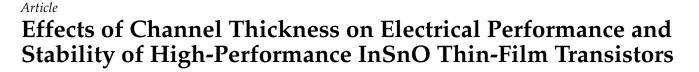

Figure 1 shows schematic structure of the ITO TFTs. Feature size of devices is width/length (W/L) = 100  $\mu$ m/100  $\mu$ m. Firstly, a heavily doped Si substrate was ultrasonic cleaned in acetone, alcohol, and deionized water, respectively. The Si substrate also acts as gate electrode. Next, a 30-nm HfO<sub>2</sub> dielectric layer was deposited by sputtering process at room temperature. Then, a 10-nm Al<sub>2</sub>O<sub>3</sub> dielectric layer was deposited by atomic layer deposition (ALD) process at 100 °C. Subsequently, an ITO channel layer was deposited by sputtering process, and the sputtering process was performed in Ar/O<sub>2</sub> gas mixture (Ar/O<sub>2</sub> flux ratio = 80/20) with a power of 70 W and a pressure of 1 Pa. Finally, a 100-nm Al source/drain electrode was deposited by sputtering process. Before we measured device performance, the ITO TFTs were thermally annealed in vacuum at 100 °C for 1 h.

Figure 1. Schematic device structure and device fabrication procedure of ITO TFTs.

#### 2.2. Characterization of ITO TFTs and ITO Films

Current-voltage (I-V) curves of the TFTs were characterized in dark at room temperature using a semiconductor parameter analyzer (Agilent B1500A). Capacitance properties of the metal–insulator–semiconductor (MIS) structure were measured using a semiconductor characterization system (Keithley 4200).

Microstructure of the ITO films were characterized by X-ray diffraction (XRD, Rigaku D/MAX 2000) and transmission electron microscopy (TEM, FEI Tecnai F20). Surface morphology of the ITO films were characterized by atomic force microscopy (AFM, Bruker Dimension Icon) and scanning electron microscope (SEM, FEI Helios Nanolab G3 CX). Chemical properties of the ITO thin films were examined using X-ray photoelectron spectroscopy (XPS, Axis Supra).

### 3. Results and Discussion

#### 3.1. Material Characterization of ITO Films

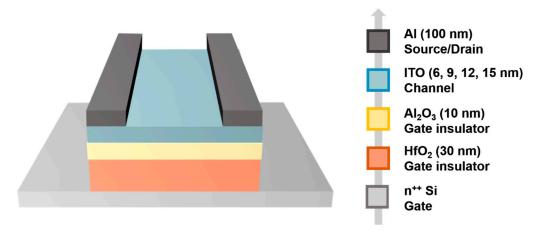

Figure 2a exhibits XRD spectrum of the ITO films. To accurately characterized diffraction peaks, the ITO films with a thickness of 55 nm were prepared on glass substrate. The obtained diffraction patterns contain only two broad peaks at approximately 23° and 45°, originating from the glass substrates [13]; this suggests that the ITO films have an amorphous phase. Normally, the amorphous phase of the ITO active layer is beneficial to the uniformity and stability of the ITO TFTs. In order to gain further insight into lattice structure of the ITO film, TEM measurement was performed, as shown in Figure 2b. It is observed that thickness of the ITO film is about 9 nm. No local crystalline grain can be observed. We performed real-time fast Fourier transform (FFT) of the ITO films, as shown in inset of Figure 2b. The FFT image exhibits amorphous diffraction pattern; thus, the lattice structure of the ITO film is definitely amorphous.

Figure 2. (a) XRD spectrum of ITO film on glass substrate. Film thickness is 55 nm. (b) TEM image and FFT image of ITO film.

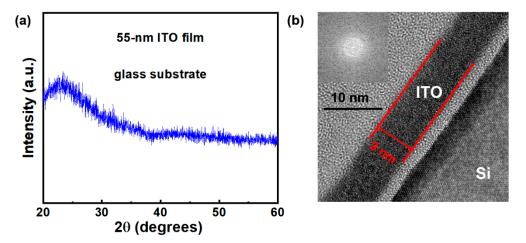

Figure 3a depicts AFM image of the ITO film, and the scanning area is set as 5  $\mu$ m × 5  $\mu$ m. Remarkably, the ITO film exhibits extremely flat surface morphology, and root-mean-square (RMS) roughness is 0.514 nm. Figure 3b shows SEM image of the ITO film. We can see that the local grains compactly and uniformly arrange with each other. The AFM and SEM validate smooth surface of the ITO films, which takes effect in reducing surface scattering and enhancing device performance of the ITO TFTs [14].

**Figure 3.** (a) AFM image of the ITO film. Scanning area is 5  $\mu$ m × 5  $\mu$ m. (b) SEM image of ITO film. Film thickness is 9 nm.

# 3.2. Electrical Characteristics of ITO TFTs

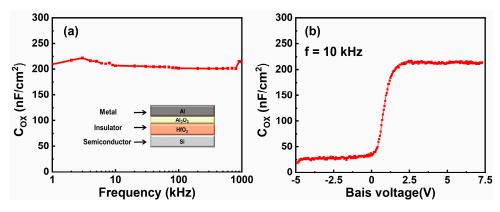

A MIS structure of Al-HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>-Si was fabricated to determine capacitance properties. Fabrication process of the HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> bilayer dielectric is mentioned above. The Si substrate is n-type, lightly doped. Figure 4a exhibits the capacitance–frequency (C–F) curve of the MIS structure. Capacitance per unit area (C<sub>OX</sub>) maintains a value of about 210 nF/cm<sup>2</sup> with frequency from 1 KHz to 1 MHz, implying high film quality of the HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> bilayer dielectric. Figure 4b exhibits capacitance–voltage (C–V) curve of the MIS structure at a frequency of 10 KHz. The C–V curve exhibits typically high-frequency capacitance property. C<sub>OX</sub> of the MIS structure is 214.55 nF/cm<sup>2</sup> when voltage is 5 V, which is consistent with the C–F curve.

Figure 4. (a) C–F curve of the MIS structure. (b) C–V curve of the MIS structure. Frequency is 10 KHz.

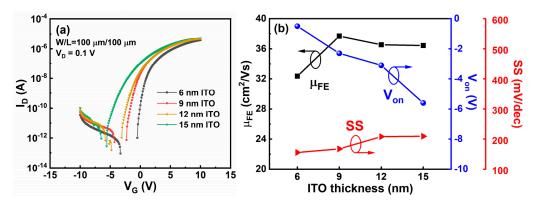

To examine effects of  $t_{ITO}$  on device performance of the ITO TFTs, drain current–gate voltage ( $I_D-V_G$ ) curves were measured, as shown in Figure 5a. All of the devices show an on-state current ( $I_{on}$ ) higher than 1  $\mu$ A and an  $I_{on}/I_{off}$  over 10<sup>7</sup>. Electrical properties of  $\mu_{FE}$ ,  $V_{on}$ , and SS are extracted, as shown in Figure 5b. Here,  $\mu_{FE}$  is calculated using the following equation:

$$\mu_{\rm FE} = \frac{\partial I_{\rm D}}{\partial V_{\rm C}} \times \frac{L}{W C_{\rm OX} V_{\rm D}} \tag{1}$$

where L and W are channel length and channel width, respectively [15]. V<sub>D</sub> is drain voltage and is set as 0.1 V. SS is extracted from the linear part of a plot of the log (I<sub>D</sub>) versus V<sub>G</sub>, using SS = dV<sub>G</sub>/dlogI<sub>D</sub> [16]. V<sub>on</sub> is defined as the gate voltage at which I<sub>D</sub> starts to monotonically increase [17]. We found that all of the devices show a  $\mu_{FE}$  larger than 30 cm<sup>2</sup>/Vs. Notably,  $\mu_{FE}$  reaches a peak value when t<sub>ITO</sub> is 9 nm. Moreover, V<sub>on</sub> and SS present a negative and a positive correlation with t<sub>ITO</sub>, and significant degeneration of V<sub>on</sub> and SS occurs as t<sub>ITO</sub> increases to 12 and 15 nm, which results from large number of free electrons and higher sheet trap density in the channel layer [18,19]. Consequently, the ITO TFTs with 9-nm ITO active layer show the best electrical properties, such as a  $\mu_{FE}$  of 37.69 cm<sup>2</sup>/Vs, a V<sub>on</sub> of -2.3 V, and a SS of 167.49 mV/decade.

**Figure 5.** (a) Transfer curves of ITO TFTs.  $V_D = 0.1$  V. (b) Electrical parameters of ITO TFTs, including  $\mu_{FE}$ ,  $V_{on}$ , and SS.

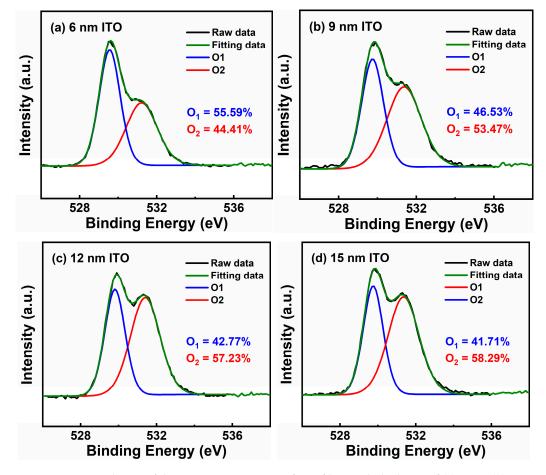

In order to deeply understand the physical mechanism behind the electrical performances of ITO TFTs, we characterized the ITO films with different thickness by XPS, as shown in Figure 6. The binding energy (BE) was calibrated by the standard C 1 s line at 284.80 eV [20]. The O 1 s peak is deconvoluted into two components: O<sub>1</sub> peak at around 529.7 eV and O<sub>2</sub> peak at around 531.3 eV, which can be regarded as metal–oxygen lattice and oxygen defects (oxygen vacancies and chemisorbed oxygen element), respectively [21]. Here, the ratio of oxygen defects is defined as the peak area ratio of O<sub>2/</sub>(O<sub>1</sub> + O<sub>2</sub>) and is positively correlated with t<sub>ITO</sub>. The oxygen defects can serve as interface traps; therefore, the SS is deteriorated with increasing  $t_{ITO}$  due to the increase of oxygen defects [22,23]. It is known that the content of oxygen vacancies, which normally acts as a shallow donor in oxide semiconductor, directly affects the carrier concentration of ITO films [1]. Consequently, the V<sub>on</sub> negatively shifts with increasing  $t_{ITO}$  and the  $\mu_{FE}$  increases with  $t_{ITO}$  increasing from 6 to 9 nm. However, similar to other impurity dopants, more oxygen defects can induce more ionized impurity scattering, which possibly results in the degradation of  $\mu_{FE}$ with  $t_{ITO}$  increasing from 9 to 15 nm [24].

**Figure 6.** Deconvolution of the O 1 s XPS spectrum of ITO films with thickness of (**a**) 6 nm, (**b**) 9 nm, (**c**) 12 nm, and (**d**) 15 nm.

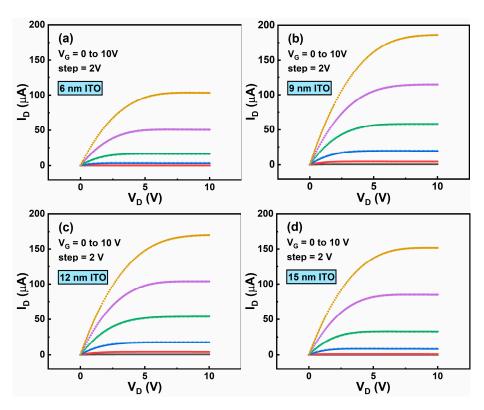

Drain current–drain voltage ( $I_D$ - $V_D$ ) curves of the ITO TFTs are measured, as shown in Figure 7a–d. All the  $I_D$ – $V_D$  curves show apparent linear and saturation region. As  $t_{ITO}$  increases from 6 to 15 nm, the saturation current increases first and then decreases, and the maximum value of 184  $\mu$ A is observed when  $t_{ITO}$  is 9 nm. Additionally, there is no obvious current crowding phenomenon for all the ITO TFTs, indicating good Ohmic contact between ITO channel layer and Al source/drain electrodes [25].

Figure 7. Output characteristics of ITO TFTs with t<sub>ITO</sub> of (a) 6 nm, (b) 9 nm, (c) 12 nm, and (d) 15 nm.

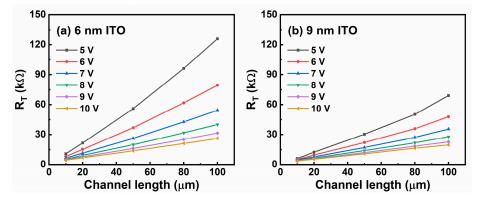

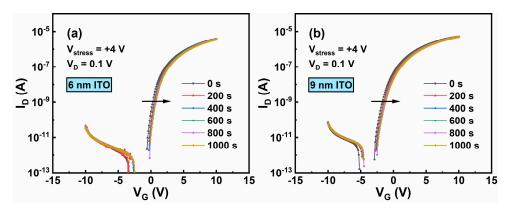

In order to comprehensively analyze contact property between ITO channel layer and Al source/drain electrode, we extract contact resistance ( $R_C$ ) based on transfer line method (TLM). Total resistance ( $R_T$ ) of the TFTs at on-state is expressed as  $R_T = R_{ch}L + 2R_C$ , where  $R_{ch}$  and L represent channel resistance per unit length and channel length, respectively [26].  $R_T$  versus L at different  $V_G$  for the ITO TFTs are shown in Figure 8a–d. By applying linear fitting, we obtain  $R_{ch}$  and  $R_C$  of the ITO TFTs, as shown in Figure 8e,f. Significantly, both  $R_{ch}$  and  $R_C$  present a negative correlation with  $t_{ITO}$ , which attributes to the increasing amount of conductive electrons in the ITO channel layers. Thereby, contact property can be enhanced by increasing  $t_{ITO}$ .

Figure 8. Cont.

**Figure 8.** Total resistance ( $R_T$ ) of ITO TFTs with  $t_{TTO}$  of (**a**) 6 nm, (**b**) 9 nm, (**c**) 12 nm, and (**d**) 15 nm. (**e**)  $R_{ch}$  and (**f**)  $R_C$  as a function of  $t_{TTO}$ .

In the aspect of contact property, we found that increasing  $t_{ITO}$  plays a role in enhancing contact property of the ITO TFTs. Commonly, a preferable contact property is desirable for high-performance metal–oxide TFTs. However, we verify that  $V_{on}$  and SS dramatically degrade when  $t_{ITO}$  increases to 12 and 15 nm (Figure 5b).  $\mu_{FE}$  and saturation current achieve the maximum value when  $t_{ITO}$  is 9 nm. That is to say, an optimal  $t_{ITO}$  is 9 nm in this work.

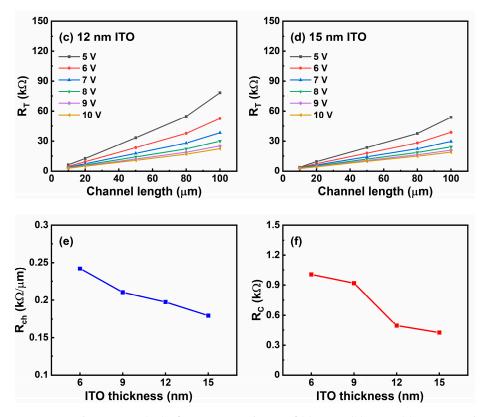

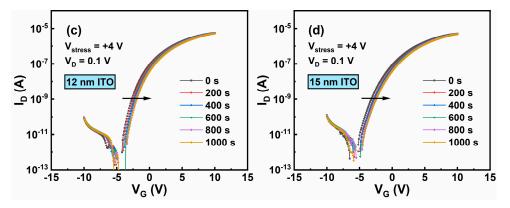

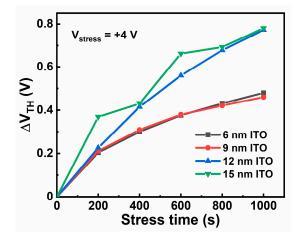

Finally, PBS stability of the ITO TFTs are measured, as shown in Figure 9a–d. Stress conditions are as follow: the stress voltage applied on the gate electrode is +4 V with the source and drain electrodes grounded, and the stress duration is 1000 s. Figure 10 presents  $\Delta V_{TH}$  of the ITO TFTs with different t<sub>ITO</sub> under PBS at different stress times. In general, the devices show improved stability under PBS with reducing t<sub>ITO</sub>, which is consistent with the previously reported results [27–29]. One possible mechanism related to PBS is the oxygen vacancy model [30]. As shown in Figure 6, for ITO TFT with a larger t<sub>ITO</sub>, there are more oxygen vacancy defects, causing a larger positive  $\Delta V_{TH}$ .

Figure 9. Cont.

**Figure 9.** PBS ( $V_G = +4 V$ ) of ITO TFTs with  $t_{ITO}$  of (**a**) 6 nm, (**b**) 9 nm, (**c**) 12 nm, and (**d**) 15 nm.

**Figure 10.**  $\Delta V_{TH}$  for the ITO TFTs with different t<sub>ITO</sub> under PBS at different stress times.

### 4. Conclusions

In conclusion, high-performance, robust ITO TFTs are fabricated at a maximum process temperature of 100 °C. We investigate the effects of  $t_{\rm ITO}$  on the electrical characteristics and PBS stability of ITO TFTs with  $t_{\rm ITO}$  of 6, 9, 12, and 15 nm. We found that content of oxygen defects positively correlates with tITO, leading to increase of both trap states as well as carrier concentration, and synthetically determining electrical properties of the ITO TFTs. Interestingly, the devices with a 9-nm ITO thickness show the best performance with a large  $\mu_{\rm FE}$  of 37.69 cm<sup>2</sup>/Vs, a high I<sub>on</sub>/I<sub>off</sub> over 10<sup>7</sup>, a reasonable V<sub>on</sub> of -2.3 V, and a steep SS of 167.49 mV/decade. Moreover, the device exhibits preferable stability under PBS ( $\Delta V_{\rm TH} = 0.46$  V). Overall, our ITO TFTs show great potential in next-generation displays.

**Author Contributions:** Q.L. and J.D. conceived and planned the experiments; Q.L. carried out the experiments; formal analysis, Q.L. and J.D.; writing—original draft, Q.L.; supervision, D.H. and Y.W.; resources, J.D., D.H. and Y.W. All authors have read and agreed to the published version of the manuscript.

Funding: This research was funded by the National Natural Science Foundation of China (Grant 62004003).

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

**Data Availability Statement:** The data that support the findings of this study are available from the corresponding author upon reasonable request.

Conflicts of Interest: The authors declare no conflict of interest.

### References

- Kamiya, T.; Nomura, K.; Hosono, H. Origins of High Mobility and Low Operation Voltage of Amorphous Oxide TFTs: Electronic Structure, Electron Transport, Defects and Doping. J. Disp. Technol. 2009, 5, 273–288. [CrossRef]

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide Semiconductor Thin-film transistors: A Review of Recent Advances. *Adv. Mater.* 2012, 24, 2945–2986. [CrossRef] [PubMed]

- Park, J.S.; Maeng, W.J.; Kim, H.S.; Park, J.S. Review of Recent Developments in Amorphous Oxide Semiconductor Thin-film Transistor Devices. *Thin Solid Film.* 2012, 520, 1679–1693. [CrossRef]

- Shi, J.; Zhang, J.; Yang, L.; Qu, M.; Qi, D.C.; Zhang, K.H.L. Wide Bandgap Oxide Semiconductors: From Materials Physics to Optoelectronic Devices. *Adv. Mater.* 2021, e2006230. [CrossRef] [PubMed]

- Goh, Y.; Ahn, J.; Lee, J.R.; Park, W.W.; Park, S.H.K.; Jeon, S. Efficient Suppression of Defects and Charge Trapping in High Density In-Sn-Zn-O Thin Film Transistor Prepared using Microwave-Assisted Sputter. ACS Appl. Mater. Interfaces 2017, 9, 36962–36970. [CrossRef]

- Kang, Y.; Lee, W.; Kim, J.; Keum, K.; Kang, S.H.; Jo, J.W.; Park, S.K.; Kim, Y.H. Effects of Crystalline Structure of IGZO Thin Films on the Electrical and Photo-stability of Metal-oxide Thin-film Transistors. *Mater. Res. Bull.* 2021, 139, 111252. [CrossRef]

- Kim, H.; Horwitz, J.S.; Kushto, G.; Piqué, A.; Kafafi, Z.H.; Gilmore, C.M.; Chrisey, D.B. Effect of Film Thickness on the Properties of Indium Tin Oxide Thin Films. J. Appl. Phys. 2000, 88, 6021–6025. [CrossRef]

- Granqvist, C.G.; Hultaker, A. Transparent and Conducting ITO Films: New Developments and Applications. *Thin Solid Film.* 2002, 411, 1–5. [CrossRef]

- 9. Wang, Y.; Wang, Z.; Huang, K.; Liang, X.; Liu, C.; Chen, C.; Liu, C. Solution-processed ITO Thin-film Transistors With Doping of Gallium Oxide Show High On-off Ratios and Work at 1 mV Drain Voltage. *Appl. Phys. Lett.* **2020**, *116*, 141604. [CrossRef]

- Li, S.; Tian, M.; Gao, Q.; Wang, M.; Li, T.; Hu, Q.; Li, X.; Wu, Y. Nanometre-thin Indium Tin Oxide for Advanced High-performance Electronics. *Nat. Mater.* 2019, 18, 1091–1097. [CrossRef] [PubMed]

- Park, S.Y.; Ji, K.H.; Jung, H.Y.; Kim, J.-H.; Choi, R.; Son, K.S.; Ryu, M.K.; Lee, S.; Jeong, J.K. Improvement in the Device Performance of Tin-doped Indium Oxide Transistor by Oxygen High Pressure Annealing at 150 °C. *Appl. Phys. Lett.* 2020, 100, 162108. [CrossRef]

- 12. Liang, K.; Li, D.; Ren, H.; Zhao, M.; Wang, H.; Ding, M.; Xu, G.; Zhao, X.; Long, S.; Zhu, S.; et al. Fully Printed High-Performance n-Type Metal Oxide Thin-Film Transistors Utilizing Coffee-Ring Effect. *Nanomicro Lett.* **2021**, *13*, 164. [CrossRef]

- Kim, D.H.; Cha, H.S.; Jeong, H.S.; Hwang, S.H.; Kwon, H.-I. Effects of Active Layer Thickness on the Electrical Characteristics and Stability of High-Mobility Amorphous Indium–Gallium–Tin Oxide Thin-Film Transistors. *Electronics* 2021, 10, 1295. [CrossRef]

- Choi, K.H.; Kim, H.K. Correlation between Ti Source/drain Contact and Performance of InGaZnO-based Thin Film Transistors. *Appl. Phys. Lett.* 2013, 102, 052103. [CrossRef]

- Lee, J.Y.; Lee, S.Y. Investigation on Hump Mechanism in Amorphous SiZnSnO Thin-Film Transistor Depending on Si Concentration. *Phys. Status Solidi A* 2020, 217, 1900953. [CrossRef]

- 16. Teng, T.; Hu, C.-F.; Qu, X.-P.; Wang, M. Investigation of the Anomalous Hump Phenomenon in Amorphous InGaZnO Thin-film Transistors. *Solid State Electron.* **2020**, *170*, 107814. [CrossRef]

- 17. Li, H.; Han, D.; Dong, J.; Yi, Z.; Zhou, X.; Zhang, S.; Zhang, X.; Wang, Y. Enhanced Performance of Atomic Layer Deposited Thin-Film Transistors With High-Quality ZnO/Al<sub>2</sub>O<sub>3</sub> Interface. *IEEE Trans. Electron. Devices* **2020**, *67*, 518–523. [CrossRef]

- 18. Barquinha, P.; Pimentel, A.; Marques, A.; Pereira, L.; Martins, R.; Fortunato, E. Influence of the semiconductor thickness on the electrical properties of transparent TFTs based on indium zinc oxide. *J. Non-Cryst. Solids* **2006**, 352, 1749–1752. [CrossRef]

- 19. Park, H.-W.; Park, K.; Kwon, J.-Y.; Choi, D.; Chung, K.-B. Effect of active layer thickness on device performance of tungsten-doped InZnO thin-film transistor. *IEEE Trans. Electron. Dev.* **2016**, *64*, 159–163. [CrossRef]

- 20. Barreca, D.; Garon, S.; Tondello, E.; Zanella, P. SnO<sub>2</sub> Nanocrystalline Thin Films by XPS. Surf. Sci. Spectra 2000, 7, 81–85. [CrossRef]

- Li, Y.; Yao, R.; Wang, H.H.; Wu, X.M.; Wu, J.Z.; Wu, X.H.; Qin, W. Enhanced Performance in Al-doped ZnO Based Transparent Flexible Transparent Thin-film Transistors Due to Oxygen Vacancy in ZnO Film With Zn-Al-O Interfaces Fabricated by Atomic Layer Deposition. ACS Appl. Mater. Interfaces 2017, 9, 11711–11720. [CrossRef]

- 22. Kwon, S.; Bang, S.; Lee, S.; Jeon, S.; Jeong, W.; Kim, H.; Gong, S.C.; Chang, H.J.; Park, H.; Jeon, H. Characteristics of the ZnO Thin Film Transistor by Atomic Layer Deposition at Various Temperatures. *Semicond. Sci. Technol.* **2009**, *24*, 035015. [CrossRef]

- Wang, Y.H.; Ma, Q.; Zheng, L.L.; Liu, W.J.; Ding, S.J.; Lu, H.L.; Zhang, D.W. Performance Improvement of Atomic Layer-deposited ZnO/Al<sub>2</sub>O<sub>3</sub> Thin-film Transistors by Low-temperature Annealing in Air. *IEEE Trans. Electron. Devices* 2016, 63, 1893–1898. [CrossRef]

- 24. Liu, L.C.; Chen, J.S.; Jeng, J.S. Ambient Constancy of Passivation-Free Ultra-Thin Zinc Tin Oxide Thin Film Transistor. *ECS Solid State Lett.* **2015**, *4*, Q59–Q62. [CrossRef]

- 25. Jeon, S.R.; Song, Y.H.; Jang, H.J.; Yang, G.M.; Hwang, S.W.; Son, S.J. Lateral Current Spreading in GaN-based Light-emitting Diodes Utilizing Tunnel Contact Junctions. *Appl. Phys. Lett.* **2001**, *78*, 3265–3267. [CrossRef]

- Campbell, J.P.; Cheung, K.P.; Suehle, J.S.; Oates, A. A Simple Series Resistance Extraction Methodology for Advanced CMOS Devices. *IEEE Electron. Device Lett.* 2011, 32, 1047–1049. [CrossRef]

- 27. Yang, Z.; Yang, J.W.; Meng, T.; Qu, M.Y.; Zhang, Q. Influence of Channel Layer Thickness on the Stability of Amorphous Indium Zinc Oxide Thin Film Transistors. *Mater. Lett.* **2016**, *166*, *46*–50. [CrossRef]

- 28. Ahn, C.H.; Yun, M.G.; Lee, S.Y.; Cho, H.K. Enhancement of Electrical Stability in Oxide Thin-film Transistors Using Multilayer Channels Grown by Atomic Layer Deposition. *IEEE Trans. Electron. Devices* **2014**, *60*, 73–78. [CrossRef]

- 29. Li, J.; Ding, X.W.; Zhang, J.H.; Zhang, H.; Jiang, X.Y.; Zhang, Z.L. Improving Electrical Performance and Bias Stability of HfInZnO-TFT With Optimizing the Channel Thickness. *AIP Adv.* **2013**, *3*, 102132. [CrossRef]

- 30. Zhou, X.B.; Han, D.D.; Dong, J.C.; Li, H.J.; Yi, Z.; Zhang, X.; Wang, Y. The Effects of Post Annealing Process on the Electrical Performance and Stability of Al-Zn-O Thin-Film Transistors. *IEEE Electron. Device Lett.* **2020**, *41*, 569–572. [CrossRef]