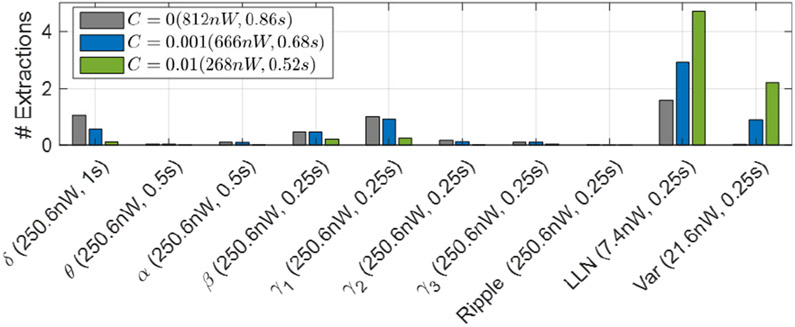

Fig. 11:

The number of extracted features in DVTE for different regularization coefficients. With greater C, the cost-aware model tends to use hardware-friendly features (e.g., LLN, Var). Features with longer windows (δ, θ, α) are also penalized in the cost-aware model. The power cost and latency for each C are shown in the legend, while the X-axis shows individual feature costs. For C = 0.01, we achieved an average power cost of 268nW and latency of 0.52s.