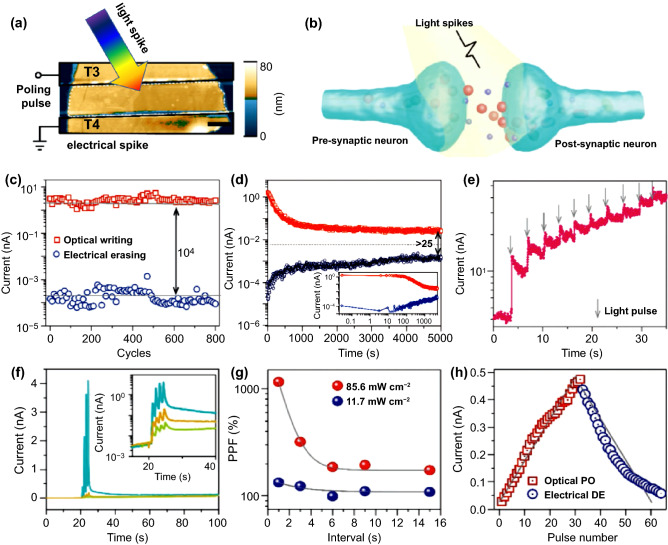

Fig. 10.

Lateral two-terminal electrical synaptic device demonstration using in-plane ferroelectric SnS thin films. a Illustration of fabricated Pt/SnS/Pt lateral device. b EPSC results triggered by 3 V and 20 ms pulse width. The partially polarized ferroelectric domains retained the current. c PPF emulation of the fabricated device. d LTP/LTD curves using identical pulses of 3, 4, and 5 V (conductance states; 50 cycles). e LTP/LTD curves using voltage incremental pulses (conductance states; 100 cycles). f STDP learning rule demonstration. g Artificial neural network simulation via MNIST database. h The recognition accuracy of i) ideal (94%), ii) identical pulses (~ 80%), and iii) variable pulses (~ 93.1%).

Reproduced with permission from Ref. [179]. Copyright 2020, ACS Nano (Color figure online)