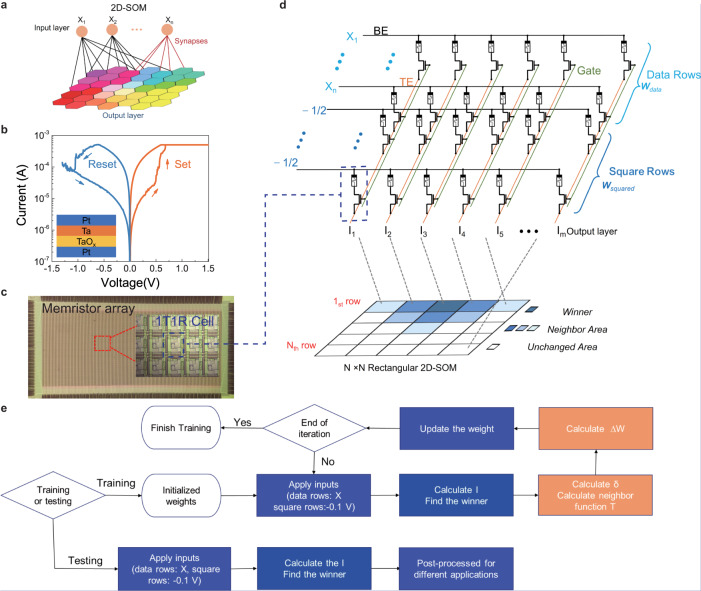

Fig. 1. The SOM concept and its implementation with memristor crossbar arrays.

a Schematic of a 2D SOM that is composed of a unidimensional input layer and a bidimensional output layer. Each node in the input layer is connected to all nodes in the output layer through the synapses. The output nodes can communicate with their neighborhoods to form a 2D-planer topological map. b Typical I–V characteristic of a memristive device used as synapses in the SOM. The device size is 2 µm by 2 µm, and the material stack is shown in the inset. c Image of a 128 × 64 1T1R memristor array (Scale bar, 500 µm). Inset shows a close-up image for part of the chip marked by a red box, and the blue dashed box shows one 1T1R cell (scale bar, 10 µm). d The implementation of the 2D SOM with the 1T1R memristor array. The synaptic weights are stored as the memristor conductance in data rows. The squared values are stored in the square rows. The top electrode (TE), bottom electrode (BE), and gate line are connected to the off-chip peripheral circuits for precise weight updating. The Euclidean distance between the input vector and weight vector is calculated in one reading process. The output currents in different columns represent the signal applied to different output nodes. The intrinsic topology of the nodes in the memristor array is a 1D line. And 2D topology of the SOM is artificial defined. For example, the output nodes of 1st to the 5th columns in the memristor array act as the nodes in the first row of 2D 5 × 5 output layer, and the last five columns in the memristor array act as the last row of the 2D 5 × 5 SOM. The node with the largest current is the winner, whereas the nodes close to the winner (in 2D space) are the neighborhood. e Flow chart of the training and testing processes. Steps in blue boxes are implemented in hardware in this work, while those in orange boxes are achieved in a CPU.