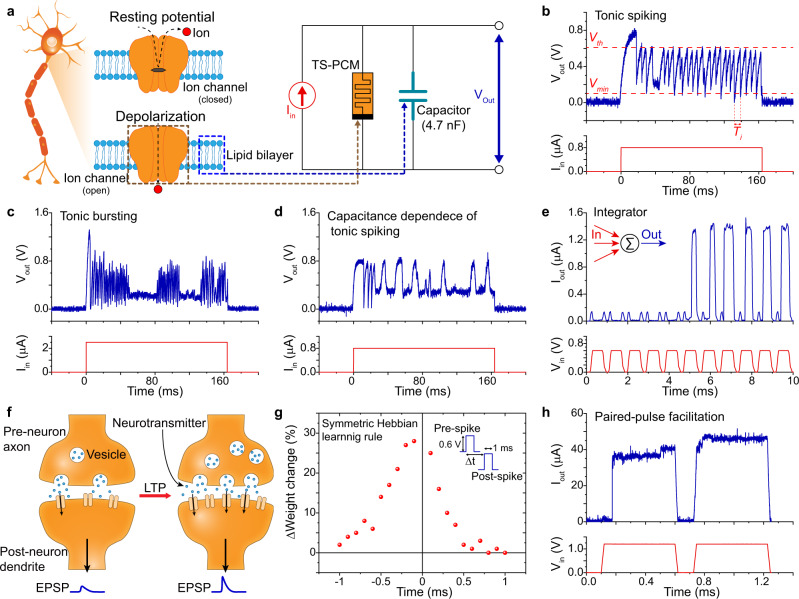

Fig. 3. Emulation of spiking behavior and synaptic plasticity by TS-PCM.

a Illustration of neuronal membrane structure (left) and corresponding circuit representation by TS-PCM (right). TS-PCM and the parallel capacitor are equivalent to a voltage-gated ion channel and lipid bilayer, respectively. b Tonic spiking behavior of TS-PCM using a 4.72 nF capacitor. The voltage spikes are generated by the charging and discharging of the capacitor with threshold switching of TS-PCM. Vth and Vmin are measured to be 0.61 V and 0.1 V, respectively. Ti is a period of i th voltage spike from total n spikes, where average spike period . c Tonic bursting of TS-PCM showing rapid voltage spiking with quiescent periods. d Tonic spiking of TS-PCM with 5.61 nF capacitor. The firing frequency shows clear dependency on the capacitance. e Emulation of LIF behavior by TS-PCM. Consecutive input signals are integrated with continuous decay, which results in the generation of current spikes for the sixth input signal with a sufficiently short time interval. f Schematic diagram of synaptic plasticity showing before and after the LTP of synapse. Synaptic vesicles in the pre-neuron and dendritic receptors in the post-neuron increase after the LTP process, leading to enhanced connection strength and EPSP output. g Emulation of STDP using TS-PCM presenting a symmetric Hebbian learning rule. The time interval between pre-spike and post-spike determines the amount of synaptic weight change. Same pulse conditions are used for pre- and post-spike, which are 0.6 V amplitude and 1 ms pulse width. The device was reset between each measurement. h Short-term synaptic plasticity of TS-PCM. Paired-pulse facilitation is emulated based on the volatility of the bottom TS layer. Repetitive stimulations induce temporary increment of the filament radius, leading to an increase of current level for same voltage pulses.