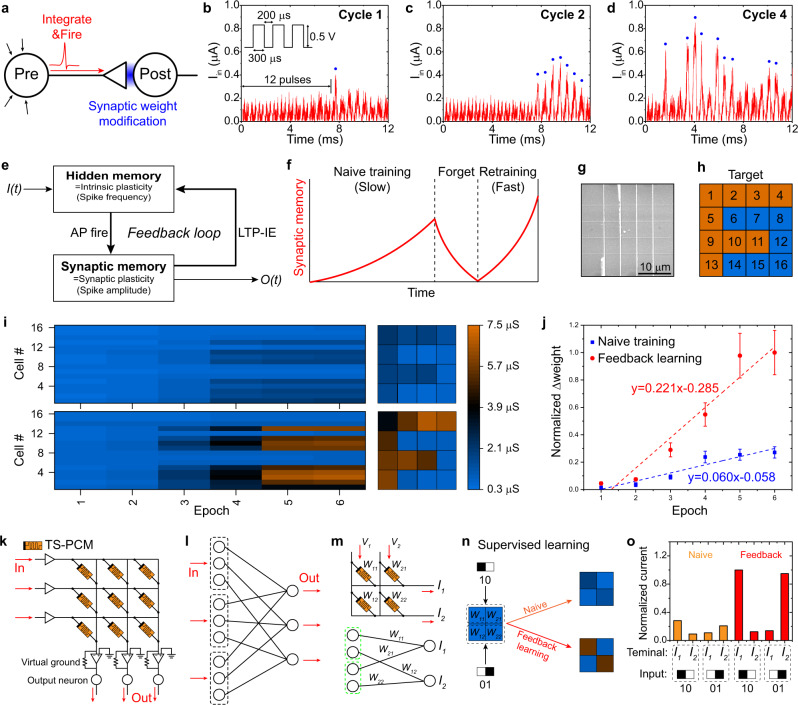

Fig. 5. Concomitant plasticity and positive feedback learning in TS-PCM.

a Illustration of neuron-synapse pair structure. Input signals are integrated to fire an AP spike modulating the synaptic strength. b–d Emulation of basic learning process using TS-PCM with the LIF model. Each cycle is consisted of 20 voltage pulses. For a repetitive input pulse trains, the number of current spikes increases along with the maximum current value, indicating the concomitant implementation of synaptic and intrinsic plasticity. Note that small peaks around 0.2 μA are the displacement current caused by the voltage gradient, which do not represent actual movement of charges across the cell. e Schematic diagram of positive feedback learning loop based on the concomitant neuroplasticity and LTP-IE. Intrinsic plasticity and synaptic plasticity construct hidden memory and synaptic (regular) memory states, respectively. f Illustration of naive training and retraining, presenting a clear difference in the rate of acquisition. Hidden memory is developed during naive training and remains after the forget process, promoting reinforcement of the retraining process. g SEM image of crossbar structured 4 × 4 TS-PCM array. h 4 × 4 pixel image of “F” used in pattern memorization task in i and j. i Resistance-based color map of naive training (upper panel) and feedback learning (lower panel) for total 6 training epochs. The right panels show the resistance states of the TS-PCM array after the training process. j Normalized synaptic weight updates for two different training schemes. Each data point indicates the mean value and the error bars indicate the standard deviation. k Schematic of TS-PCM array consists of TS-PCM, post-neuron device, and peripheral circuitry. l Network structure of TS-PCM array indicating that each word line pre-neurons are subdivided according to the number of bit lines. m Schematic and network structure of 2 × 2 TS-PCM array. n Conductance level before and after the supervised training process. Two types of 2 × 1 binary patterns were trained in the array with naive and feedback training schemes. o pattern classification result in TS-PCM array. Each pattern can be recognized by the output word line current level.