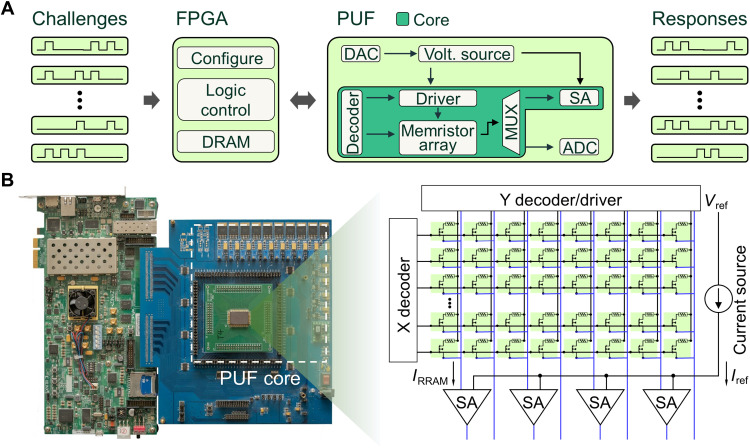

Fig. 2. Memristor-based PUF system.

(A) The architecture of the memristor-based PUF system. The FPGA communicates with the customized PCB through the FPGA Mezzanine Card (FMC) interface. The FPGA receives instructions (e.g., generating, concealing, and reading the PUF) with a specific challenge from the PC and sends control signals to the PUF chip, onboard digital-to-analog converter (DAC), and ADC. The readout results from the memristor array are sent back to the FPGA for postprocessing and then output as the response to the challenge. (B) Photograph of the PUF system. ZC706 FPGA evaluation board from Xilinx is used. The chip contains an 8-kb memristor array and supports parallel operation for up to eight memristor devices.