#### **1** Supplementary Information for

### 2 Ultrashort vertical-channel MoS<sub>2</sub> transistor

## **using a self-aligned contact**

- 4 Liting Liu<sup>1</sup>, Yang Chen<sup>1</sup>, Long Chen<sup>1</sup>, Biao Xie<sup>1</sup>, Guoli Li<sup>1,\*</sup>, Lingan Kong<sup>1</sup>,

- 5 Quanyang Tao<sup>1</sup>, Zhiwei Li<sup>1</sup>, Xiaokun Yang<sup>1</sup>, Zheyi Lu<sup>1</sup>, Likuan Ma<sup>1</sup>, Donglin Lu<sup>1</sup>,

- 6 Xiangdong Yang<sup>2</sup>, Yuan Liu<sup>1,\*</sup>

- <sup>7</sup> <sup>1</sup>Key Laboratory for Micro-Nano Optoelectronic Devices of Ministry of Education,

- 8 School of Physics and Electronics, Hunan University, Changsha 410082, China.

- 9 <sup>2</sup>Institute of Micro/Nano Materials and Devices, Ningbo University of Technology,

- 10 Ningbo, 315211, China.

- 11 \*e-mail: yuanliuhnu@hnu.edu.cn; liguoli\_lily@hnu.edu.cn

- 12

- 13

- 14

- 15

- 16

- 17

- 18

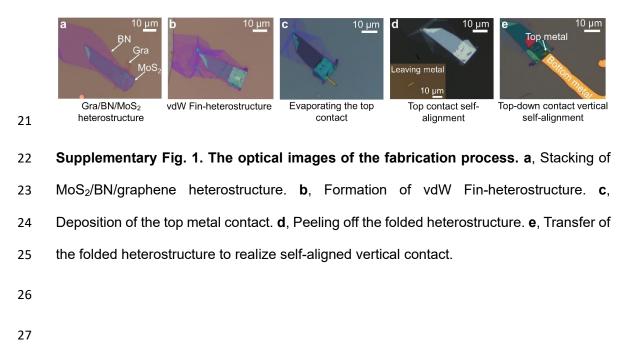

- 20

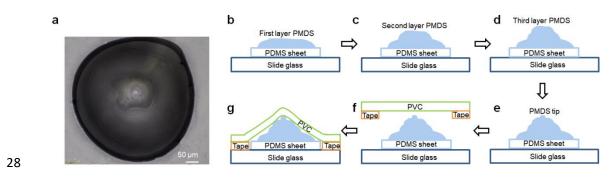

#### 29 Supplementary Fig. 2. The characterization and fabrication processes of PDMS tip.

a, The image of the bumped PDMS stamp which used to fold the heterostructure. **b–g**, The fabrication process of the PDMS tip, comprising six essential steps: (**b**) dropping first layer PDMS liquid using tungsten needle with diameter of 2 mm, (**c**) dropping the second layer PDMS liquid using the tungsten needle with diameter of 600  $\mu$ m, (**d**) dropping the third layer PDMS liquid using the tungsten needle with diameter of 50  $\mu$ m, (**e**) dropping the fourth layer PDMS liquid using the tungsten needle with diameter of 400 nm, (**f**, **g**) coating the PVC layer on top of PDMS tip to enhance the adhesion force.

39

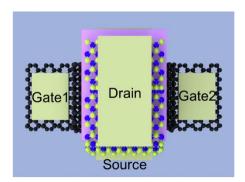

# 40 Supplementary Fig. 3. The top view schematic of the self-alignment device. During

41 the folding process, the actual graphene gate extends to both sides of the folded

- 42 heterostructure, forming two tails outside BN for gate contact (Gate 1 and Gate 2).

- 43

44

45

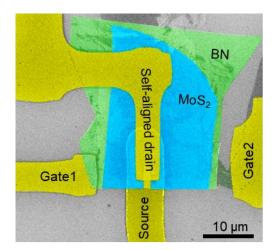

- 46 Supplementary Fig. 4. False-colored SEM image of the device. Blue color represents

- 47 MoS<sub>2</sub>, green color represents BN and yellow color represents the electrodes.

48

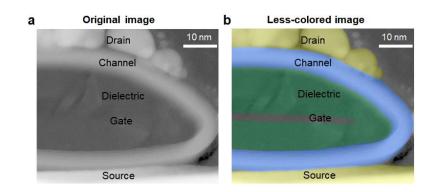

#### 51 Supplementary Fig. 5. TEM image of self-aligned device. a, Original TEM image of the

- 52 self-aligned device. **b**, Corresponding TEM image with less false-coloring.

- 53

54

55

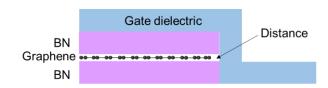

56 Supplementary Fig. 6. Graphene side gate structure (BN/graphene/BN) through 57 conventional layer-by-layer stacking processes. Within this process, it is hard to 58 precisely align the graphene with the edge of BN, resulting in large distance between the 59 graphene gate and the BN edge.

60

61

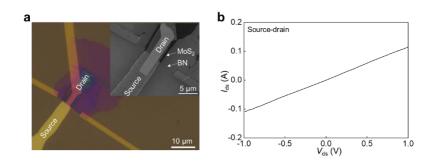

# Supplementary Fig. 7. Characterization of the tilted angle deposition device. a, The optical image and corresponding SEM image of the folded heterostructure device using tilted angle deposition for source-drain contact. b, The electrical characteristic of corresponding device, showing the short circuit between the source and drain.

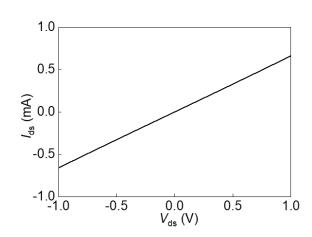

#### 70 Supplementary Fig. 8. The conductivity of graphene gate. The two terminal device

#### exhibits low resistance, demonstrating enough conductivity as a gate electrode.

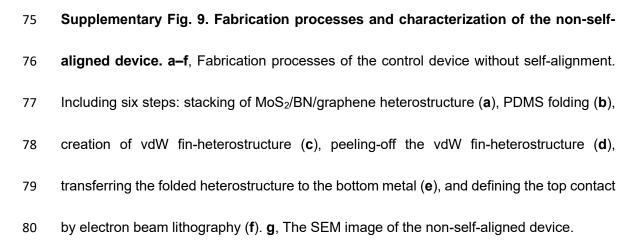

84 Supplementary Fig. 10. Stability measurement of a typical self-aligned contact

device. a, b, Transfer characteristics of an initial self-aligned contact device in both positive

(a) and negative (b) bias regions. c, d, Transfer characteristics of a self-aligned contact

device which storing at ambient condition for three months.

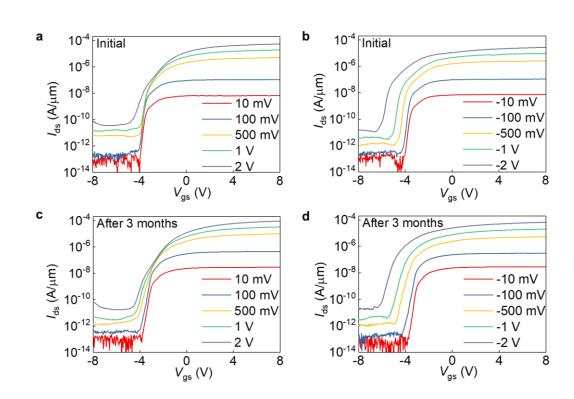

#### 91 Supplementary Fig. 11. The simulated electron density distribution of vertical device.

**a**, The electron density distribution of the  $MoS_2$  channel at off-state. **b**, The electron density

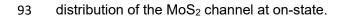

Supplementary Fig. 12. The electrical performance of self-aligned devices as a function of channel length. **a**, The on-state current density of the self-aligned devices with the relationship of channel length. **b**, The on-off ratio of the self-aligned devices with the relationship of channel length. **c**, The threshold voltage of the self-aligned devices with the relationship of channel length. **d**, The subthreshold swing of the self-aligned devices with the relationship of channel length. **d**, The subthreshold swing of the self-aligned devices with the relationship of channel length. The channel length ( $L_{ch}$ ) here is extracted by calculating the distance between edges of source and drain along the curvature.

104

105

106

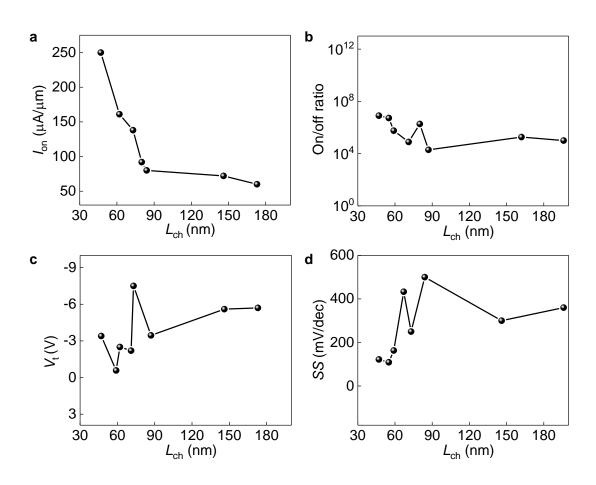

Supplementary Fig.13. Self-aligned process for thinner heterostructure. a, Optical

image of the thinner heterostructure (~25 nm thick after folding) with top contact deposited.

b, Optical image of the structure peeling from substrate, where part of the flake is left at

the original substrate owing to the similar thickness of the heterostructure and the top

contact metal.

112

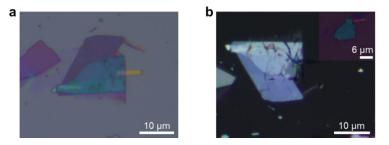

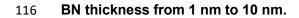

115 Supplementary Fig.14. The simulation results of gate leakage currents with different

117

118

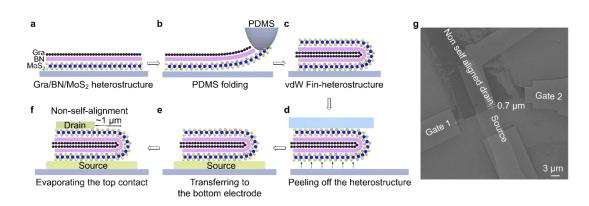

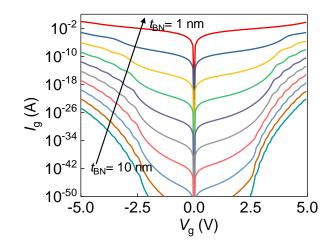

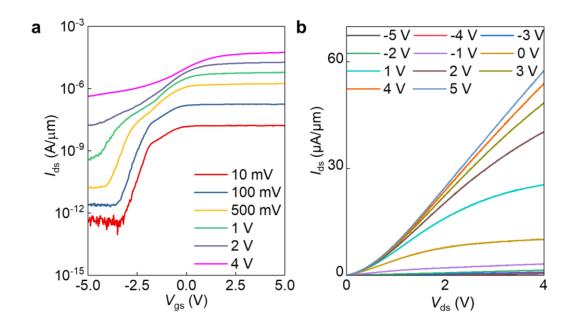

Supplementary Fig. 15. Self-aligned device operated on the SiO<sub>2</sub>. a,  $I_{ds}-V_{gs}$  transfer characteristics of a self-aligned device on SiO<sub>2</sub>. b,  $I_{ds}-V_{ds}$  output characteristics of a selfaligned device on SiO<sub>2</sub>. The thickness of MoS<sub>2</sub> is 14 layers, channel length is around 80 nm.