## Large Area Growth and Electrical Properties of p-Type WSe<sub>2</sub> Atomic Layers

Hailong Zhou<sup>†</sup>, Chen Wang<sup>†</sup>, Jonathan C. Shaw<sup>†</sup>, Rui Cheng, Yu Chen, Xiaoqing Huang, Yuan Liu, Nathan O. Weiss, Zhaoyang Lin, Yu Huang, and Xiangfeng Duan\*

(† the authors contribute equally to this work)

## **Experimental Section**

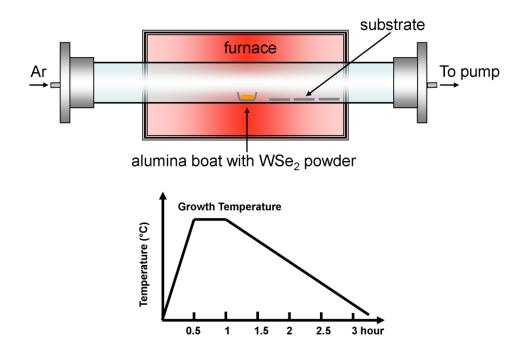

WSe<sub>2</sub> growth: To synthesize the layered WS<sub>2</sub> flakes, the 0.2 g WSe<sub>2</sub> powder (Alfa Aesar, 13084) was added into an alumina boat as precursor. The blank SiO<sub>2</sub>/Si substrates (1 cm by 5 cm) loaded into a home-built vapour deposition system in a horizontal tube furnace (Lindberg/Blue M) with 1-inch quartz tube (Figure S1 in the Supporting information). The system was pumped down to a vacuum of 10 mTorr in 10 min, and re-filled with 150 sccm of ultra-high purity argon gas (Airgas, ~ 99.9999%) then heated to desired growth temperature within 30 min. After that, the growth kept at the designed temperature for 30 min, and then terminated by shutoff the power of the furnace. The sample was naturally cooled down to ambient temperature.

WSe<sub>2</sub> Transfer: The transfer of the WSe<sub>2</sub> films onto arbitrary substrates was performed by the wet-etching of the SiO<sub>2</sub> layer. The top side of the WSe<sub>2</sub>/SiO<sub>2</sub>/Si surface was spin-coated with PMMA (495 PMMA C2, MicroChem) and baked at 120  $^{\circ}$ C for 1 min. After that, the SiO<sub>2</sub> were etched away using buffered oxide etchant (5:1:8 of NH<sub>4</sub>F: HF:

deionized H<sub>2</sub>O), resulting in a free-standing PMMA/WSe<sub>2</sub> membrane floating on the surface of the etchant bath. The PMMA/WSe<sub>2</sub> film was washed with deionized (DI) H<sub>2</sub>O for several times, and then transferred onto a prepared substrate. After dried in the air, the PMMA was dissolved by acetone and the substrate was rinsed with isopropyl alcohol to yield a WSe<sub>2</sub> film on the substrate.

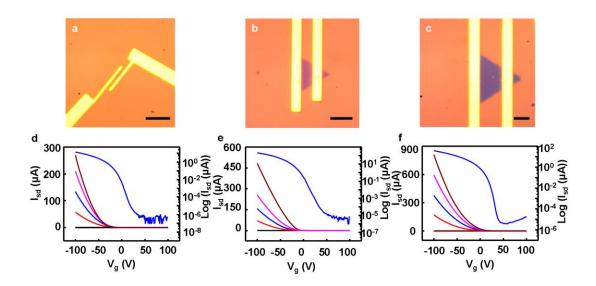

WSe<sub>2</sub> device fabrication: Single back-gated FETs were fabricated on the monolayer, bilayer, and few-layer WSe<sub>2</sub> on a silicon substrate with 300 nm SiO<sub>2</sub> substrates. E-beam lithography was employed to pattern the contact electrodes. The source/drain electrodes (Au: 100 nm) were deposited using e-beam evaporation. The back gate voltage was applied by using a Si back gate with SiO<sub>2</sub> as the dielectric.

Characterizations: The morphology and structure of the graphene were characterized with optical microscope (Olympus BX51), field emission scanning electron microscope (FESEM, JSM-6701F), high-resolution transmission electron microscopy (HRTEM, FEI Titan S/TEM at 300 kV), and Raman spectroscopy (Horiba, 514 nm laser wavelength, 50 × objective). Electrical transport properties of the samples were measured at room temperature in a Lakeshore probe station (Model PTT4) with a computer-controlled precision source/measure unit (Agilent B2902A.

**Figure S1.** Schematic illustration of the growth equipment and recipe. Up: The WSe<sub>2</sub> powders are placed in an alumina boat at the center of the quartz tube, and the clean SiO<sub>2</sub>/Si substrates designated for growth of WSe<sub>2</sub> atomic layers are leaved on the downstream side. Argon is continuously supplied through the reactor with designed flow rate. Down: temperature control curve of substrate during growth.

**Figure S2.** Electrical characteristics of the WSe<sub>2</sub> monodomains. Optical microscope image of (a) a monolayer WSe<sub>2</sub> transistor, (b) bilayer WSe<sub>2</sub> transistor, and (c) few-layer WSe<sub>2</sub> transistor, respectively.  $I_{sd}$ - $V_g$  transfer characteristics plotted in (d), (e), and (f) of the device shown in panels (a), (b), and (c) at  $V_{sd}$  = 0, 1, 2, 3 and 4 V, respectively. All scale bars are 5  $\mu$ m.