**Supplementary Information**

## Three-dimensional monolithic integration in flexible printed organic transistors

Kwon *et al*.

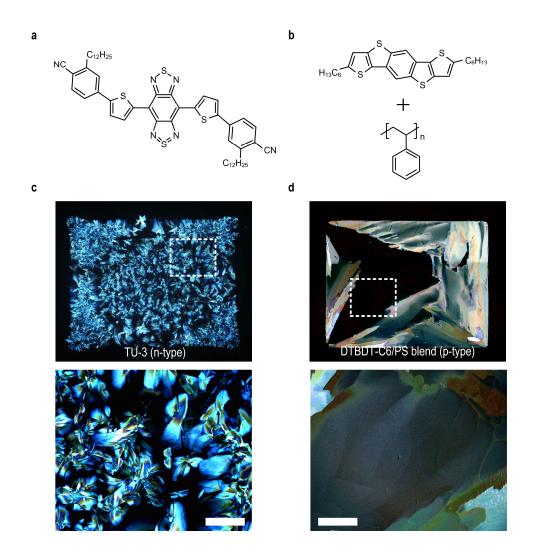

**Supplementary Figure 1** Molecular structures of complementary OSCs. **a** An n-type small molecule TU-3. **b** A p-type small molecule DTBDT-C<sub>6</sub> (top) blended with an insulating polymer PS (bottom). Polarized light microscopy of the printed complementary OSCs: **c** TU-3 and **d** DTBDT-C<sub>6</sub>/PS blend (the white dashed image areas are magnified, scale bars are 50  $\mu$ m).

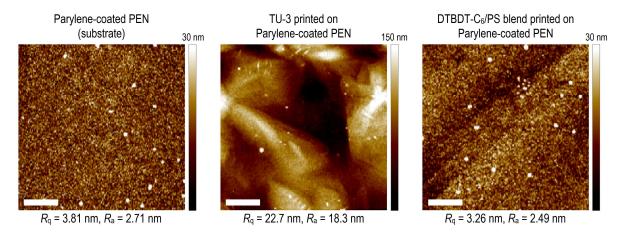

**Supplementary Figure 2** AFM topology images (scan area =  $50 \times 50 \ \mu m$ , scale bar length =  $10 \ \mu m$ ) of a Parylenecoated PEN substrate, a TU-3 layer and a DTBDT-C<sub>6</sub>/PS blend layer printed on the substrate ( $R_q$ : root-mean-square roughness,  $R_a$ : average roughness).

| Transistor<br>Floor | #  | Layer<br>Index | Layer Description                                             | Material                  | Process          | Annealing                                                |  |

|---------------------|----|----------------|---------------------------------------------------------------|---------------------------|------------------|----------------------------------------------------------|--|

|                     | 1  | SUB            | Flexible substrate                                            | PEN                       | -                | -                                                        |  |

| -                   | 2  | BASE           | Basement                                                      | Parylene diX-SR           | CVD              | -                                                        |  |

| 1F                  | 3  | M1             | Metal routing / bottom-gate electrode                         | NPS-JL                    | IJP <sup>a</sup> | 120 °C for 30 min in air                                 |  |

|                     | 4  | D1             | Bottom-gate dielectric (180 nm)                               | Parylene diX-SR           | CVD              | -                                                        |  |

|                     | 5  | M2             | Metal routing / source and drain electrode                    | NPS-JL                    | IJP              | 120 °C for 30 min in air                                 |  |

|                     | 6  | BK1            | Hydrophobic bank for semiconductor patterning                 | AF1600                    | Dispensing       | 120 °C for 30 min in nitrogen                            |  |

|                     | 7  | SAM1           | Self-assembled monolayer (lowering the WF <sup>b</sup> of Ag) | 4-MBT                     | Dipping          | -                                                        |  |

|                     | 8  | OSC1           | Organic semiconductor (p-type)                                | TU-3                      | Dispensing       | 60 ℃ for 30 min in air,<br>120 ℃ for 30 min in nitrogen  |  |

|                     | 9  | D2             | Top-gate dielectric (180 nm)                                  | Parylene diX-SR           | CVD              | -                                                        |  |

| 1F/2F               | 10 | M3             | Metal routing / top-gate for 1F /<br>bottom-gate for 2F       | NPS-JL                    | IJP              | 120 °C for 30 min in air                                 |  |

| 2F                  | 11 | D3             | Bottom-gate dielectric (360 nm)                               | Parylene diX-SR           | CVD              | -                                                        |  |

|                     | 12 | M4             | Metal routing / source and drain electrode                    | NPS-JL                    | IJP              | 120 °C for 30 min in air                                 |  |

|                     | 13 | BK2            | Hydrophobic bank for semiconductor patterning                 | AF1600                    | Dispensing       | 120 °C for 30 min in nitrogen                            |  |

|                     | 14 | SAM2           | Self-assembled monolayer (increasing the WF of Ag)            | PFBT                      | Dipping          | -                                                        |  |

|                     | 15 | OSC2           | Organic semiconductor (p-type)                                | DTBDT-C <sub>6</sub> / PS | Dispensing       | Room temp. for 30 min in air                             |  |

|                     | 16 | D4             | Top-gate dielectric (360 nm)                                  | Parylene diX-SR           | CVD              | -                                                        |  |

| 2F/3F               | 17 | M5             | Metal routing / bottom-gate for 2F /<br>top-gate for 3F       | NPS-JL                    | IJP              | 120 °C for 30 min in air                                 |  |

| 3F                  | 18 | D5             | Bottom dielectric for 3F (180 nm)                             | Parylene diX-SR           | CVD              | -                                                        |  |

|                     | 19 | M6             | Metal routing / source and drain electrode                    | NPS-JL                    | IJP              | 120 °C for 30 min in air                                 |  |

|                     | 20 | BK3            | Hydrophobic bank for semiconductor patterning                 | AF1600                    | Dispensing       | 120 °C for 30 min in nitrogen                            |  |

|                     | 21 | SAM3           | Self-assembled monolayer (lowering WF of Ag)                  | 4-MBT                     | Dipping          | -                                                        |  |

|                     | 22 | OSC3           | Organic semiconductor (n-type)                                | TU-3                      | Dispensing       | 60 ℃ for 30 min in air /<br>120 ℃ for 30 min in nitrogen |  |

|                     | 23 | D6             | Top gate dielectric for 2F (180 nm)                           | Parylene diX-SR           | CVD              | -                                                        |  |

|                     | 24 | Via            | Laser drilling for interconnection                            | -                         | Laser            | -                                                        |  |

|                     | 25 | M7             | Metal routing, top-gate electrode, via-hole filling           | NPS-JL                    | IJP              | 120 °C for 30 min in air                                 |  |

Supplementary Table 1 Summary of manufacturing process of a stacked 3-T device (24 functional layers and a via-hole).

<sup>a</sup> inkjet printing, <sup>b</sup> work function

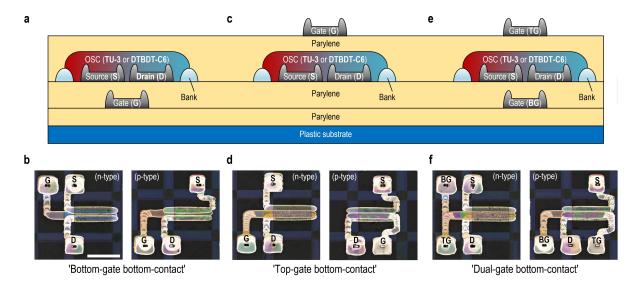

**Supplementary Figure 3** Schematic cross-section and microscopic images of the stand-alone complementary transistors. **a**, **b** Bottom-gate bottom-contact transistors. **c**, **d** Top-gate bottom-contact transistors. **e**, **f** Dual-gate bottom-contact transistors. Scale bar is 800  $\mu$ m.

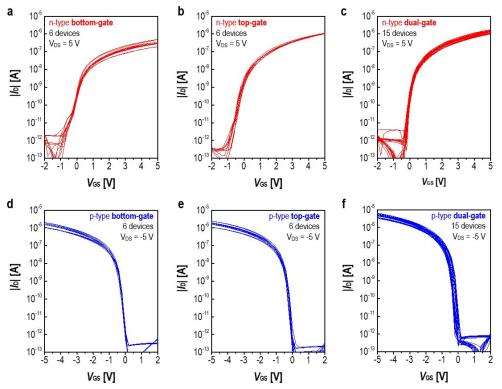

**Supplementary Figure 4** Uniform transfer characteristics of the complementary organic transistors. The n-type single-gate transistors in **a** bottom-gate and **b** top-gate configurations (6 devices for each). **c** The n-Type dual-gate organic transistors (15 devices). The p-type single-gate transistors in **d** bottom-gate and **e** top-gate configurations (6 devices for each). **f** The p-Type dual-gate organic transistors (15 devices).

|                                                                     | Stand-alone devices |            |        |        |       |        | Stacked 2-T devices |        | Stacked 3-T devices |        |       |

|---------------------------------------------------------------------|---------------------|------------|--------|--------|-------|--------|---------------------|--------|---------------------|--------|-------|

| Туре                                                                | n-type              |            |        | p-type |       | n-type | p-type              | n-type |                     | p-type |       |

| Structure                                                           | BG                  | т <b>G</b> | DG     | BG     | ТG    | DG     | DG                  | DG     | DG                  | DG     | DG    |

| (Floor)                                                             | (-)                 | (-)        | (-)    | (-)    | (-)   | (-)    | (1F)                | (2F)   | (1F)                | (3F)   | (2F)  |

| The number<br>of transistors                                        | 6                   | 6          | 15     | 6      | 6     | 15     | 24                  | 24     | 8                   | 8      | 8     |

| <i>L</i> (μm)                                                       | 17.0                | 15.4       | 14.7   | 27.8   | 26.8  | 28.5   | 17.7                | 26.9   | 37.6                | 37.0   | 60.2  |

|                                                                     | ±3.8                | ±2.4       | ±1.3   | ±2.5   | ±5.5  | ±3.7   | ±1.6                | ±3.5   | ±5.8                | ±5.5   | ±9.5  |

| W (µm)                                                              | 917                 | 921        | 916    | 932    | 935   | 937    | 918                 | 933    | 917                 | 930    | 930   |

|                                                                     | ±6                  | ±6         | ±4     | ±8     | ±6    | ±8     | ±5                  | ±8     | ±6                  | ±5     | ±5    |

| μ <sub>sat</sub> (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | 0.017               | 0.079      | 0.048  | 0.36   | 0.39  | 0.69   | 0.042               | 0.70   | 0.086               | 0.086  | 0.70  |

|                                                                     | ±0.003              | ±0.002     | ±0.001 | ±0.11  | ±0.09 | ±0.14  | ±0.009              | ±0.19  | ±0.020              | ±0.017 | ±0.29 |

| <i>V</i> <sub>тн</sub> (V)                                          | -0.77               | 0.35       | 0.29   | -0.04  | -0.12 | -0.32  | 0.23                | -0.42  | 0.51                | 0.64   | -0.41 |

|                                                                     | ±0.23               | ±0.11      | ±0.09  | ±0.14  | ±0.07 | ±0.12  | ±0.15               | ±0.11  | ±0.14               | ±0.07  | ±0.27 |

Supplementary Table 2 Channel geometries (L and W), extracted carrier mobility in saturation regime, and threshold voltage of the printed transistors of this work (BG: bottom-gate, TG: top-gate, DG: dual-gate).

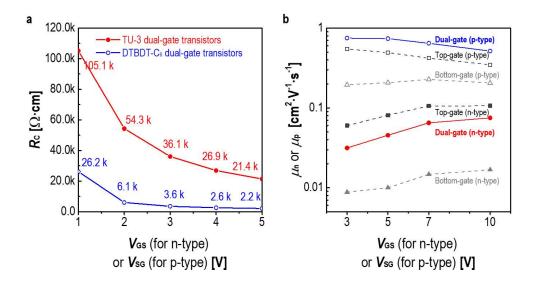

**Supplementary Figure 5 a** Contact resistance of the complementary dual-gate transistors acquired by using a transmission line measurement (TLM) method. In the TLM, the dual-gate transistors with different channel lengths were measured in dual-gate mode operation where top and bottom gates are electrically tied. **b** Gate-bias dependency of carrier mobility in the printed complementary transistors.

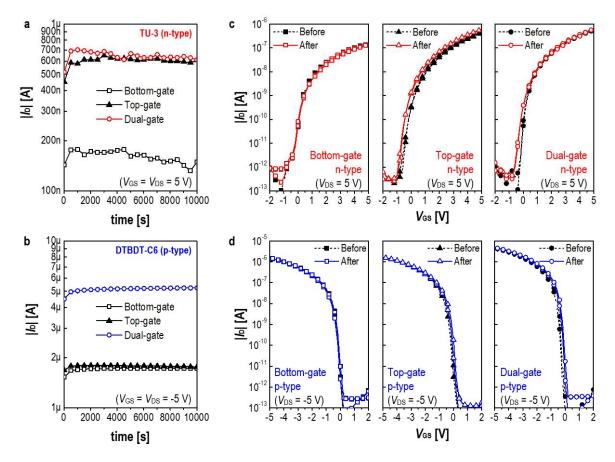

**Supplementary Figure 6** Bias stability test of the printed complementary organic transistors in bottom-gate, topgate, and dual-gate configurations. **a**, **b** Transient  $|I_D|$  of the n-type and p-type transistors in their saturation regime. **c**, **d** The saturation  $|I_D|$ - $V_{GS}$  transfer characteristics of the printed transistors before and after biased for 1000 s.

**Supplementary Figure 7** Long-term stability and environmental stress (temperature and humidity) tests. Carrier mobility and  $V_{TH}$  shift of the printed complementary transistors as kept in a dry ambient environment for one year (error bars represent standard deviation).