## Supplementary Material

## 1. System Test and Validation

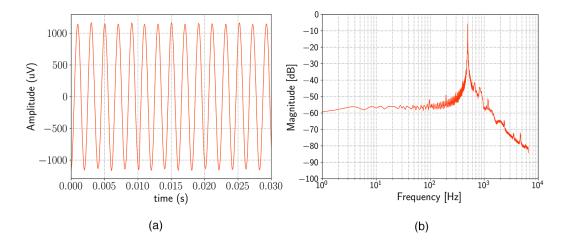

Before using the Piphys system to record neural spikes, it was tested by a standard synthetic waveform for hours. The system performance was analyzed. Figure S1a shows the recording from a 500 Hz 3 mV peak-to-peak sine wave. The power spectral density is averaged over the 32 channels. Figure S1b shows the power spectral density of the recorded signal has the frequency components with a peak at 500 Hz. Both time series and power spectral density prove the system is capable of recording real-world signals. Since the Raspberry Pi is not a perfect hard real-time device, clock issue will be discussed in the following sections.

Figure S1. Recording of a sine wave using Piphys system. Signal source is a 500 Hz 3 mV peak-to-peak sinusoid wave. (a) Result in time series. The recorded signal has a peak-to-peak voltage around 2.6 mV. (b) Power spectral density of the result.

The Intan RHD bio-amplifier supports various sample rates to accommodate different experiment requirements. Sampling on the bio-amplifier needs to be driven by the SPI clock on Raspberry Pi. The speed of the required SPI clock (SCLK<sub>r</sub>) can be calculated by equation 1, where 16 is the bit length for each data point, and 32 is the number of recording channels. In the hardware, Raspberry Pi's SPI clock (SCLK<sub>g</sub>) is generated by dividing the core clock, as shown in equation 2. The core clock frequency for Raspberry Pi 3 is set to 400 MHz. According to the BCM2835 ARM peripherals

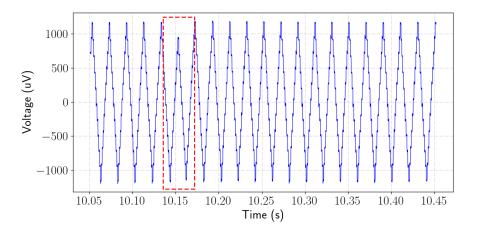

datasheet, the divider must be a multiple of 2. However, the C library<sup>‡</sup> used to generate the low level signal sets the divider to a power of 2. Clock jitter was measured by recording a continuous 50 Hz triangular wave in all channels with each sample rate. The average jitter rate is 0.067%. This jitter that happens during the recording is shown in Figure ??. No evidence shows that the jitter rate correlates with the sample rate.

$$SCLK_r = 16 \times 32 \times sample rate$$

(1)

$$SCLK_g = Core Clock/CDIV$$

(2)

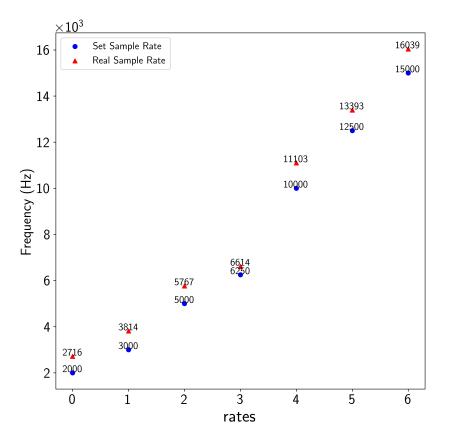

In this case, it is hard for the Raspberry Pi to generate those preferred sample rate as shown in table S1. Instead, Raspberry Pi converts the speed parameter to equivalent SPI clock divider, giving the nearest clock rate. Since the intan bio-amplifier is a passive SPI slave device, it samples the analog signal with the clock from the host board. To compensate the overhead from task scheduling, the program is set to have the highest priority that takes two CPUs out of four while running. Due to the overhead and clock jitter, the sample rate shown in the table are averaged among seven tests and errors are calculated. Considering this unstableness of SPI clock, the sample rate with each chunk of Redis data are paired for dashboard visualization. Figure S2 is plotted based on the preferred sample rates and the generated sample rates. When analyzing the recorded data, the real sample rate should be used.

| Preferred sample rate (Hz)  | 2000  | 3000  | 5000  | 6250  | 10000 | 12500  | 15000  |

|-----------------------------|-------|-------|-------|-------|-------|--------|--------|

| Generated Sample Rate (Hz)  | 2716  | 3814  | 5767  | 6614  | 11103 | 13393  | 16039  |

| Standard Deviation          | 11.01 | 20.18 | 21.03 | 17.73 | 74.26 | 107.41 | 178.48 |

| Coefficient of Variance (%) | 0.41  | 0.53  | 0.36  | 0.27  | 0.67  | 0.8    | 1.11   |

**Table S1.** Preferred sample rates and generated sample rates comparison. The generated sample rates are averaged from 7 tests with standard deviation and coefficient of variance calculated.

Knowing the intrinsic clock characteristic of Raspberry Pi, we plan to replace the hardware SPI interface with a FPGA chip that can generate precise clock pulses at desired frequency. As mentioned in Discussion section, the FPGA will be used to sample the intan bio-amplifier, and the Raspberry Pi will be in charge of data buffering with FPGA and IoT.

**Figure S2.** Desired sample rate (Set Sample Rate) and the actually generated sample rate (Real Sample Rate) from SPI clock.

Figure S3. Recording result from 50 Hz, 3 mV peak-to-peak triangular wave shows a clock jitter (red square box). All seven sample rates are tested. The average jitter rate is 0.067%. The original signal is from the White Matter signal generator with a sampling rate of 1000 Hz. Result in the figure is sampled at 13255. Because the sample rate of the device is higher than the generator, each point of the original signal is sampled multiple times during recording, thus showing the staircase effect.

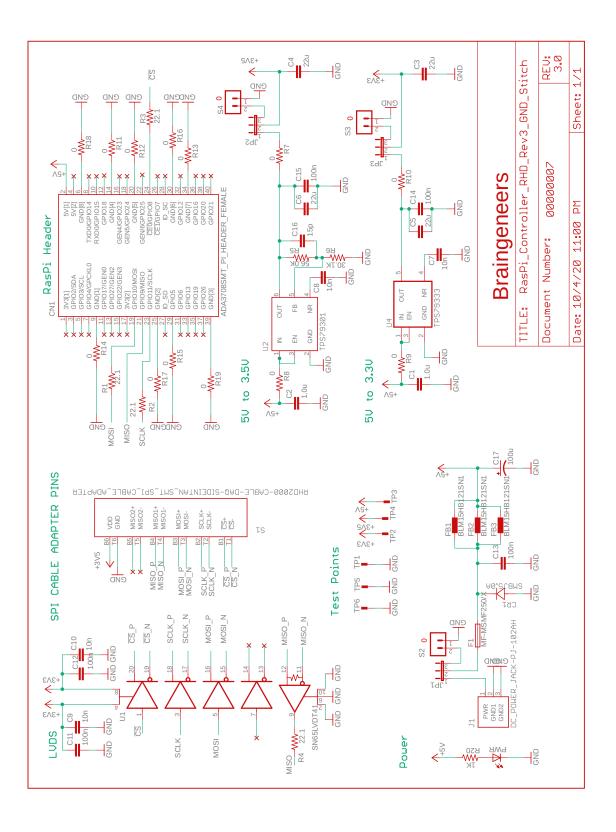

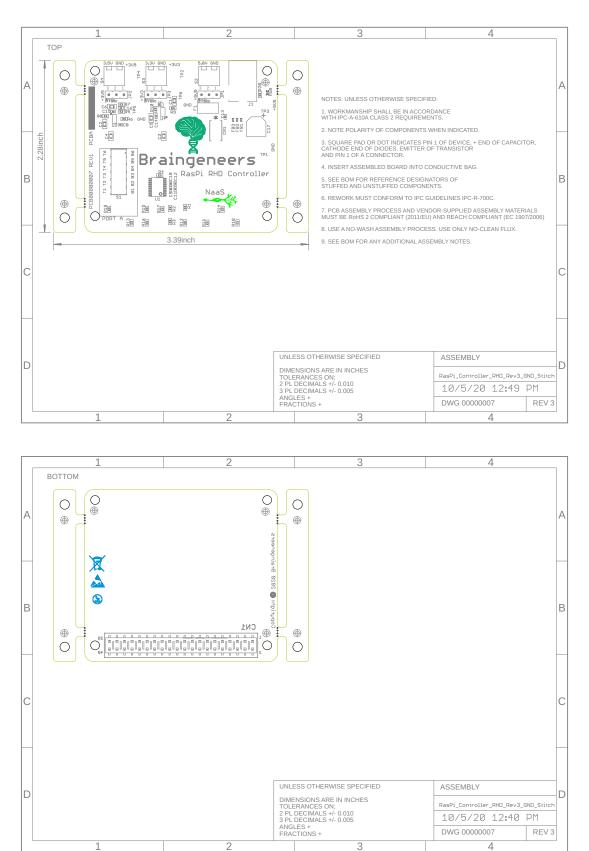

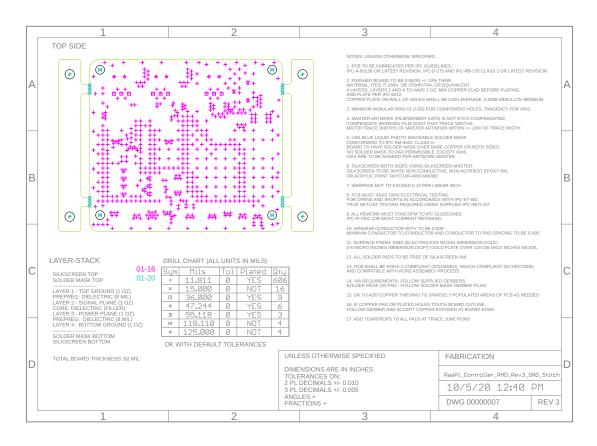

## 2. Hardware Schematics and Layouts

## 2.1. Piphys

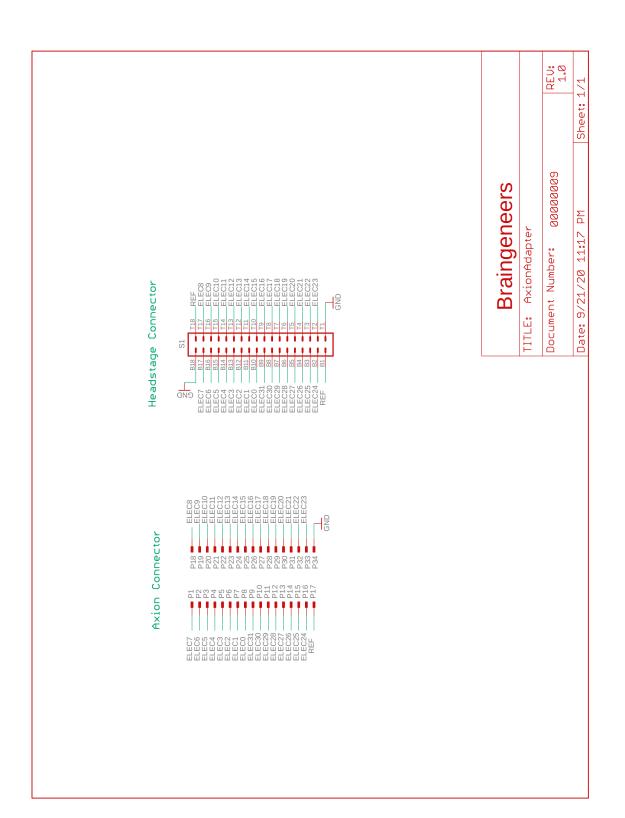

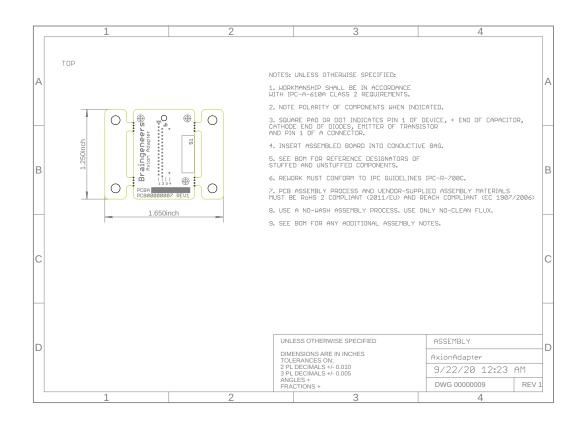

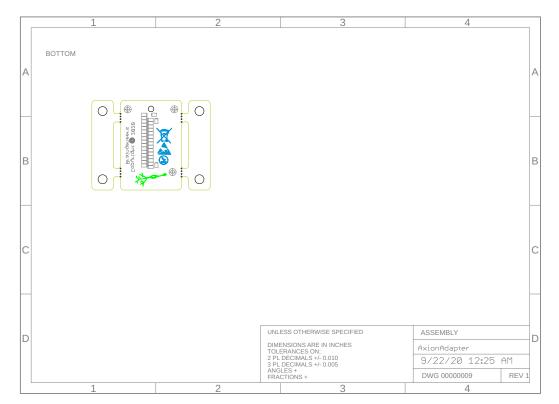

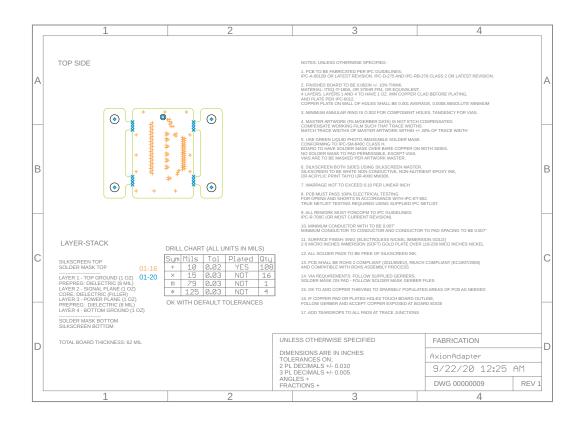

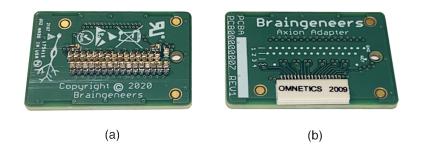

2.2. Axion Adapter

**Figure S4.** (a) Top of custom connector with finger pins which face the Axion plate. (b) Bottom of connector with Intan RHD200 headstage adapter.