# nature portfolio

### Peer Review File

Title: Experimental demonstration of highly reliable dynamic memristor for artificial neuron and neuromorphic computing

**Open Access** This file is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to

the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. In the cases where the authors are anonymous, such as is the case for the reports of anonymous peer reviewers, author attribution should be to 'Anonymous Referee' followed by a clear attribution to the source work. The images or other third party material in this file are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit <u>http://creativecommons.org/licenses/by/4.0/</u>.

#### **REVIEWER COMMENTS</B>**

Reviewer #1 (Remarks to the Author):

In this work, the authors fabricate a memristor with high endurance and low variability and claim that it is particularly suited to memristive reservoir computing (RC) systems. The proposed memristor has a decay mechanism or short-term memory which transforms spatio-temporal data to a high dimensional basis. Previous work has used similar memristor devices (with spontaneous ionic redistribution) for RC systems (reference 11), but the material and the device physics of this memristor could be leading to superior endurance and variability.

Given the novelty emphasis on being a memristive RC device, the paper should provide comparisons with other devices and demonstrate the improvements quantitatively to demonstrate the claims. Please see below for more detailed suggestions

The proposed memristor device demonstrates a novel ability to decay through the oxygen anions. This inherent self-decay feature can prove suitable in implementations of neurons for RC systems. In the case of an Echo State Network, the decay could act as the leakage factor, whereas for a Liquid State Machine the device could provide an inherent ability to act as the membrane potential of a spiking neuron. Even beyond RC methods, this device could be suitable for generic spiking neural network implementations. However, there are three key discussion points that I feel need to be addressed in this paper.

First, from my understanding this device cannot behave like traditional memristors where it can retain a specific resistance state but it is unclear as the authors state in line 147 " The LRS to HRS transition (reset) could occur without external stimulus due to the 148 diffusion of oxygen anions, which results in short-term memory effects with a 40 ms time constant." By saying it could occur, it is unclear if there is a probabilistic nature to the decay factor or if the device can become stuck at a LRS.

Second, because the novelty of this self-decay property is reliant on the W/I ratio, there should be a larger focus on the possibilities of the device. From the paper, the width/interval ratio is what determines the rate of decay. It would be beneficial to discuss the sizing of the devices for different W/I ratios, how/if device properties change, and minimum and maximum time-constants achievable.

Third, though the paper is framed for RC systems, it appears to be better suited towards an efficient neuron model using a memristor. The proposed memristors cannot serve as weights, but it is hard to assess the feasibility of designing neurons around the proposed device without the complete circuitry. The authors should focus on tailoring the discussion and simulations to show how this device can be realized to implement neuronal models, such as those in typical RC models, and how it compares in terms of efficiency with existing neuron models (memristor, analog, or digital).

RC models have less parameters than LSTMs and RNNs. This statement holds true for LSTMs which have complex gating models, but they have an equivalent number of parameters as RNNs. The only other

benefit for RC is the reduced training cost but from the discussion in the paper it does not focus on online learning. Rather they discuss a fixed, pre-trained readout which can be deployed to multiple crossbars due to the uniform nature of their fabrication.

Beyond that, at a high level the claim this as an RC computing model requires serious validation. From all the tests and architectures described there is no recurrent network. Rather, from the way it is presented, a set of memristors that act as leaky integrators are implemented and readout the final state of each individual memristor for classification. This is not a true RC model, and it is not clear how they treat the inputs to the network in terms of weights. In writing they discuss how the memristors see a combination of inputs, but in the alphabet example it is described as a 1-to-1 mapping where each memristor only sees a single input. A similar setup is described for the AMP sequences.

By framing the device contributions in the light of new neuron circuits and generalizable models, there could be lot more merit to this paper, rather than presenting it as an RC memristor.

Another concern is that the authors discuss the high-dimensional basis used for classification, but if every memristor is only a filtered version reflecting the activity of a single input category, each device belonging to the same input should be the same. This is almost like concatenating the input multiple times, but not truly expanding to a high-dimensional space where the input would become linearly separable. In this setup, one cannot see the need to use more devices than the number of unique input characters. Beyond this, how would the authors intend to extend the proposed approach to a single variable, continuous time-series data, or multivariable continuous data.

That being said, in terms of clarity I think the paper is poorly written in that it does not flow. It was very hard to follow the discussion and figures, and there seemed to be very little discussion around several key topics. First, the classification method relied on the decay of memristor states. If the decay is inherent to the memristor, it is unclear how it can be controlled to allow the memristor to hold a specific resistant state (the paper states that "decay from LRS to HRS could occur"). If it is not possible, there are limitations in how long information can be stored (likely dependent on the W/I ratio) but this is not thoroughly explored, and this device cannot be used as a synaptic weight which is common in memristor based neuromorphic circuits making it serve a very different purpose. If the decay can be controlled, what is the overhead associated with it? The other part that is difficult to understand is what the multi-modal RC setup is. It seems like it just refers to a system of crossbars with different W/I ratios which is confusing when used with the term multi-modal in ML. But then questions arise such as: how scalable is the approach with varying W/I intervals, how large are the devices, what are the limits in terms of ratios and their respective memory lengths.

Grammatical edits:

Line 27 - while using a small number of training Line 60 - The mentioned bottlenecks can be reiterated and mapped to their solutions in the existing work in the later stages of the paper Line 170 - anions across the whole TiOx bulk Fig. 2 - (b) and (c) label spelling (electrode)

Reviewer #2 (Remarks to the Author):

The work by Park et al. presents a TiOx-based memristor system and proposed an RC system based on such memristors. There are clearly interesting results, including the forming-free and uniform switching characteristics of the TiOx memristors. The materials study also seems solid, and the topic is timely. However, several concerns need to be addressed.

RC systems are suitable for processing temporal data. It's thus puzzling why the authors picked the AMP task, which has no temporal components. In fact, the readout layer seems quite elaborate (multi-layer perception with nonlinear activations) already. Given the complex readout layer, instead of using an RC system, I would expect a conventional CNN network + the existing readout layer can probably achieve similar or better results.

The AMP task is achieved through simulation. The authors have enough memristors and have 100% yield, so why not implement it experimentally?

The experimental setup was very unclear. There was no discussion in the main text, and only scant information in "Methods". From Supplementary Information Figure S13, it seems the authors send 1 character to a corresponding memristor, instead of sending a sequence to 1 memristor. Why? Overall a careful justification for the experimental setup needs to be presented, and it should be included in the main text.

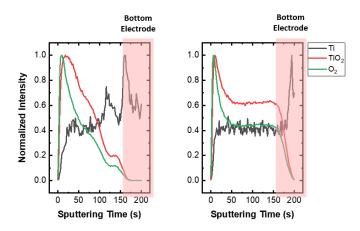

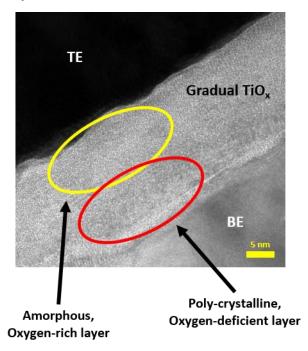

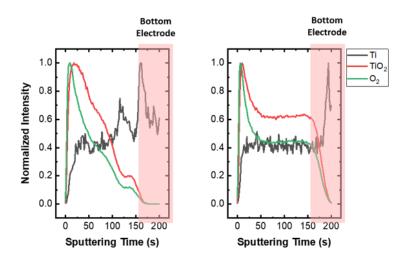

The authors highlight throughout the manuscript the idea of "gradual TiOx" and showed the two regions of amorphous oxygen-rich layer and polycrystalline oxygen-deficient layer. Since the TiOx layer is created through a single anodization of the Ti BE, why is the bottom layer polycrystalline while the top layer amorphous?

Several claims are over-reaching and incorrect. Including "To the best of our knowledge, this is the first study to demonstrate a large 1R memristor crossbar array with 100% device yield." (p6), and "For the first time, we trained and generated sequential data with memristive RC." (p15).

Reviewer #3 (Remarks to the Author):

This work combine two highly hot topics: memristors and machine learning. The main novelty of the work consist in application of memristors' array, while individual memristors possess average characterictics in comparison with other recently published based on TiO2 (10.1063/1.5037835, 10.3389/fchem.2020.00724,10.1063/1.4940361) and other matrials (10.1038/s41467-021-25455-0,10.1038/s41586-021-03748-0). Authors demonstrates important results and this study hs significant contribution to the field of application of memristors in machine learning. I recommend to publish this

article in Nature Communications after minor revision. Several questions are listed below

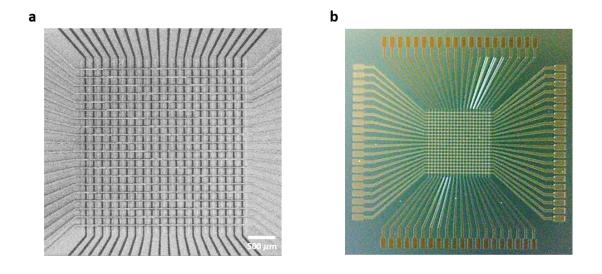

1) how was obatin fig. 1f,g and fig. S3? Is this photo or schemes?

I recommend also provide SEM of crossbar array or AFM

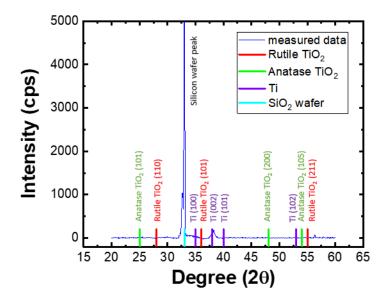

2) the choice of anodizing technique and obtained TiOx layer should be explained in more detail. What is the advantage in comparison with PVD or ALD? What phase was obtained (rutile, anataze or others? Is this nanocrystalls or nanotubes. This answers should be adressed, I recommend provide X-ray analysis for phase identification.

3) aithors should be more accurate in discusins of mechanism of TiO2 and conclusions (p. 9, word file). This paragraph sound as a guess

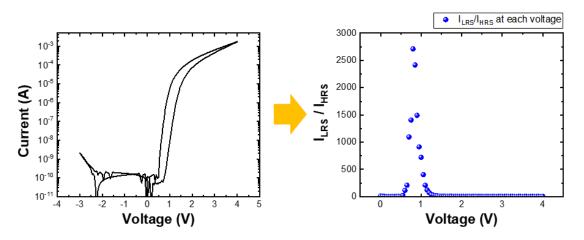

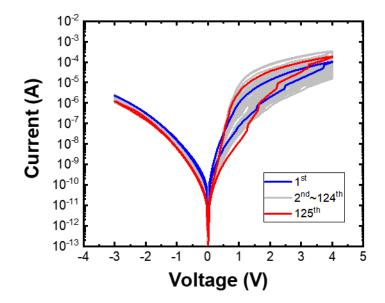

4)20 is not very high on/of ratio. What is on/of ratio for individual memristor? Is 20 is average for all arrays? Fig. S4 provides only 2 cycles, for better demonstration of stability more cycles (at least 50, if authors claims 50 cycles at fig. 1 and 10^6 cycles at p.6).

5) p. 13, clarification for mechanism of killing cell should be provided "The positively charged hydrophilic portion of the peptide attaches to the negatively charged surface of the bacteria, and the hydrophobic portion interacts with proteins on the surface of the bacterial cell to induce "bacterial lysis", which kills the cell"

### **Response Letter to Reviewers' Comments**

We sincerely appreciate the valuable time the reviewers have spent reviewing our manuscript and providing insightful comments and suggestions to help further improve the quality of our work. Considering the reviewers' evaluations, we have made a point-by-point response to the reviewers' comments, and revised our manuscript to improve the clarity of our work. We believe we have addressed all of the reviewers' comments and now the paper is more rigorous in content and clearer in presentation. Based on the responses below, we have appended twelve figures in the revised manuscript, twelve figures and two tables in the supplementary information, to address the comments. Our point-by-point responses to the reviewers' comments are as follows.

#### Reviewer #1

In this work, the authors fabricate a memristor with high endurance and low variability and claim that it is particularly suited to memristive reservoir computing (RC) systems. The proposed memristor has a decay mechanism or short-term memory which transforms spatio-temporal data to a high dimensional basis. Previous work has used similar memristor devices (with spontaneous ionic redistribution) for RC systems (reference 11), but the material and the device physics of this memristor could be leading to superior endurance and variability.

Given the novelty emphasis on being a memristive RC device, the paper should provide comparisons with other devices and demonstrate the improvements quantitatively to demonstrate the claims. Please see below for more detailed suggestions

**Response:** We thank the reviewer for the constructive comments on our work and also for pointing out the important insight to emphasis the results. To reflect the reviewer's evaluation on the manuscript, we have revised the title of the manuscript, modified several parts of the main text, and added additional experiments and discussion to address pointed issues. We also have added the comparisons with other devices in terms of an artificial neuron device and a RC device. Our detailed responses to your comments are provided below.

#### Comment #1:

The proposed memristor device demonstrates a novel ability to decay through the oxygen anions. This inherent self-decay feature can prove suitable in implementations of neurons for RC systems. In the case of an Echo State Network, the decay could act as the leakage factor, whereas for a Liquid State Machine the device could provide an inherent ability to act as the membrane potential of a spiking neuron. Even beyond RC methods, this device could be suitable for generic spiking neural network implementations. However, there are three key discussion points that I feel need to be addressed in this paper.

**Response:** Thank you very much for this insightful comment. As the reviewer mentioned, the device properties are not suitable only for the RC system, but also for the generic electrical neuron. Therefore, we have conducted additional experiments for the developed memristor based artificial neuron. We have added additional experimental data and discussion about the memristor based artificial neuron.

To emphasize the device operation as an artificial neuron, we have changed the manuscript title to "Experimental demonstration of highly reliable dynamic memristor for reliable artificial neuron and neuromorphic computing" from "Experimental demonstration of highly reliable dynamic memristor array for reservoir computing". In addition, we have added a subsection "Reliable LIF neuron with gradual  $TiO_x$  memristor" to discuss the neuron operation of the device. We also have revised the abstract, introduction, and conclusion sections to reflect the results and discussion about the neuron operation.

Detailed explanations are provided below.

#### Comment #2:

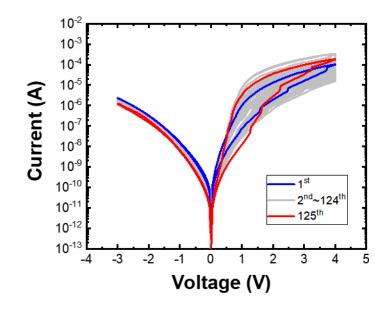

First, from my understanding this device cannot behave like traditional memristors where it can retain a specific resistance state but it is unclear as the authors state in line 147 " The LRS to HRS transition (reset) could occur without external stimulus due to the 148 diffusion of oxygen anions, which results in short-term memory effects with a 40 ms time constant." By saying it could occur, it is unclear if there is a probabilistic nature to the decay factor or if the device can become stuck at a LRS.

**Response:** Thank you for this valuable comment. We agree that our original statement is ambiguous and may be misleading. The device in this work is volatile, which means that it has short-term retention instead of long-term retention. Therefore, to inform this, we removed the word "could" from the original sentence and added the word "volatile" to emphasize the device has a short-term memory effect as follows:

Page 8, line 166: "The LRS to HRS transition (reset) occurs without external stimulus due to the diffusion of oxygen anions, which results in short-term (volatile) memory effects with about 40 ms time constant."

#### Comment #3:

Second, because the novelty of this self-decay property is reliant on the W/I ratio, there should be a larger focus on the possibilities of the device. From the paper, the width/interval ratio is what determines the rate of decay. It would be beneficial to discuss the sizing of the devices for different W/I ratios, how/if device properties change, and minimum and maximum time-constants achievable.

**Response:** Thank you very much for the constructive comments. As the reviewer suggested, we added more explanations for the device and conducted experiments as shown below.

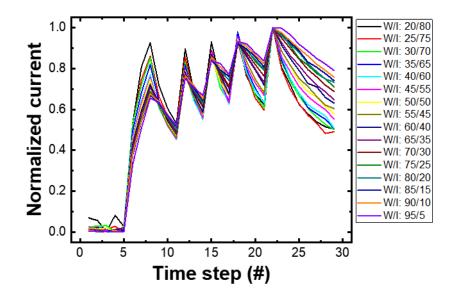

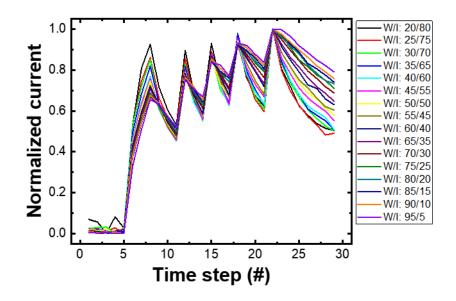

(1) The effect of the device sizes and pulse width/pulse interval (W/I) ratios on device properties.

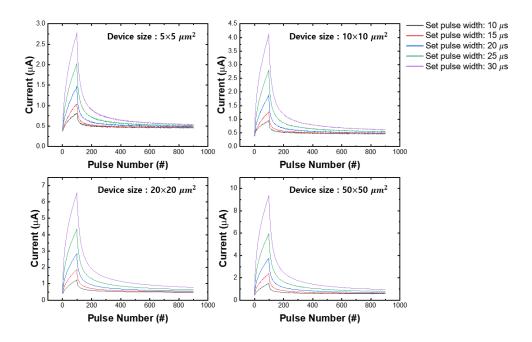

First, we have conducted the device measurements with various device sizes and W/I ratios and verified that the device size changes the current magnitude while the device properties such as potentiation/decaying characteristics remain same. The devices with different sizes  $(5\times5, 10\times10, 20\times20, 50\times50 \,\mu\text{m}^2)$  are investigated with various pulse conditions, as shown in Figure R1. The devices are potentiated with consecutive 100 set pulses (4 V) with various W/I ratios  $(10/90\sim30/70)$  within 100  $\mu$ s. As shown in the Figure R1, the device current reduces as the device size decreases due to the non-filamentary nature of the device. Moreover, it does not significantly change the other properties such as decaying speed and potentiation ratio for each W/I ratio, which means the device is scalable without property degradation. For example, the decaying time constant is about 40 ms for the largest W/I ratio case (30/70) for every device regardless of the device size. To clarify these, we appended sentences:

Page 9 and line 176: "In Supplementary Fig. 7 the device current reduces as the device size decreases due to the non-filamentary nature of the device. Moreover, it does not significantly change the other properties such as decaying speed and potentiation ratio, which means the device is scalable without property degradation."

The corresponding Figure R1 is also appended in the Supplementary Figure 7 in the Supplementary information.

Figure R1. The response of devices with different device sizes and W/I ratios. Four devices having different sizes from  $5 \times 5 \ \mu m^2$  to  $50 \times 50 \ \mu m^2$  are measured by the read pulses (1.8 V, 400  $\ \mu$ s) during the consecutive 100 set pulses (4 V) and following decaying. The pulse widths are varied from 10~30  $\ \mu$ s and the corresponding pulse intervals are 90~70  $\ \mu$ s. The responses from each device are identical except current scaling effect due to device size difference.

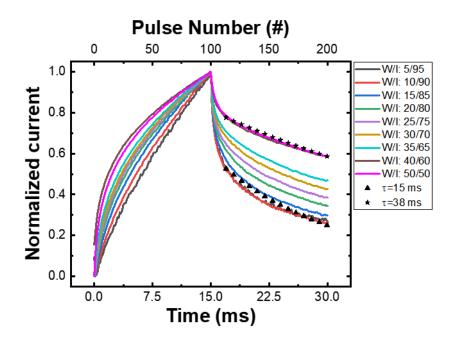

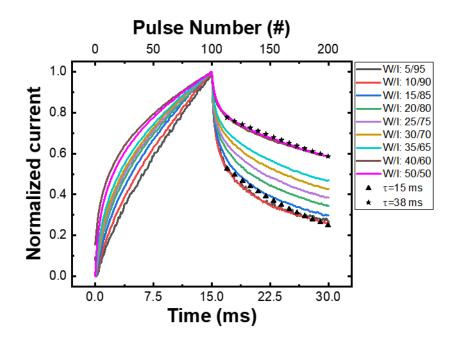

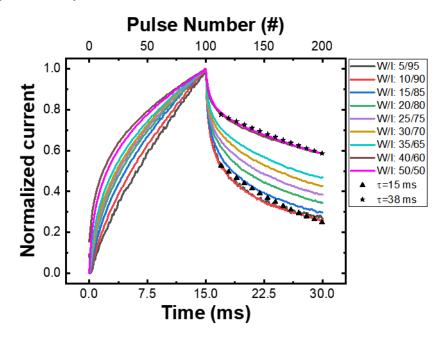

(2) The maximum and minimum of time constants

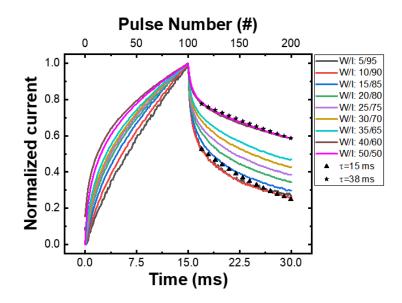

To investigate the minimum and maximum decaying time constant of the device, the gradual  $TiO_x$  memristor is potentiated with various W/I ratios from 5/95 to 50/50 within 100 µs, and the decaying time constants are analyzed. As shown in the Figure R2, the decaying characteristic is changed when the W/I ratio is changed. When the W/I ratio is large, the longer set pulse width results in a larger amount of the oxygen anions movement into the Pt-gradual oxide interface. This causes slow decaying speeds and a long time constant. The maximum time constant (~38 ms) is achieved when the W/I ratio is larger than 40/60. The minimum time constant (~15 ms) is achieved when the W/I ratio is smaller than 10/90. The decaying time constant can be adjusted by modifying the W/I ratio and we added the following sentences in the main text:

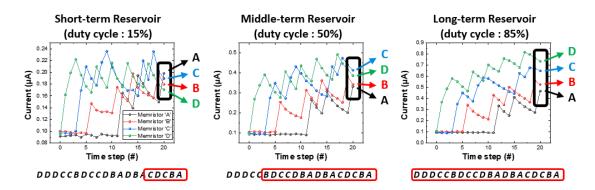

Page 17 and line 357: "As shown in the Supplementary Fig. 17, a high pulse width/interval (W/I) ratio makes the decaying speed slower and increases the time constant, while a low pulse W/I ratio makes the decaying speed faster and decreases the time constant. The decaying time constant can be controlled from 15 ms to 40 ms by adjusting the W/I ratio, and the different decaying speed enables the memristors to process the same input data differently."

We also appended Figure R2 as a Supplementary Figure 17, to show the time constant change along with the different W/I ratio.

Figure R2. The normalized responses of the gradual  $TiO_x$  memristor during the potentiation and decaying with various W/I ratios.

#### Comment #4:

Third, though the paper is framed for RC systems, it appears to be better suited towards an efficient neuron model using a memristor. The proposed memristors cannot serve as weights, but it is hard to assess the feasibility of designing neurons around the proposed device without the complete circuitry.

The authors should focus on tailoring the discussion and simulations to show how this device can be realized to implement neuronal models, such as those in typical RC models, and how it compares in terms of efficiency with existing neuron models (memristor, analog, or digital).

**Response :** Thank you for the insightful comments and suggestions about the experiments. We agree that our work can be implemented as an artificial neuron device using short-term memory effect such as a leaky-integrate and fire (LIF) neuron and a short-term neuron for RC. Therefore, we have conducted several experiments to prove the proposed memristor can be used as a reliable artificial neuron. We also discussed how the developed memristor can be realized as a LIF neuron. In addition, we appended the two comparisons; 1) LIF neuron devices, 2) RC devices in terms of efficiency. To see the feasibility of the memristor based RC, we have appended a designed circuitry for the proposed RC system. The detailed explanations are provided below.

To focus on the device property as an artificial neuron, we have conducted experiments about the memristor based LIF neuron and added a new subsection "Reliable LIF neuron with gradual  $TiO_x$  memristor" in the main text to explain the results for a highly reliable artificial neuron, and tailored the discussion. The subsection includes (1) a comparison between the biological neuron and the memristor based artificial neuron, (2) a complete circuitry for the artificial

neuron with the proposed memristor, and (3) the superior characteristics of the artificial neuron based on the gradual  $TiO_x$  memristor, especially in terms of the uniformity.

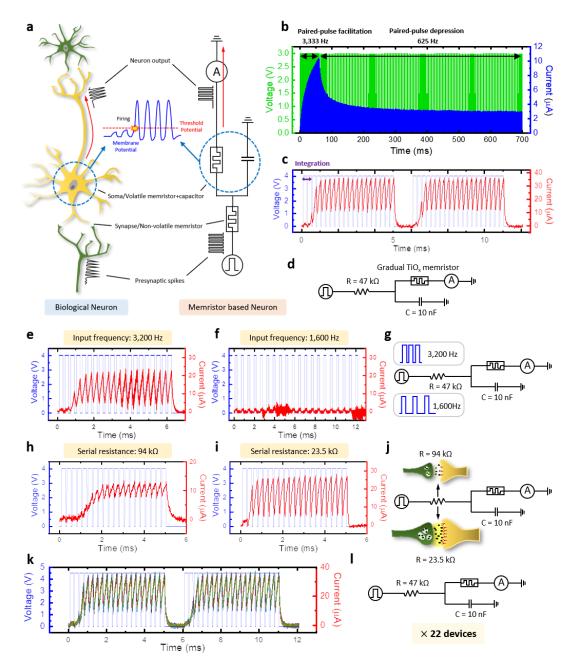

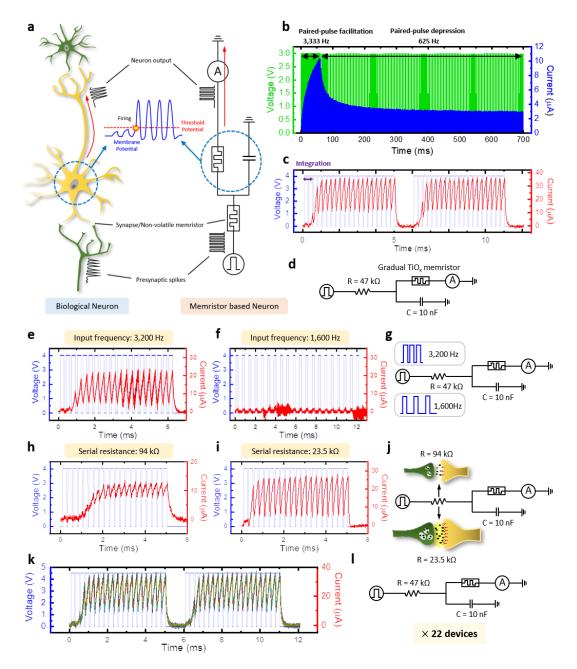

(1) Short-term plasticity and LIF neuron operation of the gradual TiO<sub>x</sub> memristor based neuron.

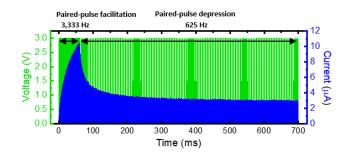

First, to show that the device can operate as a highly reliable neuron device, PPF (paired-pulse facilitation) and PPD (paired-pulse depression), which are the short-term plasticity of the biological neuron, are measured with two different input pulse train frequencies to the device. The input pulse has a 3 V amplitude and a 100 µs duration. When the pulse train frequency is high (3,333 Hz), the device conductance increases, which is similar to the short-term potentiation in the biological neuron (PPF) (see Figure R3). On the other hand, if the pulse train frequency is low (625 Hz), the conductance decreases, which is similar to the PPD of the biological neuron. These short-term plasticity features can be used as a leaky-integrator. The short-term plasticity is also applicable to the reservoir computing system, that requires the leaky-integrate neurons in the reservoir.

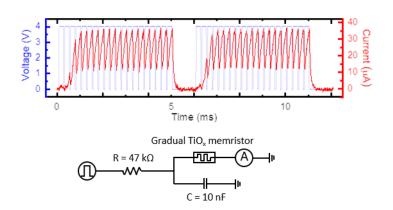

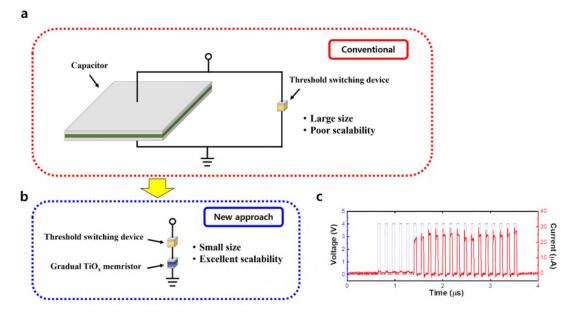

Second, to emulate a biological LIF neuron, we built a simple artificial LIF neuron based on the memristor device. The circuit schematic of the artificial neuron and the comparison to the biological neuron are shown in Figure R4. The LIF neuron circuit based on the volatile memristor is widely studied in previous studies (e.g. Wang, Z. et al. [*Nat. Electron.*, 2018], Kumar, S. et al. [*Nature*, 2020], Duan, Q. et al. [*Nat. Commun.*, 2020]). As represented in Figure R4, the parallelly connected capacitor and the memristor are analogous to the biological neuron's soma, that integrates the signals from the presynaptic neurons and makes an action potential when it fires. The serially connected non-volatile memristor represents the synaptic weight between the neuron and the presynaptic neuron, where the small resistance means the strong connection between them. In this study, to exclude the non-idealities from the non-volatile memristor to a general resistor.

Figure R3. The short-term plasticity of the gradual  $TiO_x$  memristor along with the different input spike frequencies. The gradual  $TiO_x$  memristor is tested with the input pulse train (3 V, 100 µs) having 3,333 Hz (high frequency) followed by 625 Hz (low frequency). When the input pulse train has a high frequency, the device conductance increases, which is analogous to the PPF (paired-pulse facilitation) in a biological neuron. When the input pulse has a low frequency, the device conductance decreases, which is analogous to the PPD (paired-pulse facilitation) in a biological neuron. When the input pulse has a low frequency pulse train is applied, even though the input pulse amplitude remains the same, because of the short-term memory effect of the gradual  $TiO_x$  memristor.

Figure R4. An illustration of the operation of a biological neuron (left) and the developed memristor-based artificial neuron (right). The synapse between the presynaptic neuron and the post-synaptic neuron, the soma which integrates the presynaptic spikes, and the post-synaptic spikes of the biological neuron are represented as a non-volatile memristor, a volatile memristor and parallelly connected capacitor, and the spikes from the volatile memristor, respectively, in the artificial neuron.

Based on the artificial neuron composed of a 47 k $\Omega$  serial resistor, a 10 nF capacitor and the proposed memristor, we have measured LIF neuron characteristics and analyzed the results (see Figure R5). First, when the 4 V, 200 µs input spike train with a 50 µs interval is applied to the device, the artificial neuron generates post-synaptic spikes after integrating two presynaptic spikes. During the first two input spikes, the artificial neuron does not make output spikes but just integrates the charges in the capacitor. After the two spikes, the artificial neuron's potential (or the capacitor potential) exceeds the threshold voltage of the memristor. Then, the memristor is turned into the low resistance state and conduct current, which is an analogy of the firing of a biological neuron.

Figure R5. The LIF neuron operation of the developed memristor-based artificial neuron, and the used circuitry. The gradual  $TiO_x$  memristor is connected with a serial resistor and a parallel capacitor, which serve as a synapse and a soma, respectively. At first, the memristor-based neuron does not fire because the input spike is accumulated in the capacitor. When the capacitor is charged and the potential across the capacitor becomes large as much as the set voltage (threshold voltage) of the memristor, the memristor is triggered to the low resistance state and the neuron fires. In the given resistance and capacitance, the artificial neuron requires two input spike pulses (presynaptic spikes) to exceed the threshold in this figure, as shown in the output current (red line) of the neuron.

#### (2) Characteristics of the developed artificial neuron

To test the characteristics of the gradual  $TiO_x$  memristor-based artificial neuron, we tested the artificial neuron's responses according to (1) the different presynaptic spike frequency, (2) synaptic strength (serial resistor's conductivity), (3) presynaptic spike amplitude, (4) different capacitor, and (5) the different resistor and capacitor with the same R×C value. (Figure R6-10).

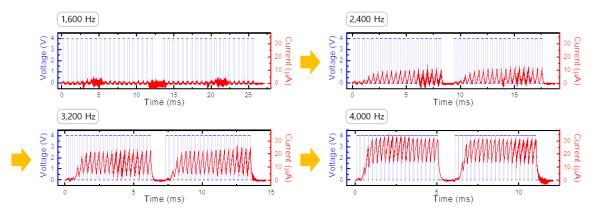

As shown in Figure R6, when the presynaptic spike frequency is low (1,600 Hz), the artificial neuron does not generate post-synaptic spikes, because the integrated charges in the capacitor are depleted during the interval between spikes. However, when the input frequency increases, the artificial neuron generates post-synaptic spikes. This frequency dependent firing characteristic is important to learning in the human brain, by potentiating (depressing) synapses between frequently (infrequently) firing presynaptic neurons and a post-synaptic neurons.

Figure R6. The responses of the developed memristor-based artificial neuron along with various presynaptic spike frequencies. The artificial neuron is tested with the presynaptic spike trains (200  $\mu$ s, 4 V) with various frequencies (1,600, 2,400, 3,200, and 4,000 Hz) to investigate the artificial neuron responses. When the frequency is 1,600 Hz (low), the artificial neuron does not fire, even though the presynaptic spike trains are applied. For the frequencies larger than 2,400 Hz (high), the artificial neuron fires. The used artificial neuron is composed of the gradual TiO<sub>x</sub> memristor, a 47 k $\Omega$  resistor and a 10 nF capacitor.

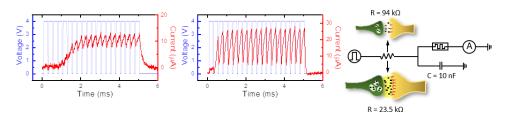

Figure R7 shows the different responses of the artificial neuron with different serial resistor (94 k $\Omega$  for left plot and 23.5 k $\Omega$  for right plot). The synapse between two neurons can be represented as a resistor. When the resistance is high (94 k $\Omega$ ), the synapse is weak and the neuron fires after integrating five presynaptic spikes. On the other hand, when the resistance is low (23.5 k $\Omega$ ), the synapse is strong and the neuron fires within integrating a single spike. The result for moderately connected synapse (47 k $\Omega$ ) is shown in Figure R5, and it integrates two spikes for firing. Biological neurons that are connected with strong synapses fire together because the spikes from the strongly connected presynaptic neuron easily induces firing of the post-synaptic neuron. If the two neurons are fired simultaneously, they are wired together (potentiation of the synapse). This means that the firing of the post-synaptic neuron right after the firing of the pre-synaptic neuron makes the synapse stronger. This is called "Hebbian learning", and is considered a fundamental learning mechanism of our brain. The developed artificial neuron in Figure R7 also shows the same property to the biological neuron; the required number of spikes for post-synaptic neuron firing decreases when the synapse is strong. Therefore, these results demonstrate that the developed artificial neuron can be utilized for the neuromorphic processor with biological learning rules.

Figure R7. The effect of the synaptic strength to the artificial neuron response.

Figure R8 shows the responses of the artificial neuron with different presynaptic spike amplitudes (2.5, 3.5, 4, and 4.5 V). When the spike amplitude is low (2.5 V), the artificial neuron does not fire. This is because the charges integrated in the capacitor are too low to generate high voltage for turning on the memristor. However, if the input amplitude is higher than 3.5 V, the neuron starts firing after integrating one or two presynaptic spikes. This result shows the artificial neuron can be modulated by the spike amplitude.

Figure R8. The effect of the presynaptic spike amplitude to the artificial neuron response.

The developed artificial neuron's characteristic can be easily modified by changing the capacitor, which determines the threshold voltage of the neuron (see Figure R9). When the capacitance is small, the capacitor's potential, which analogous to the membrane potential of the biological neuron, is easily elevated up to the threshold voltage. Therefore, when a 5 nF capacitor is used in the artificial neuron, the neuron fires after integrating a single presynaptic spike. However, if the capacitance increases to 10 nF, it requires two pulses to fire the post-synaptic spikes. Finally, when the capacitance is 20 nF, the neuron requires five spikes to fire. These results demonstrate that our artificial neuron can be easily tuned by modifying the capacitor.

### Figure R9. Modulation of the threshold characteristic of the artificial neuron by changing the capacitance.

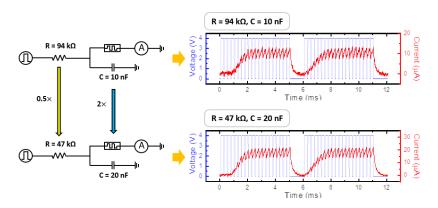

As shown in the Figure R10, when two neurons have different resistance and capacitance but the RC value remains same, the neuron shows same responses. This is because the threshold voltage is determined by the charges in the capacitor, and the speed of charging the capacitor is represented as R×C. In the experiments, an artificial neuron is composed of 94 k $\Omega$  resistance and 10 nF capacitance (a neuron that easily fires but has a weak synapse), and the other is composed of 47 k $\Omega$  resistance and 20 nF capacitance (a neuron that hardly fires but has a strong synapse). The neurons show similar response to the presynaptic spike trains.

Figure R10. The effect of the resistor and capacitor to the artificial neuron's characteristic.

#### (3) Spatio-temporal variation

Further investigations about the device-to-device variation, cycle-to-cycle variation, and operation speed of the artificial neuron have been conducted, and the results are shown in the Figure R11-13.

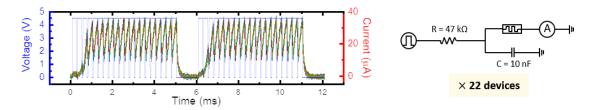

To assess the device-to-device variation of the developed gradual  $TiO_x$  memristor based artificial neuron, randomly selected 22 devices are used for the artificial neuron and measured. In the figure R11, the results of the 22 neurons are plotted. The 22 neurons show identical responses, which means excellent device-to-device uniformity. It proves the superiority of the gradual TiO<sub>x</sub> memristor for the artificial neuron device with high uniformity.

Figure R11. The LIF neuron operations from the randomly selected 22 devices. All of the 22 devices show similar response along the presynaptic spike train (200  $\mu$ s, 4.5 V). These

results demonstrate the superior device-to-device uniformity of the gradual  $TiO_x$  memristor based artificial neuron.

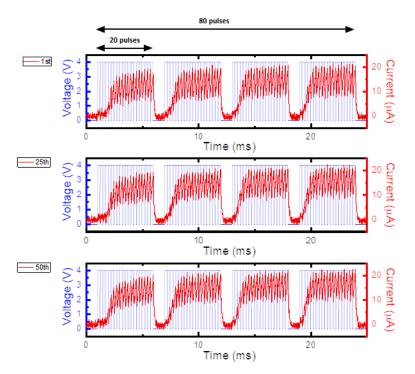

In figure R12, the cycle-to-cycle of the developed artificial neuron is assessed. The artificial neuron is tested with 50 cycles of pulse train, where a single pulse train consists of 4 sub-pulse train, and a sub-pulse train has 20 pulses (4 V, 100  $\mu$ s, and 50  $\mu$ s interval). For one cycle, four sub-pulse trains are applied to the neuron with 1 ms interval. During the test, the responses of the artificial neuron are not significantly changed, as shown in the figure R12. Because of high uniformity of the gradual TiO<sub>x</sub> memristor-based artificial neuron, a neuromorphic processor with high reliability could be utilized with the proposed device.

Figure R12. The cycle-to-cycle uniformity of the artificial neuron.

(4) Operation speed of the artificial neuron

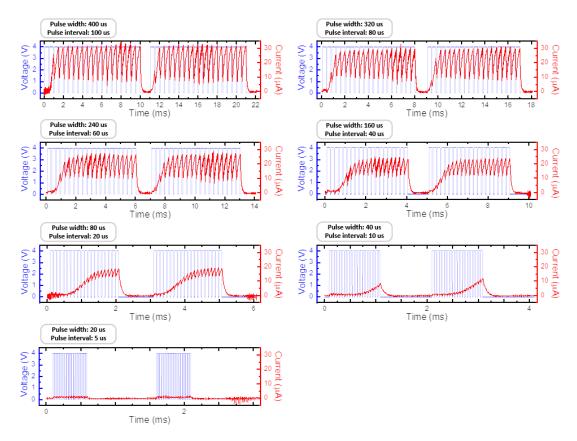

To test the operation speed of the artificial neuron, the artificial neuron has been activated in various presynaptic spike conditions, as shown in the Figure R13. The presynaptic spike width and interval decrease, while keeping the same ratio, from 400  $\mu$ s to 20  $\mu$ s for spike width and from 100  $\mu$ s to 5  $\mu$ s for spike interval. These results demonstrate that the neuron operates with short pulse as short as 40  $\mu$ s of spike width.

**Figure R13. The effects of the pulse (spike) width to the operation of the artificial neuron.** Presynaptic spike trains with various pulse widths are applied to the artificial neuron to investigate the operation speed of the artificial neuron. The neuron operates with spikes as short as 40 µs. During the test, the ratio between spike width and spike interval keeps constant.

To inform the above additional contents in the manuscript, we have appended Figure R3-R7 and R11 in the manuscript as Figure 3a-31, and others in Supplementary Figure 10-14 in Supplementary information. The Figure 3a-31 which is appended in the revised manuscript is shown in Figure R14.

**Figure R14. Gradual TiOx memristor-based LIF neuron. a,** Illustration of a biological neuron and the analogous memristor-based artificial LIF neuron. **b**, The short-term plasticity of the gradual TiO<sub>x</sub> memristor along with the different input spike frequencies. **c**, The LIF neuron operation of the developed memristor-based artificial neuron. Applied spike train condition: 4 V, 200  $\mu$ s width, and 50  $\mu$ s interval **d**, The schematic of the circuitry used for the gradual TiO<sub>x</sub> memristor-based artificial neuron. **e-g**, The output of the artificial neuron along with different presynaptic spike frequencies (3,200 Hz (e) and 1,600 Hz (f)), and the illustration of the experimental setup. During the test, the pulse amplitude and width are fixed (4 V, 200  $\mu$ s). **h-j**, The output of the artificial neuron along with the different synaptic strengths (different resistor). When the synaptic strength is weak (large resistance (h)), the artificial neuron fires within six spikes, while it requires fewer spikes when the synaptic strength is strong (small

resistance (i)). **k** and **l**, The outputs of the 22 different artificial neurons demonstrate low variation of the gradual  $TiO_x$  memristor-based artificial neuron.

We also added the newly appended subsection "Reliable LIF neuron with gradual  $TiO_x$  memristor" to reflect the correct implication.

Page 10-13:

#### "Reliable LIF neuron with gradual TiOx memristor

A biological neuron receives spike signals from presynaptic neurons and integrates the signals into its membrane potential (see Fig. 3a). When a neuron receives spikes in a certain interval, the neuron's membrane potential is elevated. Once the membrane potential exceeds the threshold potential, the neuron sends spikes (an action potential) to its post-synaptic neuron. However, because the neuron has leaky-integrate property, the membrane potential goes back to its original potential (a resting potential) if the presynaptic neuron stops sending spikes and the membrane potential does not reach the threshold. This leaky integrator property is represented as the short-term plasticity of a neuron and induces "paired-pulse facilitation (PPF)" and "paired-pulse depression (PPD)" which are the biological neuron's short-term plasticity phenomena. The leaky-integrate and fire (LIF) neuron model elaborately describes these biological neuron's properties<sup>1</sup>.

To demonstrate the gradual TiO<sub>x</sub> based memristor as an artificial neuron device, PPF and PPD characteristics of the device are tested with the different presynaptic spike frequencies as shown in Fig. 3b. The different pulse intervals (200  $\mu$ s and 1500  $\mu$ s) are applied to the 10×10  $\mu$ m<sup>2</sup> gradual TiO<sub>x</sub> memristor, while the input voltage amplitude and width (3 V, 100  $\mu$ s) keep constant. The memristor conductance increases with high input pulse frequency (3,333 Hz), while it decreases with low frequency (625 Hz). This means that the short-term memory effect of the gradual TiO<sub>x</sub> memristor induces a short-term potentiation and depression, which is analogous to the short-term plasticity of the biological neuron.

In addition to the short-term plasticity, the gradual  $TiO_x$  memristor-based LIF neuron is constructed with a parallel capacitor and a serial resistor (see Fig. 3c and 3d). The parallelly connected volatile memristor and capacitor operate as a LIF neuron's soma, where the biological neuron integrates spikes and makes an action potential when the membrane potential reaches the threshold. The resistor (or non-volatile memristor) that serves as a synaptic weight is serially connected to the gradual  $TiO_x$  based volatile memristor and capacitor<sup>2,3</sup>. To examine the neuron operation without non-ideality factors from the synapse device, a fixed resistor is utilized. The resistance is low if synaptic weight is high, and it is high if synaptic weight is low. If the parallel capacitor integrates enough charges from presynaptic spikes in a certain time interval, the capacitor voltage becomes high enough to potentiate the volatile memristor. For example, The LIF neuron operation of the gradual  $TiO_x$  memristor-based artificial neuron with a 47 k $\Omega$  resistor and a 10 nF capacitor is shown in Fig. 3c. After applying two presynaptic voltage pulses, the neuron reaches the threshold voltage and fires.

The artificial neuron's characteristics in terms of input spike frequencies are investigated in Fig. 3e, 3f, and 3g. The two different frequency spike trains (3,200 Hz, and 1,600 Hz) are applied to the memristor-based artificial neuron. When the frequency is high, the neuron fires within three spikes. However, the neuron does not fire if the input spike frequency is low at

1,600 Hz. This is because the developed neuron has leaky-integration property, and the capacitor voltage does not reach the threshold voltage.

Furthermore, in a biological neuron, the neuron easily fires when it receives spikes from a strongly connected presynaptic neuron, while it requires much more spikes to fire when the presynaptic neuron is weakly connected. This biological phenomenon is emulated in our artificial neuron by modifying the synaptic weight from the serial resistor (see Fig. 3h, i, and j). When an artificial neuron is composed of a gradual TiO<sub>x</sub> memristor, a serial resistor (47 k $\Omega$ ), and a parallel capacitor (10 nF), three presynaptic spike pulses are needed to make the neuron fire (see Fig. 3c). If the serial resistance increases to 94 k $\Omega$ , that represents a weak connection to the presynaptic neuron, the artificial neuron needs six consecutive spikes to fire (see Fig. 3h). On the other hand, if the serial resistance decreases to 23.5 k $\Omega$  representing a strong synaptic connection, the artificial neuron fires within two spikes as shown in Fig. 3i. In a human's biological neural network, the synaptic weight is long-term potentiated when the postsynaptic neuron fires just after the presynaptic neuron fires, because it means the post-synaptic neuron's firing event is strongly related to the presynaptic neuron's firing. This biological phenomenon is called a "Hebbian learning rule", and this is considered as a basic learning mechanism of biological neural networks<sup>4</sup>. The results show that the memristor-based artificial neuron behaves as the biological LIF neuron, and therefore, can be utilized for reliable neuromorphic processors with biological learning rules.

To build a reliable neuromorphic processor with memristor-based neurons, a highly reliable neuron operation is required. In Figure 3k and 3l, the gradual  $TiO_x$  memristor-based artificial neurons show similar neuron responses, which means the proposed memristor based artificial neuron has low device-to-device variation. The identical spike trains are applied to the randomly selected 22 artificial neurons, and the outputs of the neurons are shown in Fig. 3k. Every neuron operates in the same manner, without any noticeable differences. Moreover, we also test the cycle-to-cycle uniformity by applying the same pulse train 50 times to a single artificial neuron (see Supplementary Fig. 10). The response of the artificial neuron is not significantly different, demonstrating its low cycle-to-cycle variation. The low variation of the artificial neuron originates from the reliable switching behavior of the gradual  $TiO_x$  memristor.

To further investigate the characteristics of the gradual TiO<sub>x</sub> memristor-based artificial neuron, the artificial neuron's responses are measured in terms of presynaptic spike amplitude and presynaptic spike width (see Supplementary Fig. 11 and 12). As shown in Supplementary Fig. 11, the artificial neuron does not fire with a small amplitude of the presynaptic spikes (2.5 V), but it fires with a large amplitude of the spikes (>3.5 V). In Supplementary Fig. 12, it is demonstrated that the neuron can operate with a short pulse (40  $\mu$ s). Moreover, the artificial neuron's responses with the different combinations of the circuit components are measured; (1) different capacitance values and (2) different capacitance and resistance values while keeping the same R×C value (see Supplementary Fig. 13 and 14). The developed artificial neuron has a great tunability to adjust the threshold, by changing the parallelly connected capacitor or the serially connected resistor.

The gradual TiO<sub>x</sub> memristor-based neuron demonstrates superior device-to-device and cycleto-cycle uniformity, tunability, low spike current (10~35  $\mu$ A), high off-state resistance (~100

### M $\Omega$ ), and an acceptable speed (>40 $\mu$ s). The comparison table to the various memristor-based artificial neurons is shown in Supplementary Table 1."

#### (5) Comparisons to the existing devices as an artificial neuron

Furthermore, as the reviewer suggested, we provide comparisons with other devices as LIF neurons to demonstrate the improvements. We compare the gradual  $TiO_x$  memristor to other memristors in terms of the artificial neuron in Table R1. As shown in Table R1, the diffusive memristor-based neurons are fast and have high off-state resistances, which are great for energy efficiency by preventing the leakage current, but they have significant uniformity problems because of the stochastic nature of the ionic movement. The Mott transition type memristor-based neurons are the fastest memristor-based neurons. Therefore, they have been used to imitate several characteristics of biological neurons. However, the low off resistance of the Mott transition memristors causes power consumption. To realize a reliable neuromorphic processor, the artificial neuron should have properties such as acceptable speed, great uniformity, high endurance, low current consumption, and high off resistance.

| Device structure                                       | Operation<br>mechanism     | Cycle-to-cycle<br>variation            | Device-to-device<br>variation | Endurance              | Spike peak<br>current (µA) | Power at<br>spike peak<br>(µW) | Off resistance (R <sub>off</sub> )<br>(ΜΩ) |

|--------------------------------------------------------|----------------------------|----------------------------------------|-------------------------------|------------------------|----------------------------|--------------------------------|--------------------------------------------|

| Pt/gradual oxygen<br>concentrationTiO <sub>x</sub> /Ti | Ionic                      | 1.39%                                  | 3.87%                         | > 5×10 <sup>6</sup>    | 10~35                      | 35                             | 100                                        |

| Pt/SiO <sub>x</sub> N <sub>y</sub> :Ag/Pt [R5, R6]     | Ionic (diffusion<br>of Ag) | N/A                                    | N/A                           | N/A                    | 20                         | 10                             | 200                                        |

| Ag/SiO <sub>2</sub> /Au [R7]                           | Ionic (diffusion<br>of Ag) | N/A                                    | N/A                           | N/A                    | 23                         | 0.5                            | 10,000                                     |

| Pt/TiN/NbO <sub>2</sub> /TiN/W [R8]                    | Mott                       | Good, but not<br>quantitively analyzed | N/A                           | > 10 <sup>6</sup>      | 1,500                      | 133                            | N/A                                        |

| Pt/Ti/NbO <sub>x</sub> /Pt/Ti [R9]                     | Mott                       | Good, but not<br>quantitively analyzed | N/A                           | > 109                  | 800                        | 392                            | 0.1                                        |

| Pt/VO <sub>2</sub> /Pt [R10]                           | Mott                       | Good, but not<br>quantitively analyzed | d <sup>7%</sup>               | > 26.6×10 <sup>6</sup> | > 60                       | 11                             | 0.01                                       |

| TE/VO <sub>2</sub> /BE [R11]                           | Mott                       | N/A                                    | N/A                           | 10 <sup>9</sup>        | 200                        | 11.9                           | 0.1                                        |

**Table R1. Comparisons with various memristor-based artificial neurons.** To demonstrate the effectiveness of the gradual  $TiO_x$  memristor-based artificial neuron for the reliable and energy-efficient artificial neuron, several characteristics are compared to the existing artificial neuron devices. The gradual  $TiO_x$  memristor-based neuron shows advantages in terms of uniformity, low spike peak current, and high off-state resistance, and therefore, it is proper for the artificial neuron device with high reliability and low power consumption.

#### (6) Comparisons to the existing devices as a reservoir

We also provide comparisons to other devices as a reservoir in the Table R2. In Table R2, characteristics of several memristors that have been used for RC are compared to the gradual  $TiO_x$  memristor. As shown in the Table R2, the uniformity of the reservoir devices has been rarely studied, even though the cycle-to-cycle and device-to-device uniformity are essential for training and inference of the memristive RC system. The developed gradual  $TiO_x$  memristor has superior uniformity, high on/off ratio, high endurance, and fast speed, which are necessary properties for the memristor-based RC.

| Device structure                                       | Array size                | On/off ratio | Cycle-to-cycle<br>variation            | Device-to-device<br>variation | e Pulse amplitude<br>and width                       | Endurance           | Rectification<br>ratio |

|--------------------------------------------------------|---------------------------|--------------|----------------------------------------|-------------------------------|------------------------------------------------------|---------------------|------------------------|

| Pt/gradual oxygen<br>concentrationTiO <sub>x</sub> /Ti | 20 × 20<br>Crossbar array | > 2,000      | 1.39%                                  | 3.87%                         | Write : 4.5 V, 10 μs<br>Read : 1.5 V, 100 μs         | > 5×10 <sup>6</sup> | 104                    |

| Au/Pd/Wo <sub>x</sub> /W [R12]                         | 32 × 32<br>Crossbar array | N/A          | N/A                                    | N/A                           | Write : 1.5 V, 1 ms<br>Read : 0.5 V, 500 μs          | N/A                 | N/A                    |

| Au/Pd/Wo <sub>x</sub> /W [R13]                         | 32 × 32<br>Crossbar array | N/A          | N/A                                    | N/A                           | Write : 3 V, 10 $\mu$ s<br>Read : 0.6 V, 200 $\mu$ s | N/A                 | N/A                    |

| Pt/SiO <sub>x</sub> N <sub>y</sub> :Ag/Pt [R14]        | Stand-alone               | > 104        | N/A                                    | N/A                           | Write : 1.25 V, 100 μs<br>Read : 0.1 V, 300 μs       | > 10 <sup>6</sup>   | N/A                    |

| Pt/TaO <sub>y</sub> /TiO <sub>x</sub> /Ti [R15]        | Stand-alone               | N/A q        | Good, but not<br>quantitively analyzed | d N/A                         | Write : -2 ~ 2 V, 120 μs                             | N/A                 | 10 <sup>3</sup>        |

| Au/Cr/SnS flake/Au/Cr<br>[R16]                         | 1	imes 10 array           | < 2          | N/A                                    | N/A                           | Write : 4.5 V, 20 ms<br>Read : 1 V, 25 ms            | N/A                 | N/A                    |

Table R2. Comparisons with other various memristors for reservoir computing. To demonstrate the effectiveness of the gradual  $TiO_x$  memristor as a RC device, several characteristics of the device are compared to the various memristors used for RC. The gradual  $TiO_x$  memristor satisfies the superior uniformity, high on/off ratio, fast speed, high endurance, and high rectifying ratio for sneak path problems simultaneously.

To clarify the improvements in terms of the artificial neuron and the RC system, we appended Table R1, Table R2, and corresponding sentences to Supplementary Table 1 and Supplementary Table 2.

In addition, the following sentences are appended in the conclusion section:

Page 22, line 474: "The newly developed memristor is utilized for memristor-based LIF neuron, and it shows several superior characteristics such as high uniformity, tunability, and low operation current (see Supplementary Table 1)."

Page 22, line 491: "The comparisons with the memristors in the previous works for the reservoir computing are shown in Supplementary Table 2."

(7) Designed circuit for gradual TiO<sub>x</sub> memristor-based RC

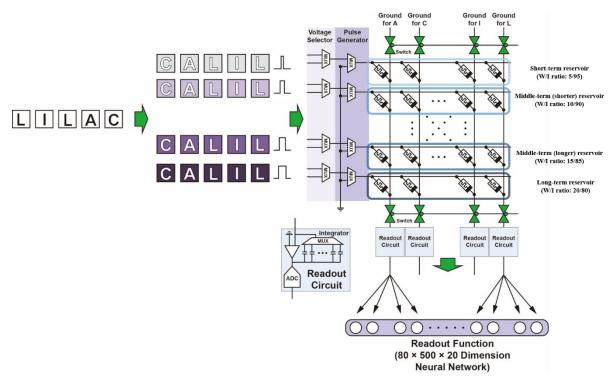

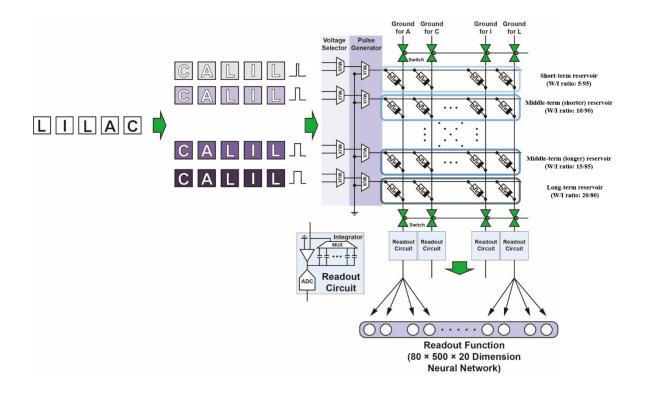

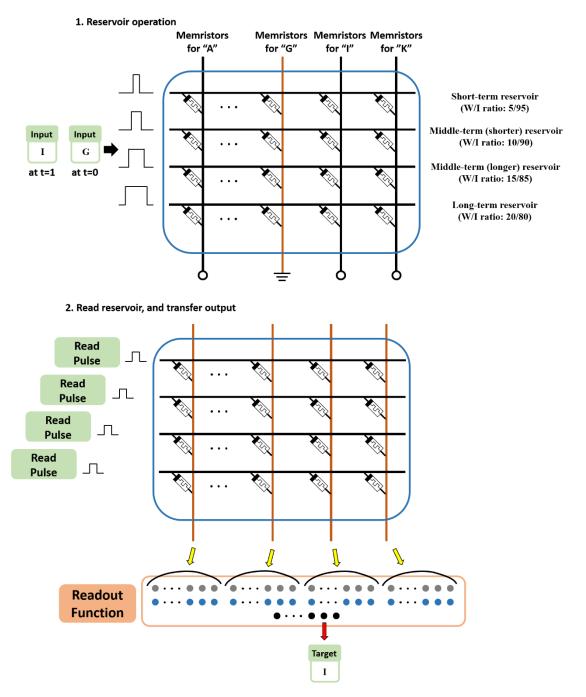

To show the feasibility of the memristor-based artificial neuron and RC, we propose a complete circuitry for the memristor-based artificial neuron and RC. The circuitry for the artificial neuron is already shown in the Figure R4 and R5. The complete circuitry of the proposed RC system in our study is in Figure R15.

The memristive RC system is composed of a highly reliable dynamic memristor array and peripheral circuitry. Each sequence element (character) is assigned to a different column of the cross-bar array. Each row of the cross-bar array is a single sub-reservoir, and memristors in different rows have different W/I ratios (duty cycles). The sequence data is transformed to the pulse train of desired duty cycles for each row by the pulse generator. The feeding voltage between set voltage and read voltage is chosen by the voltage selector. The switches determine the selected column for a character. The selected column is grounded, while others are floating. Each readout circuit, composed of an integrator and an analog-digital converter (ADC), is connected to corresponding column. The readout circuit measures the current of the memristors in a single row at the same time. The current level of each row will be different because of the different duty cycles. The long-term reservoir (the biggest W/I ratio) has the largest current level, while the short-term reservoir (the smallest W/I ratio) has the smallest current level. To compensate the difference of the current magnitude, two methods can be utilized; (1) The range of the output of an integrator can be controlled by different capacitances and a multiplexer (MUX), or (2) the longer read pulse can be used for the short-term reservoir to increase the charged data of the capacitor in the readout circuit. The outputs from each memristor device are mapped to each node of the readout function, and the readout function trains its weights with backpropagation method based on the discrepancy between the readout function output and the target data.

### Figure R15. A circuit schematic for the memristive RC composed of the highly reliable dynamic memristor array and the peripheral circuit.

To inform the information about the designed circuitry for the RC system, we added sentences as following:

Page 19, line 412: "To simulate the memristive RC based on the measured data from memristor arrays, we design a whole system for memristive RC on a circuit level (see Supplementary Fig. 19)."

Figure R15 is added in Supplementary information as Figure S19.

(8) Improved abstract, introduction, and conclusion to include the results of the artificial neuron

Because the memristor for the reservoir computing also requires short-term memory effect and leaky-integrate properties of a neuron, we have expanded our work from RC devices to artificial neuron devices. The proposed device can be widely used from the bio-plausible neural networks to the reservoir computing. To reflect the changed focus correctly, we have revised the abstract, introduction, and conclusion sections.

We have revised the abstract as following:

Page 2, line 16: "Neuromorphic computing, a computing paradigm inspired by the human brain, enables energy-efficient and fast artificial neural networks. To process information, neuromorphic computing directly mimics the operation of a biological neuron, which has synaptic plasticity and firing properties. To effectively imitate biological neurons with electrical devices, memristor-based artificial neurons attract great attention because of their simple structure, energy efficiency, and excellent scalability. However, memristor's nonreliability issues have been one of the main obstacles for the development of memristor-based artificial neuron and neuromorphic computing. Here, we show a memristor 1R cross-bar array without transistor devices for individual memristor access with low variation, 100% yield, large dynamic range, and fast speed for artificial neuron and neuromorphic computing. Based on the developed novel memristor, we experimentally demonstrate a memristor-based neuron with leaky-integrate and fire (LIF) property with excellent reliability. Furthermore, by using this newly developed memristor neuron's leaky-integrate property, we develop a memristive reservoir computing (RC) system, a type of neuromorphic computing, for efficient processing of sequential/temporal data. Our new memristive RC system successfully trains and generates bio-medical sequential data (antimicrobial peptides) while using a small number of training parameters. Our results open up the possibility of a memristor-based artificial neuron and neuromorphic computing system, which is essential for energy-efficient edge computing devices."

We have modified the introduction as following:

Page 3, line 34: "Artificial neural networks (ANNs) have shown their effectiveness in various fields such as autonomous cars, finding new drugs, designing circuits, or predicting protein structures<sup>17-20</sup>. Powered by today's elaborate complementary metal-oxide-semiconductor (CMOS) based computing processors, ANNs accomplish highly complex tasks. However,

ANNs running in a conventional von Neumann architecture computer (e.g. graphic processing units (GPU)) cannot not reach the efficiency of a biological neural network due to the bottleneck of big data transfer<sup>8</sup>. To substitute the conventional ANNs, neuromorphic computing hardware, which imitates the operation of the brain and biological neural network, has been extensively studied. The conventional CMOS-based neuromorphic hardware uses complex CMOS circuitry to imitate the neuronal activity<sup>21</sup>. However, CMOS-based complex circuitry limits scalability and increases energy consumption. Thus, it is difficult to reach the efficiency of a biological neural network using CMOS-based neuromorphic hardware<sup>10</sup>.

Memristors, instead of the CMOS-based circuit, have been widely studied as a new candidate for neuromorphic hardware. Memristors are emerging memory devices that store information in the form of resistance by changing the internal distribution of oxygen anions or metal cations<sup>22,23</sup>. They are a promising candidate for an artificial neuron device for neuromorphic hardware because of their great scalability, high energy efficiency, fast speed, small footprint, and simple fabrication process. Previous studies have developed several memristive artificial neurons and proved that memristors are proper devices for efficient artificial neurons. Short-term (volatile) memristors are used to represent two different biological neuron properties; a short-term potentiation and depression property, called paired-pulse facilitation (PPF) and paired-pulse depression (PPD), and leaky-integrate and firing (LIF) property of a biological neuron. Instead of being used for a synapse, short-term memristors are widely used for various neuromorphic computing systems such as reservoir computing (RC) and spiking neural network (SNN)<sup>2,3,13,14</sup>.

Despite these advantages, the current memristor-based artificial neuron has several limitations. Various studies have proven the feasibility of memristor-based neuron, by unambiguously showing neuronal operations such as LIF and short-term plasticity. Among them, diffusive memristors (SiO<sub>x</sub>N<sub>y</sub>:Ag) or Mott memristors (NbO<sub>2</sub> or VO<sub>2</sub>) have been extensively studied as artificial neuron device<sup>3,6,10</sup>. The diffusive memristor type neurons are fast and have high on/off ratio, and the Mott memristor type neurons have acceptable uniformity and fast speed. However, the diffusive memristor yupe neurons have uniformity issues, and Mott memristors require a large operation current (~mA). In general, memristors usually suffer from large variation problems and unreliable switching<sup>22-24</sup>. These reliability problems degrade the memristorbased neuron performance and make it difficult to build large-scale memristor-based neuromorphic computing hardware. Even though reliable memristors may exist, it is difficult to operate a memristor-based cross-bar array without other components, such as selectors and transistors, because undesired current paths, which are called sneak paths, hinder the reliable read and set/reset operations in a memristor cross-bar array<sup>22</sup>. In addition, the low on/off ratio increases the complexity of the peripheral circuit that is needed to distinguish the small conductance change of the memristor, and high current requirement (~mA) increases the energy consumption. To overcome these bottlenecks, development of a new memristor that satisfies all of the requirements is warranted.

Here, we propose a transistor-free 1R structure memristor that consists of metal oxide with gradual oxygen concentrations that are fabricated in low-temperature environments for memristor-based artificial neuron and memristive RC system construction. We demonstrate that this memristor performs with high yield in array form (~100%), obtains self-rectifying behavior, has high temporal/spatial uniformity (1.39% and 3.87%, respectively), high

endurance without degradation (>  $10^6$ ), high speed ( $10 \mu$ s), and a consistent time constant (~40 ms) in the array. Based on these ideal properties, we show that the developed memristor-based artificial neuron possesses paired-pulse facilitation (PPF), paired-pulse depression (PPD), and leaky-integrate and fire (LIF) characteristics, which are the key characteristics of a biological neuron. The developed neuron has high spatio-temporal uniformity, which is one of the essential features for building a reliable memristor-based neuromorphic processor. In addition to the artificial neuron, we build a memristive RC system by using the memristors as leaky-integrate neurons. The developed memristive RC can deal with sequential data, which can provide further complications compared to temporal data processing. With the developed memristive RC, anti-microbial peptides (AMPs), the anti-bacterial elements in the innate immune system, are utilized. The memristive RC, trained by AMP data, successfully learns the complex amino-acid grammar of AMPs and generates new AMPs."

We have changed the conclusion as following:

Page 21, line 468: "In summary, we developed a novel  $20\times20$  high-density memristor array by utilizing gradual oxygen concentration metal oxide, which possesses a high on/off ratio, excellent temporal/spatial uniformity, self-rectification, forming-free property, compliance current-free property, and high yield for a memristor-based neuromorphic system. Unlike the other existing memristors operating with conductive filaments, our gradual TiO<sub>x</sub> memristor switches its resistive state through oxygen migration without strong filament formation and changes the effective insulator thickness. It showed dynamic analog operations, such as potentiation (set), depression (reset), and self-decaying. The newly developed memristor is utilized for memristor-based LIF neuron, and shows several superior characteristics such as high uniformity, tunability, and low operating current (see Supplementary Table 1). It is demonstrated that the gradual TiO<sub>x</sub> memristor-based artificial neuron has similar features to the biological LIF neuron by modifying the presynaptic spike or the capacitance of the artificial neuron. Based on the outstanding characteristics of the gradual TiO<sub>x</sub> memristor-based neuron, our results open up a path to developing a reliable and energy-efficient neuromorphic processor with biological learning rules.

Furthermore, the gradual TiO<sub>x</sub> memristor cross-bar array as a short-term, leaky-integrator is used to create a hardware-based reservoir computing system. The newly developed memristive RC system learns the AMP sequences and generates new AMP candidates. To improve the performance of the memristive RC system, the multiple sub-reservoirs with different pulse width/interval ratios are utilized. The multiple sub-reservoir effectively expands the reservoirs' dimensionality, where short-term reservoirs memorize recent information with short decaying time constant while long-term reservoirs memorize information for a long period with long decaying time constant. Multi-reservoir memristive RC with the gradual TiO<sub>x</sub> memristor having excellent uniformity could be used for mass-production because the trained readout function will have weights that are matched to the reservoir in every single chip. Because of the reduced training cost by substituting the recurrent layer of the RNN into the reservoir, the memristive RC system can be suitable for online learning with high accuracy. The comparisons with the memristors in the previous works for the reservoir computing are shown in Supplementary Table 2. In addition, several superior properties, including self-rectification, forming-free, low temperature fabrication, and high on/off ratio make the gradual TiO<sub>x</sub> memristor suitable for memristive RC system.

The proposed highly reliable memristor can be broadly used in neuromorphic processors that handle bio-plausible neural networks such as spiking neural networks or reservoir computing. Further improvements such as peripheral control circuits, non-volatile memristor arrays as synapses, and the developed reliable artificial neurons for building SNN or RC system can be used for several practical applications including image classifications, speech recognitions, or real-time diagnosis with effectively reduced energy consumption and device size."

#### Comment #5:

RC models have less parameters than LSTMs and RNNs. This statement holds true for LSTMs which have complex gating models, but they have an equivalent number of parameters as RNNs. The only other benefit for RC is the reduced training cost but from the discussion in the paper it does not focus on online learning. Rather they discuss a fixed, pre-trained readout which can be deployed to multiple crossbars due to the uniform nature of their fabrication.

**Response:** Thank you for the constructive comment. As the reviewer mentioned, the benefit of the RC compared to the RNN is the reduced training cost. We agree that it is essential to discuss the advantages of RC in training as well as inference.

To address the point, first, we have corrected the sentence stating RC has fewer parameters than RNN.

Page 15, line 304: "RC is a type of neuromorphic computing that processes sequential/temporal data. Conventional recurrent neural network (RNN) and a long short-term memory (LSTM), which are widely used neural networks for sequential/temporal data, have a complex and repeated recurrent layer, and the recurrent layer makes the training cost increase. On the contrary, in the RC, the "reservoir" transforms sequential/temproal data into a high dimensional basis by using a short-term memory effect of the reservoir without complex calculations. The input data, processed by the reservoir, is fed to the readout function. The readout function is usually a simple fully connected network and trains its weights by using a conventional machine learning algorithm."

In addition, we have appended the advantages of the developed RC system for online training with the reliable memristor-based hardware. Cycle-to-cycle variation (or temporal variation) induces errors in the reservoir output for every input, and this variation may limit the online training. However, because the newly developed memristor has superior uniformity, stable online training without significant errors in the reservoir can be achievable. We have added the sentence as following:

Page 22, line 487: "Multi-reservoir memristive RC with the gradual  $TiO_x$  memristor having excellent uniformity could be used for mass-production because the trained readout function will have weights that are matched to reservoir in every single chip. Because of the reduced training cost by substituting the recurrent layer of the RNN into the reservoir, the memristive RC system can be suitable for online learning with high accuracy"

#### Comment #6:

Beyond that, at a high level the claim this as an RC computing model requires serious validation. From all the tests and architectures described there is no recurrent network. Rather, from the way it is presented, a set of memristors that act as leaky integrators are implemented and readout the final state of each individual memristor for classification. This is not a true RC model, and it is not clear how they treat the inputs to the network in terms of weights. In writing they discuss how the memristors see a combination of inputs, but in the alphabet example it is described as a 1-to-1 mapping where each memristor only sees a single input. A similar setup is described for the AMP sequences.

#### **Response:**

Thank you for your valuable comment. As the reviewer pointed out, the developed RC system does not have recurrence among different characters, but the recurrence only exists for each character. This is similar to the RNN which has a weight matrix that is composed of non-zero diagonal elements while other elements are zero; for example, if the sequence is a multi-dimensional vector, where the length of the vector is the length of the sequence and the dimension is the number of unique characters, there is no recurrence among each dimension. Therefore, we used a simple MLP with an activation function, because there is no non-linear connection between different characters (dimensions). In this point of view, the developed RC system is not an ideal RC, as the reviewer commented.

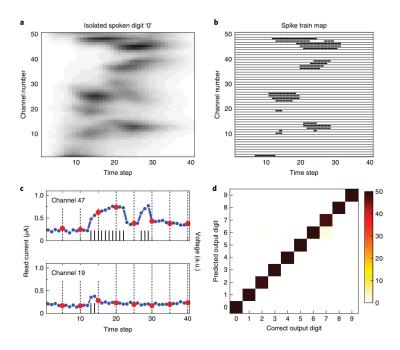

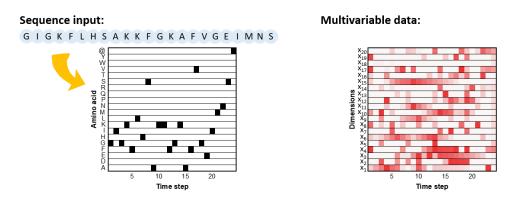

Even though the RC system in this work is not an ideal RC, similar setups have been demonstrated for some applications. In a pioneering study, a memristor-based RC system has classified the number pronounced by human voice (Moon, J. et al. [Nat. Electron., 2019]) and this work utilizes a similar setup (1-to-1 mapping of frequency range and memristor). In the work by Moon, the voice data is transformed into time-frequency data having a length in 50 (time step) and 50 channels (dimensions), as shown in the Figure R16. Each channel represents a specific frequency region and is assigned to one of the memristors. By using this method, the study obtained 99.2% classification accuracy and the result shows that matching a single variable to a single memristor can be used for RC handling multivariable data. However, as the reviewer mentioned, there is no recurrence among different channels in this type of RC system. Therefore, this approach has a limitation if the recurrence among different channels, dimensions, or characters is significant for the used data. In our work, even though this approach is not an ideal RC, it is still effective for some sequence data, which is barely studied with memristive RC, unlike single-variable time-series data. It shows great performance for the given sequence data (antimicrobial peptides). We modified the manuscript that might cause misunderstandings about the non-ideal RC system.

Figure R16. Classification of spoken digits with memristive RC in the work by Moon, J. et al. [*Nat. Electron.*, 2019]. a and b, The spoken digit data has 50 channels (frequency domain) and 50 lengths (time step) and it is converted into the digitized spike trains. c, The temporal responses of the memristors. The memristors are assigned for each channel. d, The classification results from the memristive RC.

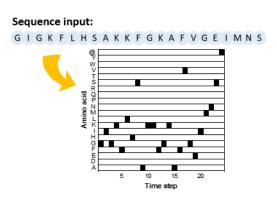

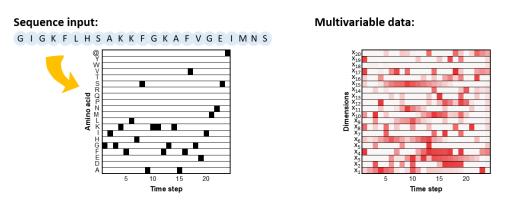

To clarify that the unique character in the sequence is considered as a channel or a dimension of a multivariable vector, we added the Figure R17 as a Figure 5b and corresponding sentences to show that the sequence data used for the RC is transformed into a multi-dimensional vector where each unique character represents each dimension of the vector:

Page 19, line 417: "First, the input sequence is transformed into a 20-dimensional (or 20channel) vector having the same time step to the original sequence data. Each memristor in a reservoir processes the spike train from the one channel (one amino-acid) among the 20 channels in the transformed input data (see Figure 5b)."

Figure R17. An illustration of the transformation of an input sequence into a 20dimensional vector (or 20-channels) with 24-time steps, where 20 is the number of the unique amino-acids in the input sequence with the added end-cursor "@", and 24 is the length of the sequence after adding the end-cursor. Furthermore, as the reviewer commented, there is little information about how input data is treated at the readout function, or the neural network level. After the input data is processed in the reservoir, the reservoir output is the input of the readout function, which is a simple multilevel perceptron neural network of the reservoir computing system. Because there are four reservoirs and each of them has 20 memristors, the reservoir output is a  $1 \times 80$  vector. This vector is the input of the readout function, and the readout function trains its weights by using the next amino-acid element as a target (label). The readout function has a three-layered structure with 80, 500, and 20 neurons for each layer. The first layer is the reservoir output itself, thus, the layer size is  $1 \times 80$ . The first and second layers use a ReLU as an activation function while the last layer uses a soft-max as an activation function. Even though there is no connection among each variable in a reservoir, the RC system well trains its weights, because each node of the reservoir output is non-linearly connected in the readout function. A categorical cross-entropy is used for the loss function, which is widely used for prediction or classification tasks. In summary, the RC system learns the amino-acid grammar of the AMP sequence, by predicting the next input from the training data.

To inform this information, we have added the Figure R15 in Supplementary Fig. 19, which shows how the memristive RC system receives input and processes the input with the reservoir and the readout function.

#### Comment #7:

## By framing the device contributions in the light of new neuron circuits and generalizable models, there could be lot more merit to this paper, rather than presenting it as an RC memristor.

**Response:** Thank you very much for the constructive comment and for suggesting the use of our device as an artificial neuron. As the reviewer suggested, the proposed device can be used as an artificial neuron for several important future applications such as bio-mimicking robotics, spiking neural networks, and reservoir computing. The manuscript now is focused on the two results; the artificial neuron that mimics the biological LIF neuron model, and the memristor-based reservoir computing system that requires short-term neurons (or leaky-integrators) as a reservoir. To demonstrate that the gradual TiO<sub>x</sub> memristor can be utilized as an artificial neuron and to show the advantages of the neuron, we added the Figure 3 in the main text of the manuscript, as shown in the Figure R18. The corresponding subsection "Reliable LIF neuron with gradual TiO<sub>x</sub> memristor" is added in the main text, as we discussed in the **comment #4**.

Figure R18. Gradual TiOx memristor-based LIF neuron.

#### Comment #8:

Another concern is that the authors discuss the high-dimensional basis used for classification, but if every memristor is only a filtered version reflecting the activity of a single input category, each device belonging to the same input should be the same. This is almost like concatenating the input multiple times, but not truly expanding to a high-dimensional space where the input would become linearly separable. In this setup, one cannot see the need to use more devices than the number of unique input characters.

**Response:** Thank you for this helpful comment. The memristors with different W/I ratios have different potentiation ratios and decaying time constants. As shown in the Figure R19, the potentiation ratio and the decaying speed are dependent on W/I ratio. Therefore, even though the memristors receive the same input, they do not have linear relationships; the history of each character differently affects the memristor state because of the different potentiation ratios and decaying speeds.

As shown in Figure R20 (Figure 3d-f in the original manuscript), the final outputs are different due to different W/I ratios, even though the inputs are identical. If the W/I ratio is high, it stores the history of the character strongly because of the slow decaying speed. In the given sequence "DDDCCBDCCDBADBACDCBA", the character "D" is the most frequently appearing character, and "A" is the least frequently appearing character. Therefore, with high W/I ratio (85/15), the largest outputis "D". If the W/I ratio is low, it represents the recent information. As a result, the largest output is "A" with low W/I ratio (15/85).