Abstract

Due to the rise of 5G, IoT, AI, and high-performance computing applications, datacenter traffic has grown at a compound annual growth rate of nearly 30%. Furthermore, nearly three-fourths of the datacenter traffic resides within datacenters. The conventional pluggable optics increases at a much slower rate than that of datacenter traffic. The gap between application requirements and the capability of conventional pluggable optics keeps increasing, a trend that is unsustainable. Co-packaged optics (CPO) is a disruptive approach to increasing the interconnecting bandwidth density and energy efficiency by dramatically shortening the electrical link length through advanced packaging and co-optimization of electronics and photonics. CPO is widely regarded as a promising solution for future datacenter interconnections, and silicon platform is the most promising platform for large-scale integration. Leading international companies (e.g., Intel, Broadcom and IBM) have heavily investigated in CPO technology, an inter-disciplinary research field that involves photonic devices, integrated circuits design, packaging, photonic device modeling, electronic-photonic co-simulation, applications, and standardization. This review aims to provide the readers a comprehensive overview of the state-of-the-art progress of CPO in silicon platform, identify the key challenges, and point out the potential solutions, hoping to encourage collaboration between different research fields to accelerate the development of CPO technology.

Graphical Abstract

Keywords: Co-packaged optics, Silicon photonics, High-performance computing, Advanced packaging, External laser, Optical power delivery, Co-simulation, Standardization, Transmitter, Receiver

Introduction1

The importance of co-packaged optics (CPO). Datacenter traffic keeps growing with the expansion of data-intensive applications, such as AI and high-performance computing (HPC). Conventional pluggable optics cannot catch up with the fast-growing bandwidth density and energy efficiency requirements. Co-packaged optics (CPO) combines photonic devices with high-performance electronics via advanced packaging to form a solution that shortens the SerDes distance significantly, greatly reducing power consumption.

Aim and Organization. The primary purpose of this paper is to provide an overview of the state-of-the-art progress of CPO, and identify the key challenges and their potential solutions. It is worth noting that the content in this paper is by no means exhaustive for such a rapidly developing field. To provide readers a comprehensive overview, we divide the paper into twelve independent sections. Here, we provide a brief overview of these sections.

2. Device fabrication. An advanced fabrication process and device structure need to be developed for CPO. In the form of 3D integrated CPO, the silicon photonic chip serves as an interposer for shorter traces and lower power consumption. In addition, standard silicon photonics fabrication technology must collaborate with the packaging development.

3. External laser source. The requirement for the laser chip is analyzed. It turns out that the high-power laser and TEC are the primary contributors. Potential solutions to reduce laser power consumption are proposed.

4. Optical power delivery. The optical power delivery system has often been oversimplified or even neglected in recent proposals. This section attempts to address the fundamental problems in optical power delivery from three aspects, specifically, how the power demands are growing, what technologies are required, and what the major challenges are.

5. DSP for CPO. The DSP chip plays an important role in CPO. This section summarizes the electrical requirements for both host-side and line-side links and provides the DSP design considerations, including the transceiver architecture, clocking scheme, and equalization implementations.

6. Microring-based transmitter array for CPO. Micro-ring modulator has small area, high power efficiency, and is compatible with wavelength division multiplexing, making it a promising candidate for CPO. However, it suffers from many challenges, such as wavelength control and polarization sensitivity. This section summarizes the challenges and recent advances of microring-based transceiver array and provides suggestions to meet these challenges.

7. Mach–Zehnder modulator (MZM) based transmitter for CPO. MZM has already been commercialized and is a promising solution to replacing the existing implementation of pluggable optical modules. However, MZM driver design poses numerous challenges in terms of voltage swing, bandwidth, energy efficiency, and other aspects. This section provides an overview of the MZM transmitter with a focus on its driver design.

8. Optical receiver front-end for CPO. Compared to BiCMOS, the CMOS-based optical receiver is more compatible with CPO in terms of integration, power efficiency, and cost. This section will provide recent advancements in the design of CMOS-based optical receiver front-end electronics, which hopefully will pave the way for future fully integrated electronics IC for CPO.

9. 2.5D and 3D packaging for CPO. 2.5D, 3D packaging technology could achieve high bandwidth and high integration with low power consumption for CPO. This section mainly discusses 2D/2.5D/3D silicon photonic co-packaging module developed by IMECAS, 2D MCM photonic module package issues, and the challenges of silicon photonic wafer-level packaging.

10. Electronic-photonic co-simulation for CPO. Electronic-photonic co-simulation is the prerequisite for large-scale electronic-photonic co-design. However, this field is relatively immature and faces many methodological and engineering challenges. The mainstream approach is to integrate the photonic devices into the electronic design automation platform. This section mainly discusses the challenges and solutions for photonic device modeling, time domain simulations, and frequency domain simulations.

11. System considerations on HPC photonic interconnect. This section breaks down the photonic interconnect link into hardware and software components, discusses accordingly their current status, challenges, as well as how they impact the integrity of the photonic link and network. Finally, this section remarks on the next milestone in the future of photonic interconnect for HPC networking.

12. Optoelectronic hybrid interface in HPC. HPC has been reluctant to switch to new technology due to compatibility considerations. So far, optoelectronic hybrid integration has failed to take advantage of the integration truly. This section analyzes different interconnecting design considerations for CPO and provides suggestions for accelerating the adaption of CPO in HPC.

13. CPO development and standardization. The China Computer Interconnect Technology Alliance (CCITA) has coordinated the efforts across academia and industry to initiate the China CPO standardization. This section provides an overview of the technical and economic considerations of the China CPO standardization efforts.

Advanced silicon photonics fabrication technology for CPO2

Status

Co-packaged Optics (CPO) is an advanced packaging technology for optoelectronic devices that involves upgrades in system architecture, chip fabrication, and packaging. In this section, we will mainly discuss the fabrication technology of silicon photonic chips for CPO applications.

Moore’s Law is a well-known phenomenon in microelectronics chip fabrication. During the last few decades, the number of transistors per chip has been doubling every two years. Similarly, silicon photonics, which claims to benefit from the existing and well-established Complementary Metal-Oxide Semiconductor (CMOS) manufacturing technology, should also follow this scaling trend and aim for the low-cost manufacturing of photonic integrated circuit (PIC) through the economies of scale [25]. However, unlike electronic devices, the scaling of photonic devices is intrinsically difficult. The size of a photonic device is mainly determined by the refractive-index contrast of materials. The global size of silicon photonic devices remains at the micrometer level and will rarely decrease to the nanometer level. Therefore, when we talk about the scaling of silicon photonics, we are talking about how advanced fabrication technology can enable the scaling of photonic packaging.

Current and future challenges

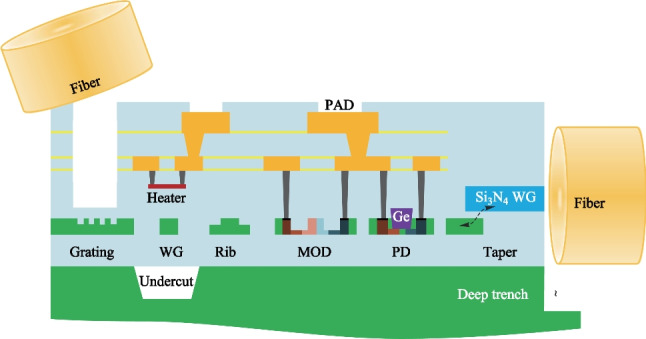

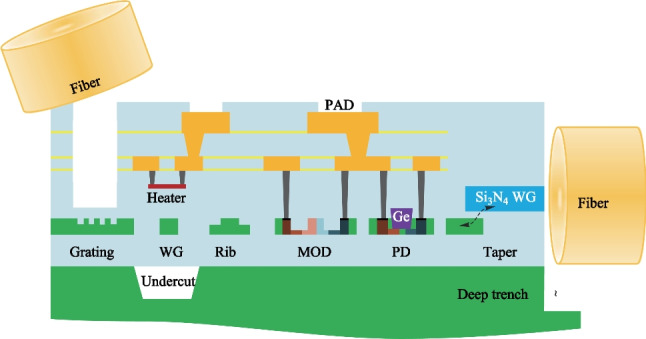

Pure-play foundries, such as TSMC, Global Foundry, TowerJazz, SMIC, and open-access pilot lines, such as IMEC, AMF, AIM, CUMEC are providing silicon photonics PDK with the basic component library of passive and active devices, as shown in Fig. 1. While customized structures are needed for CPO applications, the main fabrication challenges for CPO chips come from fiber coupling and light source integration.

Fig. 1.

Schematic of CUMEC silicon photonics PDK

An efficient fiber coupling structure is necessary for extreme high-density optical I/O. There are two kinds of coupling structures, grating coupler and edge coupler. Grating couplers are normally fabricated via a simple two-step etch process, enabling vertical light coupling. Grating couplers possess a relatively wide alignment tolerance with small optical bandwidth and high polarization sensitivity. Therefore, unlike edge couplers, grating couplers are usually used in wafer-scale testing instead of commercial products. Edge couplers enable small coupling loss and large optical bandwidth, which are desirable for real applications. However, edge coupler requires an undercut and deep etch process during the fabrication process, inducing problems in device stability and reliability. Besides, V-groove structure is developed for passive alignment of fiber edge coupling [26].

On-chip light source integration is one of the main challenges in silicon photonics. It is inherently difficult for silicon-based materials to form a high-performance laser. Heterogeneous integration or heterostructure integration of III-V compound materials on silicon photonic chips is proven to be a viable approach, while major adjustment is required for silicon photonic fabrication process.

In the future, from 2.5D CPO to 3D CPO, CPO technology will evolve to be more than a packaging process, but rather a combination of fabrication and packaging where the co-optimization of design and process is demanded. The packaging concept needs to merge deeply with fabrication process flow.

Advances in science and technology to meet challenges

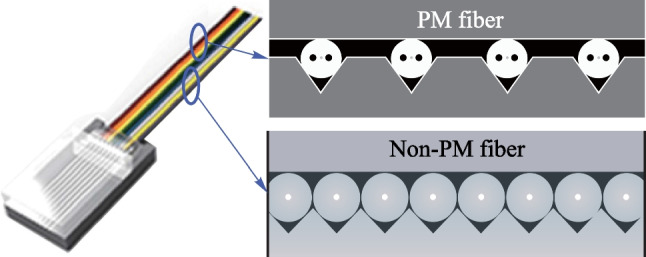

In most current CPO solutions, edge couplers are used in both light-in and light-out paths. The edge coupler is carefully designed to meet the demand of high alignment tolerance and low insertion loss simultaneously. Typical fiber-to-chip loss via passive alignment using V-groove structures could be controlled within − 1.5 dB [27]. Using structures such as thermal phase shifters could help further improve the alignment tolerance [28]. Silicon photonic transceiver serves as an important building block for high-speed switch assembly CPO system, in which several transceiver modules are arranged in close proximity to the switch ASIC. Central switch ASIC is surrounded by hundreds or thousands of fibers with a mixture of polarization-maintaining (PM) fiber and non-PM fiber, posing considerable challenges to fiber routing and packaging with high consistency and quality, as shown in Fig. 2. Adopting high order modulation technology and on-chip light source integration can reduce the number of fibers and difficulty of fiber packaging.

Fig. 2.

Hybrid packaging of PM fibers for light input and non-PM fibers for light output

Furthermore, the wavelength-division multiplexing scheme or TeraPHY [29] could be another solution to addressing larger data flow.

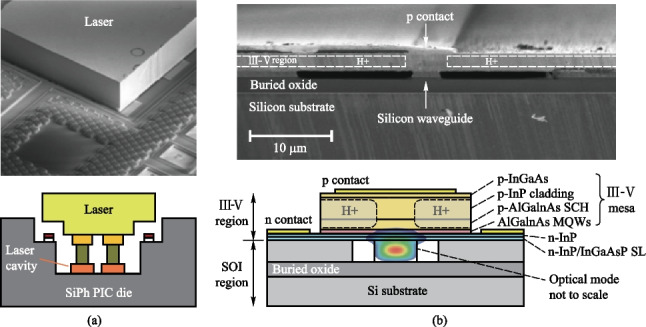

On-chip light source integration methods include heterostructure integration (e.g., laser diode flip-chip bonding) and heterogenous integration (e.g., wafer-level material bonding) (Fig. 3). For the flip-chip bonding method, commercial laser diodes are bonded via eutectic soldering on the silicon photonic chip. Mechanical stops and fiducial marks are used for high precision passive alignment between laser chip and silicon photonic chip [33]. This method utilizes the mature laser diode product for simplified development and quick commercialization. For the wafer-level material bonding method, lasers are formed together during the silicon photonic chip fabrication process [31–33]. The mode converter between III-V material and silicon waveguide requires process modification in the front-end of the line. Laser electrode fabrication induces process altering in the back-end of the line. Overall, the silicon photonic production line requires massive reconstruction for heterogenous integration. For both methods, heat dissipation and strain-induced performance degradation need to be considered for future applications in CPO.

Fig. 3.

a Heterostructure integration [30] and b heterogenous integration [33] of on-chip light source

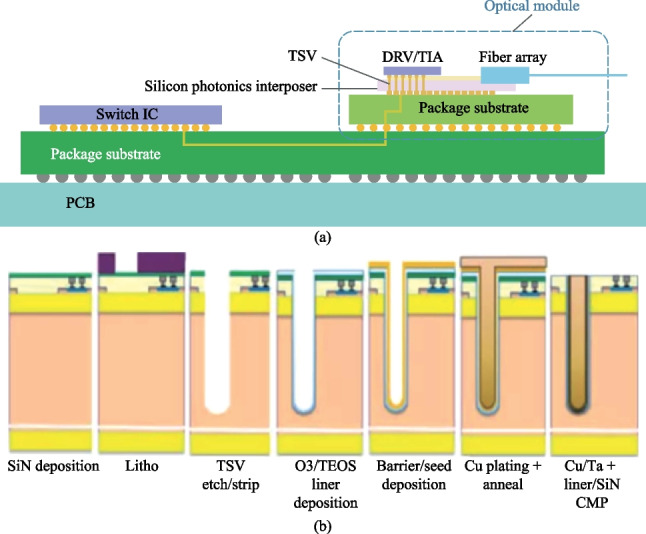

In the form of 3D integrated CPO, the silicon photonic chips serve as an interposer for shorter circuit connections and lower power consumption. Recently, imec has demonstrated a hybrid-assembled optical module embedded with through-silicon via (TSV) structure reaching above 110 GHz RF bandwidth, paving the way for next-generation silicon photonic modules operating at 100Gbaud data rates, as shown in Fig. 4 [34]. The fabrication of TSV on silicon photonic chips requires extra processes, including high-aspect-ratio Bosch deep etch and wafer thinning, which induces potential problems in yield and reliability [35].

Fig. 4.

a Hybrid-assembled optical module using silicon photonic interposer with TSV structures [10]. b TSV fabrication process on silicon photonics interposer [35]

Concluding remarks

Following the trend of integration, standard silicon photonics fabrication technology must adapt with the development of packaging. In order to meet the requirements of CPO, advanced fabrication processes and device structures need to be developed for silicon photonics. It would be more efficient for CPO application designers to work closely with foundries for design-process co-optimization.

External laser source for co-packaged optics3

Status

The laser source is one of the enabling technologies for co-packaged optics (CPO). In the context of silicon photonics based optical engine, two types of laser source are under discussion and development, i.e., on-chip laser and external laser. Each approach has its pros and cons. This session focuses on the option of external laser source (ELS), mainly due to its wider accessibility to the industry.

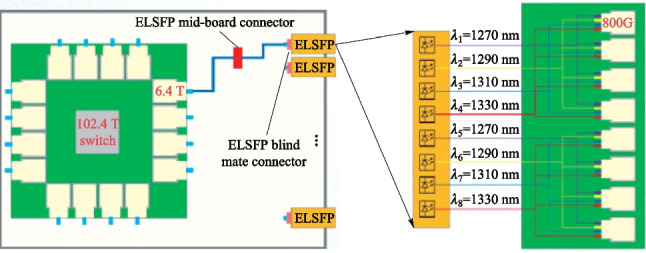

It is believed that the optical connectivity will more likely evolve to CPO form when the switching capacity reaches 102.4 Tbit/s for the data center networking (DCN) application. The CPO tile with a 6.4 Tbit/s optical input/output capacity is required by the 102.4 Tbit/s switch, as shown in Fig. 5.

Fig. 5.

Configuration of co-packaged optics for 102.4 T

The implement method of the 6.4 Tbit/s CPO tile is still under discussion, such as the data rate per lane and parallel or WDM architecture. For the sake of discussion, it is assumed that the 6.4 Tbit/s CPO tile is composed of eight sets of 800 Gbit/s cells, which are implemented by 4 × 200 Gbit/s FR4 configuration. Each 6.4 Tbit/s CPO tile requires an ELS. As shown in Fig. 5, each ELS package is composed of two sets of CWDM4 lasers, i.e., eight lasers in total. Each laser chip powers up to four 800 Gbit/s cells by utilizing a 1 × 4 splitter.

Current and future challenges

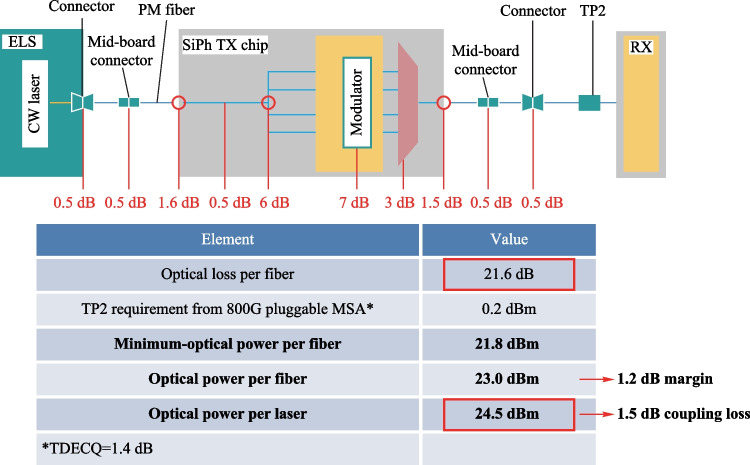

The output power and power consumption are the key features of ELS. The output power requirement of ELS can be derived from the link budget analysis of optical engines.

Table 1 shows the link budget analysis for the output power. It is assumed that the minimum required output power (at TP2) of the optical engine is 0.2 dBm, according to the specification of 800G FR4 [72]. The total insertion loss of the silicon photonic chip is 21.6 dB, as shown in Table 1. Therefore, the minimum required output power of the ELS package is 21.8 dBm. The required output power of the laser chip is 24.5 dBm when taking the laser-to-fiber coupling loss into account and leaving room for margin.

Table 1.

Link budget analysis for the optical engine

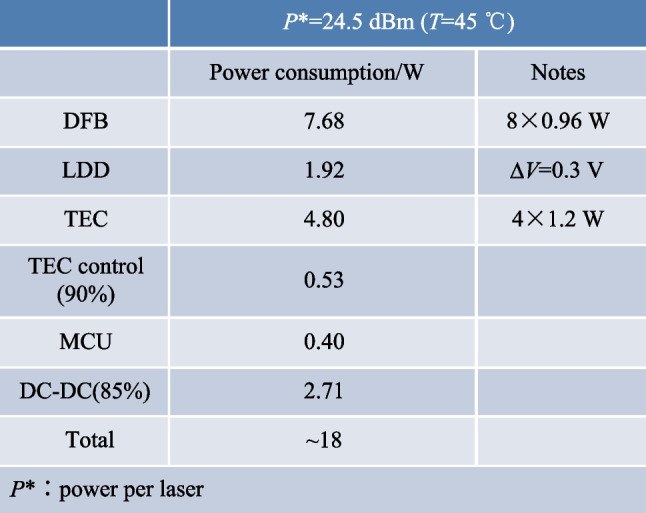

The power consumption of the ELS package is another critical parameter. Table 2 shows that the total power consumption of the ELS package for a 6.4 Tbit/s CPO is approximately 18 W. The laser chips and thermoelectric coolers account for nearly 70% of total power consumption.

Table 2.

Total power consumption of ELS package

The high output power of the laser chip is the root cause for the majority of the power consumption. The wall-plug-efficiency of the laser chip is critical to power consumption and is defined as the ratio of optical output power to consumed electrical input power. The wall-plug-efficiency used in Table 2 is approximately 0.3, meaning that only 30% of electrical input power can be converted to optical output power, while the remaining power is dissipated as heat. Furthermore, the thermoelectric cooler (TEC) consumes additional electrical power to dissipate the heat generated by the laser chip. The total power consumption of 16 ELSs, which are required for a 102.4 Tbit/s switch, is 288 W.

The form factor of ELS is being standardized in OIF [73], including the electrical and optical interface, footprint, management interface, etc.

Advances in science and technology to meet challenges

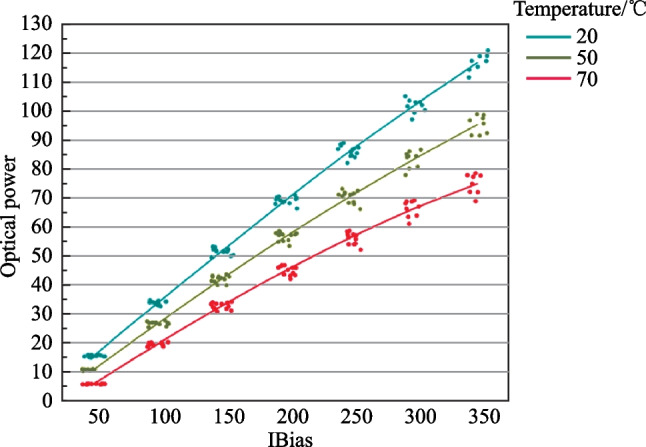

1. High output power. The existing CW lasers developed for pluggable transceivers cannot meet the high output power requirement of CPO applications. The silicon photonics based pluggable optical transceivers, e.g., 400G DR4, generally require CW lasers with < 100 mW output power. In contrast, CPO applications require much higher output power for the CW laser. As shown in Table 1, the required output power of the laser chip is 286 mW for the WDM architecture. Although the output power is much lower for the DR architecture, at least 100 mW is still required. For industrial applications, a slab-coupled optical waveguide DFB laser diode at C/C + bands with a kink-free CW output power exceeding 100 mW has been reported [74]. However, at O band, we have developed a 1310 nm CW laser that can only reach 80 mW at 50°C, as shown in Fig. 6. CWDM4 lasers with only about 70 mW output power have been reported [75]. Therefore, there is a need to develop high-power lasers for CPO applications.

Fig. 6.

Performance of high-power laser

2. High wall-plug-efficiency. In addition to high output power, high wall-plug-efficiency is another desirable feature of the high-power CW laser from the energy efficiency point of view. Moreover, a thermally efficient TEC is helpful for the reduction of ELS power consumption. Furthermore, an uncooled high-power laser might be the ultimate solution to the CPO light source.

3. Monolithic integration. Silicon photonic platform processes are well established and allow for higher overall transmission and reception performance than CMOS and BiCMOS platform, but laser integration remains a challenge for all silicon platforms and subject of active research. The previous major challenges of monolithic integrating III-V lasers on Si platform have been the impaired device performance due to materials dissimilarity. Recently, III-V QD lasers monolithically grown on Si substrates have demonstrated very promising results with a long lifetime, high output power, and low threshold current densities. However, in order to realize the application leveraging the monolithic integration of QD lasers on SOI platform, optical coupling to waveguides must be resolved. In contrast, InP based platform can readily integrate active materials, rely on a stronger electro-optic (EO) Kerr and Pockels effect, and achieve higher EO bandwidth-efficiency metrics. Further enhancement of the EO effect can be accomplished with the quantum-confined Stark effect in quantum wells, but at the cost of higher temperature and wavelength dependence.

Concluding remark

External laser source is a promising solution to the CPO light source due to its easy maintenance and wide accessibility. Standardization of ELS in OIF is underway and will accelerate the maturity of the technology. High power CW lasers with at least 100mW output power are desired to meet the link budget requirement. The wall-plug-efficiency of CW lasers requires further improvement for power-saving purposes. Monolithic integration of external laser source benefits from smaller parasitic capacitances and lower packaging cost, making them the most promising solution for achieving reliable, power efficient, high-density integration of laser diodes on silicon chips.

Optical power delivery in multiprocessor systems4

Status

With the maturity of nanophotonics, chip-scale optical networks are projected to be the enabling technology to sustain the continued performance scaling of future multiprocessor systems. This is because optical links are capable of providing intra-chip (e.g., core-to-cache) and inter-chip (e.g., core-to-memory) communication with orders-of-magnitude higher signal fidelity, lower latency, and higher bandwidth density via wavelength division multiplexing (WDM) compared to traditional electronic links [217]. Moreover, the unique properties make a chip-scale optical network more than just a simple replacement to its electrical counterpart, but rather a brand-new architectural inspiration.

Since the first proposal of Goodman et al. [218] in 1984, optical interconnection networks have become promising to offer high-quality transmission in applications ranging from high-performance computing [219], memory access networks [220, 221], data center networks [222], to even analog computing [223]. The continued progress makes this technology a natural solution to the fundamental conflicts between performance scaling and thermal constraints in future multiprocessor systems.

While remarkable, these pioneering designs are often hard to scale due to the proliferation of laser sources whose power and packaging cost can more than negate the abovementioned benefits. For a 256-core system, Corona [220] consumes as much as 58.51 pJ/bit power at best [224], I2CON requests an integration of up to 4096 lasers [225], PROBE would require at least 64 fibers attached to a single chip for power provisioning only [226]. While these numbers are still barely feasible, scaling up the system either leads to high packaging cost, complicates layout, or is entirely impractical.

The optical power distribution networks (OPDNs), on which laser light is distributed to its modulation phase, play a critical role in the system power consumption [227]. Despite the importance, floorplanning, as well as placement and routing (P&R) are less discussed in the literature because the underlying technologies are still admittedly in their early stages. Nonetheless, significant industrial and academic efforts have centered around the silicon photonic platform thanks to its compatibility with the bulk CMOS process flow and mature infrastructure.

The trend is further boosted by a combination of the cost-sharing business model and commercial availability through international foundries, such as Global Foundries, Freescale, TSMC, IMEC, CEA Leti, and IME. Therefore, as an early attempt, optical power distribution networks and their floorplan optimizations have mostly addressed silicon photonic platforms in the past few years [227, 228].

Current and future challenges

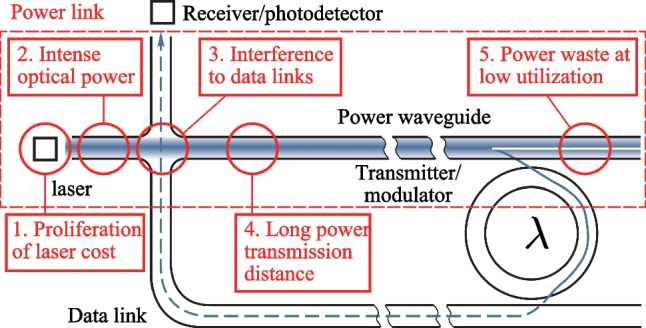

Despite the recent developments, the design paradigm for supplying power to the compact yet dense chip-level optical links has not been established thus far and several technological obstacles must be addressed before massive adoption in commercial multicore architectures is possible. Laser power consumption contributes to over 70% of the network power [229] and has become one of the primary design constraints under the increasing demand for network capacity. To enable efficient optical power delivery, five main challenges are illustrated in Fig. 7.

Fig. 7.

Challenges of optical power delivery illustrated by a simple optical link

1. Proliferation of laser cost. Hundreds to thousands of wavelength channels are making their way into chip-scale in recent works [219] as a result of the increasing demand on optical networks. However, the low energy conversion efficiency of O- and C-band lasers, ∼10% at best [230], and the lack of efficient packaging technologies make it hard to integrate laser sources at a large scale. While the debate over the use of off- v.s. on-chip laser sources is ongoing, a highly efficient, easy-to-integrate laser source would surely be favorable.

2. Intense optical power-induced power loss. A silicon waveguide can become opaque when exposed to high optical power despite being known for its transparency in the infrared spectrum. An extra 3 dB/cm loss is observed in a standard 250 nm × 450 nm strip waveguide with 50 mW of power injected [231] and the loss is projected to aggravate exponentially with increasing injected power. Theoretical explanations are given by modeling the two-photon absorption (TPA) and free-carrier absorption (FCA) phenomena in waveguides [232]. To overcome the fundamental power capacity constraint of waveguides, it would require a cross-layer effort, from conscious architecture designs and better floorplanning, to advanced material platforms.

3. Interference to data links. As an optical signal propagates through data links, it is attenuated by multiple factors, such as waveguide micro-resonator loss and crossing reflection, causing increased network loss and noise. An OPDN exaggerates the attenuation by introducing an extra amount of waveguide crossings after the P&R phase. A recent study on a 16 × 16 network has reported a 1 × more laser power consumption and − 0.73 dB SNR at worst by considering the routing of the power distribution network [227]. Note here that the numerical results are subject to complex design choices in, for example, topology and P&R algorithm. Still, most recently published works, such as [233] and [234], have admitted that increased wiring intricacy largely aggravates the power loss and crosstalk noise. However, optimizing the data network and OPDN together regarding topology, floorplanning, and P&R is still challenging and requires comprehensive studies.

4. Long power transmission distance. Power transmission arises when a laser source is spatially shared among modulators. This is often the case because assigning one dedicated laser source to every modulator would either be expensive or totally infeasible. Ref. [227] evaluates 13 networks and reports an average of 16.71% power loss during transmission. Ref. [228] further points out that a better laser sharing scheme depends on the logical topology and the physical layout of the OPDN. However, there lacks an efficient design approach that optimizes the sharing and placement of lasers in the literature.

5. Power waste during low link utilization. A majority of power is wasted in an underutilized link when the lasers are kept on. This is not uncommon for many parallel applications where the network utilization is very low (less than 5%) with only a few traffic spikes [235]. Strategically turning off underutilized links or sharing lasers among links can mitigate the waste [228].

Advances in science and technology to meet challenges

1. Device and Circuitry. Epitaxially grown quantum dot lasers are promising to attain low-power consumption and athermal performance on silicon photonic platforms, demonstrating the lowest threshold current and highest lasing temperature compared to alternatives [236]. Efforts to mitigate the nonlinear power loss in waveguides include a special p-i-n structured waveguide that cuts the carrier lifetime from 16 to 6.8 ns passively, and to 1 ns at 25 V reserve bias [237]. Additionally, an integrated grating and 16-way star coupler is capable of eliminating the high-intensity regions in waveguides and couples up to 275 mW optical power with only 0.45 dB additional loss [231]. Development on low-loss, low-crosstalk waveguide crossing has achieved ~ 0.007 dB loss and < − 40 dB crosstalk [238].

2. Topology of the power distribution network. Proposals of power distribution networks can be classified into two types, namely static OPDNs and re-configurable OPDNs. Many pioneering designs adopted static OPDNs for their simplicity in fabrication and optimization, including bus-type [220], star-type [231], and binary tree [227] structures. Static OPDNs are cheap, easy-to-reason, but less responsive to fluctuation in power demands. Recent proposals tend to apply re-configurable OPDNs, which allow flexible power sharing between links in need [229, 235].

3. Adaptive laser allocation. Another way to save laser power is by avoiding over-provisioning via offline optimization or online adaptation. Researchers have found the former effective when applied to specific applications with regular communication patterns. An average of 74% power saving is achieved over a range of applications [239]. The adaptive power allocation scheme always presents a trade-off among network re-configurability, re-configuration overhead, and power saving. A laser power saving of 68% is demonstrated in Ref. [226], but at the cost of a 12% loss in performance.

4. Advanced fabrication technologies. Significant industrial and academic efforts have centered around silicon photonics with a preference on materials, including crystalline silicon, polycrystalline silicon, and silicon nitride. Apart from the conventional single-layer crystalline silicon, polycrystalline silicon or silicon nitride can be deposited to form additional layers above. The stacked structure benefits from the low-loss materials and eases P&R compared to its 2D counterpart [235].

Concluding remarks

To meet the demands from the next-generation chip-scale optical networks, future optical power sources must aim to work with minimal lasers and power consumption while meeting the device and layout constraints. As a cross-layer effort, static approaches involve the advancement in circuitry, such as better materials, devices, floorplanning, and P&R, while dynamic approaches include runtime laser assignment and on-demand power allocation.

Acknowledgements

This work was partially supported by ACCESS and Foshan-HKUST Projects Program (FSUST20-FYTRI12F).

DSP design considerations for co-packaged optics5

Status

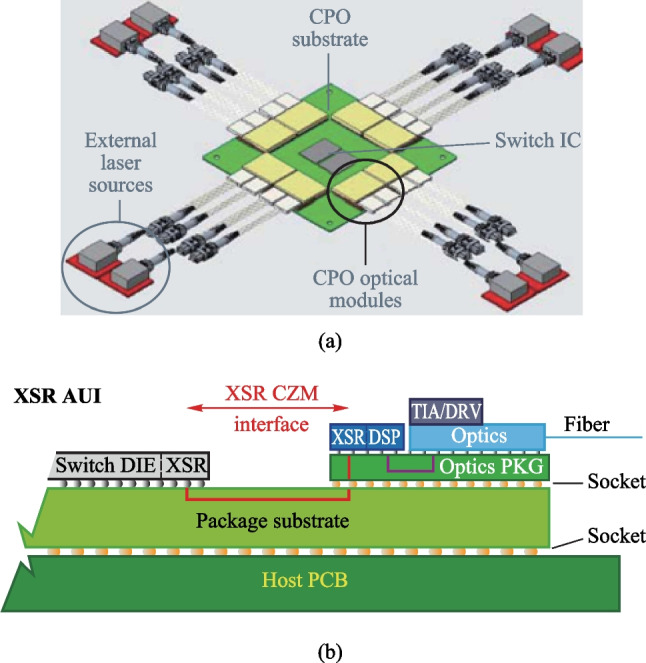

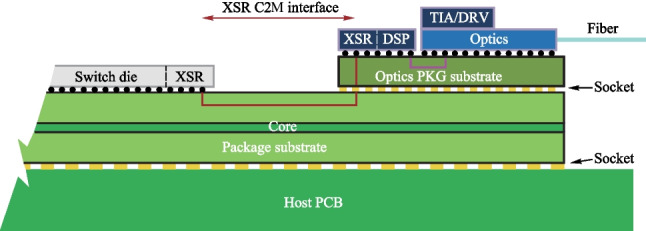

As data rate increases, traditional pluggable optical modules occupy a large volume, limiting the signal density to a certain extent (Fig. 8(a)) [13]. Figure 8(b) shows an architecture of co-packaged optics (CPO), where the optical engine and switching chip can be packaged together, the host-side of the re-timing chip is connected to the payload ASIC by XSR SerDes, and the line-side of the re-timing chip is connected to the optical engine by LR SerDes [13]. Thus, CPO effectively reduces power consumption, increases signal density, and reduces latency. This paper will focus on the design considerations of SerDes in CPO. Regarding current and future challenges, the architecture of the SerDes transceiver, as well as the requirements of SerDes on the host-side and the link-side are introduced. Then, we describe the advances in science and technology to meet challenges, including bandwidth, clock, and equalization.

Fig. 8.

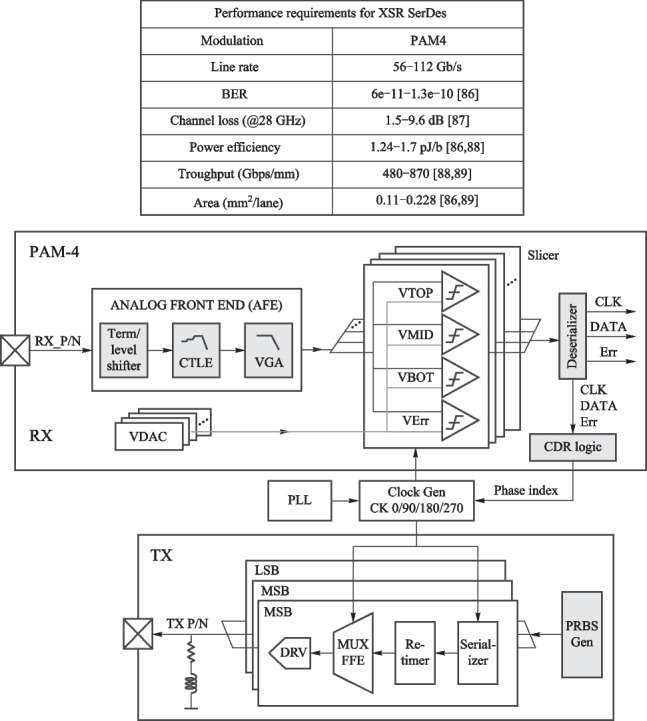

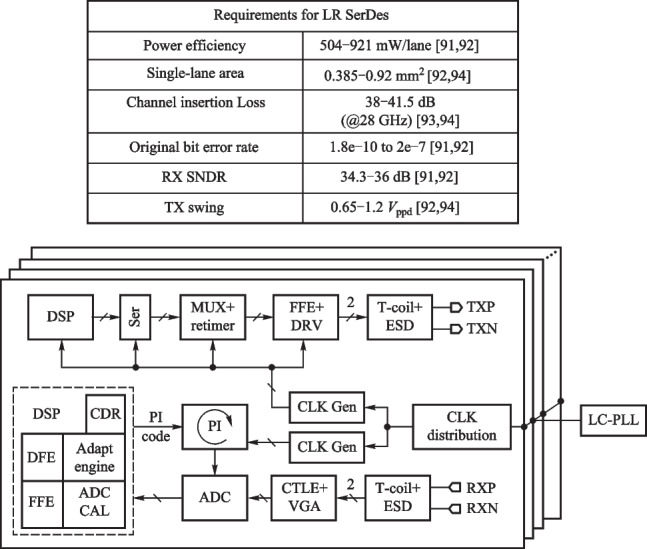

Current and future challenges

Although CPO demonstrates high performance in areas such as transmission data rate, there are also some challenges. In this section, we describe the requirements and challenges from two aspects: Host-side XSR SerDes and Line-side LR Serdes. The block digram of each SerDes is also provided.

1. Host-Side XSR SerDes design consideration

The XSR SerDes is targeted to optimize power efficiency, integration density, and transmission latency by reducing the connection distance between two communication chips. Figure 9 summarizes the performance requirements for 56–112 Gb/s PAM4 XSR SerDes and conceptually shows the architecture of the XSR transceiver. The transmitter usually adopts an analog-mixed architecture or a 5 bit DAC topology with a CMOS MUX, several tap FFE, and a SST driver architecture to implement data serialization, wave pre-distortion, and output driving. The receiver often employs a simple continuous-time linear equalizer (CTLE) followed by a VGA and several slicers to directly extract the originally transmitted data. Similar to conventional transceivers, the XSR SerDes also needs a common PLL and a local CDR to adaptively track the optimal sampling points. Overall, the main feature of the XSR SerDes is utilizing a simple RX-side CTLE combined with a TX-side FFE to achieve high power efficiency and low code error rate, while handling a relatively low channel loss.

Fig. 9.

XSR top-level structure block diagram and XSR applications and requirements

2. Line-side LR SerDes design consideration

The Line-Side LR SerDes is targeted to deal with non-ideal factors, such as finite bandwidth, chirp effect, noise, dispersion effect, and the nonlinearity of the device. Therefore, the equalization part of LR is more complicated compared to XSR, so the balance between bit error rate and energy consumption ratio should be ensured when designing.

Figure 10 shows the LR architecture and performance requirements. The transmitter is usually a DSP composed of an FIR filter, MUX, multi-tap FFE, and DAC driver. DAC driver has SST form and CML form. The receiver is mainly composed of CTLE, VGA, ADC, and a DSP with calibration, equalization, and clock recovery. A common PLL and local CDR are used to determine the best sampling point for tracking.

Fig. 10.

LR architecture and performance requirements

Advances in science and technology to meet challenges

From the system perspective, we provide notable advances in clocking scheme, bandwidth extension techniques, and equalization techniques.

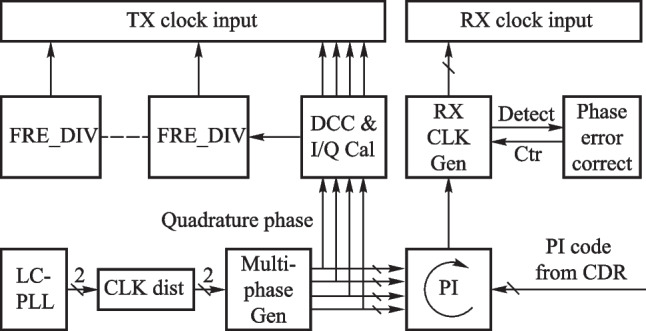

1. Clocking scheme

Figure 11 shows a widely used clock scheme of wireline transceivers. The clocking scheme of mainstreamed and advanced transceivers mainly consists of LC-PLL, phase interpolator (PI), multi-phase clock generation, clock and data recovery (CDR), clock distribution, and clock adjustment modules [86, 88, 90, 94].

Fig. 11.

Clock path

LC-PLL generates a high-frequency and adequately pure reference clock that acts as a metronome to control the transmitter process and serialize the data. By interleaved sampling in time with the multi-phase clock and high order modulation, the low-frequency clock can be used to accomplish the transmission of the high-speed bitstream. Multi-phase generation modules are generally implemented by Ring ILO (injection-locked oscillator) [95]. Due to the delay mismatch between the injection stage and other stages in the Ring ILO [94], as well as the non-ideal factors of the clock generation and transmission, the timing of the multi-phase clock will have a lot of jitter, and additional phase error correction loop is necessary to sense the error caused by the above factors and adjust the phase [94]. RX needs to sample the input data at the appropriate moment. CDR can provide phase information of input data and track its long-term jitter.

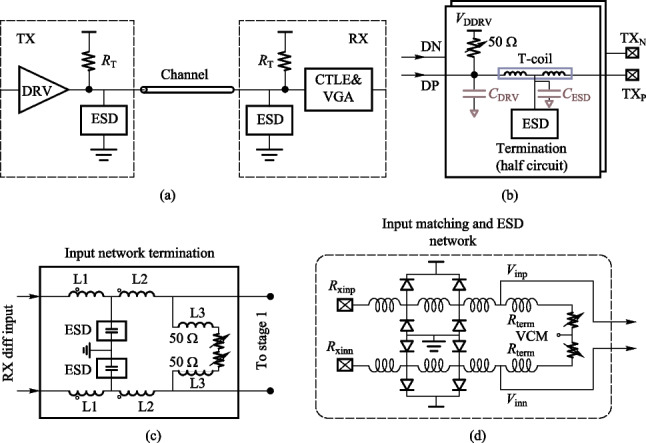

2. Bandwidth extension techniques

The large parasitic capacitance of the ESD device and PAD shown in Fig. 12(a) limits the bandwidth of the circuit and also causes a large return loss. Therefore, bandwidth extension and impedance matching methods are required.

Fig. 12.

a Terminal of the transceiver. b TX with T-coil Peaking [97]. c RX with T_coil and inductive peaking [99]. d RX with LC-π network [100]

Commonly used bandwidth extension methods include inductive peaking, T_coil peaking, and LC-π peaking. Compared to the 1.6 − 1.7 times bandwidth extension of the inductor peaking, the symmetric T_coil peaking can extend the bandwidth to 2.7 − 2.8 times [96]. Besides, T_coil is very suitable to combine with ESD to achieve high bandwidth, adequate electrostatic protection, and good impedance matching. Figure 12(b) shows a 128 Gb/s transmitter using T-coil to eliminate the ESD parasitic capacitance and achieve good impedance matching [97]. Note that sometimes asymmetric T_coil circuit may have better performance but no analytical expression, thus needed to be simulated and designed by electromagnetic simulation tools [98]. Figure 12(c) shows a 56 Gb/s PAM4 receiver that uses a combination of T_coil peaking and inductive peaking [99]. Figure 12(d) shows an LC-π network using 4-segment inductors to separate the capacitors, which achieves 56 GHz bandwidth and good impedance matching [100].

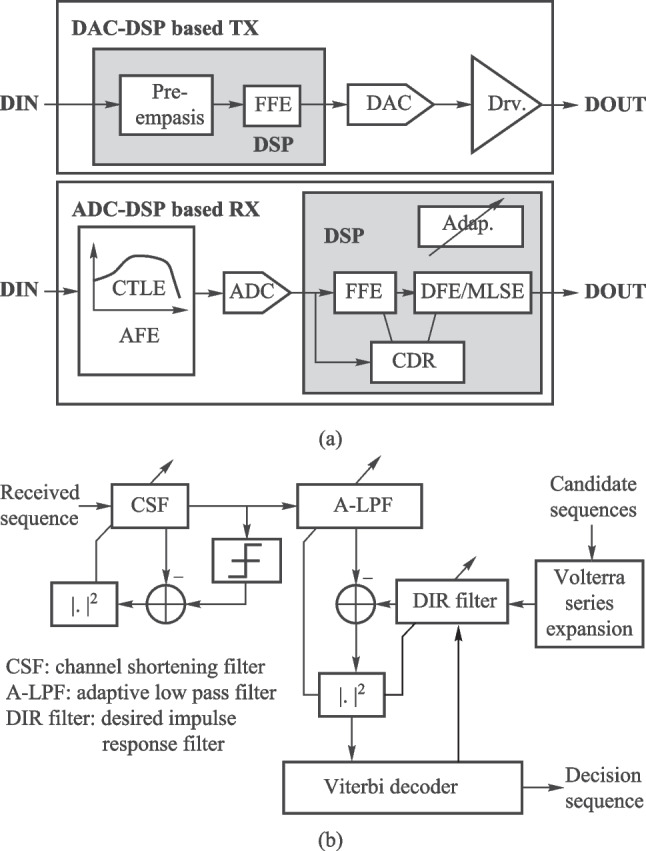

3. Equalization techniques

Equalization is a critical technology that reduces ISI and improves the reliability of the entire communication system. In high-speed SerDes, selecting a specific equalization scheme is closely related to the characteristics of channel features and signal loss For example, FFE and DFE with more taps can be used with SerDes in LR with a poor channel environment (Fig. 13(a)) [90, 93]. However, the equalizer in XSR is simpler than that of LR due to the short length of the XSR interconnection channel built in CPO [86, 87, 101].

Fig. 13.

a Equalizers in ADC-DSP based SerDes. b DF-NL-MLSE [104]

For digital FFE and DFE equalizers, the tap coefficient is directly related to the quality of equalization. Currently, the improved SS-LMS algorithm reduces the computational complexity and is widely used in equalizers. Other methods, such as PD-DLR [102] or machine learning based algorithm [103], can achieve a better adaptive result compared to the SS-LMS algorithm. However, when facing serious ISI circumstances, the performance of FFE and DFE equalizers will be degraded due to noise enhancement and error propagation. Although maximum likelihood sequence estimation (MLSE) equalization is rarely used in SerDes of CPO, the improved MLSE algorithm is still of certain reference for the design of nonlinear equalizer in high-speed receiver DSP. Figure 13(b) shows the MLSE equalizer architecture in the DSP [104].

Concluding remark

DSP plays an important role in CPO transceiver. Compared to the hybrid architecture transceiver, many algorithms that can improve the performance of the entire system can be implemented in DSP based on CMOS technology. Although certain challenges remain in the way of achieving high performance and low power comsumption, many positive attempts to solving these problems from different aspects are given in this paper. The DSPs in CPO will always advance with the progress of semiconductor technology and design methodology, including clock scheme, bandwidth extention techniques, and high-efficiency equalization algorithms.

Acknowledgements

This work was partially supported by the National Natural Science Foundation of China (Grant No. 62074162).

Microring-based transmitter array for co-packaged optics6

Status

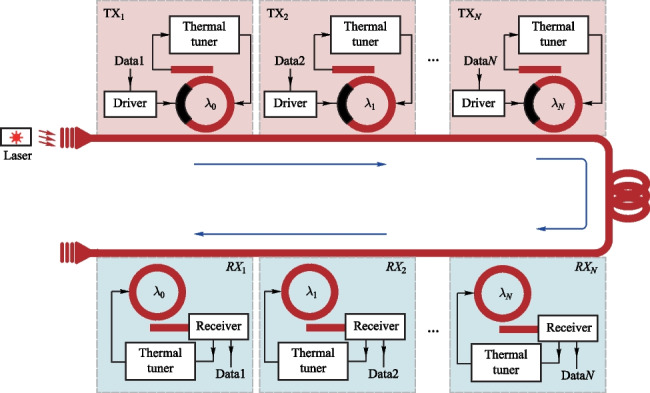

Microring (MRR)-based transceiver array (Fig. 14) is a promising solution to meeting the stringent bandwidth and power consumption requirements of future data centers due to their small size, high energy efficiency, and WDM-compatibility.

Fig. 14.

The diagram of MRR-based transceiver consisting of drivers, MRMs, receivers, MRR DEMUX, and thermal tuners

The high-bandwidth, low-power MRR-based transceiver array has already been demonstrated in hybrid integration [105] and monolithic integration platforms [106, 107]. In hybrid integration, the connection between the photonic chip and the electronic chip results in parasitics that limit the bandwidth and power consumption, such as the parasitic inductance (250 − 500 pH) and parasitic capacitance (~ 100 fF) caused by wire-bonding [108], as well as the parasitic capacitance (~ 30 fF) caused by micro-bump/copper pillar connection. However, 3D integration of electronic and photonic wafers performs with very low inter-connection parasitics capacitance (~ 3 fF) by through-oxide vias (TOVs) [109]. Monolithic integration reduces the parasitics of the wiring, improving the performance and increasing manufacturing costs. At the transmitting end, the data rate of a single micro-ring modulator (MRM) has reached 200 Gb/s [110]. At the receiving end, the data rate of a microring photodetector (MRPD) has reached 112 Gb/s [111]. However, laser integration compatible with mass-producible silicon technology is still an outstanding challenge [112].

Despite the integration challenges, the microring-based transceiver array has made rapid progress in recent years. Using hybrid integration, the single MRM-based transmitter has reached a data rate up to 112 Gb/s with 6-pJ/bit energy efficiency [113]. The MRM-based transmitter array has achieved a data rate up to 4 × 112 Gb/s with 5.8-pJ/bit energy efficiency [114]. Using monolithic integration, the single MRM-based transmitter has a data rate of 100 Gb/s with 0.7-pJ/bit energy efficiency [106]. The MRM-based transmitter array has shown a data rate up to 16 × 5 Gb/s with ~ 0.8-pJ/bit energy efficiency. In all these works, to stabilize the resonant wavelength of the MRM, closed-loop thermal tuning is required to compensate for the process variations, thermal fluctuations, and input laser wavelength/power variations [115, 116]. Using hybrid integration, a receiver based on CMOS technology has reached a data rate of 100 Gb/s with − 11.1 dBm sensitivity and 3.9 pJ/bit [117]. Using monolithic integration, the split-MRR resonant photodetector has a data rate of 12 Gb/s with 0.58 pJ/bit energy efficiency based on CMOS technology [118], and a 56 Gb/s optical receiver with 3.66 pJ/bit energy efficiency is implemented based on BiCMOS technology [119]. Closed-loop thermal tuning for MRR-filter is also necessary for wavelength locking of MRR-based receivers. In error-free transmission (bit error rate (BER) < 1e − 12), MRR-based transceiver array has reached 4 × 50 Gb/s in hybrid integration method [1] and 8 × 16 Gb/s with 4.96 pJ/bit energy efficiency in monolithic integration method [3].

Current and future challenges

Several technological challenges remain to be tackled to further improve the performance and robustness of the MRR-based transceiver array. We outline these challenges below:

1. Wavelength locking. Due to the resonant wavelength characteristics, the performance of MRRs is susceptible to fabrication variations, thermal fluctuations, and input laser wavelength/power variations. If these non-ideal factors are not compensated, the work condition of MRR will not be stable, which will significantly degrade the modulation and DEMUX performance. Therefore, it is necessary to stabilize the resonant wavelength of the MRR in a variety of different environments. The closed-loop feedback control loop [113, 115, 116, 120–126] is often used to lock the resonant wavelength of the MRR, MRPD, and MRM. However, there is almost no work that can simultaneously compensate for fabrication variations, thermal fluctuations, input laser wavelength/power variations, and random data patterns.

2. Modulation linearity. Pulse amplitude modulation with 4-level (PAM-4) is commonly used to increase the data rate but puts forward new requirements on the linearity of the modulators. The modulation quality of PAM-4 is determined by the ratio of level mismatch (RLM), and we hope that the eye pattern distribution of PAM-4 is uniform [127]. However, due to the Lorentzian shape of the transmission curve, the MRM has static nonlinearity, making a uniform level of electrical PAM-4 eye pattern input to generate a non-uniform optical eye pattern output. Furthermore, the MRM PN junction capacitance is different at different bias voltages, resulting in different bandwidths at different voltage levels, introducing different inter-symbol crosstalk. This phenomenon is called dynamic nonlinearity [113]. How to compensate for the static and dynamic nonlinear effect of the MRM is a key factor in optimizing the performance of the MRM.

3. Polarization handling. For silicon photonic wavelength division multiplexing (WDM) receivers, the performance of the channel filter changes with respect to the polarization of the optical input from a single-mode fiber (SMF). Polarization-maintaining fiber (PMF) is used to maintain the polarization state in SMF, but it is too expensive to be applied in commercial applications [128]. How to control the polarization state effectively on-chip is the key challenge to reduce cost and improve performance.

4. Circuit-level photonic-electronic co-simulation. MRR-based transceiver array is a photonic-electronic integrated circuit [108]. Photonic device design is mainly a device-level simulation implemented by PDA tools [129], and electronic circuits are circuit-level simulations implemented by mature EDA tools. Device-level simulation can provide very accurate simulation results but cannot be directly applied to circuit-level simulation design due to its low simulation efficiency. How to perform circuit-level photonic-electronic co-simulation is a prerequisite for MRR-based transceiver array design. Thermal tuning for MRM and MRR is closed-loop electrical-optical-thermal process, and there is a big frequency mismatch between thermal fluctuation (~ kHz), electrical modulation (~ GHz), and light (~ THz), which will significantly increase the simulation time and reduce simulation efficiency.

Advances in science and technology to meet challenges

Recent advances in photonic integration have addressed some of the challenges discussed above.

1. Closed-loop thermal tuning. To implement effective closed-loop thermal tuning for MRR, the relative position of the resonant wavelength and laser wavelength must be obtained using a monitor, such as photodiode [115] and contactless integrated photonic probe (CLIPP) [130]. Secondly, a controller is required to generate the control signal to align the resonance wavelength according to a suitable algorithm [115, 116, 121–124, 131] or analog control circuit [120]. To increase the tuning temperature range, a driver is required to provide sufficient current to heat the integrated resistor, thereby tuning the resonance wavelength through the thermo-optic effect [113, 132]. Unlike MRR, wavelength locking for MRM faces additional challenges. Optical bistability and data-dependent self-heating [133] will significantly reduce the performance of MRM. The average power detection based wavelength locking cannot perform optimally when the non-DC balanced data pattern is transmitted [116]. Polarization controller is widely used to solve the polarization mismatch problem between the SMF and the photonic integrated circuit (PIC). In Ref. [134], the polarization control scheme is adopted in the Microring-based WDM system to achieve the WDM polarization-independent receiver. In Ref. [135], the polarization controller is used in the coherent receiver to stabilize the polarization state of the local oscillator (LO). The polarization controller can be further improved by modifying the optical device performance and updating the controller algorithm.

2. Nonlinearity compensation for PAM transmission. Compared with NRZ, PAM4 can effectively increase the data capacity of a single channel, but it needs to effectively compensate for the deterioration of the eye diagram caused by static nonlinearity and dynamic nonlinearity. In Ref. [113], pre-distortion is used to adjust the electrical signal level to compensate for the distortion of the optical eye pattern caused by static nonlinearity, thereby generating a uniform optical eye pattern. Furthermore, feed-forward equalization (FFE) is used to compensate for level-dependent inter-symbol interference (ISI) caused by dynamic nonlinearity. In Refs. [136, 137], an optical digital-to-analog converter (ODAC) is adopted to generate a uniform eye diagram. This approach reduces the difficulty of driver design but makes the MRM design more complex. In these works, there are still many parameters that need to be manually selected, thus closed-loop automatic control methods are required.

3. Compact modeling for photonic devices. Since mature EDA tools have been able to support accurate simulation design for electronic circuits, most of the current work tends to model photonic devices on the EDA platform to combine mature electrical SPICE models to achieve accurate and fast photonic-electronic co-simulation. In Ref. [138], hierarchical design is used to model basic photonic devices, such as waveguide and coupler so that the MRR model can be combined through the basic photonic devices. In Ref. [139], the small-signal and large-signal model modeling of the MRM is realized through the SPICE model based on the coupled-mode theory. In Ref. [140], the S-parameter is used to describe the characteristics of the photonic device and the baseband-equivalent model is used to improve the simulation efficiency. However, the S-parameter based method is more suitable for modeling passive photonic devices. When modeling for active photonic devices, more metrics are needed to describe the characteristics of photonic devices, which undoubtedly increases the difficulty of modeling and reduces simulation efficiency. The baseband model can only reduce the frequency gap between the light and the modulation. Therefore, it is necessary to reduce the frequency gap between the modulation and the thermal fluctuation to further improve simulation efficiency.

Concluding remark

Adopting new technological tools enables MRR-based transceiver arrays to meet the demands of data centers with high bandwidth and low power consumption. Therefore, the MRR-based transceiver array for co-packaged optics (CPO) is a promising solution to replacing the existing implementation of pluggable optical modules and become mainstream in the future [141].

Acknowledgements

This work was partially supported by the Open Project Program of Wuhan National Laboratory for Optoelectronics (No. 2021WNLOKF013).

Mach–Zehnder modulator-based transmitter for co-packaged optics7

Status

Mach–Zehnder modulator (MZM)-based transmitter has already been demonstrated in hybrid integration [142, 143] and monolithic integration platforms [144, 145]. In hybrid integration, the connection between the photonic chip and the electronic chip results in parasitics that limit the bandwidth and power consumption. 3D integration of electronic and photonic wafers performs with very low inter-connection parasitics capacitance. Monolithic integration further reduces the parasitics of the wiring, thus improving performance but also increasing manufacturing costs. For the modulator only, the EO bandwidth of a single MZM has reached 60 GHz [146] and the data rate of a single MZM has reached 240 Gb/s [147].

The MZM-based transmitter has made rapid progress in recent years. In 2006, Luxtera demonstrated the first fully integrated optical transmitter system in silicon technology platform [148] using current-mode logic (CML). Systematic design and simulation methodology was reported in Ref. [149]. A multi-segment transmitter that can potentially remove the power-consuming electrical DAC from optical links for low-cost applications was reported in Ref. [150]. To solve the large area consumption of passive inductors, Kim et al. realized an area-efficient modulator driver by adopting custom-designed shared inductors [151]. In 2016, IBM [152] demonstrated the first fully monolithically integrated silicon photonic four-level PAM (PAM-4) transmitter operating at 56 Gb/s with error-free transmission (bit error rate < 10–12) up to 50 Gb/s without forward-error correction. IHP reported a monolithically integrated Si MZM transmitter with the highest ER values (11 dB) at that time, which demonstrated the potential of the monolithically integrated transmitters based on the SE-MZM concept [145].

For hybrid integration, the single MZM-based transmitter has reached a data rate up to 100 Gb/s with 2.03-pJ/bit energy efficiency [143]. For monolithic integration, the single MZM-based transmitter has a data rate of 56 Gb/s with 4.8-pJ/bit energy efficiency [152]. In all these works, various techniques are adopted to maximize the system performance (data rate, ER, bit error rate, and energy efficiency).

Current and future challenges

Several technological challenges remain to be tackled to further improve the performance and robustness of the MZM-based transmitter.

We outline these challenges below:

1. High voltage swing driver. Due to the limited breakdown voltage of the transistor, the voltage output of the electronic driver is generally insufficient for the MZM. In general, a SiP MZM has a Vπ*L product of approximately 1.5 V⋅cm [153, 154], suggesting that relatively long devices or large voltage swing are required to achieve modulation depth. For the same device length, if the voltage swing is not large enough, the difference between signal “1” and signal “0” will be small, resulting in low SNR and sensitive performance. Low voltage swing can lead to bit error since the transmitted signal is so weak that the receiver cannot distinguish it. Therefore, it is necessary to improve the voltage output swing of the driver. In the case of SiGe HBT technology, the breakdown voltage (BV) is typically ~ 2 V while maintaining a sufficient high ft/fmax, e.g., 300 GHz [155]. However, as for the advanced CMOS node, the BV of the core transistor is below 1 V [156], which means additional techniques should be used to improve the output voltage swing.

2. High bandwidth. Although a higher data rate requires higher bandwidth, the ft/fmax of transistors improves slowly. Thus, all kinds of bandwidth extension techniques are developed, such as inductive peaking [157–161], negative resistor, and capacitor splitting [162]. Also, equalization techniques, such as feedforward equalization (FFE) [65, 142, 163, 164] and continuous time linear equalization (CTLE) [165–167] are widely used in transmitters. Furthermore, distributed amplifier natively has wide bandwidth compared to lumped amplifier. Many works based on distributed amplifier structure have been reported, such as [65, 155, 163, 168–174], and [142]. The lumped driver is easy to implement but has limited bandwidth and modulation format. The distributed driver has superior operational BW, low sensitivity to components mismatch and modeling inaccuracies, as well as broadband power matching. However, it needs complex design, precise phase, and delay control.

3. High energy efficiency. Technology requirements for intra-DC optical interconnects are quite different from traditional long-distance telecommunication transport systems. Intra-DC interconnects have a much shorter reach (typically < 2 km) with a large number of connections, thus their cost is largely dominated by the transmitters. Additionally, intra-DC optics have more stringent power consumption, density, and cost requirements due to their sheer volume. Typically, voltage mode logic (VML) [142] is more power-efficient than current-mode logic (CML) [175–178]. Furthermore, single termination [149, 179, 180] can save half of the power consumption under the precondition of the same output voltage swing compared to the dual termination structure. However, the single termination scheme will introduce more reflection due to the impedance discontinuity. Another point to improve the energy efficiency is to employ a push–pull structure [65, 178, 181–183] rather than the pull-down structure with resistor load.

4. Circuit-level photonic-electronic co-simulation. MZM-based transmitter is a photonic-electronic integrated circuit [108]. Nowadays, photonic device design is mainly a device-level simulation implemented by PDA tools [129], while electronic circuits are circuit-level or system-level simulations implemented by mature EDA tools. Device-level simulation can provide very accurate simulation results but cannot be directly applied to circuit-level or system-level simulation design due to its low simulation efficiency. How to perform circuit-level or system-level photonic-electronic co-simulation is a prerequisite for MZM-based transmitter design.

Advances in science and technology to meet challenges

Recent advances in photonic integration have addressed some of the challenges discussed above.

1. Stacked CMOS output driver structure. For SiGe HBT designs, BV doubler is widely used to overcome the voltage limit from a single transistor [178, 184–186]. The BJT is a current controlled device, while the MOSFET is a voltage-controlled device. The BV-Doubler for BJT can no longer work properly for MOSFET. Thus, stacked FET technique [156, 175, 187–192] replaces the empty of BV-Doubler. The stacked FET structure is commonly used in power amplifier designs.

2. Inductive peaking and cherry-hopper pre-driver. The distributed amplifier can provide large BW, but consumes large area and high power, and are difficult to design. Passive filtering (e.g., shunt and series peaking) has been used since the 1930s to extend amplifier bandwidth. It uses inductors to trade off between bandwidth and peaking in the magnitude response [193, 194]. Cherry-hopper amplifier is first used in 1960s [195]. It is widely used in optical interconnects. In Ref. [196], the cherry-hopper structure is used to enhance the bandwidth of the modulator driver. In Ref. [197], a 1-pJ/bit 80-Gb/s 215 − 1 PRBS generator with a modified Cherry–Hooper output driver is presented.

3. Compact modeling for photonic device. Since mature EDA tools have been able to support accurate simulation design for electronic circuits, most of the current work tends to model photonic devices on the EDA platform to combine mature electrical SPICE models to achieve accurate and fast photonic-electronic co-simulation. In Ref. [138], hierarchical design is used to model basic photonic devices, such as waveguide and coupler, so that the MZM model can be combined through the basic photonic devices. In Ref. [198], the small-signal and large-signal model of the MZM is realized through the SPICE model. In Ref. [140], the S-parameter is used to describe the characteristics of the photonic device and the baseband-equivalent model is used to improve the simulation efficiency. However, the S-parameter based method is more suitable for modeling passive photonic devices. When modeling for active photonic devices, more metrics are needed to describe the characteristics of photonic devices, which undoubtedly increases the difficulty of modeling and reduces simulation efficiency. The baseband model can only reduce the frequency gap between the light and the modulation. Therefore, it is necessary to reduce the frequency gap between the modulation and the thermal fluctuation to further improve the simulation efficiency.

4. Segmented driver. The traveling-wave (TW) MZM requires a long phase shifter (2 − 3 mm) to obtain a sufficient optical extinction ratio due to the low modulation efficiency [199]. Thus, the electrode will introduce significant T-line attenuation. To satisfy the requirement of the ER, a higher voltage swing of the driver is demanded, e.g., 3 − 4 Vppd. Such a high voltage output swing is hard to implement using CMOS technology. Therefore, the lump-segmented (LS) MZM is developed to improve the modulation efficiency. By dividing a long phase shifter into multiple short segments and mapping the driver slice into each segment, the signal attenuation of each segment has been greatly reduced. Furthermore, each segment can be treated as a small capacitive load to the driver, resulting in higher power efficiency. Ref. [200] employed a simple and comprehensive modeling approach based on the microwave transmission matrix theory to analyze the frequency response of segmented traveling-wave optical EAM modulators.

Though LS MZM has many advantages, the choice of segment length, segment number, and the trade-off between the total power consumption and segment number will significantly influence the final performance [201].

Besides, timing matching becomes another important problem in segment configuration. Specifically, the electrical signal in different driver units should keep pace with the optical signal in different segment MZM units. Refs. [144] and [155] used artificial-designed T-lines to maintain the timing matching. Ref. [142] adopted the PI-based timing calibration approach, which can provide a wide-range delay adjustment of ~ 11 ps. The clock buffer can also provide a fixed delay (~ 10 ps) and the calculated optical propagation delay from adjacent segments is approximately 21 ps, which could be fully covered. Furthermore, considering the PVT varies, a calibration procedure of the optical eye diagram is also developed to further optimize the E-O velocity match.

Concluding remark

Although there are still many difficulties, new techniques and innovations will constantly push the limit. Therefore, MZM-based transmitter for co-packaged optics (CPO) is a promising solution to replacing the existing implementation of pluggable optical modules and become mainstream in the future [141].

Optical receiver front-end electronics in the CPO era8

Status

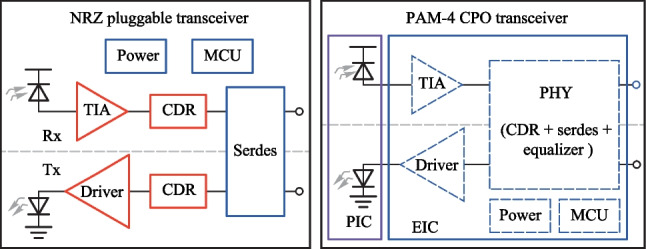

As the aggregate bandwidth of the data center core switch reaches 51.2 Tb/s, pluggable optics has become increasingly incompetent [36] due to the limited space in the switch front panel and excessive channel loss between SerDes and switch IC. Therefore, co-packaged optics (CPO) has been proposed to unleash the future bandwidth bottleneck at data center. Using integrated optics and electronics, the pluggable optical module can be dissolved and co-packaged with the switch IC. Not only can the bandwidth density limit at the switch front panel be removed, the in-package millimeter-long electrical link can incur a much smaller loss, which will greatly ease the SerDes design and facilitate lower power.

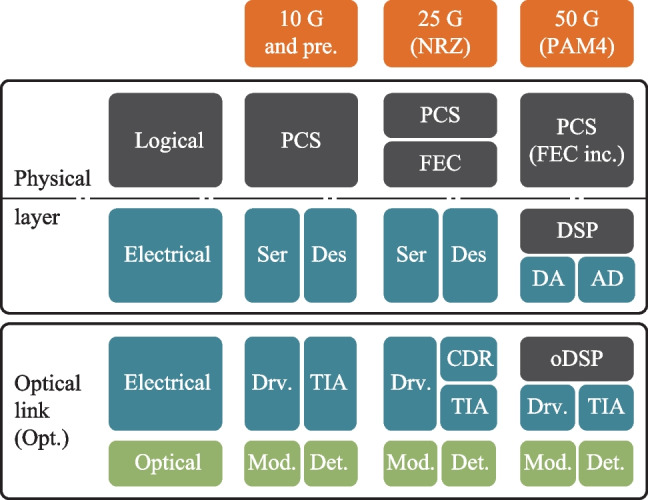

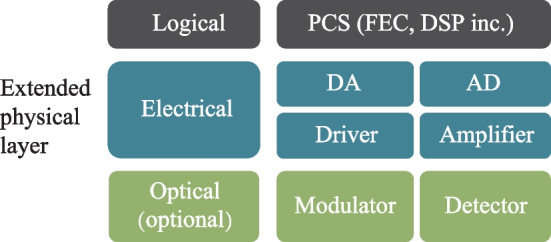

Meanwhile, as channel speed reaches 50 Gb/s and beyond, 4-level pulse amplitude modulation (PAM-4) has been introduced over non-return-to-zero (NRZ) to save half the bandwidth and the electronics in the optical module have been re-shuffled into its new form, as shown in Fig. 15. Most backend functions like CDR and SerDes are merged into a CMOS PHY chip (also known as DSP on some occasion), where intensive digital equalization is also brought in to compensate for the worsened signal integrity in PAM-4 signalling. Meanwhile, most high-speed front-end analog electronics (TIA/Driver) remain SiGe-based to leverage its superior analog performance. However, a monolithic approach is inevitable for CPO application that requires an extreme level of integration and power consumption, which will require the analog TIA and Driver to be integrated into the CMOS EIC chip. Here, we discuss the design issue of the TIA.

Fig. 15.

NRZ pluggable vs. PAM-4 CPO transceiver, red: SiGe, blue: CMOS, purple: silicon photonics

Current and future challenges

Since CMOS is optimized for digital function, it exhibits natural advantages in power consumption and cost structure (at volume). However, it also shows weakness in analog performance. For CMOS based high-speed PAM-4 TIA to be integrated in CPO EIC, there are several critical design challenges.

1. Noise. Although the bandwidth is halved in PAM-4 signalling, the SNR also shrinks by three folds and the role of noise is further amplified. The noise floor of a TIA is inversely proportional to a circuit parameter known as the transimpedance limit [37], which is generally dictated by the technology speed expressed in the form of transit frequency (ft). Therefore, in SiGe-based design, faster technology with higher ft is always preferred in implementing low-noise TIA. However, for CMOS TIA, more advanced technologies do not necessarily offer a dramatic boost in ft when FinFET comes into play from 16 nm node and beyond [38]. To make things worse, it is often difficult to bias the transistor in its peak ft condition due to several design constraints in CMOS [39]. Therefore, noise performance in CMOS TIA suffers.

2. Bandwidth. In general, high-speed optical communication circuits need the largest bandwidth over other applications, which keep pushing the limits of technology that foundries can offer. In this context, at least three factors make CMOS inferior compared to SiGe. First, the limited supply voltage (< 1 V) makes it difficult to build an effective buffer in advanced CMOS compared to SiGe, where the high-performance buffer (emitter follower) can decouple the gain stages and protect bandwidth [40]. Second, the low supply voltage also limits the maximum gain of each stage, as the transconductor transistor is biased at high current density for speed. Therefore, more gain stages are needed, inducing a severe bandwidth drop effect [41]. Finally, CMOS transistors have relatively small intrinsic device parasitics and large device footprints, making them very sensitive to extrinsic wiring parasitics, which can even dominate the overall parasitics. Together, these aspects make it difficult to design high-bandwidth circuits in CMOS.

3. Linearity. As data format evolves from NRZ to PAM-4, a new design consideration, linearity, comes into play. Non-linearity in PAM-4 signal will cause gain compression and an increased error rate. The difficulty resides in the fact that the input signal strength at the receiver side can vary more than 30 dB (1000X), rendering it difficult for the receiver to remain linear. On the contrary, at the transmitter side, the signal fed into the output driver stage is set by design, which alleviates the difficulty. Another issue comes from the direct contradiction between the reduced CMOS supply voltage (< 1 V) and the large receiver output swing needed to drive the following ADC stage, which can be several hundreds of millivolts strong, making the linearity difficult to maintain. An additional issue that also heavily impacts the PAM-4 signal integrity is phase linearity, to be clarified from the magnitude linearity discussed so far. Phase linearity is closely tied to the time-domain jitter, which can have a major impact on the decision circuit when the signal is transformed from analog to digital domain. Since there are 16 possible signal change patterns in PAM-4, the resulted jitter from phase non-linearity has a much severe adverse effect than that in NRZ.

Advances in science and technology to meet challenges

1. Noise reduction. Since the transimpedance limit tends to be the key constraint that limits TIA noise, it is possible to reduce noise by tackling it. The first is a divide-and-conquer approach to circumvent the transimpedance limit, which decouples the bandwidth and noise goals and solves them sequentially [42]. The second type of approach manages to exceed the transimpedance limit by using cascaded multi-stage amplifier [39]. Of course, one can always combine the two approaches to reach an even better outcome. Moreover, the much lower capacitance from germanium photodiode (PD) in most silicon photonics platforms [43] can also greatly reduce noise [40], where a synergized co-design approach is needed [44].

2. Bandwidth extension. The most popular approach for bandwidth extension in CMOS is to use inductor peaking. Many sophisticated inductive peaking approaches have been developed at various stages of the amplification chain. At the pre-amplifier stage, bondwire inductance is often exploited to create series peaking with the capacitance from PD [40] to extend bandwidth. With on-chip inductors, many recent CMOS TIAs have reached a data rate of 53 to 64 Baud [45, 46]. Notice that with many inductive peaking, the transfer function tends to have in-band gain ripple or deteriorated phase linearity. Thus, the bandwidth extension at PAM-4 and linear application bears more care and simulation.

3. Linearization. Most linearization techniques rely on gain control at the topological level or source/emitter degeneration at the transistor level to reduce non-linearity. In the CMOS PAM-4 receiver, by tuning the gain of VGA (Variable Gain Amplifier) that follows the TIA [45], 2% of THD can be achieved up to a few hundred microamperes, which is on par or even better than those built with SiGe [47]. In the CMOS coherent receiver, the linearity is generally better due to the differential input characteristic. In Ref. [48], with the help of gain control and source degeneration in the pre-amplifier stage, less than 2% of THD is achieved with 1.8 mApp input current.

Concluding remarks

As CPO will proliferate in the future 100 Tb/s era due to the imminent bandwidth bottleneck at data center, integration of front-end receivers with back-end processing electronics will become inevitable. This requires the technology for receiver design to shift from analog optimized SiGe to digital optimized CMOS, which will bring tremendous challenges. Possible design techniques to overcome problems regarding noise, bandwidth and linearity have been introduced here. As these techniques are combined with the instinct advantage of low power and low cost, monolithic CMOS electronics will fully unleash its power in the era of CPO.

Acknowledgements

This work was supported partly by the National Natural Science Foundation of China (Grant No. 62074126), National Key Research and Development Plan (No. 2020YFB2205801), Shaanxi Key Research and Development Plan (No. 2020GY-019), and Fundamental Research Funds for the Central Universities (No. XZY012020018).

2.5D and 3D advanced packaging for co-packaged optics (CPO)9

Status

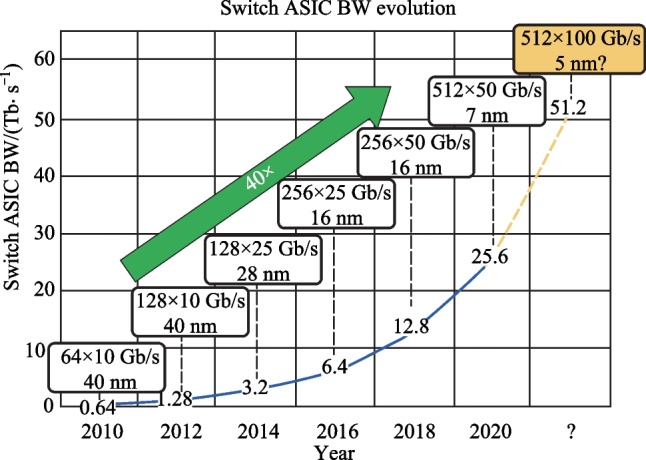

As data center traffic grows at an unprecedented rate driven by advances in Artificial Intelligence (AI) and Machine Learning (ML), network infrastructure must expand capacity while maintaining its total power consumption and footprint. Ethernet switches and optical devices also demand more bandwidth each year, with higher bandwidth density and energy efficiency [1–3].

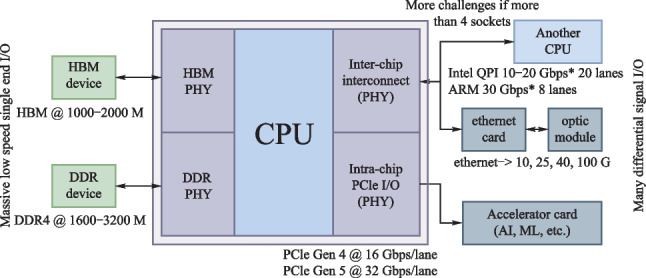

From 2010 to 2020, the bandwidth capacity of commercial switch integrated circuit (IC) increased by 40 times, from 0.64 to 25.6 Tb/s, while the process node of switch IC decreased from 40 to 7 nm, as depicted in Fig. 16.

Fig. 16.

Bandwidth growth of Switch and ASIC in the last decade [4]

If the transmission bandwidth of the switch IC per rack unit (RU) reaches above 25.6 Tbps, a RU needs 32 or more 800 Gbps face-plate-pluggable optical modules. However, the 800 Gbps pluggable optical modules with the current same form factor are challenging in terms of the required densities of electrical/optical connector, power consumption, and so on.

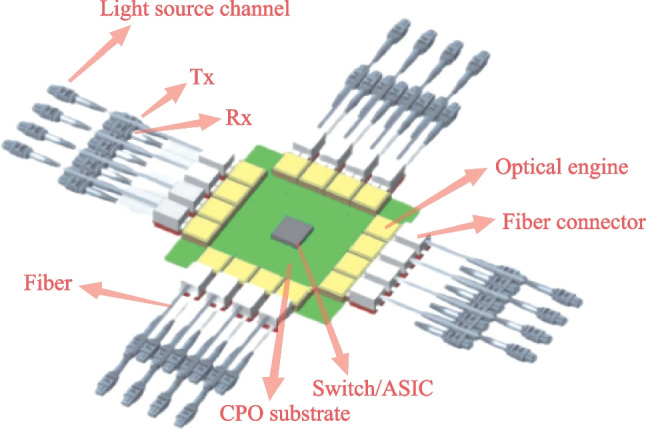

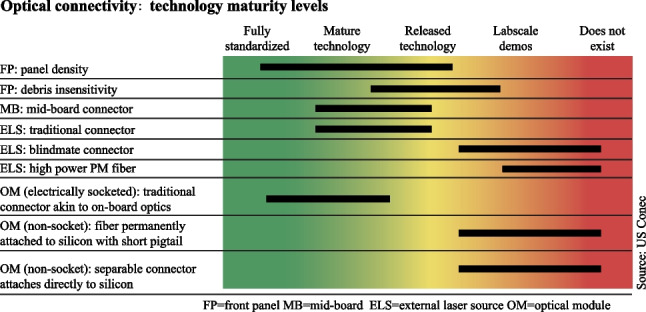

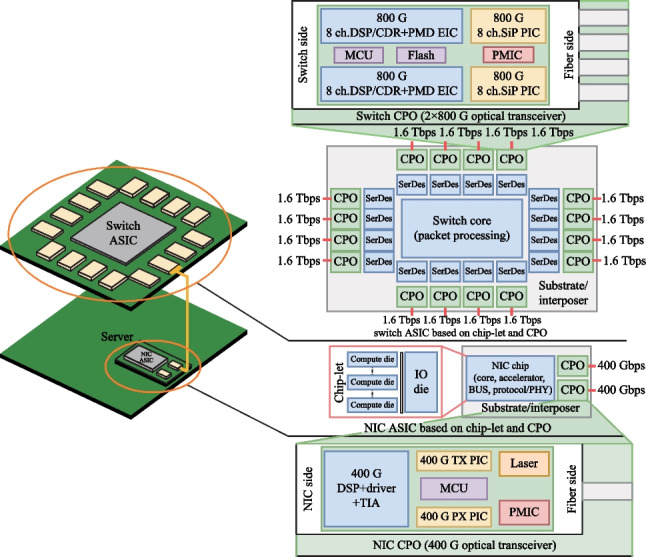

Therefore, co-packaged optics (CPO) is regarded by many companies and experts as a key technology to achieve higher speed, wider bandwidth, and greater throughput [5, 6]. It can minimize the power of the electrical links to or from the optics and substantially increase the total escape bandwidth of the chip packages by offering an extra dimension for wiring additional chip pins. In March of 2021, OIF launched the 3.2 T co-packaged module project and developed a 3.2 T co-packaged optical module draft, defining Ethernet oriented switching applications. The mechanical layout of the CPO assembly is shown in Fig. 17 [7].

Fig. 17.

Full assembly of co-packaged switch, showing sixteen transceiver modules

CPO solutions have been emerging in recent years. A collaboration between IBM and II-VI corporated to develop a chip-scale co-packaged optics module that can be directly attached to the top of an organic first-level package. They achieved energy efficiency of < 4 pJ/bit (16 channels) and the data rate is 56 Gb/s NRZ [8].

Ranovus and IBM launched 51.2 Tb/s optical modules based on CPO technology. They developed fiber V-groove interconnect packaging technology that utilizes passive alignment capabilities to achieve low insertion losses across a wide spectrum of O and C bands [9].

Intel has designed, developed, and demonstrated a SiPh (Silicon Photonics) IC-based transmitter and receiver suitable for optical co-packaging with switch ASICs. It has a compact form factor capable of bandwidth density > 40 times that of 100 Gbps QSFP28 pluggable optics, and has a power efficiency of < 20 pJ/bit and shows a path to 13.5 pJ/bit [10].

Ayar-labs and Intel made the first CPU integrated with optical I/O in package. They used O-Chiplet and EMIB technology to achieve < 5 pJ/bit energy efficiency and more than 1Tbps/mm bandwidth density [1, 11].

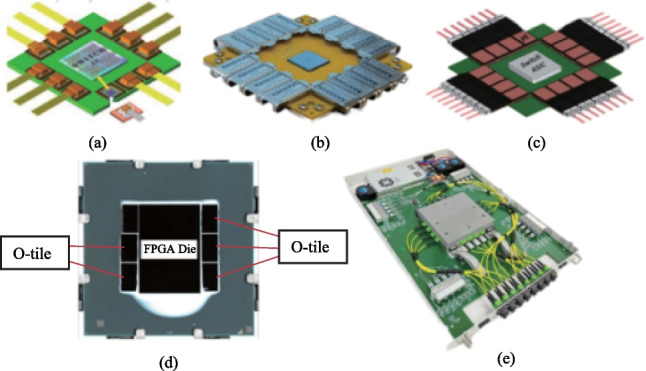

Hengtong Rockley has developed a 3.2 T CPO working prototype based on silicon optical technology, which shortens the distance between photoelectric conversion function and core switch chip [12]. These productions are shown in Fig. 18.

Fig. 18.

CPO solutions. a IBM and II-VI. b Ranovus. c Intel. d Ayar-labs. e Hengtong Rockley

Current and future challenges

The CPO is capable of high-capacity transmission, but still faces a series of challenges.

1. Light source. The integration of laser source has always been the difficulty of photonic integrated circuits. As we need to make light propagate inside CPO, the light from the light source passes through the fiber and enters the optical chip and other components through a specific coupling mode. It is necessary to ensure that the transmission of light is stable, convenient, and reliable. Whether to use on-chip laser or external laser is determined by a variety of factors, such as operating temperature, laser reliability, and SiPh process platform compatibility [13].

2. Coupling structure. The coupling boils down to a huge size mismatch between the fiber core and the Si waveguide, causing considerable optical transmission loss when light emitting from the fiber core enters the waveguide directly [14]. In most cases, we can achieve low coupling loss (CL) by edge coupling, grating coupling, and evanescent coupling. Each method inevitably requires designing a suitable spot size convert (SSC) to match the waveguide.

3. Thermal management. The power consumption of the switch die is much higher than that of the CPO module. Thermal crosstalk on the CPO module from the switch die is a severe challenge. Meanwhile, some optical devices in PIC (Photonics IC) are sensitive to temperature, especially the switch die with large power consumption, or on-chip laser integrated in close proximity to PIC. Baehr-Jones’s group [15] fabricated micro-ring structure with a radius of 30 μm on SOI substrates and tested their temperature sensitivity. When the temperature was increased from 20 to 28 °C, a shift of 0.4 nm was found in the transmission spectrum, while the insertion loss changed by up to 9 dB.

4. High-speed interconnect. Compared with traditional packaging solutions, CPO requires higher data transmission speed, but the existing packaging structure cannot achieve high-speed and high-density interconnection. 2.5D Si interposer and 3D chip stacking are the main technology to achieve the target [16].

Advances in science and technology to meet challenges

Recent advanced solutions based on these challenges have been proposed.

1. Inside or offside laser integration. We have summarized three methods that roughly include off chip laser, attached laser, and bonded hybrid laser. Although the off chip laser is flexible and substantially reduces the power of the CPO, it may require accurate alignment for large area optical interconnection and expensive long-term polarization-maintaining fiber (PMF) [17]. The most representative technology for the attached laser is that the laser is mounted to the PIC by flip-chip, and the light is guided into PIC by the edge coupler. As for bonded hybrid laser, there are three solutions, specifically directly bonding, insulation bonding, and metallic bonding [18].

2. Multi-tip and overlapped taper’s structure. Now several research groups have developed the optical coupler that achieved less than 1 dB CL. For example, Takei’s group launched a knife-edge shape coupler of 0.21 − 0.35 dB CL [19]. Papes’ group designed a large mode size for Si photonic wire waveguide coupler of 0.75 dB CL [20]. Picard’s group proposed a structure of Si taper that is under multiple SiN rods and cladded by the SiON, and it achieved 0.5 − 0.9 dB CL by verification [21]. In addition, the photonic wire bonding (PWB) technology no longer needs the traditional high-accuracy alignment between the large-sized optical fibers and the waveguide. Christian Koos and his team connected Indium phosphide (InP)-based horizontal cavity surface emitting lasers (HCSELs) to passive silicon photonic chips by PWB, which achieved the lowest insertion loss of 0.4 dB at that time [22].

3. Liquid-cooling and special structure cool plate. In recent years, some companies have announced several methods for the thermal management of the optoelectronic integration. Intel’s liquid cooling solution is for 540 W of switch IC and 56 W of each CPO. According to the conditions given in the article, they lowered the temperature of the EIC (Electronics IC) by 35°C and the switch die by 8°C [1]. Cisco’s heat sink and cold plate assembly is a great plan [23]. Compared to forced-air cooling, liquid cooling has a more pronounced cooling effect, such as less noise, more uniform heat dissipation, and does not require an additional power supply to power the fan. In addition, cold plate with thermal interface materials and a heat spreader or heat sink can be combined with the liquid cooling solution for possibly better performance.

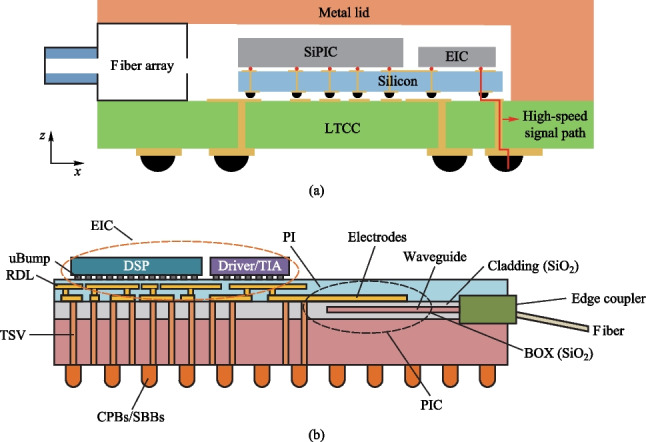

4. 2.5D&3D packaging of CPO module. Institute of Microelectronics of the Chinese Academy of Sciences (IMECAS) has been dedicated to the research of advanced packaging technology. As for the packaging form of the CPO module, IMECAS has developed 2.5D&3D packaging technology. On one hand, the solution for 2.5D packaging is that silicon PIC and EIC are flipped on 2.5D silicon interposer, and secondary packaging is then used through a low-temperature ceramic substrate [245]. On the other hand, there are two options for implementing 3D packaging. First, the EIC is placed on PIC by micro-bump (pitch: 40 μm) and the stacking structure on PCB through wire bonding. Second, the PIC is integrated in the active photonic interposer while retaining the passive function. TSV (10 μm × 100 μm) and redistribution layer (RDL) are then fabricated on the basis of EIC and the EIC is attached to the interposer face to face. Finally, the substrate and interposer will be connected by a solder ball (pitch: 150 μm). Our high-frequency transmission line shows an excellent insertion loss at 67 GHz [24]. The 3D solutions are shown in Fig. 19.

Fig. 19.