Abstract

A lateral overflow integration capacitor (LOFIC) complementary metal oxide semiconductor (CMOS) image sensor can realize high-dynamic-range (HDR) imaging with combination of a low-conversion-gain (LCG) signal for large maximum signal electrons and a high-conversion-gain (HCG) signal for electron-referred noise floor. However, LOFIC-CMOS image sensor requires a two-channel read-out chain for LCG and HCG signals whose polarities are inverted. In order to provide an area-efficient LOFIC-CMOS image sensor, a one-channel read-out chain that can process both HCG and LCG signals is presented in this paper. An up/down double-sampling circuit composed of an inverting amplifier for HCG signals and a non-inverting attenuator for LCG signals can reduce the area of the read-out chain by half compared to the conventional two-channel read-out chain. A test chip is fabricated in a 0.18 m CMOS process with a metal–insulator–metal (MIM) capacitor, achieving a readout noise of 130 for the HCG signal and 1.19 V for the LCG input window. The performance is equivalent to 103 dB of the dynamic range with our previous LOFIC pixel in which HCG and LCG conversion gains are, respectively, 160 and 10 .

Keywords: CMOS image sensor, LOFIC, HDR, read-out chain, small area, double-sampling

1. Introduction

In the development of Internet of Things (IoT), complementary metal oxide semiconductor (CMOS) image sensors are expected to be used under extreme-illumination conditions, e.g., outdoors, in which a high-dynamic-range (HDR) CMOS image sensor is required to prevent objects from becoming overexposed or underexposed. For instance, the intra-scene dynamic range required to cover both an LED sign and a person on a sidewalk in a night scene at a local town is over 86 dB [1]. The intra-scene dynamic range is defined as the ratio between electron-referred noise floor and maximum signal electrons within a single image [2]. Furthermore, an intra-scene dynamic range of greater than 100 dB is required for driver-assistance systems in automotive vehicles [1,3,4].

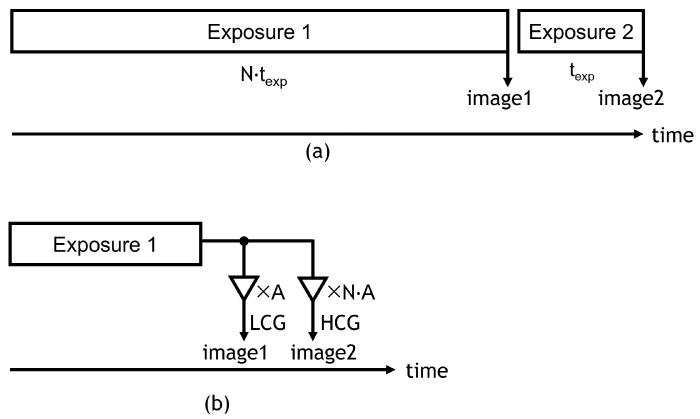

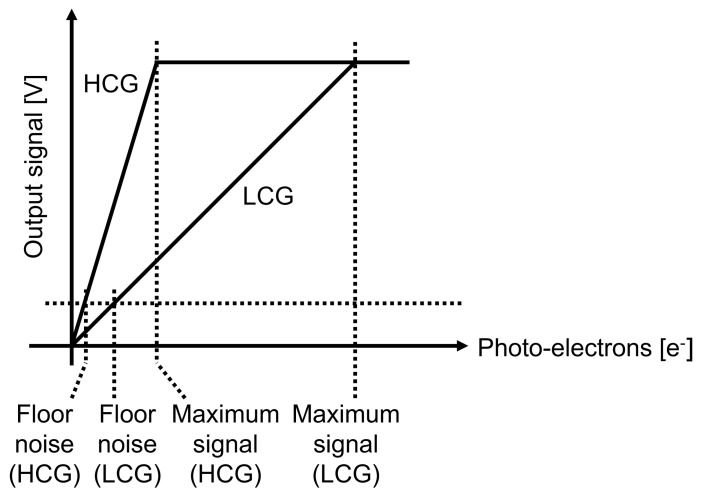

In order to realize HDR CMOS image sensors, many approaches have been proposed. Non-linear response approaches such as logarithmic compression [5,6,7] and knee compression [8] can reduce the data bandwidth because of their low bit-resolution, but are not preferred in terms of complex image signal processing. Linear response approaches such as multiple-exposure, high-dynamic-range (MEHDR) [9,10,11,12] and single-exposure, high-dynamic-range (SEHDR) approaches are preferred for simple image-signal processing. Even though the MEHDR approach is widely adopted, MEHDR images that combine two images taken at different exposure timings will be distorted due to the misalignment of the timings, as shown in Figure 1a. Thus, the SEHDR approach is becoming increasingly attractive. SEHDR is realized with dual conversion gain (DCG) pixels [13,14,15] or lateral overflow integration capacitor (LOFIC) pixels [14,15,16,17,18,19,20,21,22,23], in which the low-conversion-gain (LCG) signal and high-conversion-gain (HCG) signal are combined, as shown in Figure 1b. In DCG pixels, the photoelectrons integrated in a photodiode (PD) are read out twice in different gains, namely LCG and HCG. Since the electron-referred noise is low for the HCG, even though the maximum number of the electron readout is limited due to a given signal voltage range, as shown in Figure 2, the pixel signal under low illuminance is visible. On the other hand, since the maximum number of electrons in the read-out at LCG is high, as shown in Figure 2, the pixel signal under high illuminance is extended. Thus, the combined signal can achieve HDR with low read-out noise and large PD full-well capacity. The LOFIC pixel utilizes a similar two-times read-out scheme, HCG and LCG, and can achieve a higher dynamic range than DCG pixels because the photo-electrons are integrated not only in the PD but also in high-density capacitors. However, the circuit area for the LOFIC pixels is large due to the two-channel read-out chain for polarity-inverted LCG and HCG signals [20,22,23], while the DCG pixel signal has a one-channel read-out chain because the signal polarities of the LCG and HCG signals are the same [13]. Challenges to the read-out chain for LOFIC-CMOS image sensors are summarized as follows:

The LOFIC pixels outputs polarity-inverted HCG and LCG signals.

The circuit area of the two-channel read-out chain for the LOFIC pixels is larger than that for DCG pixel.

The chip cost of LOFIC-CMOS image sensors will be high because of the large circuit area.

Figure 1.

Image generation methods of MEHDR and SEHDR. (a) MEHDR; (b) SEHDR.

Figure 2.

Photo−conversion characteristics of LOFIC−CMOS image sensors.

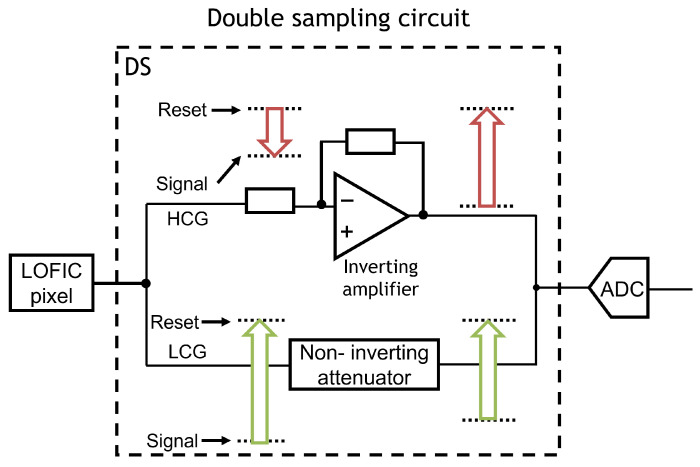

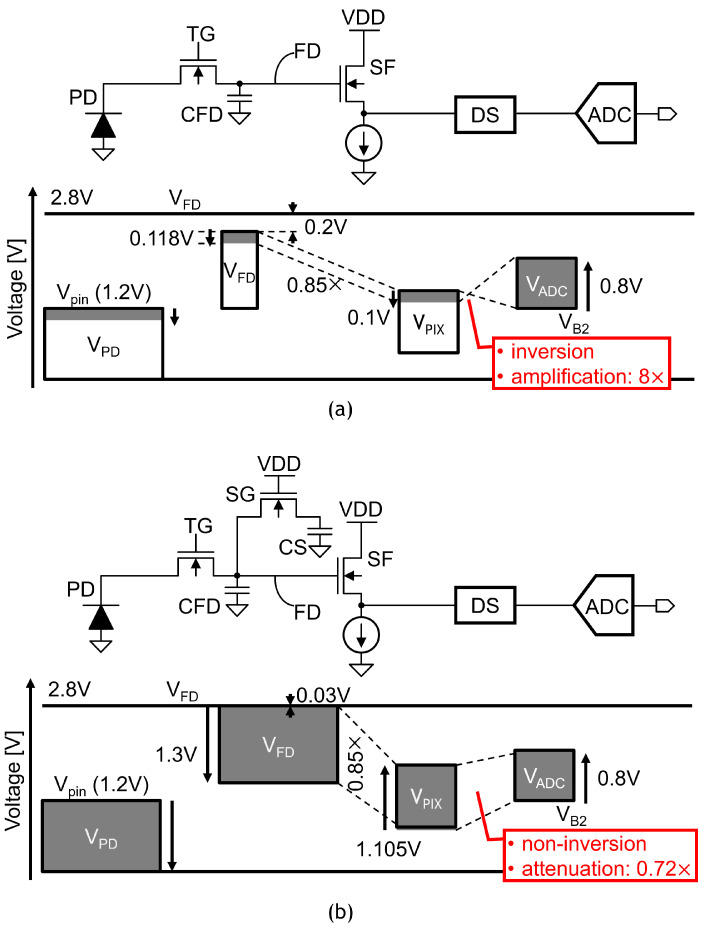

The read-out chain performs double-sampling for both HCG and LCG signals to cancel the pixel offset voltage and/or pixel reset noise, followed by analog/digital conversion. To realize a single-channel read-out chain and reduce the chip cost of LOFIC-CMOS image sensors, an up/down double-sampling circuit composed of an inverting amplifier and non-inverting attenuator is proposed in this paper. Figure 3 represents the signal processing function of the double-sampling circuit.

Figure 3.

Signal processing function of the double-sampling circuit.

The pixel HCG signal, which is the voltage difference between the reset level and signal level from LOFIC pixel, is read out with the inverting amplifier for low-input referred circuit noise. The pixel LCG signal, which is the voltage difference between reset level and signal level from the LOFIC pixel, is then read out with the attenuator to increase the maximum signal range. Even though the polarity of the LCG and HCG signal output from the LOFIC pixel is inverted, the polarity of the input signal to the following analog/digital converter (ADC) is the same and a single ADC can process both the HCG and LCG signals. Moreover, the attenuator is merged with the ADC, such as column parallel successive-approximation-register (SAR) ADC, to further decrease the area of the double-sampling circuit. A test chip of the proposed double sampling circuit was fabricated with a standard CMOS process with metal–insulator–metal (MIM), and evaluated to estimate the dynamic range of LOFIC-CMOS image sensors with the proposed double-sampling circuit. Our contribution is summarized as follows:

We propose a single-channel read-out chain for the LOFIC pixel to realize a small-area peripheral circuit for LOFIC-CMOS image sensors.

We present a design methodology of signal voltage range from the pixel to the ADC to maximize the effective full-well capacity (FWC) of the LOFIC-CMOS image sensors.

We estimate the LOFIC pixel dynamic range with the proposed up/down double-sampling circuit based on the measurement results of a fabricated test chip.

Section 2 provides a basic pixel schematic and the operation timing of the LOFIC pixel. The proposed single-channel read-out chain with the up/down double-sampling circuit is described in Section 3, followed by the design and measurement results of a fabricated test chip shown in Section 4. Section 5 provides a summary of this paper.

2. Lateral Overflow Integration Capacitor (LOFIC) Pixel

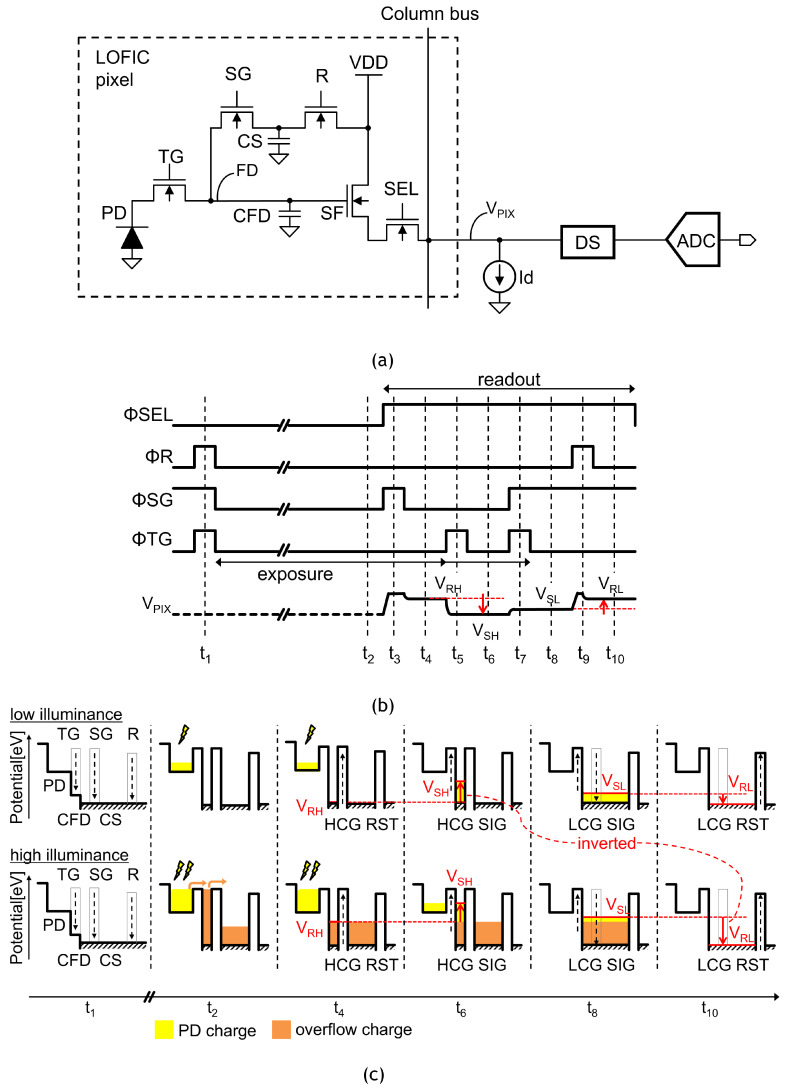

Figure 4a shows a schematic diagram of the LOFIC pixel that is composed of a photodiode PD, a transfer gate TG, a switching gate SG, a reset gate R, a source-follower transistor SF, and a select transistor SEL, the parasitic capacitance on FD node CFD, and a charge storage capacitor CS. The double-sampling circuit, DS, derives the voltage difference between a reset level () and a signal level () from LOFIC pixel, and the voltage difference is then digitized by an ADC. The photo-electrons from the pixel are read out twice by SF, which is composed of a source-follower transistor and bias (Id). First, the photo-electrons integrated in the PD are read out in the HCG mode while SG is turned off. The HCG signal is suitable for the case with low illuminance. Secondly, the photo-electrons integrated in the PD, CFD and CS are read out in the LCG mode while SG is turned on. The photo-electrons generated in PD overflow into the FD node beyond the potential barrier of the TG when the PD is saturated. Then, photo-electrons overflow into the CS capacitor beyond the potential barrier of the SG when FD is saturated. The LCG signal is suitable for the case with high illuminance.

Figure 4.

Circuit schematic, pixel operation timing and potential diagram of a lateral overflow integration capacitor (LOFIC) COMS image sensors. (a) Pixel circuit schematic of a LOFIC-CMOS image sensor; (b) pixel operation timing of LOFIC-CMOS image sensors; (c) potential diagram of LOFIC-CMOS image sensors.

The operation timing and electric potential diagrams of the LOFIC pixel are shown in Figure 4b,c, respectively. At the beginning of the exposure period (), the transistors R, SG, and TG are turned on to reset the PD, the CFD, and the CS. During the exposure period (), as shown in Figure 4c, photo-electrons generated under low illuminance are integrated in the PD, while photo-electrons under high illuminance are integrated in the PD, CFD, and/or CS. At the end of the exposure period, the pixel signal readout is provided when the SEL transistor is turned on.

The readout for the HCG reset level is provided at after the SG is pulsed to share a dark current charge integrated in the small CFD with a large CS (). Then, the HCG signal level readout is provided at after the charge transfer pulse is applied to the TG gate at . The voltage difference between and is derived using the following double-sampling circuit. Since the same FD reset noise is included in both and , a low-noise signal is readout under low illuminance. The conversion gain obtained by is as high as 160 in our previous work [16], where and CFD are the elementary charge and parasitic capacitance for the FD node, respectively. The HCG signal shows a linear photoconversion response for low-input illuminance, in which the generated photo-electron charge is lower than the charge storage capacity of the PD. It is noted that the voltage difference between and is negative because the electric potential at the FD node increases during the transition from to .

The LCG signal level readout is provided at after the SG gate is turned on and the TG is pulsed again at to merge the photo-electrons integrated in the PD, CFD, and the CS. Then, the LCG reset level readout is provided at after R is pulsed again to reset the CFD and CS at . The voltage difference between and is derived from the following double-sampling circuit. Since the conversion gain provided by is as low as 10 [16], the LCG signal shows a linear photoconversion response up to a high level of illuminance. Even though the reset noise in the LCG signal is large due to the uncorrelated double-sampling in and , the noise is not visible as long as it is lower than the optical shot noise. It is noted that the voltage difference between and is positive because the electric potential at the FD node reduces during the transition from to .

A post-processing circuit selects the HCG signal if the LCG signal is lower than a given threshold voltage; conversely, it selects the LCG signal if the LCG signal is higher than the threshold voltage. The LCG signal is also multiplied for signal linearization from low illuminance to high illuminance, and an HDR image is realized thanks to the low-noise HCG signal and the high-FWC LCG signal. However, both HCG and LCG signal readouts should be provided for the post-processing stage. Thus, a two-channel read-out chain is typically utilized for HCG and LCG signals for which the polarity is inverted.

3. Proposed Readout Circuit

A read-out chain for the LOFIC pixel to process both HCG and LCG pixel signals is presented in this section. First, a conceptual view of the voltage domain level diagram is shown to visualize the critical voltage signal. Then, an up/down double-sampling circuit is proposed in accordance with the voltage diagram, along with the evaluation results of the test chip.

3.1. Voltage Domain-Level Diagram

For LOFIC-CMOS image sensors, a voltage domain-level diagram is designed, as shown in Figure 5. The voltage diagram is given for the pinning voltage of the PD (), the signal voltage swing at the FD node and at the pixel SF output, and the input window of an ADC.

Figure 5.

Voltage level diagram of LOFIC-CMOS image sensors used to reduce input-referred noise and to increase pixel FWC. (a) HCG signal: gain of double sampling circuit should be high to decrease the input referred noise at FD node; (b) LCG signal: gain in double-sampling circuit should be low to increase the signal swing at FD node.

For the HCG signal shown in Figure 5a, the voltage gain of the double-sampling circuit needs to be high enough and is selected to decrease the input-referred circuit noise to achieve a high dynamic range. The input window of the double sampling circuit is therefore provided by 0.1 V for the 0.8 V ADC input window [2], and the signal voltage swing at the FD node is limited to below 0.118 V with a source-follower gain. Even though the clock feedthrough caused on small CFDs is as large as 0.2 V when the SG is turned off, the voltage margin used to transfer the photo-electrons integrated in the PD to the FD node is large enough.

For the LCG signal shown in Figure 5b, to transfer all PD charges to the FD node, the voltage swing at the FD node is limited to below for , and a 2.8 V power supply voltage and voltage margin in PVT variations. It is noted that the clock feedthrough caused for CFD and CS is as small as 0.03 V when the RST is turned off. The maximum voltage swing at the FD node is set to be 1.3 V because the FWC is given by . The input window of the double-sampling circuit is given by 1.105 V with a source-follower gain, and the gain of the double-sampling circuit is set as for a 0.8 V ADC input range.

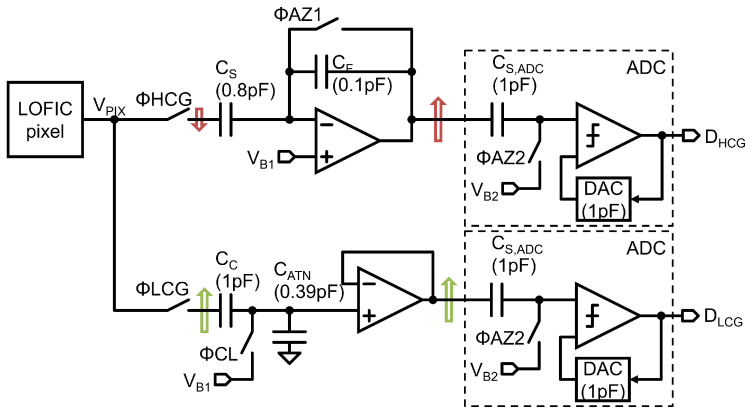

3.2. Read-Out Chain with an up/down Double-Sampling Circuit

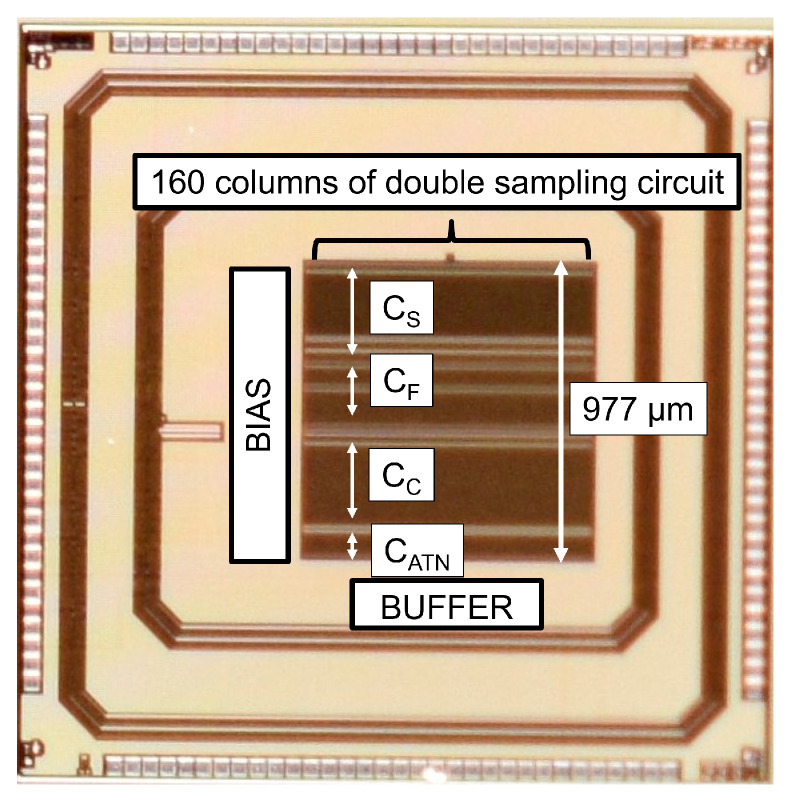

A baseline read-out chain that satisfies the voltage domain level diagram is shown in Figure 6. The LOFIC pixel output signal is fed to an inverting amplifier when is high. The voltage difference between the reset level and signal level is inverted, amplified by 8 times, and then digitized with a SAR ADC. The inverting amplifier is composed of a sampling capacitor , a feedback capacitor , and an amplifier [24,25]. The ADC is composed of a sampling capacitor , an SAR capacitor digital/analog converter (DAC), and a comparator. The LOFIC pixel output signal is fed to the attenuator when is high. The voltage difference between the signal level and reset level is attenuated times and then digitized with the ADC. The attenuator is composed of a coupling capacitor , an attenuation capacitor , and a voltage-follower [26]. Since the signal polarities of the HCG and LCG signal at the ADC input are the same, the same ADC circuit is used for HCG and LCG signals. However, this two-channel circuit requires a large area and will increase the cost of LOFIC-CMOS image sensor chips. The total capacitance of this baseline read-out chain is 6.29 pF, which can be used to roughly estimate the circuit area that is dominated by the layout area of the capacitors.

Figure 6.

A baseline two-channel read-out chain for LOFIC pixels.

In order to reduce the area of the read-out chain, an area-efficient read-out chain with an up/down double-sampling circuit is proposed, as shown in Figure 7. While the inverting amplifier is the same as the baseline circuit, the attenuator is merged in the ADC. The pixel output signal is sampled in a and attenuated with when is high, in which the coupling capacitor also operates as a sampling capacitor of the ADC. The ADC is also shared for the HCG and LCG signals. The attenuation capacitor is disconnected during the HCG mode when is turned off. The total capacitance of the proposed double-sampling circuit is 3.29 pF. The area of the proposed read-out chain will be reduced by around compared to the baseline read-out chain.

Figure 7.

Schematic diagram of the proposed double sampling circuit.

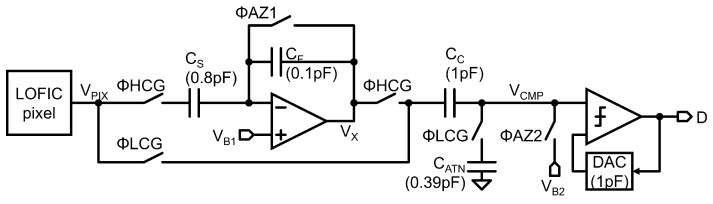

Figure 8 shows a timing diagram of the read-out chain with the up/down double-sampling circuit. In the HCG mode, is high. First, and are increased to sample the pixel reset level and reset the amplifier and the comparator (). Then, is decreased to hold in (), and is decreased to hold the bias voltage difference given by in a clamp capacitor (). After the pixel output voltage drops to , the amplifier output voltage at is obtained as follows

| (1) |

Figure 8.

Timing diagram of the double-sampling circuit.

The comparator input voltage at is given by

| (2) |

After this operation, the correlated double-sampling signal with gain is converted into a digital signal with the SAR-ADC when is high.

In the LCG mode, is high. First, is increased to sample the pixel signal level and to reset the comparator (). is then reduced to hold in (). After the pixel output voltage rises to the pixel reset level , the comparator input voltage at is given by

| (3) |

After this operation, the differential double-sampling signal with a gain of is converted into a digital signal with the ADC. Equations (2) and (3) indicate that the signal polarities of HCG and LCG signals at the comparator input are alined.

3.3. Noise Analysis

In the HCG mode, the input-referred circuit noise needs to be low to achieve a high dynamic range. On the other hand, in the LCG mode, the noise requirement can be relaxed as long as the noise of the read-out chain is lower than the photon-shot noise at the switching point between the HCG mode and the LCG mode.

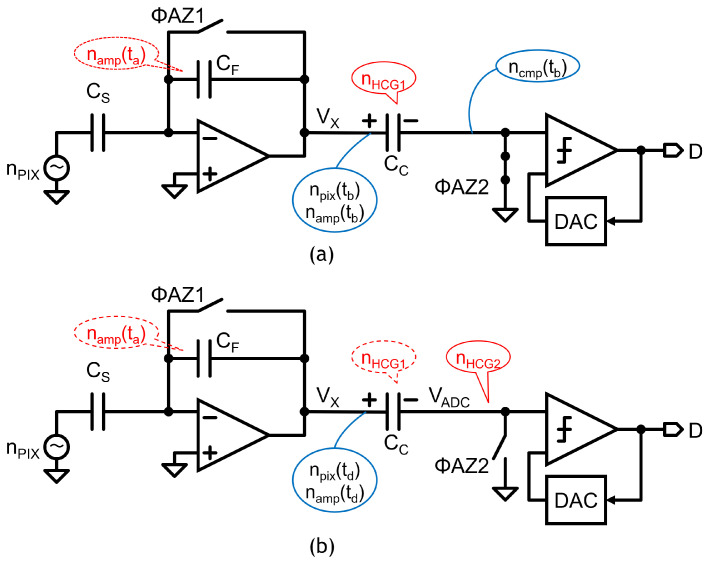

The HCG noise is analyzed with the equivalent circuits shown in Figure 9, where , , for simplicity. At the sampling of in when is turned off (), the reset noise of the amplifier, , is also sampled in . When is turned off, the reset noise , pixel output noise , amplifier output noise and comparator reset noise are sampled in (). The total noise in , , is thus given by

| (4) |

Figure 9.

Equivalent circuits to analyze HCG noise. (a) Circuit and noise at ; (b) Circuit and noise at .

During the analog/digital conversion of the HCG signal, the total noise at the comparator input, , is given by

| (5) |

Since the amplifier reset noise is removed, the total HCG noise is simulated with the sum of the noise at and the noise at . The input-referred noise is given by .

The LCG noise is analyzed with equivalent circuits shown in Figure 10, where for simplicity. When the LCG signal voltage is sampled in , with turned off, the pixel output noise and the comparator reset noise are also sampled in (). The total noise held in , , is thus given by

| (6) |

Figure 10.

Equivalent circuits to analyze LCG noise. (a) circuit and noise at ; (b) circuit and noise at .

During the analog/digital conversion of the LCG signal, the total noise at the comparator input, , is given by

| (7) |

The noise is lower than that of the baseline circuit (Figure 6) in which the voltage-follower noise is also imposed. The LCG noise is estimated using the sum of the AC noise simulation results with the pulse signal-setting at and . The input-referred noise is given by .

SPICE simulation results are summarized in Table 1. The input-referred HCG noise is given by . The input referred LCG noise is given by 545.9 . Since the LCG noise of the baseline circuit is 652.6 , the LCG noise of the proposed double-sampling circuit is lower than that of the baseline circuit by . The total capacitance and LCG noise of the baseline circuit and proposed double-sampling circuit is summarized in Table 2.

Table 1.

AC noise simulation results.

| HCG | ||

| Noise @ | Noise @ | Input referred total noise |

| 303.3 | 974.4 | 127.6 |

| LCG | ||

| Noise @ | Noise @ | Input referred total noise |

| 39.9 | 391.0 | 545.9 |

Table 2.

Comparison of the proposed read-out chain with the baseline read-out chain.

| Total Capacitance | Noise | ||

|---|---|---|---|

| HCG | LCG | ||

| Baseline | 6.29 pF | 122.1 | 652.6 |

| Proposed | 3.29 pF | 127.6 | 545.9 |

4. Fabrication and Evaluation of a Test Chip

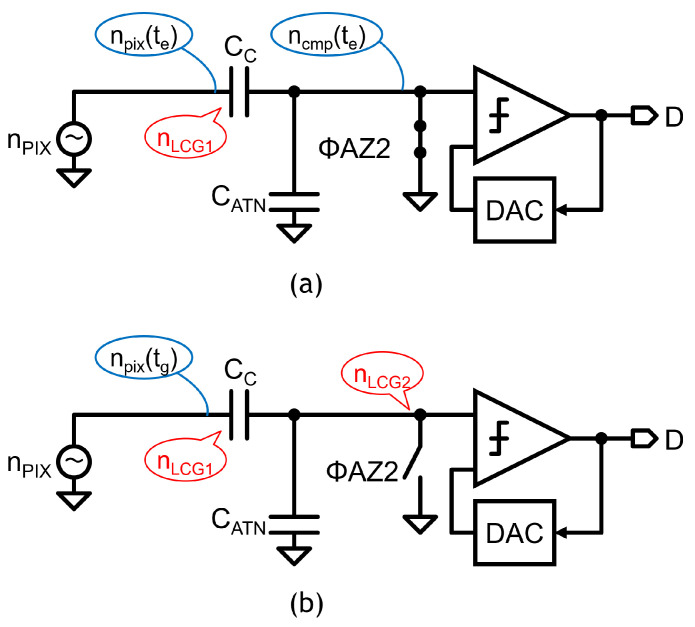

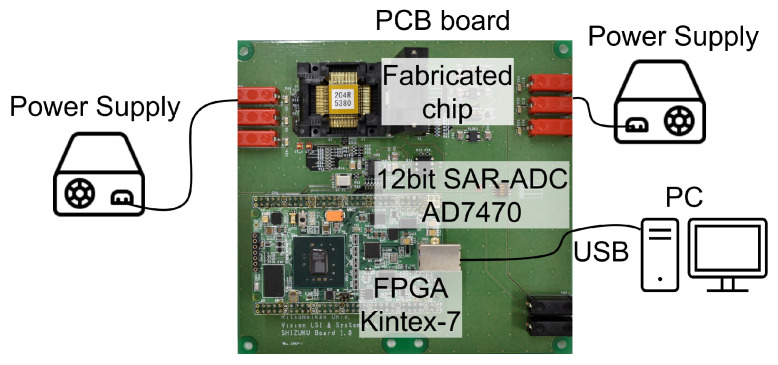

In order to verify the concept of the proposed read-out chain, a test circuit, which is shown in Figure 11, was fabricated with the m 1P5M CMOS process and with MIM capacitors. The pseudo-pixel signal is supplied from external voltages, namely the HCG and LCG reset voltage VR, HCG signal voltage VSH, and LCG signal voltage VSL. An output buffer is implemented in the test chip to drive an off-chip 12-bit SAR-ADC.

Figure 11.

Test chip of the proposed up/down double-sampling circuit.

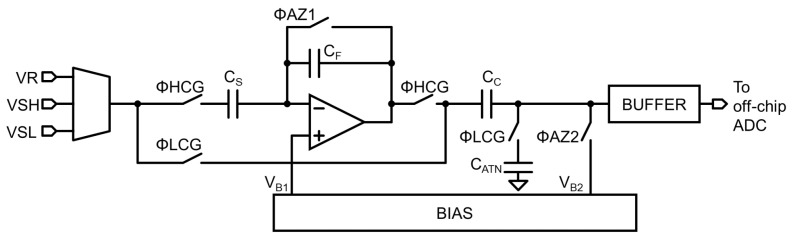

A photograph of the fabricated test chip is shown in Figure 12. The 160 column of the up/down double-sampling circuits are laid in parallel to represent the layout constraint in the CMOS image sensor. The column pitch is 6.02 m, which is obtained according to the minimum design rule of an MIM capacitor. The layout height of a column double sampling circuit is 977 m. Since the capacitance density of the MIM capacitor is as low as 1.0 fF/m, of the layout area of the column double-sampling circuit is occupied by the capacitors.

Figure 12.

A photograph of the fabricated test chip.

The measurement setup of the test chip is shown in Figure 13. The fabricated chip, the off-chip 12-bit ADC, and an FPGA is mounted on a PCB board. The power supply voltage Vdd and pseudo-pixel voltage VR, VSH and VSL are supplied from external power sources. The control signal of the test chip is supplied by an FPGA. The digital output of the ADC was transferred to the PC via USB and then analyzed.

Figure 13.

Measurement setup of the test chip.

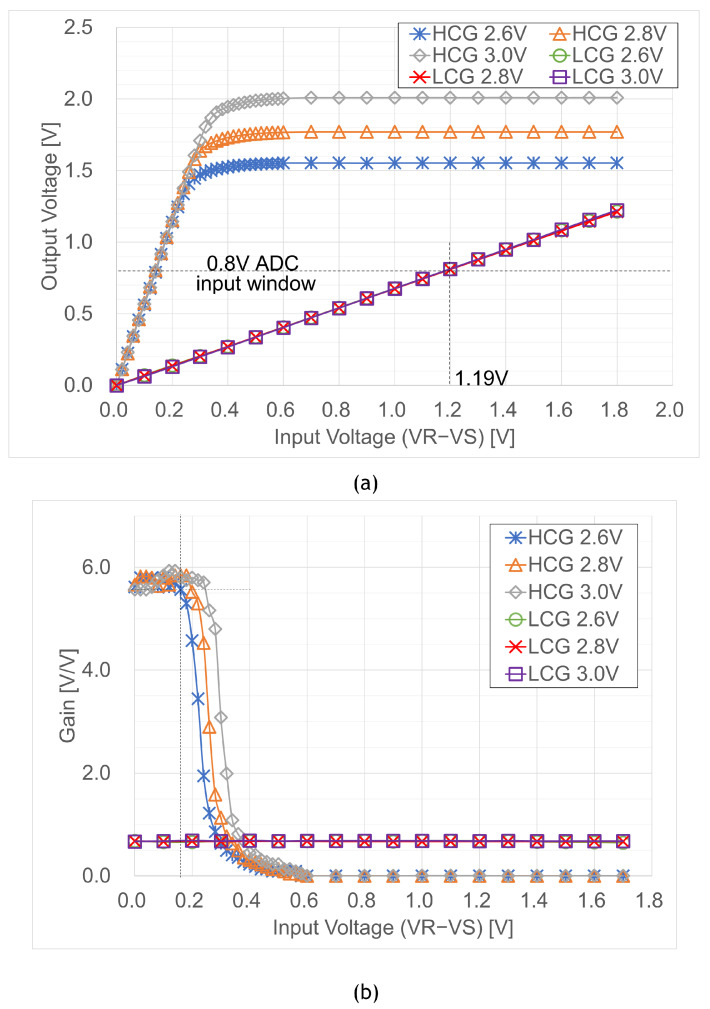

Figure 14a shows the measured input and output characteristics, where the X-axis differs between reset and signal voltages, as it is VR−VSH for HCG or VR−VSL for LCG, and the Y-axis is the output voltage swing. The power supply voltage Vdd varied from 2.6 V to 3.0 V. The HCG output signal below a 0.8 V ADC input window shows high gains for a small input signal and is saturated for a large input signal. The LCG output signal is not saturated for a large input signal, and the input window of the double-sampling circuit is 1.19 V for a 0.8 V ADC input window. Figure 14b shows the gain in the double-sampling circuit derived from the input and output characteristics. The gain of the HCG signal was for a small input signal, but lower than our target value of . The root cause is supposed to be a parasitic capacitance caused in a narrow 6.02 m pitch layout. The gain decreases as the output signal is saturated for a large input signal. The minimum confidence interval with a slope is 0.18 V under a 2.6 V power supply voltage, and the minimum output range for the HCG signal is 1.03 V; these results are wider than a 0.15 V double-sampling input window and a 0.8 V ADC input window. The gain of the LCG signal is constant over a 1.19 V double-sampling input window. The measured gain was , which is also lower than our target value of .

Figure 14.

Measurement Results of input and output characteristics of the test chip. (a) Input and output characteristics of the up/down double-sampling circuit; (b) Gain of the double-sampling circuit.

Next, the measured noise for HCG and LCG is listed in Table 3. The input-referred dark noise values at are, respectively, 130.6 at HCG and 452.9 at LCG, which are close to the noise values from the SPICE simulation results, The HCG and LCG conversion gain of the LOFIC pixel are, respectively, supposed to be 160 , 10 according to our previous work [16]. Considering the SF gain as , the expected input-referred HCG noise at FD node is converted to , while the 1.19 V LCG input window at FD node is converted to 140 ke. Thus, the dynamic range of the proposed read-out chain is given by . The specifications and performance of the proposed up/down double-sampling circuit are summarized in Table 4.

Table 3.

Measured double-sampling circuit characteristics, input-referred characteristics at FD node, and target pixel-conversion gain.

| Double-Sampling Circuit Characteristics |

Input-Referred Characteristics at FD Node |

Conversion Gain | |||

|---|---|---|---|---|---|

| Noise | Input Window |

Noise | Input window |

||

| [] | [V] | [] | [] | [] | |

| HCG | 1.0 k | 160 | |||

| LCG | 140 k | 10 | |||

Table 4.

Performance summary of the test chip.

| Process | 0.18 m 1P5M CMOS with MIM | |

| Supply voltage | 2.6 V to 3.0 V | |

| Column pitch | 6.02 m | |

| # Columns | 160 | |

| HCG | LCG | |

| Measurement noise | 130.6 V | 452.9 V |

| Input window | 0.15 V | 1.19 V |

| Power consumption (sim) | 23 W @2.8 V | |

Discussion

The test chip was fabricated with an MIM capacitor whose capacitance density is only 1.0 fF/m, and of the layout area of the column double-sampling circuit was occupied by the capacitors. In a CMOS image sensor, a depletion MOS capacitor is typically utilized. For the case of a 3.3 V MOS transistor with a 75 Åoxide thickness, the capacitance density is 4.5 fF/m. Therefore, the layout height of the column double-sampling circuit will be reduced by if the proposed double-sampling is implemented in LOFIC-CMOS image sensors.

The gain of the HCG signal was , which is lower than our target value . The root cause is supposed to be a parasitic capacitance. In the narrow 6.02 m pitch layout, a wiring to the negative input of the amplifier and a wiring from the amplifier output are laid in parallel, and the parasitic capacitance between the wires increases the feedback capacitor . According to Equation (2), the gain decreases as increases. The MIM capacitor of will be reduced considering the degradation of the gain in our future work. Furthermore, the higher-density MOS capacitor will decrease the length of the wire and will reduce the parasitic capacitor. The input-referred total noise will be reduced further by adjusting the gain to . The gain of the LCG signal was which is also lower than our target value . As a result, the voltage swing at FD node is over the limit to transfer all PD charge to the FD node. The voltage swing at FD node will be decreased to the limit by adjusting the gain to . Even though the LCG FWC on LCG will be decreased, the dynamic range will be kept, since the noise on HCG will also be decreased.

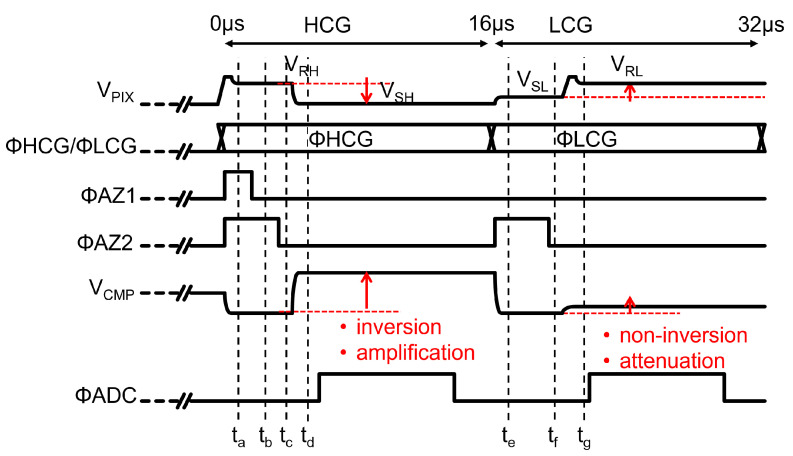

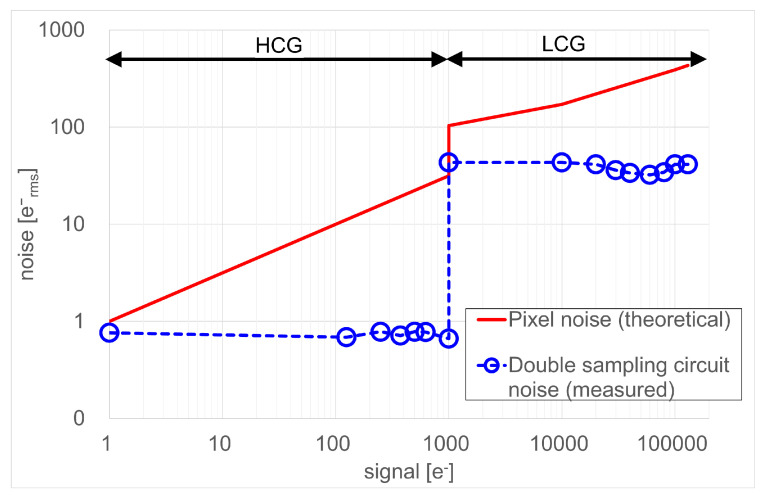

The noise of the double-sampling circuit is required to be less than the pixel noise. Figure 15 plots the measured double-sampling circuit noise and the theoretical pixel noise. In the HCG mode, the pixel noise plot is obtained by using the photon shot noise that follows for the input signal . The measured double-sampling circuit noise is lower than the pixel noise. For input signals above 1.0 k e, the HCG signal is saturated and the LCG signal is selected. In the LCG mode, the pixel noise is characterized as the photon shot noise and the FD reset noise, which is given by , where k is the Boltzmann constant, T is the absolute temperature, and C is the capacitance value of CFD and CS. The FD noise is not cancelled due to the non-correlated double-sampling operations. The double-sampling circuit noise is high in the LCG mode; however, this is still less than the pixel noise, which is at the transition point to the LCG mode.

Figure 15.

Measured double sampling circuit noise and theoretical pixel noise.

5. Conclusions

An SEHDR-CMOS image sensor is realized with LOFIC pixels, in which the LCG signal and HCG signals are combined. However, the circuit area for the LOFIC pixel is large due to the two-channel read-out chain for polarity-inverted LCG and HCG signals. In order to realize a single-channel read-out chain and to reduce the chip cost of LOFIC-CMOS image sensors, an up/down double-sampling circuit composed of a inverting amplifier and non-inverting attenuator is proposed in this paper. Even though the polarity of the LCG and HCG signals output from the LOFIC pixel is inverted, the polarity of the input signal to a following ADC is the same and a single ADC can process both the HCG and LCG signals. Moreover, the attenuator is merged with the ADC to further decrease the area of the double-sampling circuit. The area of the proposed read-out chain is roughly reduced by compared to the baseline two-channel read-out chain.

For LOFIC-CMOS image sensors, a voltage domain-level diagram is designed. The voltage gain of the double-sampling circuit in the HCG mode is selected to be to decrease the input-referred circuit noise. The gain of the double-sampling circuit at the LCG mode is selected to be to maximize FWC. In order to verify the concept of the proposed read-out chain, a test circuit is fabricated with a 0.18 m CMOS process. According to the measurement results, the LCG input window of the double-sampling circuit is 1.19 V, while the input-referred dark noise for the HCG signal is 130.6 V. Supposing the pixel conversion gain of LOFIC-pixel, the dynamic range of the proposed read-out chain can be obtained at 103 dB using the expected input-referred HCG noise and LCG input window. It is also confirmed that the measured noise of the double-sampling circuit is less than the theoretical pixel noise throughout the input range of HCG and LCG.

Author Contributions

Conceptualization, S.O.; methodology, A.O. and S.O.; validation, A.O. and H.O. (Hiroaki Ogawa); investigation, S.H. and H.O. (Hideki Owada); writing—original draft preparation, A.O.; writing—review and editing, K.M. and S.O; supervision, K.M.; funding acquisition, I.T. All authors have read and agreed to the published version of the manuscript.

Data Availability Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

Funding Statement

This research received no external funding.

Footnotes

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

References

- 1.Takayanagi I., Kuroda R. HDR CMOS Image Sensors for Automotive Applications. IEEE Trans. Electron Devices. 2022;69:2815–2823. doi: 10.1109/TED.2022.3164370. [DOI] [Google Scholar]

- 2.Takayanagi I. Ph.D. Thesis. Tohoku University; Sendai, Japan: 2020. A Study on Intra-Scene Single-Exposure High-Dynamic Range CMOS Image Sensor Technologies. [DOI] [Google Scholar]

- 3.Schanz M., Nitta C., Bussmann A., Hosticka B., Wertheimer R. A high-dynamic-range CMOS image sensor for automotive applications. IEEE J. Solid-State Circuits. 2000;35:932–938. doi: 10.1109/4.848200. [DOI] [Google Scholar]

- 4.Hertel D. Extended use of incremental signal-to-noise ratio as reliability criterion for multiple-slope wide-dynamic-range image capture. J. Electron. Imaging. 2010;19:011007. doi: 10.1117/1.3267100. [DOI] [Google Scholar]

- 5.Chamberlain S., Lee J. A novel wide dynamic range silicon photodetector and linear imaging array. IEEE J. Solid-State Circuits. 1984;19:41–48. doi: 10.1109/JSSC.1984.1052084. [DOI] [Google Scholar]

- 6.Scheffer D., Dierickx B., Meynants G. Random addressable 2048/spl times/2048 active pixel image sensor. IEEE Trans. Electron Devices. 1997;44:1716–1720. doi: 10.1109/16.628827. [DOI] [Google Scholar]

- 7.de Moraes Cruz C.A., de Lima Monteiro D.W., Souza A.K.P., da Silva L.L.F., de Sousa D.R., de Oliveira E.G. Voltage Mode FPN Calibration in the Logarithmic CMOS Imager. IEEE Trans. Electron Devices. 2015;62:2528–2534. doi: 10.1109/TED.2015.2446992. [DOI] [Google Scholar]

- 8.Decker S., McGrath D., Brehmer K., Sodini C. A 256/spl times/256 CMOS imaging array with wide dynamic range pixels and column-parallel digital output. IEEE J. Solid-State Circuits. 1998;33:2081–2091. doi: 10.1109/4.735551. [DOI] [Google Scholar]

- 9.Komobuchi H. 1/4 inch NTSC Format Hyper-D Range IL-CCD; Proceedings of the 1995 IEEE Workshop on CCDs and Advanced Image Sensors; Dana Point, CA, USA. 20–22 April 1995. [Google Scholar]

- 10.Takayanagi I., Fukunaga Y., Yoshida T., Nakamura J. A Four-Transistor Capacitive Feedback Reset Active Pixel and Its Reset Noise Reduction Capability; Proceedings of the International Image Sensor Workshop; Lake Tahoe, NV, USA. 7–9 June 2001; pp. 118–121. [Google Scholar]

- 11.Yadid-Pecht O., Fossum E. Wide intrascene dynamic range CMOS APS using dual sampling. IEEE Trans. Electron Devices. 1997;44:1721–1723. doi: 10.1109/16.628828. [DOI] [Google Scholar]

- 12.Mase M., Kawahito S., Sasaki M., Wakamori Y., Furuta M. A wide dynamic range CMOS image sensor with multiple exposure-time signal outputs and 12-bit column-parallel cyclic A/D converters. IEEE J. Solid-State Circuits. 2005;40:2787–2795. doi: 10.1109/JSSC.2005.858477. [DOI] [Google Scholar]

- 13.Takayanagi I., Yoshimura N., Mori K., Matsuo S., Tanaka S., Abe H., Yasuda N., Ishikawa K., Okura S., Ohsawa S., et al. An Over 90 dB Intra-Scene Single-Exposure Dynamic Range CMOS Image Sensor Using a 3.0 μm Triple-Gain Pixel Fabricated in a Standard BSI Process. Sensors. 2018;18:203. doi: 10.3390/s18010203. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 14.Miyauchi K., Mori K., Isozaki T., Sawai Y., Yasuda N., Chien H.C., Fu K.W.C., Takayanagi I., Nakamura J. 4.0 μm Stacked Voltage Mode Global Shutter Pixels with Single Exposure High Dynamic Range and Phase Detection Auto Focus Capability. ITE Trans. Media Technol. Appl. 2022;10:234–242. doi: 10.3169/mta.10.234. [DOI] [Google Scholar]

- 15.Velichko S., Jasinski D., Guidash M., Tekleab D., Innocent M., Perkins A., Amanullah S., Suryadevara M., Silsby C., Beck J. Automotive 3 μm HDR Image Sensor with LFM and Distance Functionality. IEEE Trans. Electron Devices. 2022;69:2951–2956. doi: 10.1109/TED.2022.3165517. [DOI] [Google Scholar]

- 16.Takayanagi I., Miyauchi K., Okura S., Mori K., Nakamura J., Sugawa S. A 120-ke- Full-Well Capacity 160 μV/e- Conversion Gain 2.8 μm Backside-Illuminated Pixel with a Lateral Overflow Integration Capacitor. Sensors. 2019;19:5572. doi: 10.3390/s19245572. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 17.Sugawa S., Akahane N., Adachi S., Mori K., Ishiuchi T., Mizobuchi K. A 100 dB dynamic range CMOS image sensor using a lateral overflow integration capacitor; Proceedings of the ISSCC, 2005 IEEE International Digest of Technical Papers, Solid-State Circuits Conference; San Francisco, CA, USA. 10 February 2005; New York, NY, USA: IEEE; 2005. pp. 352–603. [Google Scholar]

- 18.Akahane N., Sugawa S., Adachi S., Mori K., Ishiuchi T., Mizobuchi K. A sensitivity and linearity improvement of a 100-dB dynamic range CMOS image sensor using a lateral overflow integration capacitor. IEEE J. Solid-State Circuits. 2006;41:851–858. doi: 10.1109/JSSC.2006.870753. [DOI] [Google Scholar]

- 19.Sakai S., Tashiro Y., Kawada S., Kuroda R., Akahane N., Mizobuchi K., Sugawa S. Pixel scaling in complementary metal oxide silicon image sensor with lateral overflow integration capacitor. Jpn. J. Appl. Phys. 2010;49:04DE03. doi: 10.1143/JJAP.49.04DE03. [DOI] [Google Scholar]

- 20.Sugo H., Wakashima S., Kuroda R., Yamashita Y., Sumi H., Wang T.J., Chou P.S., Hsu M.C., Sugawa S. A dead-time free global shutter CMOS image sensor with in-pixel LOFIC and ADC using pixel-wis e connections; Proceedings of the 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits); Honolulu, HI, USA. 15–17 June 2016; New York, NY, USA: IEEE; 2016. pp. 1–2. [Google Scholar]

- 21.Sakano Y., Sakai S., Tashiro Y., Kato Y., Akiyama K., Honda K., Sato M., Sakakibara M., Taura T., Azami K., et al. 224-ke saturation signal global shutter CMOS image sensor with in-pixel pinned storage and lateral overflow integration capacitor; Proceedings of the 2017 Symposium on VLSI Circuits; Kyoto, Japan. 5–8 June 2017; New York, NY, USA: IEEE; 2017. pp. C250–C251. [Google Scholar]

- 22.Fujihara Y., Murata M., Nakayama S., Kuroda R., Sugawa S. An Over 120 dB Single Exposure Wide Dynamic Range CMOS Image Sensor With Two-Stage Lateral Overflow Integration Capacitor. IEEE Trans. Electron Devices. 2021;68:152–157. doi: 10.1109/TED.2020.3038621. [DOI] [Google Scholar]

- 23.Shike H., Kuroda R., Kobayashi R., Murata M., Fujihara Y., Suzuki M., Harada S., Shibaguchi T., Kuriyama N., Hatsui T., et al. A Global Shutter Wide Dynamic Range Soft X-ray CMOS Image Sensor With Backside- Illuminated Pinned Photodiode, Two-Stage Lateral Overflow Integration Capacitor, and Voltage Domain Memory Bank. IEEE Trans. Electron Devices. 2021;68:2056–2063. doi: 10.1109/TED.2021.3062576. [DOI] [Google Scholar]

- 24.Takahashi H., Noda T., Matsuda T., Watanabe T., Shinohara M., Endo T., Takimoto S., Mishima R., Nishimura S., Sakurai K., et al. A 1/2.7-in 2.96 MPixel CMOS Image Sensor with Double CDS Architecture for Full High-Definition Camcorders. IEEE J. Solid-State Circuits. 2007;42:2960–2967. doi: 10.1109/JSSC.2007.908719. [DOI] [Google Scholar]

- 25.Tsai T.H., Sun T.W., Cheng R.W., Chang C.C. A Low-Power Sensing System of VEGF Concentration with Noise Reduction Using Sub-Sampling Technique for Cancer Diagnosis. IEEE Sens. J. 2023 doi: 10.1109/JSEN.2023.3263869. [DOI] [Google Scholar]

- 26.Hynecek J., Nishiwaki T. Excess noise and other important characteristics of low light level imaging using charge multiplying CCDs. IEEE Trans. Electron Devices. 2003;50:239–245. doi: 10.1109/TED.2002.806962. [DOI] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Data Availability Statement

Not applicable.