Abstract

Flip Chip Ball Grid Array (FCBGA) packages, together with many other heterogeneous integration packages, are widely used in high I/O (Input/Output) density and high-performance computing applications. The thermal dissipation efficiency of such packages is often improved through the use of an external heat sink. However, the heat sink increases the solder joint inelastic strain energy density, and thus reduces the board-level thermal cycling test reliability. The present study constructs a three-dimensional (3D) numerical model to investigate the solder joint reliability of a lidless on-board FCBGA package with heat sink effects under thermal cycling testing, in accordance with JEDEC standard test condition G (a thermal range of −40 to 125 °C and a dwell/ramp time of 15/15 min). The validity of the numerical model is confirmed by comparing the predicted warpage of the FCBGA package with the experimental measurements obtained using a shadow moiré system. The effects of the heat sink and loading distance on the solder joint reliability performance are then examined. It is shown that the addition of the heat sink and a longer loading distance increase the solder ball creep strain energy density (CSED) and degrade the package reliability performance accordingly.

Keywords: FCBGA, solder joint, finite element method, mechanical loading, reliability

1. Introduction

Over the past few years, demand has risen for electronic devices with increasing Input/Output (I/O) density and enhanced computational capabilities to support high-performance computing (HPC) applications such as AI (Artificial Intelligence) and machine learning. Flip Chip Ball Grid Array (FCBGA) packaging, 2.5D/3D heterogeneous integration packages, and Fan-Out Chip on Substrate (FOCoS) are the mainstay of such devices [1,2,3,4]. FCBGA (see Figure 1a) is particularly common in telecom, workstation, and computer applications due to its superior bandwidth and electrical performance. However, as the speed and I/O count of high-power packages increase, thermal dissipation control and management poses a critical concern [5,6,7]. Most of the heat generated by the chip is transferred to the printed circuit board (PCB) [8]. FCBGAs are commonly attached to a metal cavity heat spreader through a thermal interface material (TIM) to extend the heat conduction area of the die and further improve the heat dissipation (see Figure 1b). However, the resulting high-performance FCBGA (HFCBGA) assembly suffers the problem of an increased junction-to-case thermal resistance (Rjc) [9], which increases the junction temperature on the die.

Figure 1.

Schematic illustrations of: (a) FCBGA package and (b) HFCBGA package.

The heat dissipation performance of HFCBGA packages can be improved further yet through their integration with an external heat sink or an air fan (see Figure 2) to force the heat flow upward and convection cooling use to remove excess heat. However, the additional load imposed by the heat sink and fan increases the risk of solder joint cracking at the point where the package is mounted on the PCB (Figure 3 shows the occurrence of solder joint fracture in the HFCBGA package mounted on the PCB with a heatsink) [10]. To improve the packaging yield rate, it is therefore necessary to properly understand the board-level fatigue reliability of advanced high-power consumption packages under coupled mechanical load and thermal cycling conditions.

Figure 2.

Schematic illustration showing HFCBGA with heat sink and air-fan assembly.

Figure 3.

Cross-sectional images of solder joint crack.

The problem of minimizing the junction temperature and enhancing the heat dissipation capacity of advanced packages has attracted significant attention in the literature [11,12,13]. Han et al. [14] conducted computational fluid dynamics (CFD) simulations to investigate the heat dissipation capability of a 30 × 25 mm2 2.5D package with various heat sink types and found that the package with the optimal heat sink structure was capable of dissipating more than 100 W of power. Rajan et al. [15] studied the thermal management efficiency of high-power CPUs fitted with micro pin fins on the backside of the silicon and a microfluidic cooling system. The results showed that the thermal resistance of the chip was reduced by around 44% compared to that of a conventional cold-plate cooling system. Lin et al. [16] developed a two-phase immersion cooling system to enhance the high-power dissipation of a chip on wafer on substrate (CoWoS) HPC package and showed that the thermal design power reached as much as 900, W. Su et al. [17] utilized a three-dimensional (3D) finite-element model (FEM) to investigate the thermal resistance of a fan-out (FO) package with various graphite terminal interface materials (TIMs). The optimal heat dissipation performance was obtained using a TIM fabricated of directional graphite.

The form factors of advanced packaging are trending towards ever larger sizes in order to meet the requirements for higher IO densities and power consumption. Thermal cycle on board (TCoB) tests have emerged as an important tool for evaluating the solder joint reliability in order to improve the packaging yield rate and physical integrity of the final assembly. Several studies have employed FE models to examine the TCoB reliability of solder interconnects [18,19,20]. Shao et al. [21] used a three-dimensional (3D) digital image correlation (DIC) technique to measure the warpage of a 55 × 55 mm2 2.5D lidded package, and then constructed a verified FE model based on the DIC measurements to analyze the board-level thermal reliability for various geometry factors and material properties. The results revealed that the solder joint reliability was determined mainly by the thickness of the lid, PCB, and substrate, with a thinner thickness being preferred in each case. Lau et al. [22] conducted a thorough experimental and numerical investigation to assess the TCoB solder joint performance of fan-out panel level packaging (FOPLP) with a redistribution layer (RDL)-first and die face-down configuration. It was found that cracking of the solder joint occurred mainly at the interface between the RDL layer and the bulk solder. Ahmed et al. [23] performed nonlinear FE analyses using a global and sub-model modeling technique to analyze and assess the effects of heat sink application and the PCB laminate material properties on the solder joint reliability of 2.5D lidless structures. The simulation results showed that the solder joint reliability increased without the heat sink, with a thinner PCB thickness, and lower coefficient of temperature expansion (CTE) of the PCB laminate. Ji and Chai [24] combined a 3D slice FE model and a robust design-of-experiment (DOE) approach to examine the TCoB solder joint reliability of a 45 × 51 mm2 high density fan-out wafer-level package (FOWLP). The authors additionally employed a design technology co-optimization method (DTCO) to identify the dominant factors affecting the fatigue life of the solder joints under TCoB testing. Yang et al. [25] used a validated 3D FE model to analyze the solder joint plastic work energy of a lidless 2.5D package with a heat sink in board-level thermal cycling tests. The results showed that the solder fatigue life increased as the pre-load force of the bolts and CTE mismatch between the substrate and PCB reduced.

As described above, a larger package size and lidless structure are commonly used to improve the heat dissipation performance of high-power consumption package assemblies. Moreover, heat sink devices may also be added to the assembly to further cool the package. However, with the larger package size and external load imposed by the heat sink, the TCoB solder joint reliability of the package is a critical issue. Consequently, the present study constructs a 3D numerical model of a lidless FCBGA package with a heat sink to examine the solder joint reliability of the assembly under thermal cycling tests (TCT). The validity of the FE model is confirmed by comparing the simulation results for the warpage of the FCBGA package substrate with the experimental measurements obtained using a shadow moiré system. Finally, the validated model is used to examine the effects of various external load conditions on the mechanical characteristics and reliability performance of the solder joints. The simulation results provide useful guidance for evaluating the solder joint reliability of FCBGA packages with heat sink assemblies under coupled mechanical compression and thermal cycling test conditions.

2. Board-Level Thermal Cycling Tests

2.1. Test Vehicle Structure

In the present study, we considered and fabricated a lidless FCBGA assembly. As shown in Table 1, the package had an overall size of 40 × 40 mm2 and a build-up layer substrate thickness of 1.2 mm. The die had dimensions of 15.5 × 15.5 × 0.78 mm3. Finally, the underfill had a thickness of 25 μm.

Table 1.

Test Vehicle information.

| Package size (mm) | 40 × 40 |

| Die size (mm) | 15.5 × 15.5 × 0.78 |

| Substrate thickness (mm) | 1.2 |

| Underfill thickness (μm) | 25 |

2.2. Thermal Cycling Tests

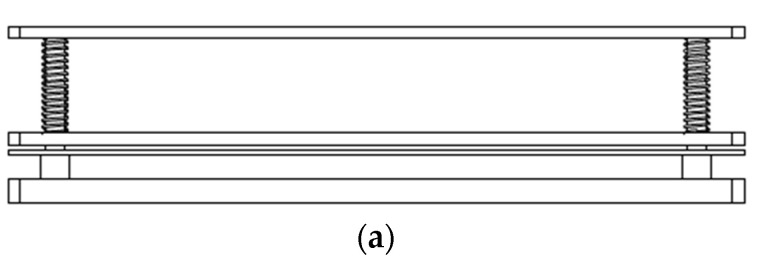

The test vehicle was mounted on a 300 × 160 × 2.35 mm3 PCB test board made of FR-4 with eight layers and was subjected to board-level TCT testing in accordance with the JEDEC (Joint Electron Device Engineering Council) and IPC (Institute of Printed Circuits) standards [26,27]. The test board footprint and layout are shown in Figure 4a. The die was attached to the test board using an array of Sn-Ag-Cu solder joints (Figure 4b), with a diameter of 0.6 mm and a standoff of 0.55 mm. The opening size on both the package side and the test board side was set to 0.475 mm. Additionally, the pitch between adjacent solder joints in the array was set as 1.0 mm. A compressive fixture (see Figure 5a) was designed to examine the compressive loading effect of the heat sink on the die assembly. As shown in Figure 5b, the fixture was used to apply a force of 40 N to the FCBGA package to mimic the loading effect of the heat sink. A gel type thermal interface material was applied to the top surface of the chip with a maximum thickness of 0.1 mm after the heat sink (i.e., compressive metal plate) was attached to the base plate via four corner screws. In performing the thermal cycling tests, the assembly was placed in a thermal cycling chamber capable of applying a temperature range from −70 °C to 180 °C with a maximum ramp rate of 15 °C per minute.

Figure 4.

(a) Test board size and layout (Unit: mm) and (b) Lidless FCBGA package mounted on board.

Figure 5.

Schematic illustrations of (a) compressive fixture and (b) mechanical loading tests.

The JEDEC TCT test conditions are specified mainly in terms of the temperature range and the heating/cooling rate. In accordance with JESD22-A104E Test Condition G [27], the TCT in the present study was performed using a temperature range from −40 to 125 °C with a dwell/ramp time of 15/15 min and a cycling rate of one cycle every 1 h (see Figure 6). A daisy chain circuit design was implemented to interconnect each solder joint in the FCBGA assembly, enabling the measurement of electrical resistance in the sample. The resistance measurements were captured by an event detector data acquisition system and monitored in real time to assess the change in resistance of the test sample over the course of the TCT.

Figure 6.

Thermal cycling temperature profile.

2.3. Thermal Cycling Test Results

Table 2 shows the TCT reliability results obtained for the packages with and without the heat sink, respectively. For all three samples, the number of cycles to first failure is significantly reduced when the heat sink is added to the assembly. In other words, the additional loading force applied by the heat sink has a significant adverse effect on the reliability of the package. Figure 7 presents cross-sectional optical images of the die and substrate edge solder joints on the test vehicle without a heat sink following TCT. As shown, the initiation and failure of cracks predominantly transpired in the upper region of the solder ball near the substrate side, primarily affecting the joints situated at the corners of the BGA. A similar solder joint failure location was also observed for the test vehicles with a heat sink. Figure 8 compares the fractured solder joints of the test assemblies without a heat sink (Figure 8a) and with a heat sink (Figure 8b), respectively. It is evident that the mechanical compression force imposed on the solder joints through the additional weight of the heat sink results in a more severe cracking of the solder balls in the corners of the array as the FCGBA assembly undergoes thermal cycling.

Table 2.

TCoB test matrix and results.

| Sample | Cycles to First Failure | |

|---|---|---|

| W/O Heat Sink | W/Heat Sink | |

| 1 | 3652 | 2694 |

| 2 | 3689 | 2496 |

| 3 | 3865 | 2587 |

Figure 7.

Cross-sectional views of die and package edge solder joints (w/o heat sink).

Figure 8.

Cross-sectional views of fractured corner solder joints: (a) w/o and (b) w/heat sink.

3. Coupled Mechanical Compression and Thermal Cycling Simulation

3.1. Finite-Element Modeling

Figure 9 illustrates the lidless FCBGA with heat sink assembly considered in the present simulations. As shown in Table 1, the FCBGA model consisted of an eight-layer build-up organic substrate with a thickness of 1.2 mm and a single die with a footprint of 40 × 40 mm2 and thickness of 780 μm. The package was mounted on the test board using 96 Sn–4 Ag–0.5 Cu solder alloy joints. The TIM between the die and the heat sink had a thickness of 0.1 mm, while the heat sink had a size of 300 × 160 × 5 mm3.

Figure 9.

Schematic illustration of lidless FCBGA package with heat sink on test board.

Simulations were performed to investigate the warpage of the FCBGA and the accumulated inelastic work in the critical solder ball joints during TCT, with various heat sink arrangements. Due to the bi-axial symmetry of the architecture, the simulations considered only one quarter of the 3D board-level model for computational simplicity (Figure 10a). As shown in Figure 10b, the sub-model of the global-local model consisted of a single pitch solder ball. To simplify the analysis, the solder balls in the global model were meshed using simple cubic elements, and the solder bump layers were considered to be homogeneous layers. In accordance with the experimental observations, the sub-model of the solder ball used to examine the fatigue behavior of the solder joints was assigned to the upper-right corner of the global model beneath the substrate, which is generally regarded as the most critical point in the entire solder ball layout.

Figure 10.

3D TCoB analysis model: (a) global-level model and (b) sub-model.

The FE mesh consisted of a total of 389,702 elements of various types (including hexahedral and tetrahedron elements ANSYS solid186 3D modeling of solid structures). The global-level model and sub-model had average FE mesh sizes of 0.2 mm and 0.06 mm, respectively. Due to the bi-axial symmetry of the assembly, the simulations applied no-displacement boundary conditions in the X- and Y-directions along the YZ and ZX symmetry planes, respectively (see Figure 11a). Furthermore, to prevent any rigid body motion, the center point of the lower surface of the PCB was constrained in the z-direction.

Figure 11.

(a) Boundary conditions and (b) compressive loadng condition.

3.2. Material Properties

The thermomechanical properties of the different components of the model are summarized in Table 3. The table includes Young’s modulus (E), coefficient of thermal expansion (CTE), glass transition temperature (Tg), and Poisson’s ratio (ν). The Young’s modulus of the test board was calculated as C0 + C1 * T, where T is the temperature in Kelvin [28]. As shown in Figure 12, the elastic moduli of the underfill and substrate were temperature dependent and were determined via dynamic mechanical analysis (DMA). As mentioned above, the solder bumps and underfill were considered to be homogeneous materials with approximately equivalent thermomechanical properties based on the relative volume fraction of the solder bump and underfill materials [29,30].

Table 3.

Thermomechanical properties of Package Components.

| Component | E (GPa) | CTE (ppm/°C) | Tg (°C) | ν |

|---|---|---|---|---|

| Die | 131 | 2.8 | - | 0.30 |

| Solder mask | 2.7 | 50/140 | 100 | 0.30 |

| Underfill | Figure 12 | 32/110 | 70 | 0.30 |

| Substrate | Figure 12 | X/Y: 23.46 Z: 52.65/156.4 |

156 | 0.30 |

| Test board | X/Y: C0 = 27.924, C1 = −0.0372 Z: C0 = 12.203, C1 = −0.016 |

X/Y: 16.5 Z: 67.2 |

- | 0.39 |

| Solder Ball | 48.5@-55 °C 33@210 °C |

20 | - | 0.35 |

| TIM | 0.0083 | 14 | - | 0.35 |

| Heat spreader | 68 | 24 | - | 0.344 |

Figure 12.

Temperature-dependent Young’s modulus of underfill and substrate.

Throughout the duration of the TCoB tests, the solder balls experienced a consistently high homologous temperature. Hence, the deformation kinetics of the balls were dominated by a steady-state creep behavior [31,32] described by the following generalized Garofalo-Arrhenius constitutive equation [33,34]:

| (1) |

In the equation, and represent the steady-state creep strain rate and stress, respectively. Moreover, C1–C4 denote constants with their respective values provided in Table 4.

Table 4.

Constants of Garofalo-Arrhenius Creep model for solder balls [34].

| Constant | Unit | Value |

|---|---|---|

| C1 | S−1 | 277,984 |

| C2 | MPa−1 | 0.02447 |

| C3 | n | 6.41 |

| C4 | K | 6489.7 |

3.3. Verification of Simulation Model

The validity of the simulation model was evaluated by comparing the numerical results for the warpage of the lower surface of the substrate (see Figure 13), with the warpage measurements obtained using an Akrometrix shadow moiré non-contact optical measurement system with an accuracy of 1 μm in the vertical displacement direction.

Figure 13.

Warpage measurements of FCBGA package.

Figure 14a,b shows the experimental and simulation results for the FCBGA warpage contours, respectively. In the modeling, we consider that the temperature decreases from the stress-free temperature at 150 °C to room temperature. That is immediately after cure of the underfill. Both result sets indicate that the package exhibits concave warpage when at room temperature. Based on the experimental findings, the highest warpage is observed at the substrate center, reaching approximately 122 μm (4.8 mils) in magnitude. The simulation results predict a maximum warpage of 128 μm (5.04 mils). The two measurements deviate by less than 5%. Thus, the basic validity of the FE model is confirmed.

Figure 14.

Warpage contour distributions of lower surface of substrate in lidless FCBGA package at 30 °C: (a) experimental results and (b) simulation results.

3.4. Solder Joint Reliability Analysis

The coupled mechanical compression and TCT reliability of the board-level FCBGA was simulated using ANSYS FE code under the thermal loading conditions specified by JEDEC standard G. To simulate the mechanical compression effect of the heat sink in the experimental tests (see Figure 11b), a loading force of 40 N was applied to the heat sink at a distance of 45 mm from the center point in the x-axis direction and 50 mm in the y-axis direction. During the simulations, it was assumed that the temperature would decrease from a stress-free temperature of 217 °C to room temperature after the solder joint reflow process.

It was shown in [4] that the creep strain energy density (CSED) provides a reasonable index for examining the risk of solder joint cracking. Figure 15a shows the simulation results for the CSED distribution of the FCBGA package at the end of the thermal cycling test. The results confirm that the maximum CSED in the FE model occurs in the solder joint near the right-hand corner of the package. The results of the sub-model simulation are depicted in Figure 15b. It is evident that the highest CSED (creep strain energy density) is concentrated in the upper region of the solder ball. The simulation results are thus consistent with the experimental observations in Figure 7 and Figure 8. Thus, the validity of the FE model is further confirmed.

Figure 15.

CSED distribution contours at 125 °C: (a) full package and (b) outermost solder ball.

The stress/strain data obtained from the FE simulations are affected by the mesh density and element size effects in the FE model. Therefore, an element volumetric averaging technique was applied to reduce the solution sensitivity with regard to the mesh density [32], i.e.,

| (2) |

where is the total CSED accumulated per cycle in the region, and V is the volume of the region that covers an area of 1 mm from the upper surface of the solder ball. The fatigue resistance of the solder joint interconnections was then evaluated by calculating the average CSED increment between cycle-1 and cycle-2 in accordance with:

| (3) |

3.5. Effects of Heat Sink

Figure 16 shows the simulation results obtained for the average SED under three different heat sink conditions: (1) without a heat sink; (2) with a heat sink and a loading force at 45 mm from the center point in the x-direction; and (3) with a heat sink and a loading force at 90 mm from the center point in the x-direction. The corresponding average SED values are 0.23 MJ/m3, 1.75 MJ/m3, and 1.98 MJ/m3, respectively. In other words, the SED increases when adding a heat sink to the FCGBA assembly due to the additional mechanical loading force applied to the die. Moreover, the average SED also increases with an increased loading distance from the center of the heat sink due to the longer loading distance resulting in a greater bending moment.

Figure 16.

Average CSED in solder joints given different heat sink conditions.

4. Conclusions

This study has examined the thermal cycling solder interconnection reliability of a board-level lidless FCBGA assembly with a heat sink under JEDEC thermal cycle testing (TCT). A 3D FE computational model with an inelastic creep behavior of the solder joints has been used to evaluate the solder ball TCT reliability of the package with and without a heat sink, respectively. The validity of the FE model has been confirmed by comparing the simulation results for the out-of-plane deformation of the FCBGA package substrate with the experimental measurements. The validated model has been used to investigate the CSED of the solder joints under various heat sink and loading force conditions. The experimental and simulation results support the following conclusions:

The board-level TCT results have shown that fracture occurs at the outermost corner solder ball joint in the BGA irrespective of whether or not a heat sink is attached to the package. However, the severity of the solder ball cracking increases under the additional load imposed by the heat sink. Consequently, the number of cycles to first failure is significantly reduced.

The CSED within the solder balls at the outermost corners of the BGA increases with both the addition of the heat sink to the FCBGA assembly and an increasing distance of the loading force position from the center of the heat sink. A greater loading distance increases the compressive force acting on the BGA as the result of the bending moment, and is thus detrimental to the TCT reliability of the FCBGA assembly.

Overall, the present results show that an external heat sink and a greater loading distance have a significant adverse effect on the solder joint reliability of FCBGA packages. However, the addition of a heat sink is often necessary to improve the heat dissipation performance of high-power advanced packages. Consequently, further studies on the impact of the heat sink on the reliability of high-power packages are required to investigate such issues as the geometry and assembly loading force.

Acknowledgments

This collaborative research is part of the Corporate Research and Development at Advanced Semiconductor Engineering Inc. The authors would like to thank the Stress-Thermal Analysis Lab at ASE Inc. for providing the package samples and excellent support and thank the Ministry of Science and Technology, Taiwan (under Grant MOST-111-2221-E-150-003) for supporting this research.

Author Contributions

Conceptualization, M.-K.S. and C.L.; methodology, M.-K.S. and C.L.; software, Y.-H.L.; validation, Y.-H.L.; resources, C.L. and C.P.H.; writing—original draft preparation, M.-K.S.; writing—review and editing, M.-K.S.; supervision, C.P.H. All authors have read and agreed to the published version of the manuscript.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

The data presented in this study are available on request from the corresponding author.

Conflicts of Interest

The authors declare no conflict of interest.

Funding Statement

This work was supported by the Ministry of Science and Technology, Taiwan, under MOST-111-2221-E-150-003.

Footnotes

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

References

- 1.Lau J.H. TSV Manufacturing Yield and Hidden Costs for 3D IC Integration; Proceedings of the Electronic Components and Technology Conference; Las Vegas, NV, USA. 1–4 June 2010; pp. 1031–1042. [Google Scholar]

- 2.Lee C.-C., Hung C., Cheung C., Yang P.-F., Kao C.-L., Chen D.-L., Shih M.-K., Chien C.-L.C., Hsiao Y.-H., Chen L.-C., et al. An Overview of the Development of a GPU with integrated HBM on Silicon Interposer; Proceedings of the Electronic Components and Technology Conference; Las Vegas, NV, USA. 31 May–3 June 2016; pp. 1439–1444. [Google Scholar]

- 3.Wu Z.-J., Carey C., Donavan S., Hunt D., Justison P., Anemikos T., Cincotta J., Gagnon H., Chacon O., Martel R., et al. Chip-Package Interaction Challenges for Large Die Applications; Proceedings of the Electronic Components and Technology Conference; San Diego, CA, USA. 29 May–1 June 2018; pp. 656–662. [Google Scholar]

- 4.Shih M.-K., Lai W., Liao T., Chen K., Chen D.-L., Hung C.P. Thermal and Mechanical Characterization of 2.5-D and Fan-Out Chip on Substrate Chip-First and Chip-Last Packages. IEEE Trans. Compon. Packag. Manuf. Technol. 2022;12:297–305. doi: 10.1109/TCPMT.2022.3145377. [DOI] [Google Scholar]

- 5.Wang T.H., Chen H.-Y., Lee C.-C., Lai Y.-S. High-powered thermal gel degradation evaluation on board-level HFCBGA subjected to reliability tests. Microelectron. Eng. 2011;88:3101–3107. doi: 10.1016/j.mee.2011.06.007. [DOI] [Google Scholar]

- 6.Zhang H.Y., Zhang X.W., Lau B.L., Lim S., Ding L., Yu M.B., Lee Y.J. Thermal characterization and simulation study of 2.5D packages with multi-chip module on through silicon interposer; Proceedings of the Electronics Packaging Technology Conference; Las Vegas, NV, USA. 28–31 May 2013; pp. 363–368. [Google Scholar]

- 7.Morgan A., Choobineh L., Fresne D., Hopkins D.C. Numerical and experimental determination of temperature distribution in 3D stacked power devices; Proceedings of the International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems; San Francisco, CA, USA. 29 August–1 September 2017; pp. 363–368. [Google Scholar]

- 8.Silveira J.V.T., Li Z., Yang B., Yasui R., Shinoda T., Fushinobu K. Analysis of heat transfer from a heat dissipating device on a substrate; Proceedings of the InterSociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems; Las Vegas, NV, USA. 28–31 May 2019; pp. 446–450. [Google Scholar]

- 9.Hu I., Tsai J.-C., Cheng F., Yen S.-F., Shih M.-K., Tarng D., Pai B., Hung C. High Power Large Size HFCBGA Thermal Characterization; Proceedings of the Electronics Packaging Technology Conference; Singapore. 4–6 December 2019; pp. 467–471. [Google Scholar]

- 10.Nayini M., Horn T., Patel J., Burrell L. Coupled thermal-mechanical simulation methodology to estimate BGA reliability of 2.5D Packages; Proceedings of the Electronic Components and Technology Conference; Orlando, FL, USA. 3–30 June 2020; pp. 1653–1658. [Google Scholar]

- 11.Loeblein M., Tsang S.H., Han Y., Zhang X., Teo E.H.T. Heat Dissipation Enhancement of 2.5D Package with 3D Graphene & 3D Boron Nitride Networks as Thermal Interface Material (TIM); Proceedings of the Electronic Components and Technology Conference; Las Vegas, NV, USA. 31 May–3 June 2016; pp. 707–713. [Google Scholar]

- 12.Huang Y.L., Chung C.K., Lin C., Yu K.H., Lin R.J., Hong W. Highly Thermal Dissipation for Large HPC Package Using Liquid Metal Materials; Proceedings of the Electronic Components and Technology Conference; Virtual. 1 June–4 July 2021; pp. 1102–1108. [Google Scholar]

- 13.Chen H., Lim T.G., Tang G. Thermal Challenges and Design Considerations in Heterogeneous Integrated Through-Silicon-interposer Platform for III-V HEMT Flip Chip; Proceedings of the Electronic Components and Technology Conference; San Diego, CA, USA. 31 May–3 June 2022; pp. 1030–1035. [Google Scholar]

- 14.Han Y., Li H., Lim S.S.H., Kawano M. Thermal Analysis of 2.5D Package in High Power Application; Proceedings of the Electronics Packaging Technology Conference; Singapore. 4–6 December 2019; pp. 402–405. [Google Scholar]

- 15.Rajan S.K., Ramakrishnan B., Alissa H., Kim W., Belady C., Bakir M.S. Integrated Silicon Microfluidic Cooling of a High-Power Overclocked CPU for Efficient Thermal Management. IEEE Access. 2022;10:59259–59269. doi: 10.1109/ACCESS.2022.3179387. [DOI] [Google Scholar]

- 16.Lin P.-Y., Kuo S.-L., Yan K., Chen W.-M., Liao M.D.-D. Advanced Thermal Integration for HPC Packages with Two-Phase Immersion Cooling; Proceedings of the Electronic Components and Technology Conference; San Diego, CA, USA. 31 May–3 June 2022; pp. 566–573. [Google Scholar]

- 17.Su P.-J., Lin D., Lin S., Xu X.-Z., Lin R.J., Hung L.-Y., Wang Y.-P. High Thermal Graphite TIM Solution Applied to Fan-Out Platform; Proceedings of the Electronic Components and Technology Conference; San Diego, CA, USA. 31 May–3 June 2022; pp. 1224–1227. [Google Scholar]

- 18.Mandal R., Chong C.T. Mechanical modeling study for fan-out wafer level package parameters to enhance BGA TCoB life; Proceedings of the Electronics Packaging Technology Conference; Singapore. 7–9 December 2021; pp. 589–593. [Google Scholar]

- 19.Yang H.-C., Chiu T.-C. Numerical implementation of a unified viscoplastic model for considering solder joint response under board-level temperature cycling. Comput. Model. Eng. Sci. 2021;128:639–668. doi: 10.32604/cmes.2021.016159. [DOI] [Google Scholar]

- 20.Afripin A., Hauck T. Influence of Ball Grid Array Design Parameters on Solder Joint Reliability; Proceedings of the International Electronics Manufacturing Technology Conference; Kuala Lumpur, Malaysia. 19–21 October 2022. [Google Scholar]

- 21.Shao S., Niu Y., Wang J., Liu R., Park S., Lee H., Yip L., Refai-Ahmed G. Design guideline on board-level thermomechanical reliability of 2.5D package. Microelectron. Reliab. 2020;111:113701. doi: 10.1016/j.microrel.2020.113701. [DOI] [Google Scholar]

- 22.Lau J.H., Ko C.T., Peng C.Y., Yang K.M., Xia T., Lin P.B., Chen J.-J., Huang P.-C., Tseng T.-J., Lin E., et al. Thermal cycling test and simulation of fan-out chip-last panel-level packaging for heterogeneous integration. J. Microelectron. Electron. Packag. 2020;18:29–39. doi: 10.4071/imaps.1419800. [DOI] [Google Scholar]

- 23.Ahmed O., Hutchinson L., Su P., Jiang T. Effects of Heatsink Application and PCB Design Variations on BGA Solder Joint Reliability; Proceedings of the Electronic Components and Technology Conference; Virtual. 1 June–4 July 2021; pp. 1001–1006. [Google Scholar]

- 24.Ji L., Chai T.C. Reliability life assessment and prediction for high density FOWLP package using finite element analysis and statistical approach; Proceedings of the Electronic Components and Technology Conference; Virtual. 1 June–4 July 2021; pp. 1359–1365. [Google Scholar]

- 25.Yang J., Cai C., Yin P., Pan K., Lai Y., Wang J., Park S. Optimal thermo-mechanical reliability design of 2.5D lidless package; Proceedings of the InterSociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems; San Diego, CA, USA. 31 May–3 June 2022. [Google Scholar]

- 26.Performance Test Methods and Qualification Requirements for Surface Mount Solder Attachments. IPC; Northbrook, IL, USA: 2002. [Google Scholar]

- 27.Temperature Cycling. JEDEC Solid State Technology Association; Arlington County, VA, USA: 2014. [Google Scholar]

- 28.Shih M.-K., Huang Y.-W., Lin G.-S. Next-Generation High-Density PCB Development by Fan-Out RDL Technology. IEEE Trans. Device Mater. Reliab. 2022;22:296–305. doi: 10.1109/TDMR.2022.3174604. [DOI] [Google Scholar]

- 29.Park S., Lee H.C., Sammakia B., Raghunathan K. Predictive model for optimized design parameters in flip-chip packages and assemblies. IEEE Trans. Compon. Packag. Technol. 2007;30:294–301. doi: 10.1109/TCAPT.2007.898363. [DOI] [Google Scholar]

- 30.Lee C.-C., Wang C.-W., Chen C.-Y. Comparison of Mechanical Modeling to Warpage Estimation of RDL-First Fan-Out Panel-Level Packaging. IEEE Trans. Compon. Packag. Manuf. Technol. 2022;12:1100–1108. doi: 10.1109/TCPMT.2022.3175953. [DOI] [Google Scholar]

- 31.Dasgupta A., Oyan C., Barker D., Pecht M. Solder Creep-Fatigue Analysis by an Energy-Partitioning Approach. ASME. J. Electron. Packag. 1992;114:152–160. doi: 10.1115/1.2906412. [DOI] [Google Scholar]

- 32.Zahn B.A. Solder Joint Fatigue Life Model Methodology for 63Sn37Pb and 95.5Sn4Ag0.5Cu Materials; Proceedings of the Electronic Components and Technology Conference; New Orleans, LA, USA. 27–30 May 2003; pp. 83–94. [Google Scholar]

- 33.Hertzberg R.W., Hauser F.E. Deformation and Fracture Mechanics of Engineering Materials. 4th ed. John Wiley & Sons Inc.; New York, NY, USA: 1996. [Google Scholar]

- 34.Schubert A., Dudek R., Auerswald E., Gollbardt A., Michel B., Reichl H. Fatigue life models for SnAgCu and SnPb solder joints evaluated by experiments and simulation; Proceedings of the Electronic Components and Technology Conference; New Orleans, LA, USA. 27–30 May 2003; pp. 603–610. [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Data Availability Statement

The data presented in this study are available on request from the corresponding author.