Abstract

This paper presents a versatile first-order analog filter using differential difference transconductance amplifiers (DDTAs). The DDTA employs the bulk-driven (BD) multiple-input MOS transistors technique (MI-MOST) operating in the subthreshold region. This results in low-voltage and low-power operational capability. Therefore, the DDTA, designed using 130 nm CMOS technology from UMC in the Cadence environment, operates with 0.3 V and consumes 357.4 nW. Unlike previous works, the proposed versatile first-order analog filter provides first-order transfer functions of low-pass, high-pass, and all-pass filters within a single topology. The non-inverting, inverting, and voltage gain of the transfer functions are available for all filters. Furthermore, the proposed structure provides high-input and low-output impedance, which is required for voltage-mode circuits. The pole frequency and voltage gain of the filters can be electronically controlled. The total harmonic distortion of the low-pass filter was calculated as −39.97 dB with an applied sine wave input signal of 50 mVpp@ 50 Hz. The proposed filter has been used to realize a quadrature oscillator to confirm the advantages of the new structure.

Keywords: differential difference transconductance amplifier, analog filter, voltage-mode circuit, low-voltage low-power circuit

1. Introduction

The second-generation current conveyor (CCII) was introduced in [1] as a single active building block, namely containing a voltage follower between the y- and x-terminals and a current follower between the x- and z-terminals. To increase the performance of the CCII for handling differential input signals, a differential difference current conveyor (DDCC) was proposed [2]. A DDCC includes the advantages of both CCII and the differential difference amplifier (DDA) [3] within a single circuit. One such advantage is a high input impedance and arithmetic operation capability, which is valuable for voltage-mode circuits. However, the circuits based on DDCCs lack electronic tuning capability. Thus, the next phase of development of DDCCs has been to obtain electronic tuning capability, for example, as a differential difference current conveyor transconductance amplifier (DDCCTA) [4], differential difference transconductance amplifier (DDTA) [5], or differential voltage current conveyor transconductance amplifier (DVCCTA) [6]. Recently, the DDTA has been designed to operate with a low power supply and low power consumption and has been successfully utilized for various applications with analog filters [7,8,9,10,11,12].

First-order filters are single-pole circuits that are widely used in signal processing. There are three filtering functions to realize first-order transfer functions: low-pass (LP), high-pass (HP), and all-pass (AP) filters. The first-order LP and HP filters can be used as subcircuits to realize high-order filters [13,14,15,16], while the first-order AP filters are an important block of high-quality (Q) band-pass (BP) filters [17], sinusoidal oscillators [18], time delays [19], group-delay or phase equalizers [20].

Universal first-order filters are topologies that can realize the first-order transfer functions of LP, HP, AP filters into a single circuit. There are many universal first-order filters available in open literature [21,22,23,24,25,26,27,28,29,30,31,32,33,34,35,36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51,52,53,54,55]. Nowadays, the topic of the first-order universal filter is an interesting area for research. Considering the input and output signals of universal first-order filters in [21,22,23,24,25,26,27,28,29,30,31,32,33,34,35,36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51,52,53,54,55], these topologies can be classified as current-mode (CM) filters [21,22,23,24,25,26,27,28,29,30,31,32,33,34,35], voltage-mode (VM) filters [36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51], mixed-mode (MM) filters [52,53,54,55]. Focusing on the CM filters, the circuits in [21,29] offer maximum first-order transfer functions of LP, HP, AP filters. With a suitable choice of the output currents, the filters in [21,29] offer both non-inverting and inverting transfer functions of LP, HP, AP filters, thus obtaining six transfer functions. However, the gain of the transfer functions cannot be controlled. Considering the VM filters in [36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51], the filters in [41,43,44,45,46] offer the voltage gain of the transfer functions, but these filters can control the gain only for a few transfer functions, such as LP and HP filters.

The MM filters are topologies that offer four types of transfer functions in a single circuit: VM, CM, trans-admittance mode (TAM), and trans-impedance mode (TIM). Considering MM filters in [52,53,54,55], the filters in [52,53,54] offer four types of transfer functions (CM, VM, TIM, TAM), but each type offers only three transfer functions of LP, HP, and AP filters.

In this work, a voltage-mode versatile first-order analog filter based on DDTA as an active element is presented. The work shows that the multiple-input DDTA (MI-DDTA) can offer an easy choice for voltage-mode first-order filters. The MI-DDTAs with 0.3 V and 357.4 nW consumption were used, with the bulk-driven (BD) technique of multiple-input MOS transistors (MI-MOST) operating in the subthreshold region. Unlike previous works, the proposed versatile first-order analog filter can realize both non-inverting and inverting transfer functions of LP, HP, and AP filters in a single circuit. In addition, the voltage gain of all transfer functions can be controlled. The proposed structure provides high-input and low-output impedance, which is ideal for voltage-mode circuits. Furthermore, both the pole frequency and voltage gain of all filters can be controlled electronically. The proposed filter has been used to realize a quadrature oscillator to confirm the advantages of the new structure.

2. Proposed Circuit

2.1. CMOS Structure of the Multiple-Input DDTA

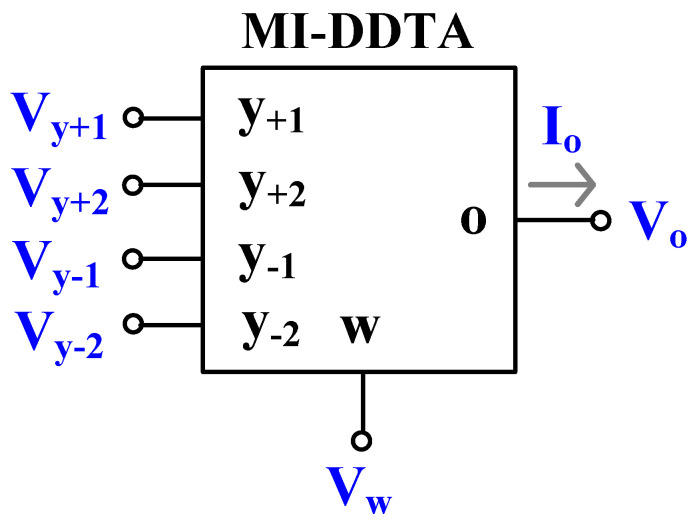

Figure 1 shows the electrical symbol of the DDTA. The y- and o-terminals possess a high impedance level, while the w-terminal possesses a low impedance level. The addition and subtraction voltages at the w-terminal (Vw) are transformed to a current at the o-terminal by the transconductance . The port characteristic of the DDTA can be expressed as:

| (1) |

Figure 1.

Electrical symbol of the MI-DDTA.

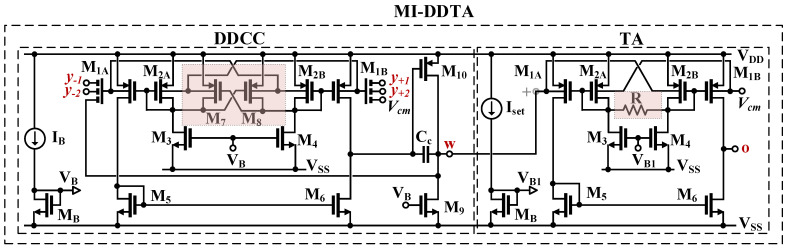

The CMOS structure of the LV LP DDTA was first presented in [10]. The circuit, as shown in Figure 2, consists of two main blocks: a differential-difference current conveyor (DDCC) and a transconductance amplifier (TA). The DDCC can be considered as a two-stage amplifier with a differential difference input stage (M1–M8) and a second stage based on the transistor (M10) operating in a common source configuration. The capacitance CC is used for frequency compensation. The input stage of the DDCC is based on a bulk-driven non-tailed differential pair with partial positive feedback [56,57]. The non-tailed architecture allows operation at very low supply voltages, while providing good common-mode and power supply rejection ratios (CMRR and PSRR, respectively) [56,57]. The BD technique achieves a large common-mode range, which is usually rail-to-rail. In order to improve the voltage gain of the differential amplifier, partial positive feedback (PPF) is introduced by the cross-coupled pair of transistors, M7 and M8. The transistors generate negative conductances, which partially compensate for the total conductances at the gate/drain nodes of M2A and M2B, thus increasing the voltage gain of the whole input stage. The differential difference capability is realized using an MI-BD technique, i.e., using an additional capacitive voltage summing circuit. A particular realization of the MI-BD transistors is shown in Figure 3. The capacitors (CBi) form a voltage divider/voltage summing circuit. In a passband, their impedances are much lower than the resistances of the large resistors (RMOS). The resistors are realized as an anti-parallel connection of two minimum-size MOS transistors operating in a cut-off region (Figure 3c), which are used to provide proper biasing of the bulk terminals of the input MOS transistors for DC. This solution provides differential difference capability without using a second transistor pair, thus saving dissipation power and simplifying the overall structure. The voltage VW can then be expressed as:

| (2) |

where the open-loop gain Av can be expressed as:

| (3) |

where is the voltage gain of the input capacitive divider. Assuming equal capacitances, CBi is equal to 1/3, and is the coefficient associated with PPF. Note that for stable operation, the value of should always be less than unity. In the proposed design, .

Figure 2.

CMOS implementation of the MI-DDTA.

Figure 3.

MI-BD MOST: (a) symbol, (b) realization, (c) possible implementation of RMOS.

The output resistance of the DDCC, seen from the w terminal, can be expressed as:

| (4) |

and is typically 20–30 times lower than .

The second block of the proposed DDTA, namely the transconductance amplifier, was originally proposed and verified experimentally in [58]. The circuit can be seen as a non-tailed differential pair (M1–M6), with an additional linearization resistor R. Assuming M1 = M2, the circuit transconductance can be expressed as [58]:

| (5) |

The circuit shows optimum linearity when the following condition is satisfied [58]:

| (6) |

However, the circuit linearity remains good even for relatively large differences between R and . This enables the tuning of the transconductance of the TA with the biasing current Iset. The voltage gain of the TA can be expressed as:

| (7) |

Due to the non-cascoded structure, its value is relatively low but sufficient for the proposed application.

2.2. Proposed Voltage-Mode First-Order Versatile Analog Filter

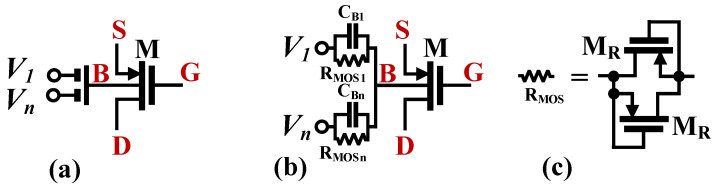

Figure 4 shows the proposed voltage-mode first-order analog filter employing two MI-DDTAs, one grounded capacitor C1 and one grounded resistor, R1. The Vin1, Vin2, Vin3, and Vin4 are the input voltages, while Vo1 and Vo2 are the output voltages. The inputs, Vin1, Vin2, Vin3, and Vin4, are applied via the high-impedance level (y-terminal) of the MI-DDTA, while the output Vo1 is available at the low-impedance level (w-terminal) of the MI-DDTA. Thus, the proposed filter possesses high-input and low-output impedances.

Figure 4.

Proposed voltage-mode first-order universal analog filter.

From Figure 4, using (1) and nodal analysis, the outputs Vo1 and Vo2 can be expressed, respectively, as:

| (8) |

| (9) |

The LP, HP, AP filtering functions can be obtained by suitably applying the input voltages to the circuit. The variant filtering functions of first-order filters are shown in Table 1. It is obvious that the non-inverting and inverting transfer functions of LP, HP, AP filters can be obtained in a single circuit without the need for an inverted input signal. The voltage gain of all transfer functions is obtained at the output Vo2, which can be controlled by . The electronic tuning capability is obtained by varying . However, since this output node does not have a low-impedance level, a buffer circuit maybe required if a low-impedance load is connected.

Table 1.

Obtaining variant filtering functions of the first-order analog filter.

| Filtering Function | Input | Transfer Function | ||

|---|---|---|---|---|

| LP | Non-inverting | |||

| Inverting | ||||

| HP | Non-inverting | |||

| Inverting | ||||

| AP | Non-inverting (Phase leg) | |||

| Inverting (Phase lead) | ||||

The pole frequency of all transfer functions can be expressed by:

| (10) |

The pole frequency can be controlled by . Therefore, the voltage gain and the pole frequency can be electronically controlled.

2.3. Non-Ideality Analysis

The non-ideal characteristics of MI-DDTA can be considered as [11]:

| (11) |

where, for the j-th DDTA, is the voltage gain between and , is the voltage gain between and , is the voltage gain between , and , is the voltage gain between and , of j-th DDTA, and is the non-ideal transconductance of the j-th MI-DDTA. Ideally, the voltage gains, , , , , are equal to unity. However, these voltage gains may sightly deviate from ideality and affect the transfer functions of the proposed filter.

For the DDTA operating near the cut-off frequency, can be approximated by [11]:

| (12) |

where , and denotes the first pole of the j-th MI-DDTA.

Using (11), (8) and (9) can be rewritten, respectively as:

| (13) |

| (14) |

The non-ideal transfer functions of LP, HP, AP filters can be expressed by:

| (15) |

| (16) |

| (17) |

| (18) |

Letting , we obtain:

| (19) |

Letting , we obtain:

| (20) |

Using (12), the denominator of all transfer functions (D(s)) can be expressed by:

| (21) |

The non-ideal transconductance can be made negligible by satisfying:

| (22) |

If the non-ideal behavior of the DDTA operating at a high frequency is also considered, the parallel connection of parasitic resistance (Ro) and parasitic capacitance (Co) at the o-terminal should be taken in account (Ro//Co) [43]. In consideration of the non-ideal behavior of the DDTA given by Ro//Co, the pole frequency of Figure 4 obtained from (21), while satisfying (22), can be determined by:

| (23) |

where and , and are the parasitic capacitance and resistance at the o-terminal of MI-DDTA1.

3. Application Example

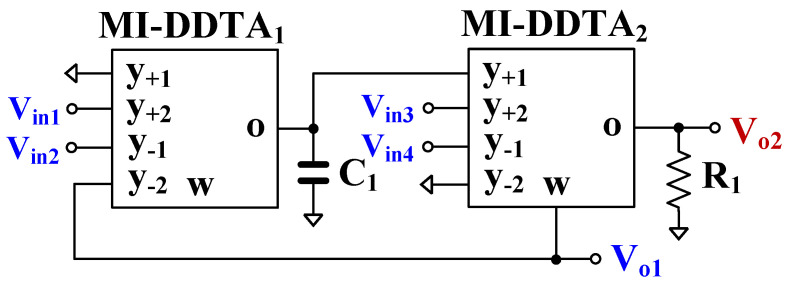

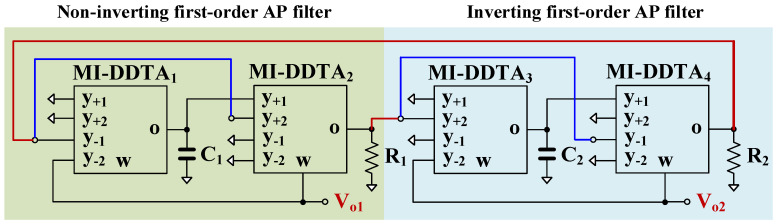

To demonstrate the advantages of the proposed versatile filter, two first-order AP filters, namely non-inverting and inverting AP filters based on the same topology, have been used to realize a sinusoidal oscillator as shown in Figure 5.

Figure 5.

Proposed sinusoidal oscillator using first-order AP filters.

Using Table 1 and the row for AP filters, the loop gain (LG) of the oscillator can be given as:

| (24) |

Letting , , and LG = 1, the characteristics of the oscillator can be expressed by:

| (25) |

The condition of oscillation (CO) can be given by:

| (26) |

The frequency of oscillation (FO) can be given as:

| (27) |

From (15) and (26), the CO can be controlled electronically by and/or and the FO can be controlled electronically by .

4. Simulation Results

The circuit was designed and simulated using the Cadence Virtuoso Analog Design Environment with 130 nm using UMC CMOS technology. The transistor’s aspect ratio and the values of passive devices are shown in Table 2. The voltage supply was 0.3 V (±0.15 V), the bias current of the DDCC IB = 50 nA, and the nominal value of the setting current of the TA Iset = 0.5 µA. The nominal power consumption of the DDTA was 357.4 nW. The input and compensation capacitors were highly linear metal–isolator–metal capacitors (MIM). The linear resistor’s R was a high-resistance poly-resistor. Intensive simulation results of the standalone MI-DDTA including Monte Carlo analysis (MC) and process, voltage, and temperature (PVT) corners were presented in detail in [10]. The open-loop gain of the DDCC (i.e., without the unity gain feedback) was simulated as 73.9 dB and the phase margin was 56.2° for 20 pF load capacitor. The low-frequency gain for Vw/Vy+1 (=Vw/Vy+2) and Vw/Vy-1 (=Vw/Vy-2) is 14 mdB and 57.29 mdB while the −3 dB bandwidth is 22.24 kHz and 22.23 kHz, respectively. The simulated DC transfer characteristics of the DDCC show rail-to-rail operation capability. The simulated gain and phase characteristics for the TA with Iset = 0.5 µA and 20 pF load capacitance show that the low DC gain is 23.2 dB and the bandwidth is 19.65 kHz, while the phase error is 3.8° [10]. The DC characteristic of the output current and the transconductance of the TA versus fully differential input voltage for Iset = 0.125 µA, 0.25 µA, 0.5 µA confirms a rail-to-rail operation with high linearity.

Table 2.

Transistor aspect ratios of the MI-DDTA.

| Device | W/L (µm/µm) |

|---|---|

| M1A, M2A, M1B, M2B | 20/3 |

| M7, M8 | 15/3 |

| M3–M6, MB | 10/3 |

| M9 | 6 × 10/3 |

| M10 | 6 × 20/3 |

| MR | 5/3 |

| MIM capacitor: CB = 0.2 pF, Cc = 4 pF | |

| Poly-resistor R = 90 kΩ | |

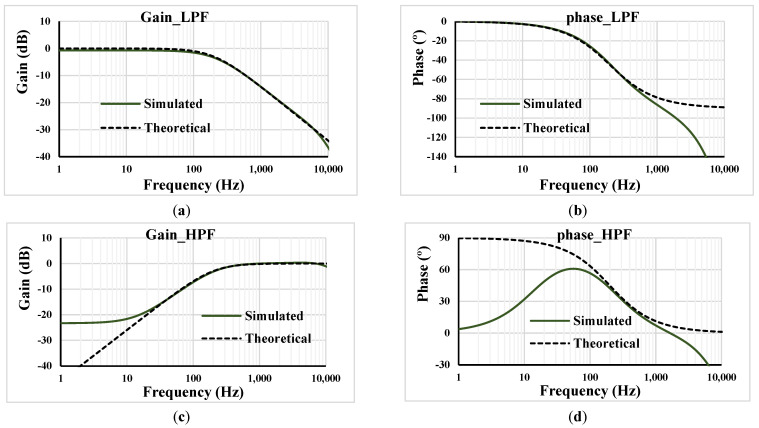

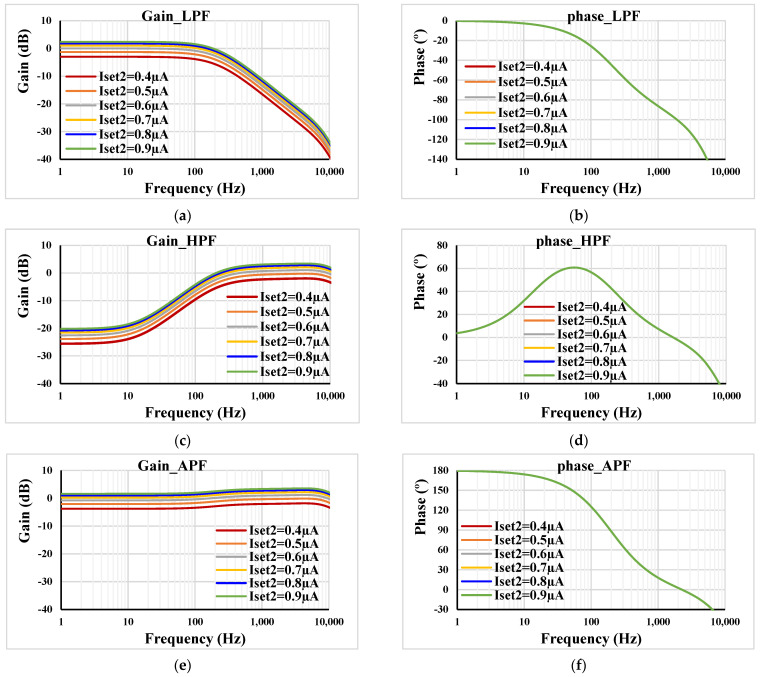

Figure 6 shows the simulated and theoretical frequency characteristics of the gain and phase of the proposed voltage-mode first-order universal filter from Figure 4 with R1 = 400 kΩ, capacitor C1 = 2 nF and setting current Iset1 = Iset2 = 0.5 µA (gm = 2.5 µS). The designed cut-off frequency of 197.4 Hz was very close to the simulated frequency of 195.6 Hz.

Figure 6.

Frequency characteristics of the gain and phase: (a,b) LPF; (c,d) HPF; (e,f) APF.

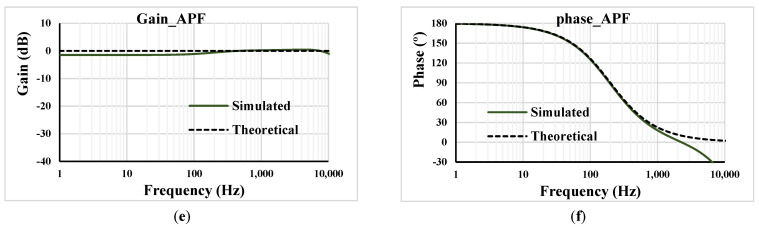

In order to confirm the electronic tuneability of the filter, the frequency characteristics of the gain and phase were repeated for C1 = 2 nF, R1 = 400 kΩ, Iset2 = 0.5 µA, and different Iset1 = (0.3, 0.4, 0.5, 0.6, 0.7) µA. the cut-off frequency was 120.8 Hz, 158.8 Hz, 195.6 Hz, 231.8 Hz, 260.7 Hz, respectively, as depicted in Figure 7.

Figure 7.

Frequency responses of the gain and phase: (a,b) LPF; (c,d) HPF; (e,f) APF with different Iset1.

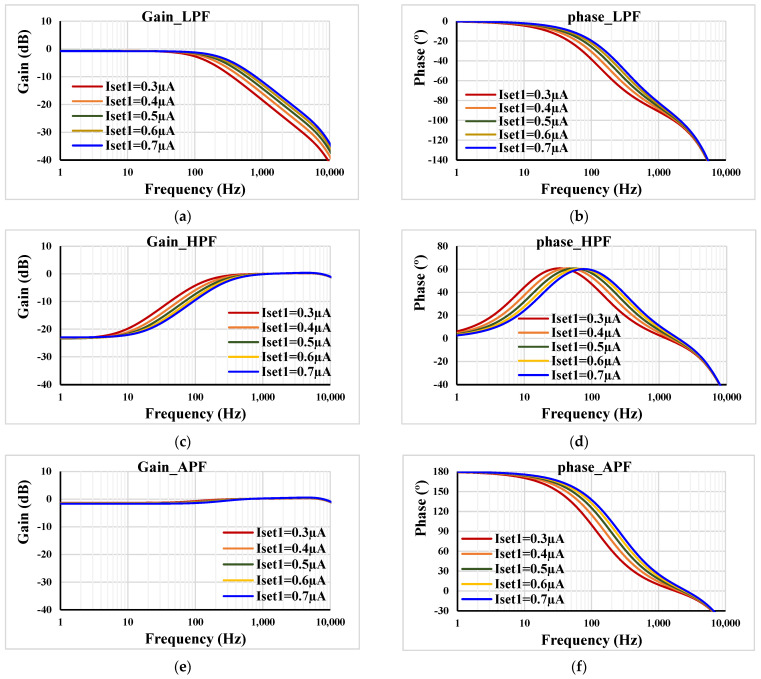

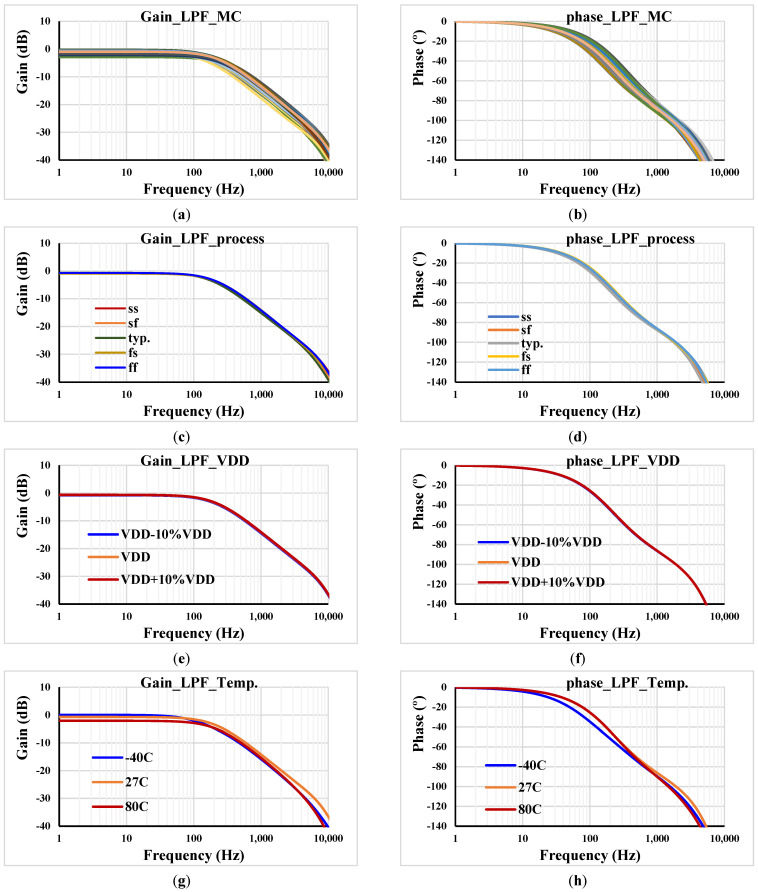

Figure 8 shows the frequency characteristics of the gain and phase for C1 = 2 nF, R1 = 400 kΩ, Iset1 = 0.5 µA, and different Iset2 = (0.4, 0.5, 0.6, 0.7, 0.8, 0.9) µA. The gain was in range of −3 dB to 3.3 dB, which confirms the electronic tunability of the filter gain. When the value of the resistor was changed to R1 = 800 kΩ, the gain was in range of −3 dB to 8 dB.

Figure 8.

Frequency responses of the gain and phase: (a,b) LPF; (c,d) HPF; (e,f) APF with different Iset2.

Figure 9 shows the frequency characteristics of the gain and phase of the LPF for C1 = 2 nF, R1 = 400 kΩ, and Iset1,2 = 0.5 µA. The Monte Carlo analysis, including process and mismatch variation and 200 runs, is shown in (a,b). The gain of the LPF at low frequency was in the range of −2.87 dB to −0.243 dB and the cut-off frequency was in the range of 158.48 Hz to 335.26 Hz. The slow–slow (ss), slow–fast (sf), fast–slow (fs) and fast–fast (ff) processes are shown in (c,d). Finally, (e,f) shows the voltage supply corners, VDD ± 10%VDD, and (g,h) shows the temperature corners −40 °C and 80 °C. As is evident, the curves are almost overlapped, with a slight variation in the temperature corner analysis. This is suspected to be due to the subthreshold region operation that is known to be sensitive to temperature. The deviation of the cut-off frequency can be readjusted by the setting current.

Figure 9.

Frequency responses of the gain and phase for LPF: (a,b) MC; (c,d) process corners; (e,f) voltage corners and (g,h) temperature corners.

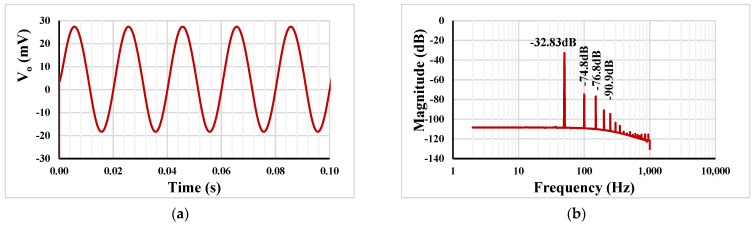

Figure 10a shows the transient response of the LPF with R1 = 400 kΩ, capacitor C1 = 2 nF, the setting current Iset1 = Iset2 = 0.5 µA, and the applied sine wave input signal 50 mVpp@ 50 Hz. The spectrum of the output signal Vo using fast Fourier transform (FFT) is shown in (b). The total harmonic distortion was calculated as −39.97 dB (1.024%).

Figure 10.

The transient response of the LPF (a) and the spectrum of the Vo using FFT (b).

The comparison between the proposed versatile first-order filter and some previous works is shown in Table 3. Recently published filters, such as the CM filter in [29], the VM filters in [44,46,51,59], or the MM filter in [54], have been selected for comparison. The proposed filter offers six transfer functions similar to [29], but the proposed filter can control the voltage gain of the transfer functions. Moreover, the CM filter in [29] uses multiple-output ICCII, which has a high-power consumption. Compared with [44,46,51,59], the proposed filter exhibits rich filtering functions, and the gain of all transfer functions can be controlled. The MM filter in [54] offers nine transfer functions through CM, VM, TAM, and TIM filters, but each filter offers only three transfer functions of LP, HP, and AP filters, whereas the proposed VM filter offers six transfer functions of LP, HP, and AP filters. The filters using a single active device in [44,46,54] apply the input voltage signal via a capacitor or resistor, which is not ideal for voltage-mode circuits and integrated circuits. In comparison, the proposed filter has high-input and low-output impedance. Finally, compared with all filters in [29,44,46,51,54,59], the proposed filter unequivocally offers the lowest power supply and power consumption, which is served by the low-voltage low-power MI-DDTA. The comparison table also includes a figure of merit (FoM) = Pdiss/(N) fo, where Pdiss is the power dissipation, N is the filter order (number of poles), and fo is the pole frequency. However, here it is important to note that this FoM is specific to power dissipation, filter order, and pole frequency and does not cover all aspects of filter performance. The proposed filter offers many advantages over other designs due to the multiple-input MOS transistor, which increases the capability of the arithmetic operations of the proposed MI-DDTA without increasing the power consumption such as number of filter functions, high input impedance, electronic parameter control, gain control, and use of grounded passive components, which is the main attractive performance of the proposed filter which cannot be achieved by using two conventional DDTAs.

Table 3.

Comparison of the proposed design with previous first-order filters.

| Features | Proposed | [29] 2017 | [44] 2021 | [46] 2022 | [51] 2022 | [54] 2023 | [59] 2023 |

|---|---|---|---|---|---|---|---|

| Active and passive elements | 2 DDTA, 1 C, 1 R | 2 ICCII, 1 C, 1 MOS Figure 4 |

1 LT1228, 1 C, 2 R | 1 VD-DIBA, 1 C, 2 R | 2 CFOA, 1 C, 4 R Figure 1d |

1 VGA, 1 C, 1 R | 2 OTA, 1 C |

| Realization | CMOS structure (0.13 μm) | CMOS structure (0.13 μm) | Commercial IC (LT1228) | Commercial IC (LT1228, AD830) | Commercial IC (AD844) | CMOS structure (0.18 μm) | CMOS structure (0.18 μm) |

| Mode operation | VM | CM | VM | VM | VM | MM | VM |

| Type of filter | MISO | SIMO | MISO | MISO | MISO | MIMO | MISO |

| Number of filtering functions | 6 (LP+, LP−, HP+, HP−, AP+, AP−) | 6 (LP+, LP−, HP+, HP−, AP+, AP−) | 4 (LP+, HP+, AP+, AP−) | 4 (LP−, HP−, AP+, AP−) | 3 (LP−, HP+, AP+) | 3 (LP+, HP+, AP+) | 6 (LP+, LP−, HP+, HP−, AP+, AP−) |

| High-input impedance | Yes | - | No | No | Yes | No | Yes |

| Electronic control of parameter | Yes | Yes | Yes | Yes | No | Yes | Yes |

| Control of gain | Yes | No | Yes (LP, HP) | Yes (LP, HP) | Yes | No | No |

| Using grounded capacitor/resistor | Yes | No | No | No | No | No | Yes |

| Pole frequency (kHz) | 0.195 | 2600 | 90 | 159.15 | 159 | 1590 | 0.220 |

| Total harmonic distortion (%) | 1.024@50 mVpp | <1.5@90 μApp | 1@200 mVpp | <1@150 mVpp | - | - | 0.36@40 mVpp |

| Supply voltage (V) | 0.3 | ±0.75 | ±5 | ±5 | ±12 | ±0.9 | 0.5 |

| Power dissipation (µW) | 0.7148 | 4080 | 57,600 | - | - | - | 59.5 × 10−3 |

| FoM (µW/kHz) | 3.66 | 1.56 | 640 | - | - | - | 0.27 |

| Verification of result | Sim. | Sim. | Exp. | Exp. | Exp. | Sim/Exp | Post-layout Sim. |

Note: VD-DIBA = voltage differencing differential input buffered amplifier, ICCII = inverting second-generation current conveyors, VGA = voltage differencing gain amplifier, MISO = multiple-input single-output, SIMO = single-input multiple-output, MIMO = multiple-input multiple-output, MM = Mixed-mode, LP+ = non-inverting low-pass filter, LP− = inverting low-pass filter, HP+ = non-inverting high-pass filter, HP− = inverting high-pass filter, AP+ = non-inverting all-pass filter, AP− = inverting all-pass filter.

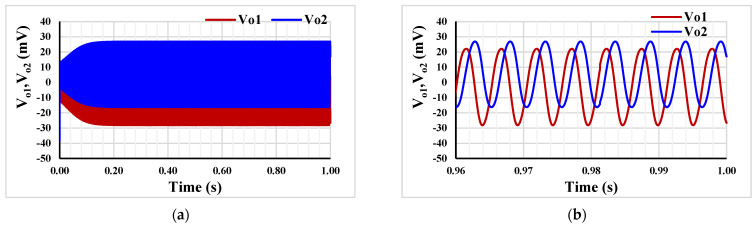

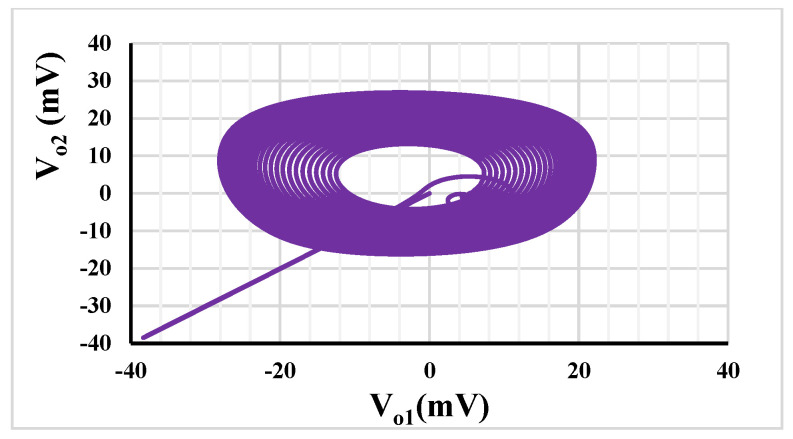

For the oscillator in Figure 5, R1 = 400 kΩ, capacitors C1 = C2 = 2 nF and setting current Iset1 = 0.5 µA were selected. To start the oscillation, R2 = 500 kΩ and Iset2 = 0.55 µA. Figure 11a,b show the running oscillation and steady state, respectively. The THD was around 3%. The outputs Vo1 and Vo2 are in quadrature with a frequency of 192 Hz. Figure 12 shows the relation between Vo1 and Vo2 that can confirm the quadrature relationship of the output signals.

Figure 11.

The running oscillation (a) and the steady state (b).

Figure 12.

The quadrature relationship between Vo1 and Vo2.

5. Conclusions

This work presents the realization of a versatile first-order analog filter that consists of two MI-DDTAs, one grounded capacitor, and one resistor. The proposed filter possesses six transfer functions of LP, HP, and AP filters in a single topology, high-input and low-output impedance, and electronic control of the gain and the pole frequency of transfer functions. Thanks to the bulk-driven multiple-input MOS transistor technique operating in the subthreshold region, the DDTA works with a 0.3 V of power supply and 357.4 nW of power consumption. In order to confirm the advantages of the new circuit, the proposed first-order filter has been used to realize a sinusoidal oscillator with a frequency of 192 Hz and 3% THD. The filter and oscillator are suitable for low frequency applications such as biomedical applications. The simulation results confirm the performance of the filter.

Author Contributions

Conceptualization, M.K., F.K. and T.K.; methodology, M.K. and F.K.; software, F.K. and P.S.; validation, F.K. and T.K.; formal analysis, T.K., M.K. and F.K.; investigation, F.K. and M.K.; resources, F.K. and M.K.; writing—original draft preparation, M.K., F.K., T.K. and P.S.; writing—review and editing, F.K. and T.K.; visualization, F.K., T.K., P.S. and M.K.; supervision, F.K.; project administration, F.K.; funding acquisition, F.K. and M.K. All authors have read and agreed to the published version of the manuscript.

Conflicts of Interest

The authors declare no conflict of interest.

Funding Statement

This work was supported by the University of Defence within the Organization Development Project VAROPS.

Footnotes

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

References

- 1.Smith K., Sedra A. The current conveyor—A new circuit building block. Proc. IEEE. 1968;56:1368–1369. doi: 10.1109/PROC.1968.6591. [DOI] [Google Scholar]

- 2.Chiu W., Liu S.-I., Tsao H.-W., Chen J.-J. CMOS differential difference current conveyors and their applications. IEE Proc.-Circuits Devices Syst. 1996;143:91–96. doi: 10.1049/ip-cds:19960223. [DOI] [Google Scholar]

- 3.Sackinger E., Guggenbuhl W. A versatile building block: The CMOS differential difference amplifier. IEEE J. Solid-state Circuits. 1987;22:287–294. doi: 10.1109/JSSC.1987.1052715. [DOI] [Google Scholar]

- 4.Pandey N., Paul S.K. Differential Difference Current Conveyor Transconductance Amplifier: A New Analog Building Block for Signal Processing. J. Electr. Comput. Eng. 2011;2011:361384. doi: 10.1155/2011/361384. [DOI] [Google Scholar]

- 5.Kumngern M. DDTA and DDCCTA: New active elements for analog signal processing; Proceedings of the 2012 IEEE International Conference on Electronics Design, Systems and Applications (ICEDSA); Kuala Lumpur, Malaysia. 5–6 November 2012; pp. 141–145. [DOI] [Google Scholar]

- 6.Jantakun A., Pisutthipong N., Siripruchyanun M. A synthesis of temperature insensitive/electronically controllable floating simulators based on DV-CCTAs; Proceedings of the 2009 6th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology; Chonburi, Thailand. 6–9 May 2009; pp. 560–563. [DOI] [Google Scholar]

- 7.Kumngern M., Suksaibul P., Khateb F., Kulej T. 1.2 V Differential Difference Transconductance Amplifier and Its Application in Mixed-Mode Universal Filter. Sensors. 2022;22:3535. doi: 10.3390/s22093535. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 8.Kumngern M., Khateb F., Kulej T. 0.5 V Universal Filter and Quadrature Oscillator Based on Multiple-Input DDTA. IEEE Access. 2023;11:9957–9966. doi: 10.1109/ACCESS.2023.3240520. [DOI] [Google Scholar]

- 9.Khateb F., Kumngern M., Kulej T., Biolek D. 0.5 V Differential Difference Transconductance Amplifier and Its Application in Voltage-Mode Universal Filter. IEEE Access. 2022;10:43209–43220. doi: 10.1109/ACCESS.2022.3167700. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 10.Khateb F., Kumngern M., Kulej T., Biolek D. 0.3-Volt Rail-to-Rail DDTA and Its Application in a Universal Filter and Quadrature Oscillator. Sensors. 2022;22:2655. doi: 10.3390/s22072655. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 11.Kulej T., Kumngern M., Khateb F., Arbet D. 0.5 V Versatile Voltage- and Transconductance-Mode Analog Filter Using Differential Difference Transconductance Amplifier. Sensors. 2023;23:688. doi: 10.3390/s23020688. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 12.Khateb F., Kumngern M., Kulej T., Ranjan R.K. 0.5 V multiple-input multiple-output differential difference transconductance amplifier and its applications to shadow filter and oscillator. IEEE Access. 2023;11:31212–31227. doi: 10.1109/ACCESS.2023.3260146. [DOI] [Google Scholar]

- 13.Palani R.K., Sturm M., Harjani R. A 1.56mW 50MHz 3rd-order filter with current-mode active-RC biquad and 33dBm IIP3 in 65nm CMOS; Proceedings of the 2013 IEEE Asian Solid-State Circuits Conference (A-SSCC); Singapore. 11–13 November 2013; pp. 373–376. [DOI] [Google Scholar]

- 14.Hanumantha G.R., Sreenivasulu P., Rekha S., Bhat M.S. A 0.3-V, 2.4-nW, and 100-Hz fourth-order LPF for ECG signal processing. Int. J. Circuit Theory Appl. 2020;48:1853–1863. doi: 10.1002/cta.2839. [DOI] [Google Scholar]

- 15.Abuan D.D., Perez G.F., Medrano M.B., Velasco C.P. Wide Bandpass Filter Composed of First-order and Second-Order Active High Pass Filters Simulated Using MATLAB and Multisim Live; Proceedings of the 2022 2nd International Conference on Technological Advancements in Computational Sciences (ICTACS); Tashkent, Uzbekistan. 10–12 October 2022; pp. 403–408. [DOI] [Google Scholar]

- 16.Isaksen J., Leber R., Schmid R., Schmid H.-J., Generali G., Abacherli R. The first-order high-pass filter influences the automatic measurements of the electrocardiogram; Proceedings of the 2016 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP); Shanghai, China. 20–25 March 2016; pp. 784–788. [DOI] [Google Scholar]

- 17.Comer D., Gonzalez J. A high-frequency integrable bandpass filter configuration. IEEE Trans. Circuits Syst. II Analog. Digit. Signal Process. 1997;44:856–861. doi: 10.1109/82.633445. [DOI] [Google Scholar]

- 18.Gift S. The application of all-pass filters in the design of multiphase sinusoidal systems. Microelectron. J. 2000;31:9–13. doi: 10.1016/S0026-2692(99)00084-1. [DOI] [Google Scholar]

- 19.Garakoui S.K., Klumperink E.A.M., Nauta B., Vanvliet F.E. Frequency Limitations of First-Order gm−RC All-Pass Delay Circuits. IEEE Trans. Circuits Syst. II Express Briefs. 2013;60:572–576. doi: 10.1109/tcsii.2013.2268418. [DOI] [Google Scholar]

- 20.Paul A., Ramirez-Angulo J., Lopez-Martin A.J., Carvajal R.G. CMOS First-Order All-Pass Filter With 2-Hz Pole Frequency. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018;27:294–303. doi: 10.1109/TVLSI.2018.2878017. [DOI] [Google Scholar]

- 21.Li Y.-A. A series of new circuits based on CFTAs. AEU-Int. J. Electron. Commun. 2012;66:587–592. doi: 10.1016/j.aeue.2011.11.011. [DOI] [Google Scholar]

- 22.Kumar A., Paul S.K. Current mode first order universal filter and multiphase sinusoidal oscillator. AEU-Int. J. Electron. Commun. 2017;81:37–49. doi: 10.1016/j.aeue.2017.07.004. [DOI] [Google Scholar]

- 23.Maheshwari S. Tuning approach for first-order filters and new current-mode circuit example. IET Circuits Devices Syst. 2018;12:478–485. doi: 10.1049/iet-cds.2017.0431. [DOI] [Google Scholar]

- 24.Chaturvedi B., Mohan J., Jitender, Kumar A. A Novel Realization of Current-Mode First Order Universal Filter; Proceedings of the 2019 6th International Conference on Signal Processing and Integrated Networks (SPIN); Noida, India. 2–3 February 2017; pp. 623–627. [DOI] [Google Scholar]

- 25.Horng J.-W., Wu C.-M., Zheng J.-H., Li S.-Y. Current-Mode First-Order Highpass, Lowpass, and Allpass Filters Using Two ICCIIs; Proceedings of the 2020 IEEE International Conference on Consumer Electronics-Taiwan (ICCE-Taiwan); Taoyuan, Taiwan. 28–30 September 2020; pp. 1–2. [DOI] [Google Scholar]

- 26.Yucel F. A DVCC-Based Current-Mode First-Order Universal Filter. J. Circuits Syst. Comput. 2021;30:2150305. doi: 10.1142/S0218126621503059. [DOI] [Google Scholar]

- 27.Yuce E., Minaei S. A new first-order universal filter consisting of two ICCII + s and a grounded capacitor. AEU-Int. J. Electron. Commun. 2021;137:153802. doi: 10.1016/j.aeue.2021.153802. [DOI] [Google Scholar]

- 28.Herencsar N., Koton J., Sagbas M., Ayten U.E. New tunable resistorless CM first-order filter based on single CBTA and grounded capacitor; Proceedings of the 2016 IEEE 59th International Midwest Symposium on Circuits and Systems (MWSCAS); Abu Dhabi, United Arab Emirates. 16–19 October 2016; pp. 1–4. [DOI] [Google Scholar]

- 29.Safari L., Yuce E., Minaei S. A new ICCII based resistor-less current-mode first-order universal filter with electronic tuning capability. Microelectron. J. 2017;67:101–110. doi: 10.1016/j.mejo.2017.07.015. [DOI] [Google Scholar]

- 30.Agrawal D., Maheshwari S. An Active-C Current-Mode Universal First-Order Filter and Oscillator. J. Circuits Syst. Comput. 2019;28:1950219. doi: 10.1142/S0218126619502190. [DOI] [Google Scholar]

- 31.Chaturvedi B., Kumar A., Mohan J. Low Voltage Operated Current-Mode First-Order Universal Filter and Sinusoidal Oscillator Suitable for Signal Processing Applications. AEU-Int. J. Electron. Commun. 2018;99:110–118. doi: 10.1016/j.aeue.2018.11.025. [DOI] [Google Scholar]

- 32.Singh P., Varshney V., Kumar A., Nagaria R. Electronically Tunable First Order Universal Filter based on CCDDCCTA; Proceedings of the 2019 IEEE Conference on Information and Communication Technology; Allahabad, India. 6–8 December 2019; pp. 1–6. [DOI] [Google Scholar]

- 33.Chaturvedi B., Mohan J., Jitender, Kumar A. Resistorless Realization of First-Order Current Mode Universal Filter. Radio Sci. 2020;55:1–10. doi: 10.1029/2019RS006932. [DOI] [Google Scholar]

- 34.Mohan J., Chaturvedi B. Jitender CMOS Compatible First-Order Current Mode Universal Filter Structure and its Possible Tunable Variant. J. Circuits Syst. Comput. 2022;31:2250242. doi: 10.1142/S0218126622502425. [DOI] [Google Scholar]

- 35.Kumar A., Kumar S., Elkamchouchi D.H., Urooj S. Fully Differential Current-Mode Configuration for the Realization of First-Order Filters with Ease of Cascadability. Electronics. 2022;11:2072. doi: 10.3390/electronics11132072. [DOI] [Google Scholar]

- 36.Myderrizi I., Minaei S., Yuce E. An Electronically Fine-Tunable Multi-Input–Single-Output Universal Filter. IEEE Trans. Circuits Syst. II Express Briefs. 2011;58:356–360. doi: 10.1109/TCSII.2011.2158168. [DOI] [Google Scholar]

- 37.Abaci A., Yuce E. Voltage-mode first-order universal filter realizations based on subtractors. AEU-Int. J. Electron. Commun. 2018;90:140–146. doi: 10.1016/j.aeue.2018.04.017. [DOI] [Google Scholar]

- 38.Banerjee K., Bnadopadhyaya P.K., Sarkar B., Biswas A. Multi Input Single Output using Operational Transresistance Amplifier as First Order Filter; Proceedings of the 2020 IEEE VLSI DEVICE CIRCUIT AND SYSTEM (VLSI DCS); Kolkata, India. 18–19 July 2020; pp. 271–274. [DOI] [Google Scholar]

- 39.Kumari S., Nand D. DDCC-based MISO type Voltage-mode First-order Universal Filter; Proceedings of the 2022 2nd International Conference on Intelligent Technologies (CONIT); Hubli, India. 24–26 June 2022; pp. 1–6. [DOI] [Google Scholar]

- 40.Dogan M., Yuce E. A first-order universal filter including a grounded capacitor and two CFOAs. Analog. Integr. Circuits Signal Process. 2022;112:379–390. doi: 10.1007/s10470-022-02021-2. [DOI] [Google Scholar]

- 41.Chinpark K., Jaikla W., Siripongdee S., Suwanjan P. Electronically controllable first-order multifuntion filter with using single active building block; Proceedings of the 2018 3rd International Conference on Control and Robotics Engineering (ICCRE); Nagoya, Japan. 20–23 April 2018; pp. 192–195. [DOI] [Google Scholar]

- 42.Moonmuang P., Pukkalanun T., Tangsrirat W. Voltage differencing buffered amplifier-based electronically tunable grounded capacitance multiplier; Proceedings of the 8th International Conference on Informatics, Environment, Energy and Applications; Osaka, Japan. 16–19 March 2019; pp. 208–211. [DOI] [Google Scholar]

- 43.Jaikla W., Talabthong P., Siripongdee S., Supavarasuwat P., Suwanjan P., Chaichana A. Electronically controlled voltage mode first order multifunction filter using low-voltage low-power bulk-driven OTAs. Microelectron. J. 2019;91:22–35. doi: 10.1016/j.mejo.2019.07.009. [DOI] [Google Scholar]

- 44.Jaikla W., Buakhong U., Siripongdee S., Khateb F., Sotner R., Silapan P., Suwanjan P., Chaichana A. Single Commercially Available IC-Based Electronically Controllable Voltage-Mode First-Order Multifunction Filter with Complete Standard Functions and Low Output Impedance. Sensors. 2021;21:7376. doi: 10.3390/s21217376. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 45.Barile G., Safari L., Pantoli L., Stornelli V., Ferri G. Electronically Tunable First Order AP/LP and LP/HP Filter Topologies Using Electronically Controllable Second Generation Voltage Conveyor (CVCII) Electronics. 2021;10:822. doi: 10.3390/electronics10070822. [DOI] [Google Scholar]

- 46.Duangmalai D., Suwanjan P. The voltage-mode first order universal filter using single voltage differencing differential input buffered amplifier with electronic controllability. Int. J. Electr. Comput. Eng. (IJECE) 2022;12:1308–1323. doi: 10.11591/ijece.v12i2.pp1308-1323. [DOI] [Google Scholar]

- 47.Singh P., Nagaria R.K. Voltage mode and trans-admittance mode first-order universal filters employing DV-EXCCCII. Aust. J. Electr. Electron. Eng. 2022;19:396–406. doi: 10.1080/1448837X.2022.2088571. [DOI] [Google Scholar]

- 48.Dogan M., Yuce E., Dicle Z. CFOA-based first-order voltage-mode universal filters. AEU-Int. J. Electron. Commun. 2023;161:154550. doi: 10.1016/j.aeue.2023.154550. [DOI] [Google Scholar]

- 49.Chaturvedi B., Kumar A. Electronically Tunable First-Order Filters and Dual-Mode Multiphase Oscillator. Circuits Syst. Signal Process. 2018;38:2–25. doi: 10.1007/s00034-018-0849-x. [DOI] [Google Scholar]

- 50.Rohilla K., Pushkar K.L., Kumar R., Raj A. Resistorless First-Order Universal Filter Structures Employing OTAs with Independent Controllability of Gain and Pole Frequency. IETE J. Res. 2022:1–21. doi: 10.1080/03772063.2022.2132305. [DOI] [Google Scholar]

- 51.Raj A., Bhaskar D.R., Senani R., Kumar P. Extension of recently proposed two-CFOA-GC all pass filters to the realisation of first order universal active filters. AEU-Int. J. Electron. Commun. 2022;146:154119. doi: 10.1016/j.aeue.2022.154119. [DOI] [Google Scholar]

- 52.Raj A. Mixed-Mode Electronically-Tunable First-Order Universal Filter Structure Employing Operational Transconductance Amplifiers. J. Circuits Syst. Comput. 2022;31:2250234. doi: 10.1142/S0218126622502346. [DOI] [Google Scholar]

- 53.Bhaskar D.R., Raj A., Senani R., Kumar P. CFOA-based simple mixed-mode first-order universal filter configurations. Int. J. Circuit Theory Appl. 2022;50:2631–2641. doi: 10.1002/cta.3289. [DOI] [Google Scholar]

- 54.Roongmuanpha N., Likhitkitwoerakul N., Fukuhara M., Tangsrirat W. Single VDGA-Based Mixed-Mode Electronically Tunable First-Order Universal Filter. Sensors. 2023;23:2759. doi: 10.3390/s23052759. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 55.Varol A., Yucel F., Cakir A. A New Electronically Tunable Transimpedance-Mode OTA-Based First-Order Universal Filter and Its Quadrature Oscillator Application. J. Circuits Syst. Comput. 2022 doi: 10.1142/S0218126623501840. [DOI] [Google Scholar]

- 56.Kulej T. 0.4-V Bulk-Driven Operational Amplifier with Improved Input Stage. Circuits Syst. Signal Process. 2014;34:1167–1185. doi: 10.1007/s00034-014-9906-2. [DOI] [Google Scholar]

- 57.Kulej T., Khateb F. Design and implementation of sub 0.5-V OTAs in 0.18-μm CMOS. Int. J. Circuit Theory Appl. 2018;46:1129–1143. doi: 10.1002/cta.2465. [DOI] [Google Scholar]

- 58.Kulej T., Khateb F., Arbet D., Stopjakova V. A 0.3-V High Linear Rail-to-Rail Bulk-Driven OTA in 0.13 μm CMOS. IEEE Trans. Circuits Syst. II Express Briefs. 2022;69:2046–2050. doi: 10.1109/TCSII.2022.3144095. [DOI] [Google Scholar]

- 59.Khateb F., Kumngern M., Kulej T. 0.5-V Nano-Power Voltage-Mode First-Order Universal Filter Based on Multiple-Input OTA. IEEE Access. 2023;11:49806–49818. doi: 10.1109/ACCESS.2023.3277252. [DOI] [Google Scholar]