Abstract

This paper presents the complete design, fabrication, and characterization of a shallow-mesa photodiode for short-wave infra-red (SWIR) sensing. We characterized and demonstrated photodiodes collecting 1.55 μm photons with a pixel pitch as small as 3 μm. For a 5 μm pixel pitch photodiode, we measured the external quantum efficiency reaching as high as 54%. With substrate removal and an ideal anti-reflective coating, we estimated the internal quantum efficiency as achieving 77% at 1.55 μm. The best measured dark current density reached 5 nA/cm2 at −0.1 V and at 23 °C. The main contributors responsible for this dark current were investigated through the study of its evolution with temperature. We also highlight the importance of passivation with a perimetric contribution analysis and the correlation between MIS capacitance characterization and dark current performance.

Keywords: InGaAs, photodiode, SWIR, shallow-mesa, small pitch

1. Introduction

The development of short-wave infra-red (SWIR) sensors is being led by the growing demand in various fields such as security, automotive, industry, and agriculture [1]. In the SWIR range between 1 and 2.5 μm, silicon is quasi transparent () hence, to absorb an SWIR photon, the absorption material needs to be changed. The main candidates to do so and to be integrated in a SWIR sensor are PbS quantum dots in quantum films [2], In0.53Ga0.47As [3,4,5,6], Ge on Si [7,8], or graphene [9,10].

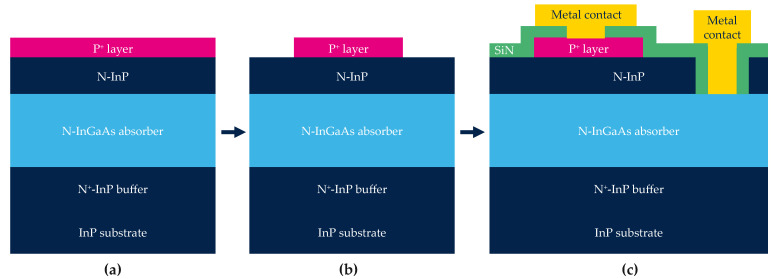

In0.53Ga0.47As is latticed-matched to InP and has a band gap of 0.74 eV at room temperature [11]. This band gap is suitable for SWIR collection, leading to a cut-off wavelength of 1.7 μm. The state-of-the-art for an InGaAs image sensor integrated on a Si-based read-out integrated circuit (ROIC) is a 5 μm pixel pitch with quantum efficiency (QE) greater than 75% at 1.2 μm. The dark current is reported to be as low as 2 nA/cm2 at −0.1 V and at 23 °C [3]. The standard structure for an InGaAs-based SWIR sensor is shown in Figure 1a. It is composed of a thick low doped n-InGaAs absorption layer epitaxied on an InP substrate. III-V materials, such as InGaAs, lack high quality native dielectric and are sensitive to electrical surface defect density [12,13]. To minimize surface leakage current at the InGaAs/dielectric interface, the InGaAs layer is covered by an InP layer which has a larger band gap of 1.34 eV at 25 °C [14]. This layer is used as passivation to move the poor electronic interface away from the active region. In such structures where the InGaAs layer is the active region, it is a priority to have the lowest defect density possible at the interfaces and in the bulk.

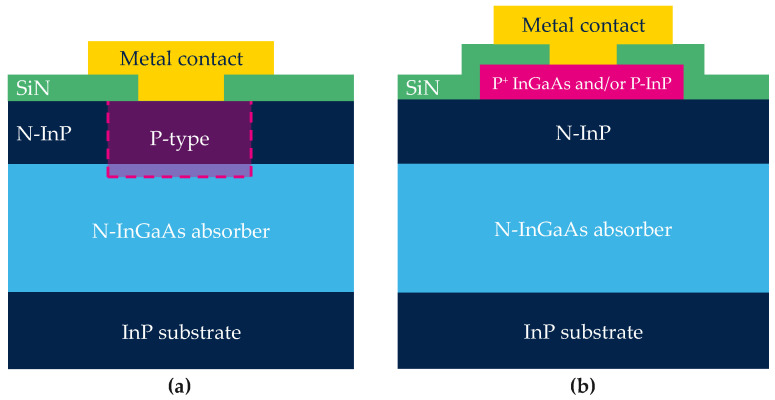

Figure 1.

Schematic cross section of the photodiode after different processes. (a) Photodiode fabricated by Zn diffusion or Be implantation; (b) photodiode fabrication using shallow mesa technique.

For the InGaAs photodiode fabrication, the crucial process step is the definition of each pixel by the creation of a P region in the N-type stack. Literature reports different alternatives for this purpose such as Zn diffusion [3,4,15], Be implantation [16,17], or shallow mesa-type architecture [18,19].

Today, the standard industrial process to create the P-type area relies on the Zn diffusion process. First, a SiN dielectric mask is deposited on the N-type stack. The dielectric is then opened, and Zn is diffused through this aperture. Zn atoms diffuse in the InP layer and reach the InGaAs absorption layer, creating the P-type region. Figure 1a shows the schematic cross section of the photodiode after the diffusion process. To scale down the pixel pitch to a few μm dimensions, the isotropic behaviour of the diffusion presents a challenge. In addition to this isotropic diffusion, it has been shown that Zn diffuses laterally faster in InGaAs than in InP [20]. Greater doping near the interface in the InGaAs layer seems to successfully limit the lateral spread for a 15 μm pixel pitch [20]. With the reduction of the pixel pitch, this diffusion process is harder to control as the distance between the two nearest P-type wells reduces. This phenomenon might then limit the final resolution of the image sensor.

Ionic implantation (I/I) could be an interesting solution to overcome the issue of lateral diffusion. I/I is commonly used in Si processes to precisely locate the dopants in the structure. The main drawback of this technique is due to the introduction of many defects. It is mandatory to cure as many defects as possible during the anneal following the implantation to avoid the generation of dark current. Few studies have reported the damage in InP/InGaAs photodiodes caused by I/I [21] but curing defects in the III-V structure have been studied mostly in GaAs [22,23,24,25]. After I/I, the amorphous III-V layer shows poor recrystallization because of the binary or ternary nature of the material. The differences in solubility contribute to the formation of disorder in the lattice [22]. We previously reported the use of Be implantation to define the InGaAs/InP photodiode. The published dark current is at best in the range of the μA/cm2 [17].

Finally, combining in situ Zn-doped with photolithography and etching tools to define the p region could allow control of the lateral size of the diode. Only a few groups have reported studies of such architecture [18,19,26]. Unlike other studies, our process for mesa-type device fabrication only removes the p-doped region from the top stack. The final schematic structure is presented on Figure 1b and is referred to as shallow-mesa architecture. The stack must be carefully designed to allow the collection of photo-carriers generated in the InGaAs absorption layer (colour: light blue in Figure 1).

For the fabrication of the InGaAs image sensor with pixel pitch below 5 μm, the Cu–Cu hybridization technique from Si image sensors can be adapted to InGaAs image sensors [3] as this method is already in mass production for pixel pitch down to 1 μm [27].

The InGaAs image sensor fabrication targets a Si-CMOS compatible process in large format for high volume. First, epitaxial dies would be bonded on a large format carrier Si wafer. Then, the III-V photodiode process would be performed with up-to-date Si tools. Lastly, the photodiodes would be bonded on the Si ROIC. In this perspective, the in situ doping alternative is a low thermal budget process which is an asset for this integration in a Si-CMOS compatible fab. This kind of Si-CMOS compatible process flow is also presented in [3] with Zn diffused photodiodes.

2. Design of the Shallow-Mesa Architecture

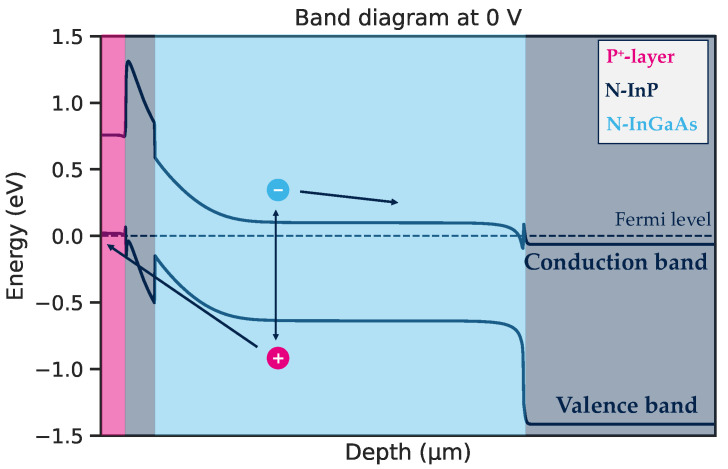

The goal of the designed structure is to collect the photogenerated carriers from the InGaAs absorption layer at low reverse bias, to match the ROIC needs. The minority carriers must go through the heterojunction visible on the simulated band diagram presented in Figure 2. The N-InP layer passivates the small gap InGaAs layer as mentioned previously, but the heterojunction introduces an unfavourable barrier for the hole collection. To overcome this barrier, the structure is designed to intrinsically introduce an electric field that attracts carriers at equilibrium.

Figure 2.

Band diagram of simulated structure at equilibrium with the photogenerated pair schematically represented with their path of collection.

The device simulation is performed with Synopsys Sentaurus software [28] and aims at finding a set of parameters which suppresses the electrostatic barrier for the collection path. The simulation is conducted considering Auger and radiative recombination as well as Shockley–Read-Hall (SRH) recombination. Intrinsic and quality related material parameters are based on the literature [29,30] and are used as simulation inputs for model calibration.

For the carrier collection, the electric field can be modulated by three key parameters which are the doping and thickness of the barrier N-InP layer and the doping concentration of the P-type contact layer. Figure 3 shows the evolution of the band diagram at equilibrium for a fixed P-type layer doping. The impact of the N-InP thickness ranging from 80 nm to 300 nm is presented Figure 3a where the thicker the N-InP, the greater the electrostatic barrier. This is also visible in Figure 3b as the larger the doping of the N-InP layer, the greater the barrier (doping values between 1015 and 1018 cm−3).

Figure 3.

Top zoom of the structure—Impact of the N-InP (a) thickness and (b) doping on the band diagram at equilibrium.

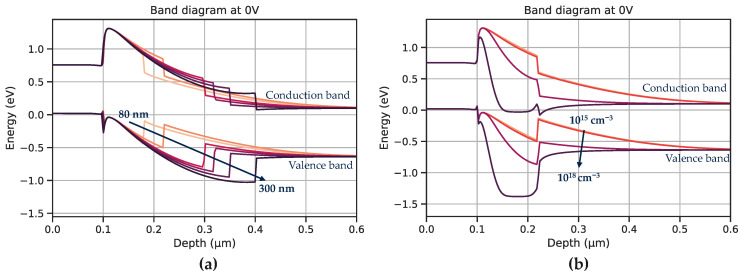

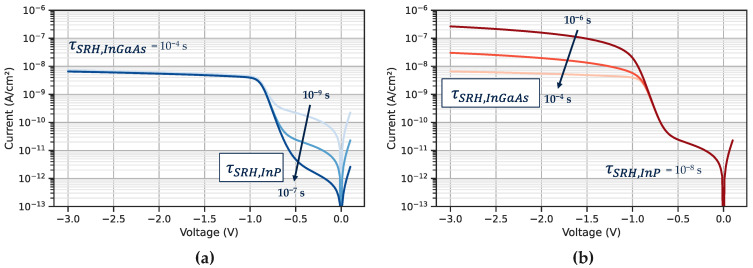

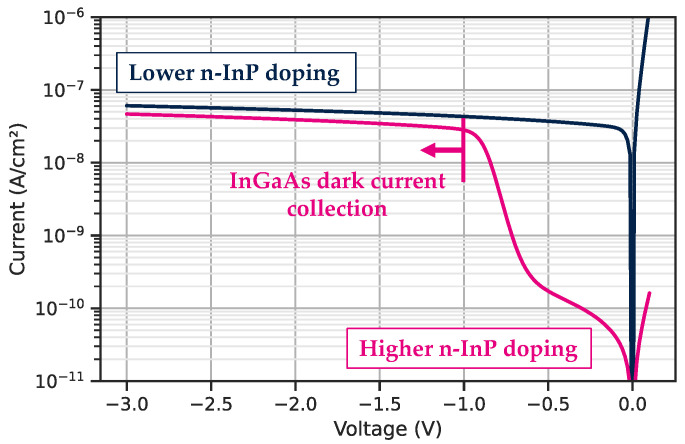

The simulation helps us to separate the contribution of dark current from InP and from the InGaAs layer. The origin of each dark current was verified by changing the carrier lifetime in each material and analysing the evolution on the total dark current. For a non-optimized structure as presented in Figure 4, the simulated dark current shows that carriers collected at low reverse bias (<1 V) are generated in InP (Figure 4a). At higher reverse bias (>1 V), the current of interest is collected in the InGaAs layer (Figure 4b). Our goal was to find a configuration that allows the collection of the InGaAs carriers at low reverse bias.

Figure 4.

Simulated dark current with TCAD Synopsys tools [28]. (a) Shows evolution of the dark current when the InP SRH lifetime is modulated; (b) evolution of the dark current when the InGaAs SRH lifetime is modulated.

The dark blue curve in Figure 5 shows a well-designed structure where the current from InGaAs is collected at quasi null voltage. If the N-InP barrier layer is doped too much (in Figure 5 in pink), it increases the electrostatic barrier and blocks the carrier at low bias.

Figure 5.

Impact of the doping concentration of the InP barrier on the carrier collection.

On the other hand, if the N-InP cap is too thin to minimize the electrostatic barrier, process constraints appear during the P-layer etching process that make it difficult to control uniformity on the wafer.

This theoretical study allows us to find a set of doping concentration and thickness parameters that suppresses the barrier for hole collection. This set of parameters has been used to define the epitaxial stack for photodiode fabrication.

3. Fabrication

The schematic and simplified process of the shallow-mesa type photodiode is represented in Figure 6. All layers are grown on a 3 inches InP substrate (see Figure 6a).

Figure 6.

Simplified and schematic process flow of the shallow mesa-type process. (a) The full stack; (b) the definition of the pixel by etching the P layer and (c) the encapsulation and fabrication of contacts.

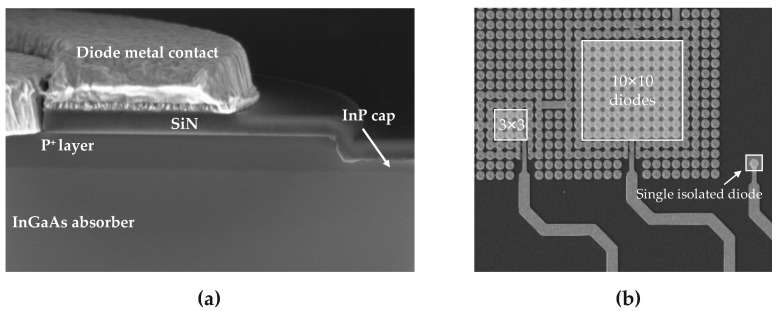

The pixel definition is performed by etching the P-type layer (see Figure 6b and SEM cross-section view Figure 7a). Then, the device is passivated by a dielectric deposition. The final step is the fabrication of both diode and N metal contacts (see Figure 6c).

Figure 7.

SEM views after the whole process. (a) A cross-section of the top stack where the P layer is etched and (b) a top view of the different configuration of the test structures (single in-array diode is not shown on this SEM view).

A specific test structure is designed to emulate a matrix-like environment. Multiple diodes in-array are connected, while two additional rows of diodes at the periphery of this array are independently connected and can be polarized independently. The tested structures shown in Figure 7b could be single isolated or in-array diodes and bundles of three-by-three or ten-by-ten diode bundles in a matrix-like environment.

4. Results

The main figure of merit of a sensor is its signal to noise ratio (SNR). It is defined as the ratio of the useful signal divided by its noise. It must be maximized to reach the best performances. It implies high QE for a high signal and low noise. The noise is ultimately limited by the Schottky noise , with I the total current, i.e., the sum of the photonic and the dark current and q the elementary electric charge. For photodiode fabrication, the dark current is a parasitic current and must be negligeable compared to the photonic current.

In the following part, we first compare two processes on 15 μm large pixels to analyse the impact of the passivation on dark current performances. Then, we fabricate 5 μm pixel pitch photodiodes with the most suitable process and characterize it. Lastly, we present 3 μm pixel pitch photodiodes as a demonstration of pixel pitch reduction.

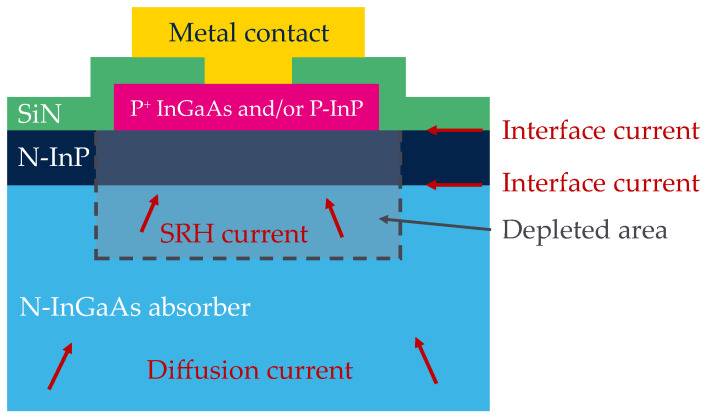

4.1. Dark Current Contributor Investigation

The structure is recalled in Figure 8 with the potential sources of dark current. The main sources considered are the diffusion current and generation–recombination (GR) current in the depletion region as well as interface current between dielectric/InP and InP/InGaAs. The diffusion current and Shockey–Read–Hall (SRH) generation–recombination (GR) current from the InP layer is neglected as the volume is very small and the band gap is approximately twice the band gap of InGaAs (EG, InP = 1.34 eV and EG, InGaAs = 0.74 eV) [31,32,33,34].

Figure 8.

Schematic cross section of the structure with its potential sources of the dark current. Inspired from [32].

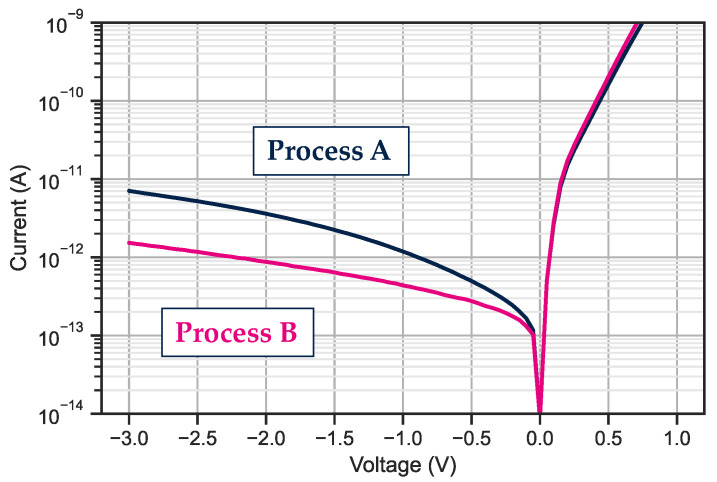

Two processes are compared here to identify the impact of the dielectric for the realization of small pitch photodiode with the lowest dark current possible. The active stack is identical, but the passivation steps are different in terms of dielectric nature. Dark current measurements on 15 μm pixel pitch photodiodes are presented in Figure 9. The evolution is different with the reverse bias. At −0.5 V and at room temperature, the dark current for process A reaches A and for process B, it reaches A.

Figure 9.

Dark current measurement on 15 μm pitch in a matrix like environment. The curve is the median of more than 100 single in-array diodes measured.

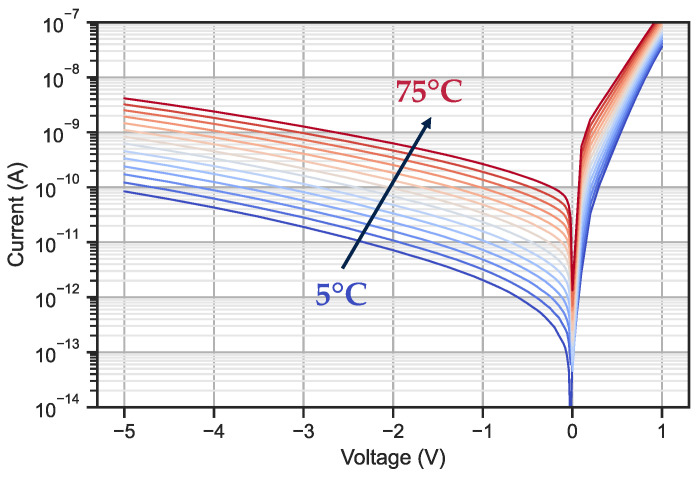

The main contributors to the dark current can be studied by analysing its evolution with temperature. We briefly review the theory of the dark current’s dependence with temperature. The generation–recombination current due to SRH processes in the depleted region follows a specific temperature dependence . If the dark current is limited by the diffusion, the current is proportional to [35]. We measured the dark current for temperatures ranging from 5 °C to 75 °C every 5 °C and an example of our results is presented in Figure 10.

Figure 10.

Dark current measurement of the ten-by-ten diode bundle. This measurement is from process B.

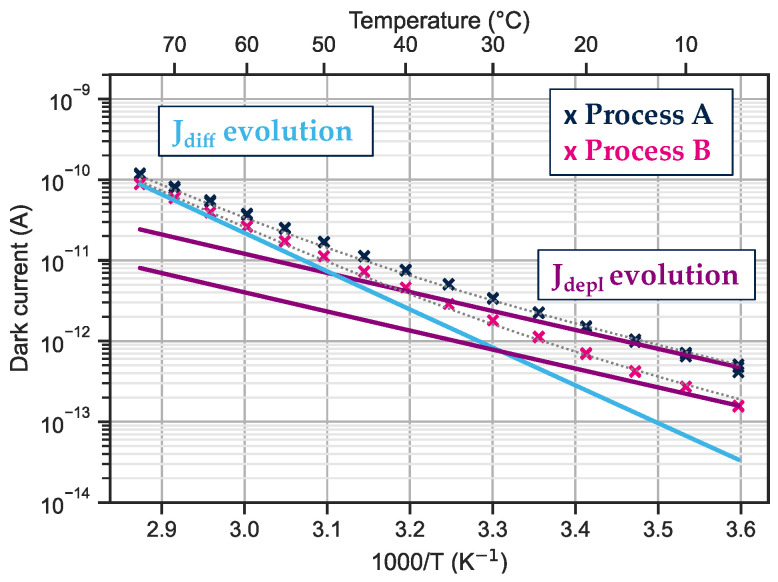

The evolution of the dark current at −0.1 V with temperature is shown in Figure 11. The solid lines show the temperature dependence of the current for diffusion-limited current (light blue) or SRH generation in the depletion current (purple) in the InGaAs absorption layer.

Figure 11.

Evolution of the dark current with temperature at −0.1 V. The solid lines show the theoretical evolution of the current limited by diffusion (light blue line) and by generation recombination (purple line). The temperature measurement is performed on a bundle of ten-by-ten 5 μm pixel pitch diodes.

At room temperature and below, the main dark current contributor is the generation–recombination from the depletion region. For temperatures greater than 50 °C, the dark current is mainly limited by the diffusion phenomenon.

For the two processes studied here, the diffusion contribution is the same, but the current from the depletion region is higher for process A than for process B. As the structures and processes are identical except for the dielectric, this difference in Jdepl indicates that the dielectric has an impact on the dark current.

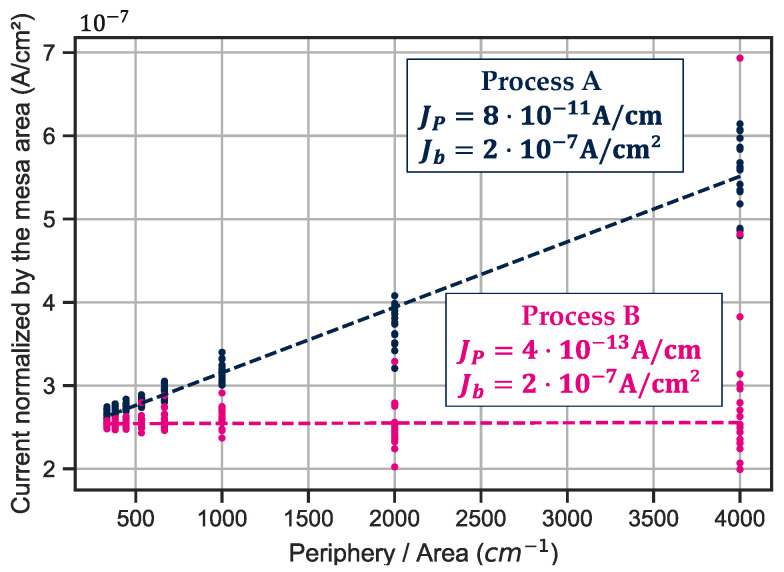

To further investigate the impact of the dielectric on the dark current, the comparison is conducted on diodes of different sizes ranging from 10 μm to 120 μm to characterize contributions from the bulk () and from the periphery () based on the following equation:

| (1) |

is the area of the diode defined by its P-layer diameter and is the perimeter of the diode defined by the perimeter of the P-layer. The measured photodiodes have different P/A ratios, which were used to plot I/A as a function of P/A. By performing a simple linear regression, we were able to distinguish between the bulk and perimeter current densities, and , respectively. In our case, Figure 12 shows the significant different value in for the two cases at −0.5 V. As the diode diameter is reduced, the contribution from the perimeter becomes increasingly important relative to the bulk one.

Figure 12.

Perimetric and bulk contribution to the global dark current from measurements performed on diodes with diameter ranging from 10 to 120 μm.

Here, the bulk contribution is even for the two processes as in both cases; for the perimetric one, in process A, and for process B, . The perimetric contribution is drastically reduced in process B which implies that this process is much more suitable for small pixel pitch fabrication.

The evolution of the dark current with temperature in Figure 11 indicates a different level of Jdepl that limits the dark current at room temperature. However, the P/A study presented Figure 12, identifies a clear difference between the two processes. Even though the perimetric contribution is always lower than the bulk one, process A shows a larger perimetric contribution compared to process B. This difference must be due to different dielectric properties obtained with these two processes.

Specific capacitive characterizations of dielectrics are thus conducted on metal–insulator–semiconductor (MIS) structures. The interface state could be determinant for the dark current performances. Poor interface between dielectric and InP creates traps which generate parasitic carriers. The fixed charges in the dielectric can also have significant impact on the dark current by either creating a depletion region near the interface or accumulating charges and passivating this region.

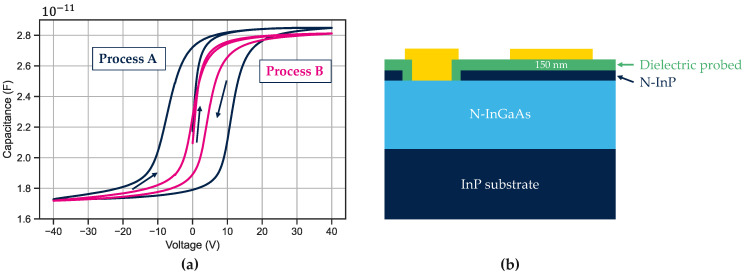

A wide bias ramp of 40 V is applied to the MIS structure (Figure 13b) while capacitance is measured. We use the Maserjian method to extract the flat band voltage (VFB) as explained in [36]. For each branch of the curve, we extract a VFB, and we compare the two extreme values. The delta is very different as we measured 18 V for process A and 4 V for process B (see Figure 13a). The VFB hysteresis is directly proportional to the charge trapped in the dielectric as [37]. Relatively, the passivation of process B traps less charges than process A.

Figure 13.

(a) Capacitance measurement on metal–insulator–semiconductor structure. The measurement starts at 0 V then ramps to +40 V then goes to −40 V and ends at +40 V. (b) A cross section of the MIS structure. The MIS is a 300 μm diameter circle.

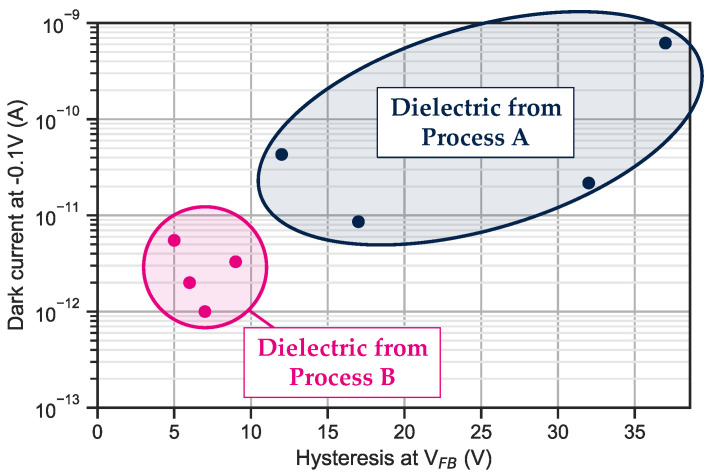

This measurement protocol is conducted on various wafers. This hysteresis of the VFB is plotted as a function of the dark current measured at −0.1 V and at room temperature for ten-by-ten 5 μm pixel pitch bundle. A correlation between VFB hysteresis and Idark is clearly visible in Figure 14.

Figure 14.

Dark current performances compared to the hysteresis measured on several different wafers.

As the dielectric properties could alter the device’s performances, it is thus very important to minimize the trap density at the InP/dielectric interface in the final device. Further investigations would allow quantification of the fixed charge and trap density for both processes A and B.

4.2. Photodiode Performances for 5 μm Pixel Pitch

To reach a pixel pitch as low as 5 μm for the photodiode fabrication, we use the passivation from process B which shows better dark current performances.

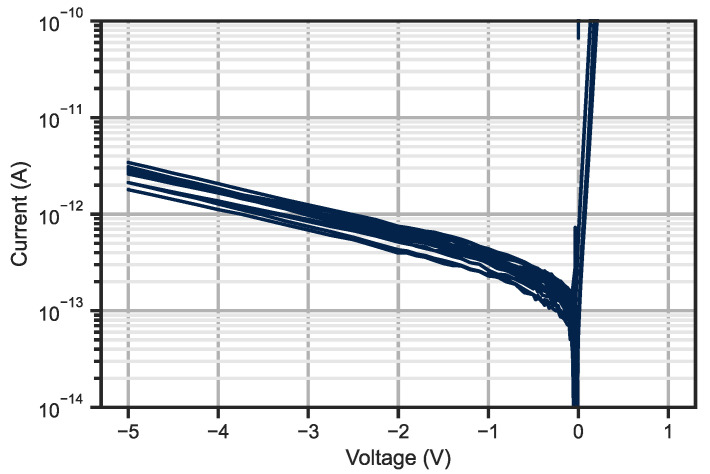

4.2.1. Dark Current

The current noise limit of our set-up is estimated at 50 fA but the dark current from a single small pitch diode is below this value. Thus, we probe bundles of ten-by-ten diodes and the behaviour of one photodiode is extrapolated assuming all diodes behave homogeneously along the bundle.

For dark current measurement, neighbouring photodiodes, as explained in the fabrication section, are biased with the same polarization as the measured diode to mimic an imager environment. Figure 15 shows the measured dark current of more than 10 bundles of photodiodes (i.e., 1000 photodiodes). The median dark current is 121 fA at −0.1 V which corresponds to a dark current density of 5 nA/cm2 at 23 °C. This dark current density is comparable to the state-of-the-art to date [3]. Previous results of the 5 μm pixel pitch photodiode presented in [38] were measured for a bundle of ten-by-ten bundle with unbiased neighbouring diodes.

Figure 15.

Dark current measurement of a ten-by-ten bundle of 5 μm pixel pitch photodiode. The measurements are conducted at 23 °C.

For read-out integrated circuit concerns, we also measure the diode capacitance at −0.1 V and the typical value is 3 fF.

4.2.2. Quantum Efficiency

The QE is an important figure of merit and quantifies the capacity of a photodiode to convert photons into collected charges (see Equation (2)):

| (2) |

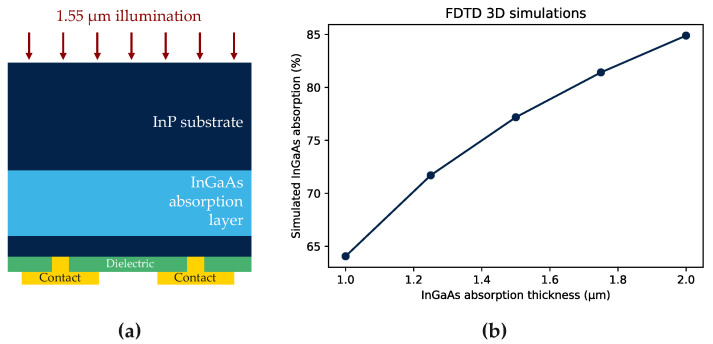

Finite-difference time-domain (FDTD) simulations are conducted with Lumerical software to estimate the theorical QE of the photodiodes. The structure has a 1.5 μm thick InGaAs layer. Based on the literature, the absorption coefficient considered here is [39]. Considering the layout and material configuration, the simulation predicts an absorption as high as 77.2% for a 1.5 μm InGaAs layer (see Figure 16b). This result estimates the internal QE as the reflection between air while InP is not considered in the simulation.

Figure 16.

(a) Schematic test structure for QE measurement; (b) the results of the 3D FDTD simulations conducted with Lumerical to estimate the internal QE of the photodiode.

To measure the QE, we focus all the photons from a 10 μm diameter fibre in a 5 μm pitch ten-by-ten bundle (50 × 50 μm2 square). Photodiodes are illuminated from the back side, i.e., from the substrate, to avoid metallic layers in the optical path. The output power in Table 1 is measured with a power meter directly before entering the test structure. QE is measured for different laser powers to check the stability of the measurements.

Table 1.

Measured QE and extrapolated QE with an anti-reflective coating.

| Output Power (μW) | Photocurrent at −0.1 V (μA) | Raw QE (%) | QE with Ideal Anti-Reflective Coating (%) |

|---|---|---|---|

| 86 | 55.9 | 53.5 | 75.7 |

| 97 | 61.3 | 53.2 | 75.3 |

| 107 | 69.6 | 55.2 | 78.1 |

| 117 | 78.1 | 54.6 | 77.2 |

The photocurrent is measured at −0.1 V for all output powers and the data are gathered in Table 1. The mean raw QE is about 54.1% and is constant with the rising optical power.

However, raw QE is lower than expected (see Figure 16) because photodiodes are measured with the InP substrate which impacts the photon transmission. The reflection between air and InP is 27% at 1.55 μm [40]. It is thus possible to extrapolate the QE considering the substrate removal and an ideal anti-reflective coating. In this case, the QE is estimated to reach 76.6%.

The mean expected QE is very similar to the one estimated by FDTD simulations. The value is consistent considering the experimental uncertainties such as alignment of the fibre in the optical system.

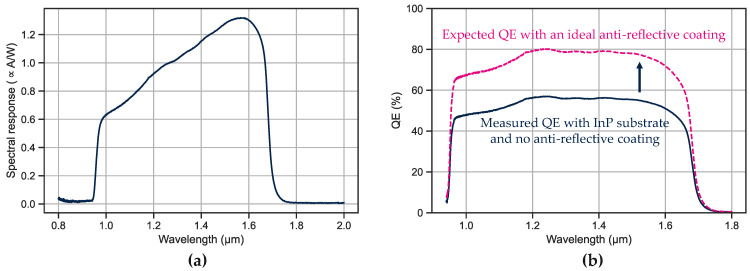

The spectral response of these photodiodes is then measured by Fourier transform infrared (FTIR) spectroscopy. The raw measurement is presented in Figure 17a. The spectral response is null for wavelengths lower than 0.93 μm because of the absorption in the InP substrate ( = 1.34 eV, i.e., = 0.93 μm).

Figure 17.

Measurements on the ten-by-ten bundle of photodiodes. (a) is the raw spectral response measured at −0.1 V and at room temperature; (b), QE in the SWIR range with the InP substrate (dark blue) and without the substrate and considering an ideal anti-reflective coating (dashed pink).

To obtain the QE in the SWIR range, the spectral response is adjusted based on photon energy and a calibrated photodiode. The resulting QE curve in the SWIR range is shown in Figure 17b. It should be noted that the decrease in QE for wavelengths below 1.2 μm may be caused by free carrier absorption due to high N-type doping in the substrate. Further simulations are being conducted to determine the cause of this decrease.

Typical values of the quantum efficiency are gathered in Table 2 for material comparison.

Table 2.

Typical values of quantum efficiency for the main absorption materials in SWIR range.

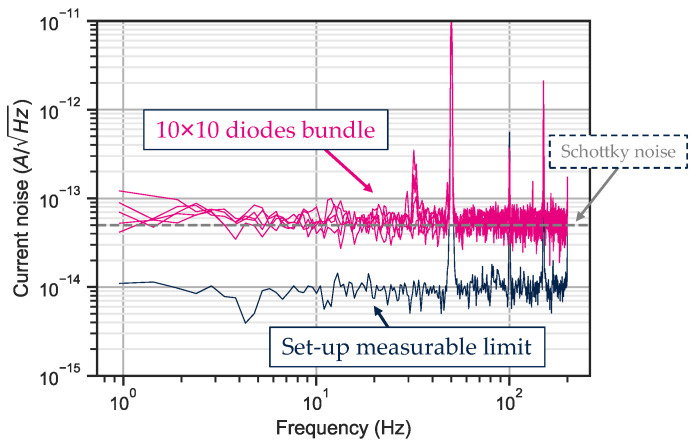

4.2.3. Sensor Spectral Noise under Illumination

Current noise measurements were performed on several bundles under illumination. The test bench performs a time measurement of the current and the result is displayed in Figure 18 as a spectral current noise after applying a Fourier transform function.

Figure 18.

Current noise for a ten-by-ten 5 μm pixel pitch photodiode bundle measured at −0.1 V.

The measured photodiode bundles on Figure 18 are limited by Schottky noise and do not show any 1/f trend noise at low frequency. This result confirms that the electrostatic barrier introduced by the InP cap layer along the collection path does not impact the carrier transport.

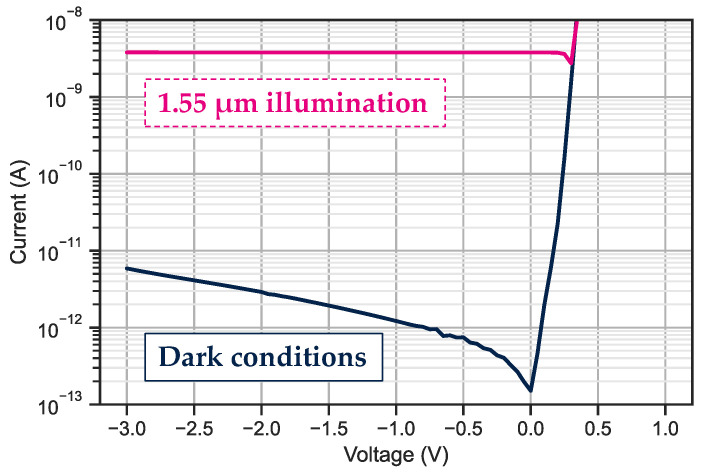

4.3. Towards Smaller Pixel Pitch: 3 μm Pixel Pitch Shallow-Mesa Photodiodes

To demonstrate that this innovative architecture is adapted for the fabrication of pixel pitch below 5 μm, we fabricated 3 μm pitch photodiodes.

The measurements of the dark current and photocurrent on bundles of ten-by-ten 3 μm pixel pitch photodiodes are presented in Figure 19. The collection of the photons is achieved at 0 V, indicating that there is no electrostatic barrier for the carriers generated in the InGaAs layer. The median dark current value is 0.28 pA at −0.1 V, which corresponds to a current density of 30 nA/cm2.

Figure 19.

Median current measurement for bundles of one hundred 3 μm pixel pitch photodiodes under dark and SWIR illumination conditions. The dark blue line represents the dark current and the pink line is the photocurrent under 1.55 μm illumination.

The successful 3 μm pixel pitch photodiode fabrication is demonstrated in Figure 19. The dark current density is higher than for larger pitches but the critical dimensions are close to our lithography tool limit. For such small pitch, actual process variations play an important role in the dark current performances. This architecture is promising for pitch reduction as we are now targeting adaptation of the process with up-to-date large format Si tools. The dark current density is constant with pixel pitch reduction from 15 μm to 5 μm indicating the absence of surface leakage between pixels. The measured dark current increases for 3 μm pixel pitch, probably due to lithography issues leading to electrical crosstalk between neighbouring pixels. In order to decrease the dark current, we are currently adapting the process to a CMOS compatible fab to access a more resolved scanner tool.

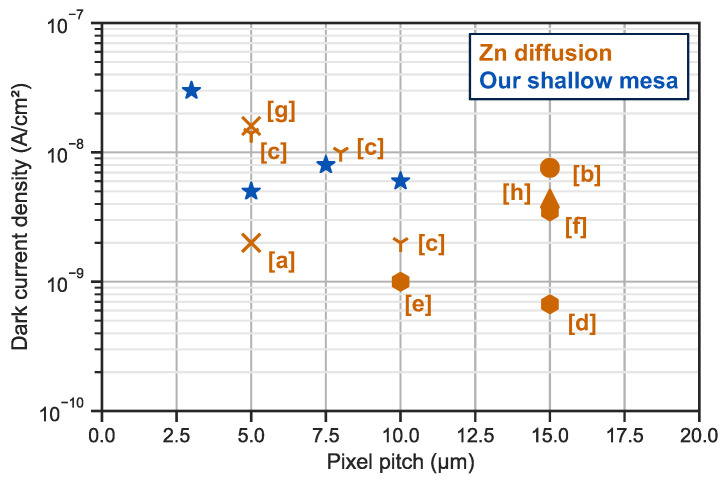

5. Discussion

We benchmarked our architecture with state-of-the-art data of InGaAs photodiodes with small pitch and low dark current (see Figure 20) from the literature.

Our innovative structure shows major improvement compared to the mesa-type architecture published to date [18,26,43].

Zn diffused diodes in orange make up the standard industrial process for InGaAs photodiode fabrication and ref. [3] reports a dark current of 2 nA/cm2 for a 5 μm pixel pitch. From 10 to 5 μm pixel pitch, our diodes in blue show a flat dark current density of about 6 nA/cm2. The impact of charges in the dielectric or traps at the dielectric/cap interface could have a great impact on the dark current and is a clear way to improve the dark current density of these small pitch photodiodes.

The measurement for 3 μm pixel pitch is the first published for such a small pitch, and we obtain a dark current density as low as 30 nA/cm2. This slight increase in dark current density when the pitch reduces from 5 to 3 μm is under investigation and might be due to process imperfections as the critical dimensions are close to the tool limit.

Figure 20.

Comparison of our work in blue versus the state of the art for the fabrication of InGaAs photodiodes. Associated articles and measurement conditions if given: [a] 23 °C @−0.1 V article: [3]—[b] 30 °C @−0.2 V article: [4]—[c] 22 °C @−0.1 V article: [6]—[d] 20 °C article: [5]—[e] 20 °C article: [41]—[f] 30 °C article: [44]—[g] 25 °C article: [45]—[h] 25 °C @−0.3 V article: [15].

As the pixel pitch reduces, crosstalk between pixels becomes a major concern. The typical diffusion length in such devices could reach tens of μm [46]. MFT measurements were performed on 15 and 10 μm pitches leading to suitable values [47]. Further investigations will be required to assess the impact of the crosstalk in our photodiodes with such small pitches.

6. Conclusions

With our innovative shallow mesa-type architecture, we demonstrated InGaAs photodiodes with promising results. We reached dark current as low as 5 nA/cm2 at −0.1 V and at room temperature for 5 μm pixel pitch. The measured external QE is 54% with the InP substrate and no anti-reflective coating. This value is expected to reach 76% with optimized anti-reflective coating and substrate removal. For lower pitch down to 3 μm, we successfully demonstrated the operation of photodiodes, even if the dark current density increases to 30 nA/cm2. Many improvement paths have been identified to reduce it. Future investigations with simulations and capacitive measurements will continue to quantify the impact of the charge in the dielectric and along the interface with the top layer. This promising architecture is now under study to be integrated as an imager with a Si-CMOS tools compatible process and hybridized on a Si-ROIC.

Acknowledgments

The author would like to thank all the CEA-Leti teams for the fabrication, hybridization, and help during the measurements.

Author Contributions

Data analysis and writing J. T.; Conceptualization, review and supervision C.C., J.B., F.R., T.B. and F.B.; Characterizations J.T., T.D.R. and S.G.; Fabrication F.N. and C.J.; Simulations O.S. and G.M.; Investigations J.T., C.C., J.B. and O.G. All authors have read and agreed to the published version of the manuscript.

Informed Consent Statement

Not applicable.

Data Availability Statement

Data are contained in the article.

Conflicts of Interest

The authors declare no conflict of interest.

Funding Statement

This work is part of the IPCEI Microelectronics and Connectivity and was partially supported by the French Public Authorities within the frame of France 2030.

Footnotes

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

References

- 1.Clouet A., Chalak A., Domengie F., Bouhamri Z. SWIR Imaging 2023. Yole; Lyon, France: 2023. pp. 27–28. [Google Scholar]

- 2.Steckel J.S., Pattantyus-Abraham A.G., Josse E., Mazaleyrat E., Rochereau K. High resolution quantum dot global shutter imagers. Dig. Tech. Pap. SID Int. Symp. 2021;52:975–977. doi: 10.1002/sdtp.14852. [DOI] [Google Scholar]

- 3.Manda S., Zaizen Y., Hirano T., Iwamoto H., Matsumoto R., Saito S., Maruyama S., Minari H., Hirano T., Takachi T., et al. High-definition Visible-SWIR InGaAs Image Sensor using Cu-Cu Bonding of III-V to Silicon Wafer; Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM); San Francisco, CA, USA. 7–11 December 2019; pp. 390–393. [DOI] [Google Scholar]

- 4.Rouvié A., Coussement J., Huet O., Truffer J.P., Pozzi M., Oubensaid E.H., Hamard S., Chaffraix V., Costard E. InGaAs focal plane array developments and perspectives; Proceedings of the Infrared Technology and Applications XLI; Baltimore, MD, USA. 20–24 April 2015; p. 945105. [DOI] [Google Scholar]

- 5.Fraenkel R., Berkowicz E., Bikov L., Elishkov R., Giladi A., Hirsh I., Ilan E., Jakobson C., Kondrashov P., Louzon E., et al. Development of low-SWaP and low-noise InGaAs detectors; Proceedings of the Infrared Technology and Applications XLIII; Anaheim, CA, USA. 9–13 April 2017; p. 1017703. [DOI] [Google Scholar]

- 6.Yuan H., Meixell M., Zhang J., Bey P., Kimchi J., Kilmer L.C. Low dark current small pixel large format InGaAs 2D photodetector array development at Teledyne Judson Technologies; Proceedings of the Infrared Technology and Applications XXXVIII; Baltimore, MD, USA. 23–27 April 2012; pp. 105–108. [DOI] [Google Scholar]

- 7.Rouse C., Zeller J.W., Efstathiadis H., Haldar P., Lewis J.S., Dhar N.K., Wijewarnasuriya P., Puri Y.R., Sood A.K. Development of Low Dark Current SiGe Near-Infrared PIN Photodetectors on 300 mm Silicon Wafers. Opt. Photonics J. 2016;6:61–68. doi: 10.4236/opj.2016.65009. [DOI] [Google Scholar]

- 8.Durlin Q., Aliane A., André L., Kaya H., Le Cocq M., Goudon V., Vialle C., Veillerot M., Hartmann J.M. Fabrication and characterisation of the PiN Ge photodiode with poly-crystalline Si:P as n-type region. Aula Abierta. 2023;31:e144550. doi: 10.17811/rifie.45.1.2017.33-40. [DOI] [Google Scholar]

- 9.Farooq U., Min-Dianey K.A.A., Rajagopalan P., Malik M., Kongnine D.M., Choi J.R., Pham P.V. Photodetection Tuning with High Absorptivity Using Stacked 2D Heterostructure Films. Nanomaterials. 2022;12:712. doi: 10.3390/nano12040712. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 10.Koppens F.H.L., Mueller T., Avouris P., Ferrari A.C., Vitiello M.S., Polini M. Photodetectors based on graphene, other two-dimensional materials and hybrid systems. Nat. Nanotechnol. 2014;9:780–793. doi: 10.1038/nnano.2014.215. [DOI] [PubMed] [Google Scholar]

- 11.Paul S., Roy J.B., Basu P.K. Empirical expressions for the alloy composition and temperature dependence of the band gap and intrinsic carrier density in GaxIn 1-xAs. J. Appl. Phys. 1991;69:827–829. doi: 10.1063/1.348919. [DOI] [Google Scholar]

- 12.Laukkanen P., Punkkinen M.P.J., Kuzmin M., Kokko K., Lång J., Wallace R.M. Passivation of III-V surfaces with crystalline oxidation. Appl. Phys. Rev. 2021;8:23. doi: 10.1063/1.5126629. [DOI] [Google Scholar]

- 13.Zhou L., Bo B., Yan X., Wang C., Chi Y., Yang X. Brief review of surface passivation on III-V semiconductor. Crystals. 2018;8:226. doi: 10.3390/cryst8050226. [DOI] [Google Scholar]

- 14.Hang Z., Shen H., Pollak F. Temperature dependance of the E0 and E0 + △0 gaps of InP up to 600 °C. Solid State Commun. 1990;73:15–18. doi: 10.1016/0038-1098(90)90005-V. [DOI] [Google Scholar]

- 15.Dolas M.H., Atesal O., Caliskan M.D., Bek A., Ozbay E. Low dark current diffusion limited planar type InGaAs photodetectors; Proceedings of the Infrared Sensors, Devices, and Applications IX; San Diego, CA, USA. 11–15 August 2019; p. 10. [DOI] [Google Scholar]

- 16.Chen C.L., Yost D.R., Knecht J.M., Chapman D.C., Oakley D.C., Mahoney L.J., Donnelly J.P., Soares A.M., Suntharalingam V., Berger R., et al. Wafer-scale 3D integration of InGaAs image sensors with Si readout circuits; Proceedings of the 2009 IEEE International Conference on 3D System Integration; San Francisco, CA, USA. 28–30 September 2009; pp. 1–4. [DOI] [Google Scholar]

- 17.Tillement J., Cervera C., Baylet J., Gravrand O., Lalauze Q., Jany C., Di Rito T., Saxod O., Moussy N., Baron T., et al. Fabrication of 3 μm Pixel Pitch InGaAs Photodiodes Using Be Implantation Doping for SWIR Sensing. Solid State Devices Materials. 2022. [(accessed on 10 November 2023)]. Available online: https://confit.atlas.jp/guide/organizer/ssdm/events?lang=en.

- 18.Chen C.L., Yost D.R., Knecht J.M., Wey J., Chapman D.C., Oakley D.C., Soares A.M., Mahoney L.J., Donnelly J.P., Chen C.K., et al. Wafer-scale 3D integration of InGaAs photodiode arrays with Si readout circuits by oxide bonding and through-oxide vias. Microelectron. Eng. 2011;88:131–134. doi: 10.1016/j.mee.2010.09.020. [DOI] [Google Scholar]

- 19.Dolas M.H., Circir K., Kocaman S. Optimization of mesa structured InGaAs based photodiode arrays; Proceedings of the Image Sensing Technologies: Materials, Devices, Systems, and Applications IV; Anaheim, CA, USA. 9–13 April 2017; p. 102090K. [DOI] [Google Scholar]

- 20.Djedidi A., Rouvie A., Reverchon J., Pires M., Chevalier N., Mariolle D. Investigation of the Influence of Zn-diffusion profile on the electrical properties of InGaAs/InP photodiodes; Proceedings of the 2012 International Conference on Indium Phosphide and Related Materials; Santa Barbara, CA, USA. 27–30 August 2012; pp. 110–112. [DOI] [Google Scholar]

- 21.Akano U.G., Mitchell I.V., Shepherd F.R., Miner C.J. Ion implantation damage of InP and InGaAs. Nucl. Inst. Methods Phys. Res. B. 1995;106:308–312. doi: 10.1016/0168-583X(95)00724-5. [DOI] [Google Scholar]

- 22.Sadana D.K. Mechanisms of amorphization and recrystallization in ion implanted III-V compound semiconductors. Nucl. Inst. Methods Phys. Res. B. 1985;7–8:375–386. doi: 10.1016/0168-583X(85)90585-3. [DOI] [Google Scholar]

- 23.Tandon J.L., Madok J.H., Leybovich I.S., Bai G., Nicolet M.-A. Sequential nature of damage annealing and activation in implanted GaAs. Appl. Phys. Lett. 1989;54:448–450. doi: 10.1063/1.100948. [DOI] [Google Scholar]

- 24.Ronning C., Dalmer M., Uhrmacher M., Restle M., Vetter U., Ziegeler L., Hofsäss H., Gehrke T., Järrendahl K., Davis R.F. Ion implanted dopants in GaN and AIN: Lattice sites, annealing behavior, and defect recovery. J. Appl. Phys. 2000;87:2149–2157. doi: 10.1063/1.372154. [DOI] [Google Scholar]

- 25.Pearton S.J. Ion implantation for isolation of III-V semiconductors. Mater. Sci. Rep. 1990;4:313–363. doi: 10.1016/S0920-2307(05)80001-5. [DOI] [Google Scholar]

- 26.Klem J.F., Kim J.K., Cich M.J., Keeler G.A., Hawkins S.D., Fortune T.R. Mesa-isolated InGaAs photodetectors with low dark current. Appl. Phys. Lett. 2009;95:2–5. doi: 10.1063/1.3184807. [DOI] [Google Scholar]

- 27.Lau J.H. Recent Advances and Trends in Cu-Cu Hybrid Bonding. IEEE Trans. Compon. Packag. Manuf. Technol. 2023;13:399–425. doi: 10.1109/TCPMT.2023.3265529. [DOI] [Google Scholar]

- 28.Synopsys . SentaurusTM Device User Guide. Synopsys, Inc.; Mountain View, CA, USA: 2019. P-2019.03. [Google Scholar]

- 29.Ahrenkiel R.K., Ellingson R., Johnston S., Wanlass M. Recombination lifetime of In0.53Ga0.47As as a function of doping density. Appl. Phys. Lett. 1998;72:3470–3472. doi: 10.1063/1.121669. [DOI] [Google Scholar]

- 30.Vignaud D., Lampin J.F., Lefebvre E., Zaknoune M., Mollot F. Electron lifetime of heavily Be-doped In0.53Ga0.47As as a function of growth temperature and doping density. Appl. Phys. Lett. 2002;80:4151–4153. doi: 10.1063/1.1483126. [DOI] [Google Scholar]

- 31.Trezza J.A., Masaun N., Ettenberg M. Analytic modeling and explanation of ultra-low noise in dense SWIR detector arrays; Proceedings of the Infrared Technology and Applications XXXVII; Orlando, FL, USA. 25–29 April 2011; p. 80121Y. [DOI] [Google Scholar]

- 32.Boisvert J., Isshiki T., Sudharsanan R., Yuan P., McDonald P. Performance of very low dark current SWIR PIN arrays; Proceedings of the Infrared Technology and Applications XXXIV; Orlando, FL, USA. 16–20 March 2008; p. 69400L. [Google Scholar]

- 33.Yuan P., Chang J., Boisvert J., Karam N. Low-dark current 1024 × 1280 InGaAs PIN arrays; Proceedings of the Infrared Technology and Applications XL; Baltimore, MD, USA. 5–9 May 2014; [DOI] [Google Scholar]

- 34.DeWames R.E., Schuster J. Performance and limitations of NIR and extended wavelength eSWIR InP/InGaAs image sensors; Proceedings of the Quantum Sensing and Nano Electronics and Photonics XVII; San Francisco, CA, USA. 1–6 February 2020; p. 17. [DOI] [Google Scholar]

- 35.Sze S.M., Kwok K.N. Physics of Semiconductor Devices. Volume 10. Springer; Berlin/Heidelberg, Germany: 2006. [Google Scholar]

- 36.Maserjian J., Petersson G., Svensson C. Saturation capacitance of thin oxide MOS structures and the effective surface density of states of silicon. Solid-State Electron. 1974;17:335–339. doi: 10.1016/0038-1101(74)90125-7. [DOI] [Google Scholar]

- 37.Schroder D. Semiconductor Material and Device Characterization. J. Wiley & Sons; Hoboken, NJ, USA: 2006. [Google Scholar]

- 38.Tillement J., Cervera C., Baylet J., Jany C., Nardellib F., Lalauze Q., Di Rito T., Paquet R., Saxod O., Moussy N., et al. Fabrication of Small Pitch InGaAs Photodiodes Using In-Situ Doping and Shallow Mesa Architecture for SWIR Sensing. 2023. [(accessed on 10 November 2023)]. Available online: https://imagesensors.org/Past%20Workshops/2023%20Workshop/2023%20Papers/R63.pdf.

- 39.Verdun M. Photodétecteurs InGaAs Nanostructurés pour l’Imagerie Infrarouge. Université Paris Saclay (COmUE); Paris, France: 2016. [Google Scholar]

- 40.Pettit G.D., Turner W.J. Refractive index of InP. J. Appl. Phys. 1965;36:2081. doi: 10.1063/1.1714410. [DOI] [Google Scholar]

- 41.Fraenkel R., Berkowicz E., Bykov L., Dobromislin R., Elishkov R., Giladi A., Grimberg I., Hirsh I., Ilan E., Jacobson C., et al. High definition 10 μm pitch InGaAs detector with asynchronous laser pulse detection mode; Proceedings of the Infrared Technology and Applications XLII; Baltimore, MD, USA. 17–21 April 2016; p. 981903. [Google Scholar]

- 42.Steckel J.S., Josse E., Pattantyus-Abraham A.G., Bidaud M., Mortini B., Bilgen H., Arnaud O., Allegret-Maret S., Saguin F., Mazet L., et al. 1.62 μm Global Shutter Quantum Dot Image Sensor Optimized for Near and Shortwave Infrared; Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM); San Francisco, CA, USA. 11–16 December 2021; pp. 518–521. [Google Scholar]

- 43.Circir K., Dolas M.H., Kocaman S. Optimization of in-device depleted passivation layer for InGaAs photodetectors. Infrared Phys. Technol. 2019;97:360–364. doi: 10.1016/j.infrared.2018.12.024. [DOI] [Google Scholar]

- 44.Shkedy L., Koifman A., Giladi A., Tuito A., Ilan E., Grimberg I., Bykov L., Elishkov R., Fraenkel R., Vasserman S. Multi-function InGaAs Detector for SWIR Imaging. Proc. SPIE. 2014;2930312 [Google Scholar]

- 45.Lalucaa V., Calvinhac L., Virmontois C., Member S. Dark Current Random Telegraph Signal in visible and SWIR Direct Cu-Cu bonding InGaAs Image Sensor; Proceedings of the 2021 21th European Conference on Radiation and Its Effects on Components and Systems (RADECS); Vienna, Austria. 13–17 September 2021; pp. 1–4. [DOI] [Google Scholar]

- 46.Walker A.W., Pitts O.J., Storey C., Waldron P., Flueraru C. Minority carrier diffusion in InGaAs/InP P–i–N heterojunctions for photodetector arrays. Opt. Quantum Electron. 2020;52:96. doi: 10.1007/s11082-020-2192-2. [DOI] [Google Scholar]

- 47.Colin T., Aufranc S., Fantini J., Bonvalot C., Grille R., Dagher G., Renaudat-Saint-Jean M., Coussement J., Péré-Laperne N. Small pixel pitch developments in the short wave infrared range at LYNRED; Proceedings of the Infrared Technology and Applications XLIX; Orlando, FL, USA. 30 April–5 May 2023; p. 1. [DOI] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Data Availability Statement

Data are contained in the article.