Abstract

Due to its advantages, the asymmetrical dual three-phase induction motor drive is a strong choice in high-power applications. However, the common-mode voltage produced by the voltage source inverters affects the winding insulation and damages the bearings. Common-mode voltage is also responsible for electromagnetic interference and leakage currents. This paper, therefore, analyses the common-mode voltage produced by the inverter supplying a dual three-phase induction motor drive and proposes a novel modified space vector decomposition-based Space Vector Pulse Width Modulation (SVPWM) technique for common mode reduction. The vector space decomposition-based space vector modulation technique offers excellent flexibility as it reduces the common-mode voltage (CMV) by exploiting the additional degree of freedom in a dual three-phase system. The common-mode voltage (CMV) can be reduced to one-sixth of the DC link voltage compared to the highest CMV, i.e. half of the DC-link voltage produced in conventional space vector modulation. The proposed method is also validated experimentally to demonstrate the effectiveness of the proposed scheme in terms of the amplitude of CMV, pulsations, and total harmonic distortion(THD) in current.

Subject terms: Electrical and electronic engineering, Energy infrastructure

Introduction

Dual three-phase adjustable speed drives are becoming popular in recent times due to various advantages in comparison with conventional three-phase drives1. Higher reliability, reduced switch rating, fault tolerance capability2, and reduced torque ripple3 etc. are some of the advantages offered by the dual three-phase machine. Voltage source inverters are extensively used for variable speed drives involving dual three-phase machines; however, the issues of CMV do exist in multi-phase machines4,5 for industrial applications. CMV produces common-mode currents that lead to bearing damage6,7, results in electromagnetic interference8, and also injures the winding insulation. CMV produces common-mode currents that lead to bearing damage due to high dv/dt at the motor terminals; common-mode currents in such circumstances include electrostatic discharge machining (EDM) currents, circulating currents, and rotor ground currents. The two solutions now available for three-phase systems to solve the above issue are (i) hardware and (ii) software solutions. Hardware solutions include (a) common-mode chokes, (b) passive and active filters, and (c) various inverter topologies. These techniques can partially solve the CMV issue, but they can increase size, weight, expense, and complexity. On the other hand, software solutions that modify switching signals or modulation techniques tend to be more effective. Building software solutions is much simpler since highly effective Digital Signal Processors (DSPs) and Field Programmable Gate Arrays (FPGAs) controllers are readily available..

The concept behind CMV reduction is that active voltage vectors can eliminate zero voltage vectors in a three-phase machine fed by either a two-level or multi-level inverter9–11. Common-mode voltage reduction using the active zero state for dual three-phase induction motor drive is mentioned in12, where simulation results are presented showing that the common-mode voltage can be reduced by extending the active zero state SVPWM in three-phase inverters to six-phase inverters. In the case of a five-phase induction motor drive, the open-end winding setup for CMV reduction is a straightforward extension of the three-phase idea13. In the case of dual three-phase inverters, CMV reduction approaches that are based on carrier-based PWM (CPWM) are utilized in order to lower the CMV; nevertheless, this results in a higher level of current distortion. A generalized strategy for the reduction of CMV is based on reference order and is applicable to an odd number of phases14,15. The reduction of CMV for five-phase induction motor drives employing SVPWM in the overmodulation region is mentioned in Refs.16,17. Performance of the six-phase induction machine with active voltage vector-based direct torque control to reduce the common-mode voltage is found in Ref.18. The vector space decomposition (VSD) method for the dual three-phase machine is introduced in Ref.19. This method offers a great deal of simplicity in terms of ease of controlling the machine, reducing the number of sensors used for the closed-loop control. The additional degree of freedom available with the VSD-based space vector modulation is being exploited here to minimize the CMV in the case of a dual three-phase induction machine (DTIM). One of the significant advantages of the VSD method is that the control techniques can be implemented quickly. The six-phase voltages, when transformed to three mutually perpendicular surfaces, the components in the plane are responsible for electromagnetic energy conversion. The components on subspace contribute to harmonics in the system. The components on subspace contain zero sequence components. Therefore, the reference vector is synthesized so that the components in subspace are kept minimal.

The dual three-phase induction machine has isolated neutrals. So, the components of currents in subspace remain zero. So it has one set of currents like its three-phase counterparts, which is the main advantage of the VSD-based approach. Therefore, an attempt is made in this article to develop a modulation technique for reducing the common-mode voltage using the VSD approach.

The DTIM fed from two three-phase inverters is studied first with conventional SVPWM and implemented using the VSD approach. Then a pair of active voltage vectors are chosen on the -plane of the VSD approach to replace the null vector. A comparison is made between the two approaches to verify the merits of the proposed approach over the conventional method20–22. The highest CMV-producing switching states are excluded in the proposed approach. In a two-level three-phase inverter, there are two such states, namely and , which have a CMV of . Similarly, in a six-phase inverter, a pair of null vectors exists, which are replaced by a pair of active vectors depending on the position of the desired space vector on the dq-plane. Following are the contributions of this paper.

Vector space decomposition theory based SVPWM technique is developed for CMV reduction in inverter-fed dual three-phase induction machine.

The proposed work addresses the amplitude and pulsation in the common-mode voltage and reduces both.

The switching states are selected so that it results in minimum current components in the plane. Thus the losses are kept to a minimum.

This paper is structured into four sections. Section "Methodology" includes the VSD-based conventional space vector modulation technique and the proposed space vector modulation technique for the dual three-phase machine. Section "Result and discussion" consists of simulation and hardware implementation for the proposed scheme, and Sect. "Conclusion" presents the concluding remark. The modeling of the dual three-phase machine modeling using the vector space decomposition technique and is mentioned in Appendix.

Methodology

The vector space decomposition method is a powerful tool for the dual three-phase machine. In this approach, the six-dimensional space is converted into three orthogonal subspaces (), and 23. The components on the () plane are corresponding to the electromechanical energy conversion. The other four components are not involved in the energy conversion process. But at the same time, the components on subspace produce harmonics, and those on subspace produce the zero sequence currents.

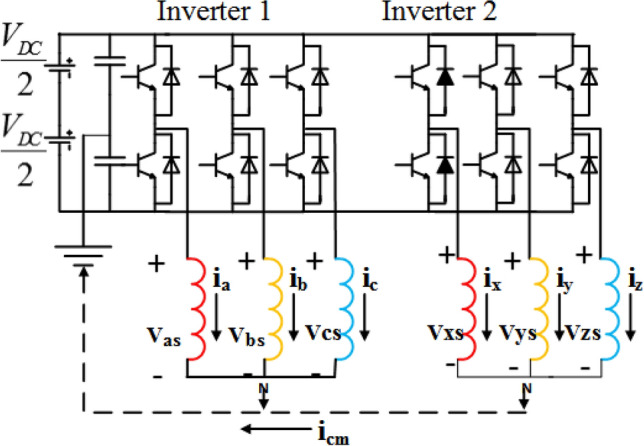

The six-phase inverter (Fig. 1) can be considered as two three-phase inverters sharing a common DC link. Subsequently, the phase voltages can be expressed as:

| 1 |

where s refers to stator and S refers to switching vector of the corresponding inverter leg

Figure 1.

Dual three-phase induction motor drive fed from two-Level inverter with single DC link.

By using the vector space decomposition method, the voltage vectors in (), , and plane can be obtained easily. The objective of the space vector PWM technique is to apply the component of the stator voltage vector duly produced by the control system. The average voltage vectors produced in the other two planes should be kept at a minimum to reduce large harmonic currents.

The voltage vectors in each sector and their timings can be decided by solving a few equations. This involves two equations each for obtaining the voltage vector in reference frame (I), zero voltage vector in and plane (II), and one equation for defining the time period (III).

As neutral points of the machine are isolated, there is no current in the plane. So to implement any SVPWM technique, five equations are to be solved. These equations are:

| 2 |

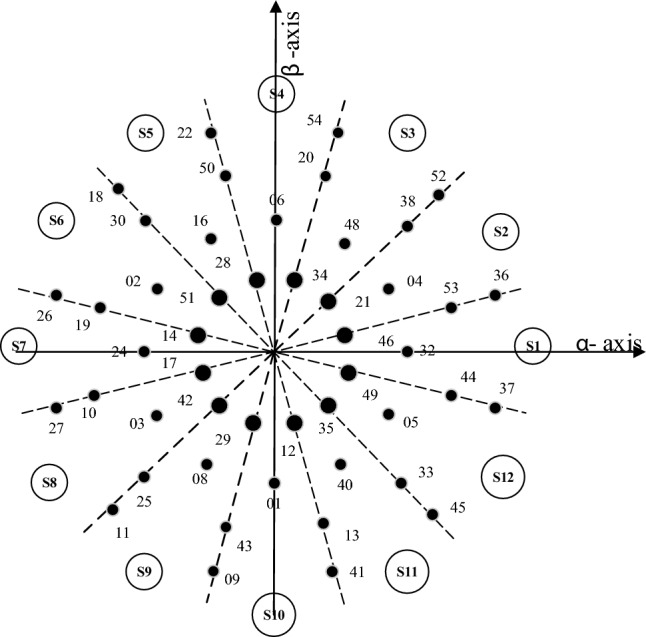

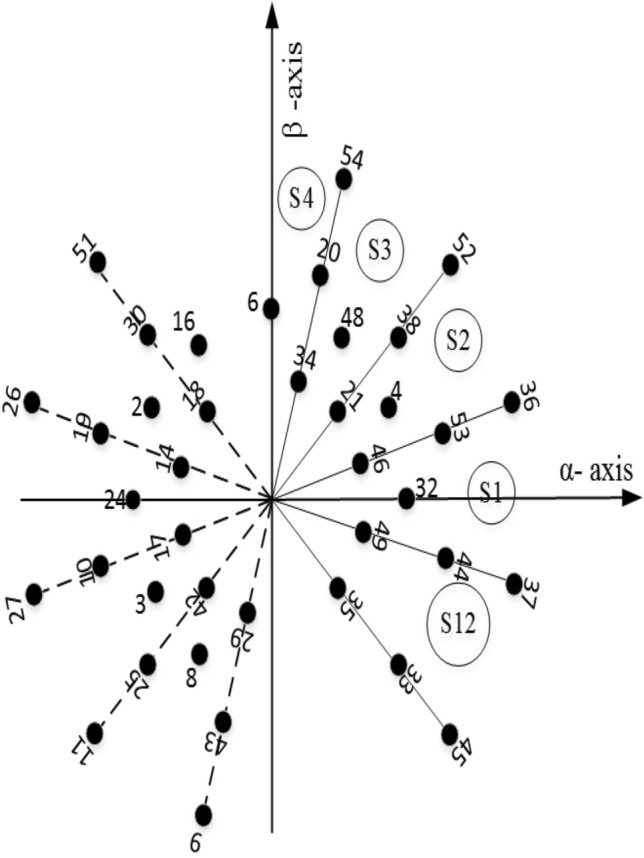

where n denotes the number of voltage vectors used to synthesize the reference in any sector. and are the projection of voltage vector on the x-axis and is the dwell time of a particular voltage vector corresponding to the switching sequence. The reference voltage vector is generated in a 12 sector plane (Fig. 2) as discussed below:

Figure 2.

12-sector space vector diagram representing Voltage vectors in plane.

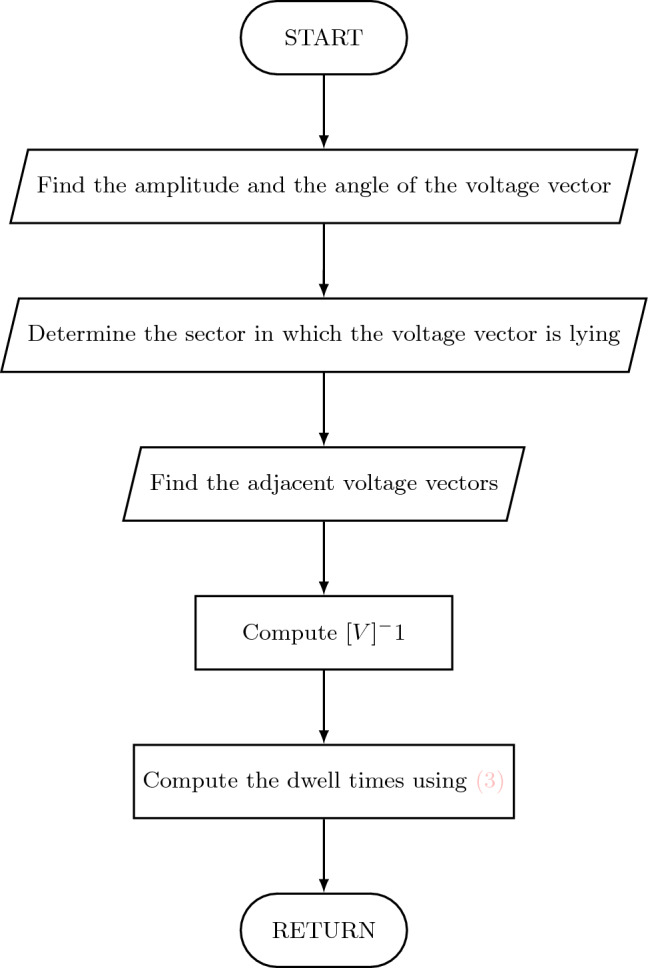

The steps for finding the dwell times in each sector involve some calculation as given in a flow chart in Fig. 3. The matrix V comprises of the components of the voltage vectors in , plane along with the dwell times. Equation (2) can written as:

| 3 |

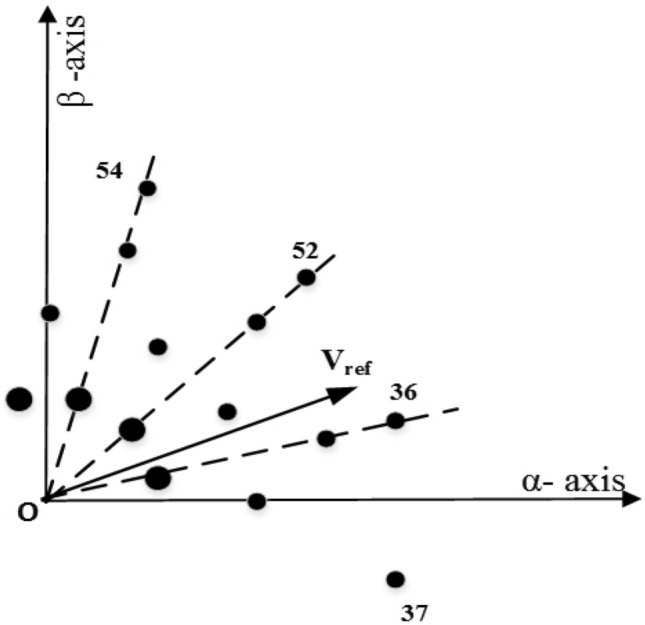

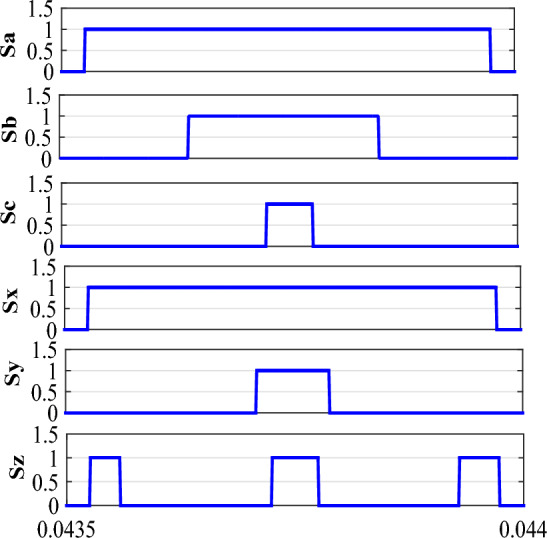

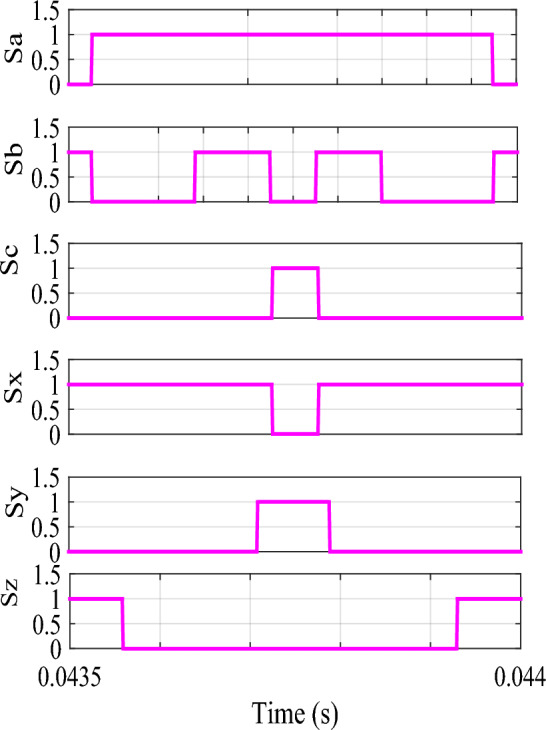

The reference voltage vector is synthesized using the five voltage vectors namely 36, 37, 52, 54, 0 as mentioned below when in sector-I (Fig. 4). Similar to the conventional SVPWM, to have symmetry, the switching sequence is V(0), V(37), V(36), V(52), V(54), V(52), V(36), V(37), V(0). The switching signals are shown in Fig. 5.

Figure 3.

Flow chart for dwell time calculation.

Figure 4.

Voltage vectors in sector-I.

Figure 5.

Switching signals in sector-II.

Proposed SVPWM for common-mode voltage reduction

Common mode voltage (CMV) is defined as the potential of the load neutral to earth (in this case, the DC bus midpoint). CMV in the case of an n-phase voltage source inverter, is given by Eq. (4) and the CMV produced by the two three-phase inverter is given by Eqs. (5) and (6).

| 4 |

| 5 |

Similarly, for the second inverter, the CMV produced is;

| 6 |

where S refers to the switching vector of the respective invertlegs

The vector space decomposition method offers great flexibility in terms of selecting a switching scheme that reduces the CMV. As seen from Fig. 6, in sector-I, the switching sequence with reduced CMV may be selected as V(45), V(37), V(36),V(52) and a virtual zero vector comprising of v(49), v(14). Similarly, in other sectors, the virtual zero voltage vectors used are mentioned below.

Figure 6.

Voltage vectors in sector-I for RCMV.

The virtual vectors chosen for CMV reduction are not limited to the listed ones only. For example, in sector-I, the virtual zero vector could be any one of the following:

.

The voltage ripple will be minimal if the voltage vectors selected for producing the desired fundamental voltage are close to the reference voltage. The option to choose the virtual voltage vectors in sector-I is shown in Fig. 6. Of course, an optimal switching pattern can be obtained in terms of minimum THD and Switching losses. Based on the above fact, in sector-I is used here for this purpose. The switching signals for the proposed method are shown in Sector-II (Fig. 7). Vectors used in each sector for reduced CMV are mentioned in Table 1.

Figure 7.

Switching signals in sector-II for RCMV.

Table 1.

Table for switching vector selection.

| Sectors | Voltage vectors used without CMV reduction | Voltage vectors used with CMV reduction |

|---|---|---|

| I | V(0),V(45),V(37), V(36),V(52) | V(49),V(45),V(37), V(36),V(52),V(14) |

| II | V(0),V(37),V(36), V(52),V(54) | V(21),V(37),V(36), V(52),V(54),V(42) |

| III | V(0),V(36),V(52), V(54),V(22) | V(21),V(36),V(52), V(54),V(22),V(42) |

| IV | V(0),V(52),V(54), V(22),V(18) | V(28),V(52),V(54), V(22),V(18),V(35) |

| V | V(0),V(54),V(22), V(18),V(26) | V(28),V(54),V(22), V(18),V(26),V(35) |

| VI | V(0),V(22),V(18), V(26),V(27) | V(14),V(22),V(18), V(26),V(27),V(49) |

| VII | V(0),V(18),V(26), V(27),V(11) | V(14),V(18),V(26), V(27),V(11),V(49) |

| VIII | V(0),V(26),V(27), V(11),V(9) | V(42),V(26),V(27), V(11),V(9),V(21) |

| IX | V(0),V(27),V(11), V(9),V(41) | V(42),V(27),V(11), V(9),V(41),V(21) |

| X | V(0),V(11),V(9), V(41),V(45) | V(35),V(11),V(9), V(41),V(45),V(28) |

| XI | V(0),V(9),V(41), V(45),V(37) | V(35),V(9),V(41), V(45),V(37),V(28) |

| XII | V(0),V(41),V(45), V(37),V(36) | V(49),V(41),V(45), V(37),V(36),V(14) |

It is a well-known fact that, in the case of two-level three-phase VSI, CMV produced is 24. The dual three-phase induction machine though a six-phase machine, has two isolated neutral. The advantage of such a configuration is well documented. So CMV produced, in this case, is also . By using the above-proposed algorithm, CMV is limited to as the machine has two isolated neutrals. CMV produced by the two-level voltage source inverter is given in Table 2.

Table 2.

CMV and phase voltage in different states.

| State | ||||

|---|---|---|---|---|

Performance of the proposed SVPWM technique

Number of switching and vector sequence

The proposed reduced common-mode voltage space vector modulation technique (RCMV-SVPWM) is based on the vector space decomposition method. The proposed method is also valid for any number of phases; and, therefore, helps in reducing the common-mode voltage in VSI-fed dual three-phase drives. The switching frequency in the case of RCMV-SVPWM does not remain the same as in the case of conventional SVPWM. But as the switching frequency used is low, particularly for the dual three-phase drives, the increase in switching frequency will not affect much in terms of the switching loss.

CMV elimination

The new modulation technique reduces the CMV to one-sixth of the DC link voltage from half of the DC link voltage as found in the case of conventional SVPWM. The switching vectors chosen by the new method result in a lower CMV; nevertheless, when dead times are considered, pulses in the neutral voltage with an amplitude of are produced during some of the vector transitions. This undesirable effect has been reported in Refs.25 and26. Even then, the CMV produced by the RCMV-SVPWM is much less than that produced by the conventional SVPWM.

Result and discussion

The performance of the proposed RCMV-SVPWM scheme is presented for a six-phase asymmetrical induction motor as load fed from a two-level voltage source inverter. The machine parameters are given in Table 3.

Table 3.

Machine parameter.

| Stator resistance () | |

| Rotor resistance () | |

| Stator leakage inductance () | 0.015H |

| Rotor leakage inductance () | 0.015H |

| Magnetizing inductance () | 0.119H |

| No. of pole pairs (p) | 3 |

| Moment of inertia(J) |

Simulation result discussion

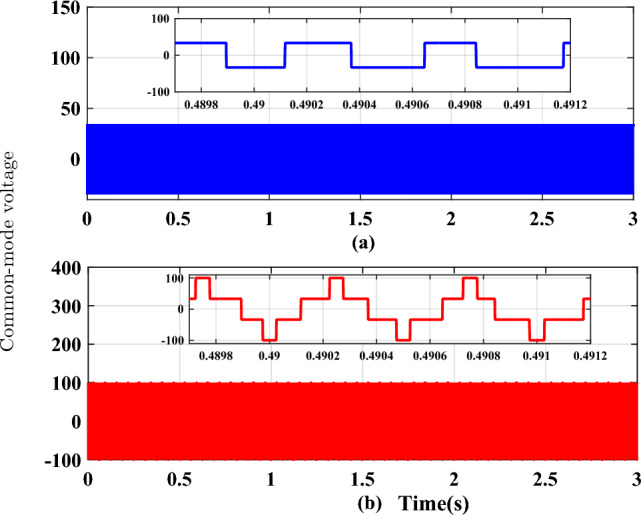

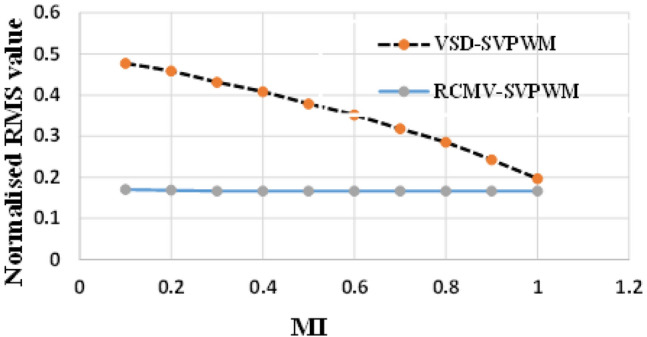

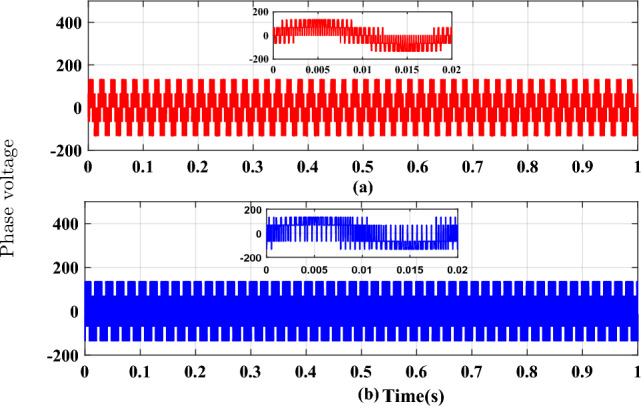

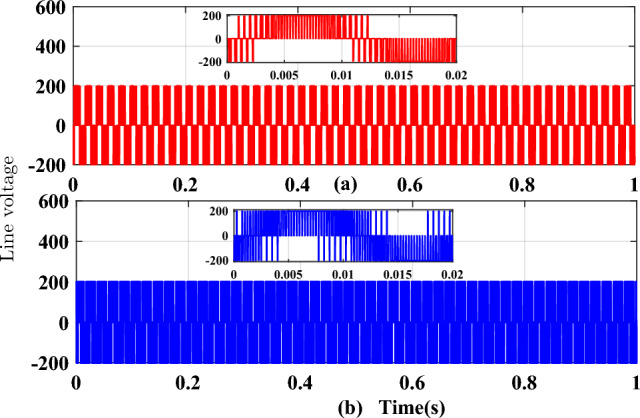

The proposed methodology is simulated on the Matlab platform. A DC link voltage of 200V and a switching frequency of 2kHz is used for the simulation purpose. From the simulation result, it can be observed that the peak amplitude of common-mode voltage generated with the proposed modulation scheme is 33.33 V (Fig. 8a), where the common-mode voltage produced in the conventional SVPWM scheme is 100V (Fig. 8b). The number of pulsations in the common-mode voltage is 6 in the proposed method. The pulsation in the common-mode voltage is 18 in the case of conventional SVPWM, as shown in the zoomed window (8) for each case. Additionally, the RMS value of the common-mode voltage is also reduced by a factor of 1/3. The combined effect results in a decrease of the current due to common-mode voltages by many folds, and hence improve the life of machine insulation and bearing, etc. Figure 9 shows the CMV (RMS value) variation to modulation index for the two cases. It is observed that there is no significant change in the RMS value of common-mode voltage in the proposed scheme, whereas, in a conventional modulation scheme, the variation is from 0.5 pu to 0.2 pu. The output phase voltage waveforms for the conventional SVPWM and the proposed RCMV-SVPWM are shown in Fig. 10. The corresponding line voltage waveforms are shown in Fig. 11. As shown in the zoomed window of one cycle of line voltage, the voltages are primarily similar except for the appearance of very few pulses of opposing polarity.

Figure 8.

Common mode voltage waveforms (a) RCMV-SVPWM, (b) SVPWM.

Figure 9.

rms common-mode voltage.

Figure 10.

Phase voltage waveforms (a) SVPWM, (b) RCMV-SVPWM.

Figure 11.

Line voltage waveforms (a) SVPWM, (b) RCMV-SVPWM.

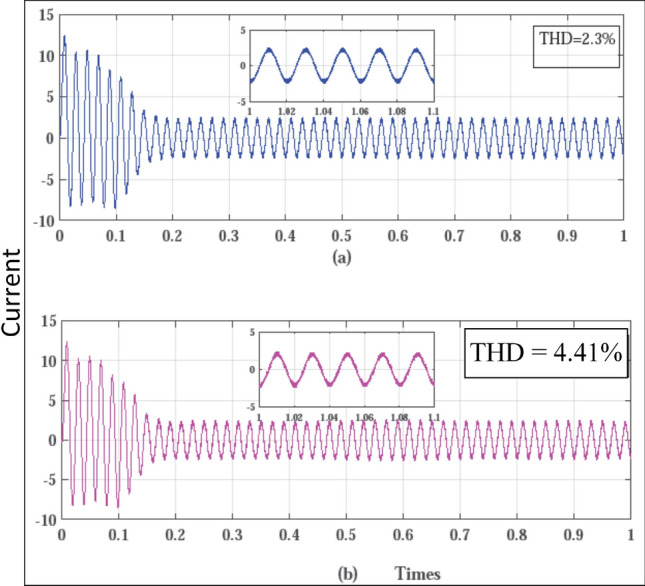

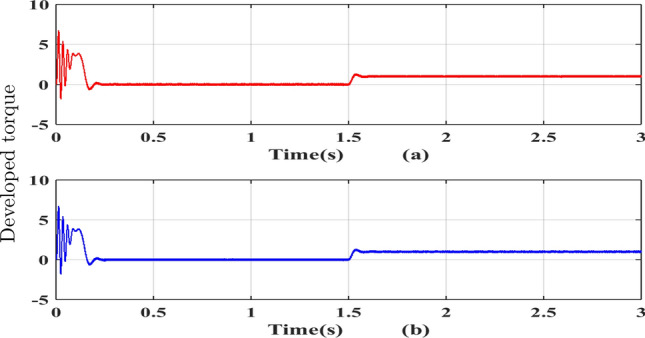

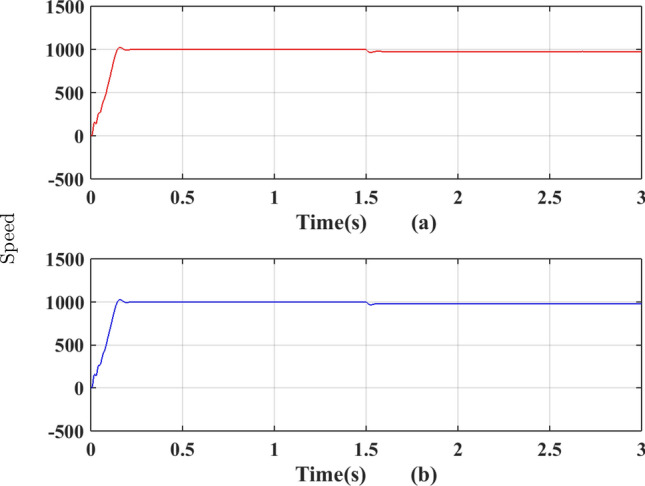

The phase current waveforms for the conventional SVPWM and RCMV-SVPWM are shown in Fig. 12. As non-zero voltage vectors are used to eliminate common-mode voltage, the THD in current is increased from and in RCMV-SVPWM schemes. But it is still within acceptable limits. The developed toque is depicted in Fig. 13 and the motor speed in Fig. 14. As seen from the figures, they are identical in both modulation schemes.

Figure 12.

Line current waveforms (a) SVPWM, (b) RCMV-SVPWM.

Figure 13.

Developed torque (a) SVPWM, (b) RCMV-SVPWM.

Figure 14.

Speed (a) SVPWM, (b) RCMV-SVPWM.

Experimental validations and discussion

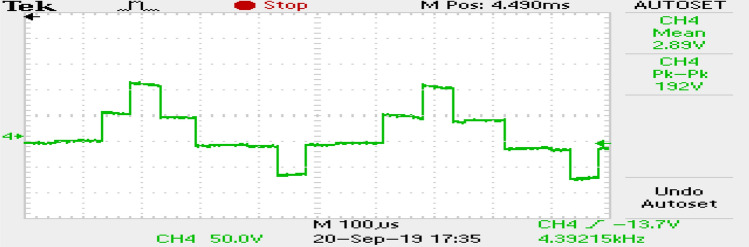

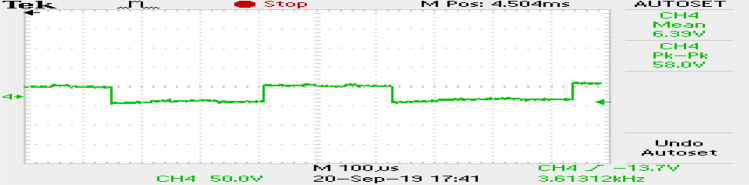

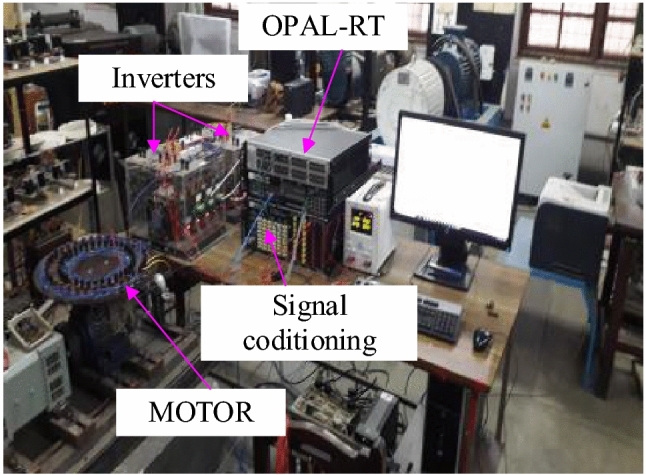

The proposed algorithm is verified using a test bench comprising of a dual three-phase inverter and dual three-phase induction machine, developed in the laboratory as shown in Fig. 15. The machine parameters are given in Appendix. Based on vector space decomposition theory, two PWM algorithms, namely the SVPWM and RCMV-SVPWM, are implemented on an FPGA-based OPAL-RT controller board (OP5660 along with OP8660). The low switching frequency of 2kHz is used for the dual three-phase machines, as they are used for high-power applications. The load is an asymmetrical six-phase squirrel cage motor having six poles made by rewinding the stator phases on the 36 stator slots of a 0.75-kW, 4-pole, three-phase motor. The performances of the proposed RCMV-SVPWM and SVPWM based on VSD techniques are compared. The phase current, line voltage, and CMV are measured without filtering by means of a TPS2014B Tektronix Oscilloscope. The common-mode voltage is measured between the -ve of the DC bus and the neutral of the machine.

Figure 15.

Exptsetup.pdf.

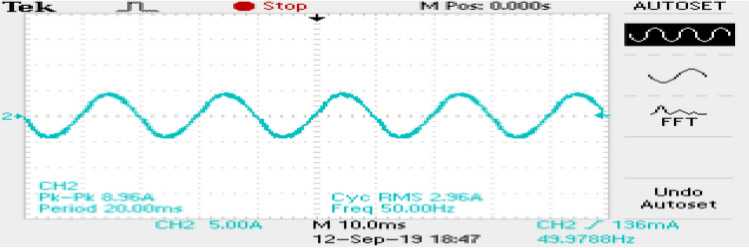

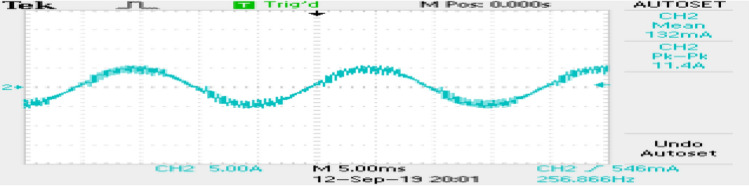

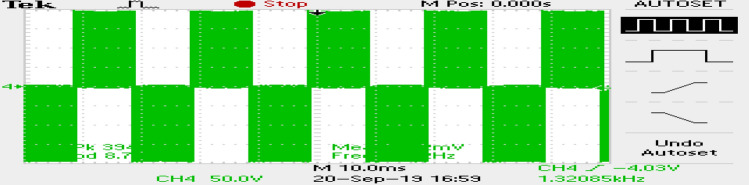

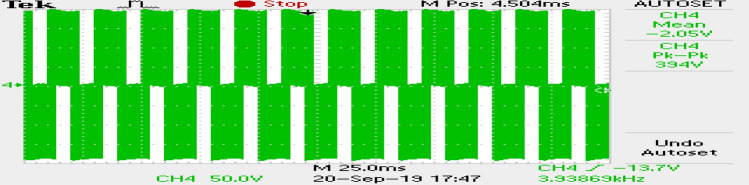

The phase currents in the case of SVPWM and RCMV-SVPWM are depicted in Figs. 16 and 17. From the figure, it can be observed that the current waveforms are almost similar, measuring 2.3A and 2.35A, respectively. The line current THD is 2.1% and 3.8%. The line voltage waveforms are shown in Figs. 18 and 19 without much of a difference between them. With conventional SVPWM, the peak-to-peak CMV() is 200V (Fig. 20) for a DC link voltage of 200V, much higher than the 66V (Fig. 21) for the same DC link voltage, obtained with the RCMV-SVPWM technique. Although there are spikes in CMV waveforms, they are largely due to the nonlinear behavior of the inverter and dead time. The reduction in common-mode voltage is the leading cause of the significant decrease in the high-frequency ripple content in the common-mode current. In summary, the proposed topology is able to reduce the common-mode voltage from half of the DC link voltage to one-sixth of the dc link voltage without hampering the other performance parameters, mainly current THD. A comparison between the two methods is mentioned in Table 4.

Figure 16.

Line current (SVPWM).

Figure 17.

Line current (RCMV-SVPWM).

Figure 18.

Line voltage (SVPWM).

Figure 19.

Line voltage (RCMV-SVPWM).

Figure 20.

Common-mode voltage (SVPWM).

Figure 21.

Common-mode voltage (RCMV-SVPWM).

Table 4.

Performance comparison.

| Performance parameter | SVPWM | RCMV-SVPWM |

|---|---|---|

| CMV | Vdc/2 | Vdc/6 |

| No of switching in CMV | f | f/3 |

| THD | 2.1% | 3.8% |

| RMS CMV | v | v/3 |

Conclusion

In this paper, a space vector modulation technique based on vector space decomposition theory is presented for the reduction of common-mode voltage in dual three-phase machines supplied by a six-phase inverter. The performance of the dual three-phase induction motor drive is analyzed for the proposed RCMV-SVPWM and conventional SVPWM. The main contribution of the proposed work shows that the VSD theory can be used to reduce CMV to a great extent. From the results, it is seen that the proposed method not only reduces the amplitude of the common-mode voltage but also reduces the pulsations in the common-mode voltage. The current THD is also compared in both cases. Though the THD produced in the case of RCMV-SVPWM is slightly higher than that of SVPWM, it is still found that the THD produced in the case of RCMV-SVPWM is within the specified limits as per IEEE-519.

Supplementary Information

List of symbols

Stator flux linkage

Rotor self flux linkage

Rotor stator mutual flux linkage

Stator rotor mutual flux linkage

Stator self flux linkage

Common-mode voltage

Dual three-phase induction machine

Rotor current

Stator current

Loss component in plane

d-axis rotor current

d-axis stator current

q-axis rotor current

q-axis stator current

Zero sequence component in loss plane

Magnetising inductance

Stator rotor mutual inductance

Stator self inductance

Reduced common-mode voltage

Space vector pulse width modulation

Total harmonic distortion

Rotor voltage

Stator voltage

d-axis stator voltage

q-axis stator voltage

Vector space decomposition

Voltage source inverter

Rotor leakage inductance

Stator leakage inductance

Rotor self inductance

Rotor stator mutual inductance

Stator resistances of the two three-phase winding sets

Author contributions

M.K.C. has written the manuscript. M.K.P. and G.K.S. have helped in preparing the manuscript. All the authors have reviewed the manuscript.

Data availability

The datasets used and/or analysed during the current study available from the corresponding author on reasonable request.

Competing interests

The authors declare no competing interests.

Footnotes

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

The online version contains supplementary material available at 10.1038/s41598-023-48339-3.

References

- 1.Singh GK. Multi-phase induction machine drive research-a survey. Electr. Power Syst. Res. 2002;61(2):139–147. doi: 10.1016/S0378-7796(02)00007-X. [DOI] [Google Scholar]

- 2.Mohammadpour A, Parsa L. A unified fault-tolerant current control approach for five-phase pm motors with trapezoidal back emf under different stator winding connections. IEEE Trans. Power Electron. 2013;28(7):3517–3527. doi: 10.1109/TPEL.2012.2223717. [DOI] [Google Scholar]

- 3.Apsley J, Williamson S, Smith A, Barnes M. Induction motor performance as a function of phase number. IEE Proc. Electr. Power Appl. 2006;153(6):898–904. doi: 10.1049/ip-epa:20060091. [DOI] [Google Scholar]

- 4.Cacciato M, Consoli A, Scarcella G, Testa A. Reduction of common-mode currents in PWM inverter motor drives. IEEE Trans. Ind. Appl. 1999;35(2):469–476. doi: 10.1109/28.753643. [DOI] [Google Scholar]

- 5.Liu Z, Zheng Z, Sudhoff SD, Gu C, Li Y. Reduction of common-mode voltage in multiphase two-level inverters using SPWM with phase-shifted carriers. IEEE Trans. Power Electron. 2016;31(9):6631–6645. doi: 10.1109/TPEL.2015.2499380. [DOI] [Google Scholar]

- 6.Romanenko, A., Ahola, J., Muetze, A., & Niskanen, V. Study of incipient bearing damage monitoring in variable-speed drive systems. In Power Electronics and Applications (EPE’14-ECCE Europe), 2014 16th European Conference on, IEEE, 1–10 (2014).

- 7.Freitas, I. S., Toliyat, H. A., Jacobina, C. B., & Ozturk, S. B. A pwm strategy with reduced bearing currents for five-phase motors. In Vehicle Power and Propulsion Conference, 2007, 354–358 (IEEE, 2007).

- 8.Muetze A, Niskanen V, Ahola J. On radio-frequency-based detection of high-frequency circulating bearing current flow. IEEE Trans. Ind. Appl. 2014;50(4):2592–2601. doi: 10.1109/TIA.2013.2296626. [DOI] [Google Scholar]

- 9.Tallam RM, Kerkman RJ, Leggate D, Lukaszewski RA. Common-mode voltage reduction PWM algorithm for AC drives. IEEE Trans. Ind. Appl. 2010;46(5):1959–1969. doi: 10.1109/TIA.2010.2057396. [DOI] [Google Scholar]

- 10.Hava AM, Ün E. Performance analysis of reduced common-mode voltage PWM methods and comparison with standard PWM methods for three-phase voltage-source inverters. IEEE Trans. Power Electron. 2009;24(1):241–252. doi: 10.1109/TPEL.2008.2005719. [DOI] [Google Scholar]

- 11.Un E, Hava AM. A near-state PWM method with reduced switching losses and reduced common-mode voltage for three-phase voltage source inverters. IEEE Trans. Ind. Appl. 2009;45(2):782–793. doi: 10.1109/TIA.2009.2013580. [DOI] [Google Scholar]

- 12.Kumar, C. M., Pathak, K. M., & Kumar, S. G. Space vector pwm with common-mode voltage reduction for six-phase drive. In 2020 IEEE 9th Power India International Conference (PIICON), 1–6. 10.1109/PIICON49524.2020.9112946 (2020).

- 13.Bodo N, Jones M, Levi E. A space vector PWM with common-mode voltage elimination for open-end winding five-phase drives with a single DC supply. IEEE Trans. Ind. Electron. 2014;61(5):2197–2207. doi: 10.1109/TIE.2013.2272273. [DOI] [Google Scholar]

- 14.Chen K-Y, Hsieh M-S. Generalized minimum common-mode voltage PWM for two-level multiphase VSIS considering reference order. IEEE Trans. Power Electron. 2017;32(8):6493–6509. doi: 10.1109/TPEL.2016.2615111. [DOI] [Google Scholar]

- 15.Review on pulse width modulation strategies for common-mode voltage reduction in three phase voltage source inverters. IET Power Electronics9(14), 2611–2620 (2016).

- 16.Durán MJ, Prieto J, Barrero F, Riveros JA, Guzman H. Space-vector PWM with reduced common-mode voltage for five-phase induction motor drives. IEEE Trans. Ind. Electron. 2013;60(10):4159–4168. doi: 10.1109/TIE.2012.2217719. [DOI] [Google Scholar]

- 17.Durán MJ, Prieto J, Barrero F. Space vector PWM with reduced common-mode voltage for five-phase induction motor drives operating in overmodulation zone. IEEE Trans. Power Electron. 2013;28(8):4030–4040. doi: 10.1109/TPEL.2012.2229394. [DOI] [Google Scholar]

- 18.Sharma S, Aware M, Bhowate A, Levi E. Performance improvement in six-phase symmetrical induction motor by using synthetic voltage vector based direct torque control. IET Electr. Power Appl. 2019;13(11):1638–1646. doi: 10.1049/iet-epa.2018.5983. [DOI] [Google Scholar]

- 19.Zhao Y, Lipo TA. Space vector PWM control of dual three-phase induction machine using vector space decomposition. IEEE Trans. Ind. Appl. 1995;31(5):1100–1109. doi: 10.1109/28.464525. [DOI] [Google Scholar]

- 20.Huang Y, Walden J, Zhang X, Yan Y, Bai H, Jin F, Cheng B. A novel zero/reduced common-mode voltage modulation scheme for a dual three-phase motor drive system in full modulation span. IEEE Trans. Power Electron. 2022;37(6):6765–6779. doi: 10.1109/TPEL.2022.3140261. [DOI] [Google Scholar]

- 21.Abid ME, Shaikh MS, Maurya R. Performance investigation on SVPWM sequences based on reduced common-mode voltage in dual three-phase asymmetrical machine. IEEE Trans. Energy Convers. 2021;36(4):2884–2893. doi: 10.1109/TEC.2021.3069019. [DOI] [Google Scholar]

- 22.Zhang Z, Jin S, Zhang Z, Zhang F, Li B. Novel space vector PWM technology with lower common-mode voltage for dual three-phase PMSM. IEEE Trans. Energy Convers. 2020;13(7):1426–1433. doi: 10.1049/iet-pel.2019.0929. [DOI] [Google Scholar]

- 23.Bojoi R, Farina F, Profumo F, Tenconi A. Dual-three phase induction machine drives control-a survey. IEEJ Trans. Ind. Appl. 2006;126(4):420–429. doi: 10.1541/ieejias.126.420. [DOI] [Google Scholar]

- 24.Hassan M, Abdelhakim A, Shoyama M, Dousoky GM. On-the-analysis and reduction of common-mode voltage of a single-stage inverter through control of a four-leg-based topology. Int. J. Electr. Power Energy Syst. 2021;127(106710):1–24. doi: 10.1016/j.ijepes.2020.106710. [DOI] [Google Scholar]

- 25.Levi E, Bojoi R, Profumo F, Toliyat H, Williamson S. Multiphase induction motor drives a technology status review. IET Electr. Power Appl. 2007;1(4):489. doi: 10.1049/iet-epa:20060342. [DOI] [Google Scholar]

- 26.Lopez O, Alvarez J, Malvar J, Yepes AG, Vidal A, Baneira F, Pérez-Estévez D, Freijedo FD, Doval-Gandoy J. Space-vector PWM with common-mode voltage elimination for multiphase drives. IEEE Trans. Power Electron. 2016;31(12):8151–8161. doi: 10.1109/TPEL.2016.2521330. [DOI] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Supplementary Materials

Data Availability Statement

The datasets used and/or analysed during the current study available from the corresponding author on reasonable request.