Abstract

Two-dimensional transition metal dichalcogenide (2D TMD) semiconductors allow facile integration of p- and n-type materials without a lattice mismatch. Here, we demonstrate gate-tunable n- and p-type junctions based on vertical heterostructures of MoS2 and WSe2 using van der Waals (vdW) contacts. The p–n junction shows negative differential resistance (NDR) due to Fowler–Nordheim (F–N) tunneling through the triangular barrier formed by applying a global back-gate bias (VGS). We also show that the integration of hexagonal boron nitride (h-BN) as an insulating tunnel barrier between MoS2 and WSe2 leads to the formation of sharp band edges and unintentional inelastic tunnelling current. The devices based on vdW contacts, global VGS, and h-BN tunnel barriers exhibit NDR with a peak current (Ipeak) of 315 μA, suggesting that the approach may be useful for applications.

Keywords: 2D materials, negative differential resistance, tunnel transistor, MoS2/WSe2 heterostructure, h-BN tunnel barrier

Devices with negative differential resistance (NDR) exhibit multiple threshold voltages, making them attractive for multivalue logic systems1,2 and radio frequency oscillators.3 NDR devices are based on the transition of carrier transport from quantum mechanical tunnelling to thermionic emission by sweeping the applied voltage.4 To use NDR for functional devices, the output characteristics of the transistor in the NDR regime should have a high peak current (Ipeak) and a high peak-to-valley current ratio (PVCR). The importance of high Ipeak and high PVCR lies in their role in enabling efficient signal amplification, reliable switching behavior, and optimization of device performance for various high-frequency applications.5,6

Two-dimensional transition metal dichalcogenide (2D TMD) semiconductors are ideally suited for realizing NDR because they can be easily assembled, and sharp interfaces can be formed without lattice mismatch.7 A variety of NDR devices based on heterostructures of 2D semiconductors have been reported. In particular, heterostructures using SnSe28−10 or black phosphorus (BP)11,12 have been studied because both are highly doped degenerate 2D semiconductors—SnSe2 being n-type and BP being p-type. Despite the ease of forming type III band alignment due to the degeneracy, the low ambient stability and consequential surface oxidation make it difficult to achieve clean interfaces.8 Conversely, widely used 2D TMDs such as MoS2 and WSe2 can provide improved ambient stability. Thus, several reports have explored tunnel devices using MoS2 and WSe2 heterostructures. Roy et al. have reported a dual-gate MoS2/WSe2 heterojunction, which shows NDR behavior at low temperatures.13 Here, the dual-gate structure plays a key role in electrostatically doping the two materials to split the band alignment. Additionally, Nourbakhsh et al. have shown room-temperature (RT) NDR with MoS2/WSe2 heterostructure with back-gate bias (VGS) modulation.1 Through calculated band diagrams, the authors determined the optimal thicknesses of the two materials that would allow tunneling in the transverse direction. However, the low Ipeak of a few hundred pA should be improved for practical application.

In this work, we demonstrate RT gate-tunable MoS2 and WSe2 heterostructures. We use In/Au van der Waals (vdW) contacts for n-type transport in MoS214 and Pt vdW contacts for p-type transport in WSe2,15 which help in boosting electron and hole injection, respectively. We compare the performance of the MoS2/WSe2 junctions when they are directly in contact with each other and when a thin hexagonal boron nitride (h-BN) tunnel barrier is inserted between them. We observe that the devices with a h-BN tunnel barrier and vdW contacts exhibit an Ipeak of 315 μA, which is among the highest values reported at RT.

For the NDR, forming an effective p–n junction is necessary. We applied three strategies to form an effective p–n junction. First, for all devices, we have used WSe2 consisting of two or three layers and MoS2 of >10 layers, fabricated on h-BN on SiO2 (90 nm)/Si substrates (device fabrication is described in detail in the Supporting Information, Experimental Methods). We selected the layer thicknesses based on an earlier study, which calculated the optimal thicknesses for NDR.1 The use of h-BN as a substrate helps reduce hysteresis due to substrate traps,16 interface phonon scattering,17 and most importantly electron doping from SiO2,15 essential for achieving p-type (WSe2) and improving device performance (Figure S1). Finally, we used In (8 nm)/Au (80 nm) and Pt (20 nm capped with 60 nm of Au) vdW contacts for the MoS2 and WSe2 FETs, respectively. The optical microscope (OM) image of MoS2 and WSe2 FETs with vdW contacts is shown in Figure 1a. Our prior investigation revealed that vdW contacts, specifically In/Au on MoS2 and Pt on WSe2, exhibit distinct n- and p-type transport behavior, originating from clean metal/semiconductor interfaces that prevent Fermi-level pinning (FLP).14,15

Figure 1.

FET comparison of vdW and Cr/Au contacts. (a) OM image of MoS2 and WSe2 FETs. The scale bar is 10 μm. (b,c) VGS-dependent transfer curves of (b) multilayer MoS2 and (c) few-layer WSe2. Gray-colored curves represent gate-leakage current (IGS). (d) Energy band alignment of WSe2 and the metal contacts. FLP of Cr contacts induce n-type transport of WSe2.

We compared the characteristics of FETs with vdW contacts with non-vdW contacts based on Cr (5 nm)/Au (80 nm), commonly used for 2D TMD FETs (Figure 1b and c). Both In/Au and Cr/Au contacts show n-type behavior,18 while In/Au contacts show an improved on/off ratio. In contrast, Cr/Au contacts on few-layer WSe2 exhibit n-type transport while the vdW Pt contacts show p-type-dominant behavior.19 This result is consistent with previous studies showing that vdW contacts are effective in achieving p-type transport in WSe2.15,20 In addition, temperature-dependent transport measurements showing stable transport behavior over a large temperature range are shown in Figure S2.

The p-type behavior with Pt vdW contacts can be understood by using the energy band diagram in Figure 1d. According to the band alignment, Cr/Au contact is expected to show ambipolar transport closer to p-type.21,22 However, for non-vdW contacts, defects are formed at the metal/semiconductor interface leading to FLP close to the conduction band (CB) of WSe2,23 which leads to n-type behavior of Cr/Au-WSe2 FETs.24 In contrast, Pt deposition forms a vdW gap between the metal and WSe2, which follows the Pt work function. This leads to an effective hole injection for p-type WSe2.

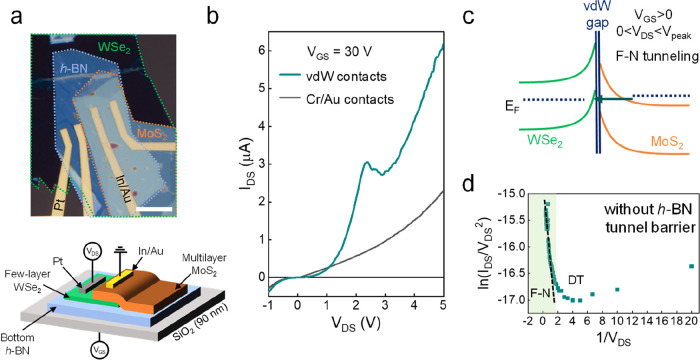

Figure 2 describes the role of vdW contacts in heterostructure performance. We prepared two different sets of devices with identical configurations: a stack of multilayer MoS2 flakes on top of few-layer WSe2 on the h-BN bottom layer. In the first set of devices, we deposited In and Au on MoS2 and Pt on WSe2. Figure 2a displays an OM image of a device along with a device schematic at the bottom. For comparison, we fabricated another set of devices with Cr/Au contacts (see Figure S3 for an OM image of such a device). We applied voltage (drain-source voltage, VDS) to WSe2 (drain) while MoS2 (source) was grounded. The current–voltage (I–V) curves of these two types of devices, measured at RT, are plotted in Figure 2b (the VGS-dependent I–V curves are presented in Figure S4). The devices with vdW contacts exhibit a clear NDR, whereas it is absent in devices with Cr/Au contacts. The observation of NDR in the devices with vdW contacts is evidence of tunneling (the IDS–VGS curve is depicted in Figure S5).

Figure 2.

A comparison of NDR from FETs with vdW and Cr/Au contacts. (a, top) OM image of MoS2/WSe2 heterostructure devices. In/Au and Pt electrodes were used as electrical contacts on MoS2 and WSe2, respectively. The scale bar is 10 μm. (bottom) A device schematic drawing of the device. (b) I–V curves of the vdW (green) and Cr/Au contacts (black). (c) Energy band diagram of the MoS2/WSe2 heterojunction with a vdW gap and F–N tunnelling. The drawing is based on VGS > 0, 0 < VDS < Vpeak conditions. (d) ln(IDS/VDS2) versus 1/VDS plot. Linear region (black dotted line) refers to the F–N tunnelling.

To observe NDR in the forward bias region (VDS > 0) of a p–n junction, a type III junction, with a broken band alignment at VDS = 0 V is needed. Type III junctions can form when both p- and n-type semiconductors are highly doped and are in a degenerate state. However, the materials that we used (MoS2 and WSe2) are not in a degenerate state. Moreover, unlike a dual gate structure,13 global VGS makes it difficult to control the carrier density of each material separately. Notably, in our heterostructures, NDR shows a more distinct trend at VGS > 0, which is also observed in previous works.12,25 We attribute this to steep band bending of a few layers of WSe2 with better VGS coupling due to its proximity to the gate and slight bending of multilayer MoS2 due to screening from WSe2 (Figure 2c). At 0 < VDS < 2.35 V (peak voltage, Vpeak), the electrons from the MoS2 tunnel through the thin triangular barrier and reach WSe2. With increasing forward bias, the overlap between the MoS2 CB and the WSe2 VB closes the thin triangular tunnel path, and therefore the tunneling current begins to decrease, thereby showing NDR. Conversely, the case differs when Cr/Au contacts are employed. Because the Fermi-level is pinned, WSe2 band bending cannot occur effectively under VGS variation. Hence, the MoS2 electrons will face the midband gap state of WSe2 due to the forming of a small triangular barrier. The tunnel transport mechanism is depicted in Figure 2d to validate the tunnel transport mechanism. The I–V curve in the region of 0 < VDS < Vpeak can be modeled using the Simmons approximation.26 The Fowler–Nordheim (F–N) tunnelling can be expressed as

Here, d represents the thickness of the tunnel barrier, m* denotes the effective electron mass, φ corresponds to the tunnelling barrier height, and h is the Planck constant. Plotting ln(I/V2) versus 1/V should reveal a linear regime with a negative slope (black dotted line) for F–N tunnelling.27,28 From the slope of the curve, we can derive the F–N tunneling barrier height (φ) of 0.11 eV.

We further validate the occurrence of F–N tunneling in our devices through temperature-dependent transport measurements. In Figure S6, we present the temperature-dependent I–V curves from a device showing NDR with In/Au and Pt contacts. Here, we can observe that the steep increase of tunnelling current in the reverse bias region (VDS < 0 V) is insensitive to changes in temperature. Furthermore, the F–N tunnelling current, which is the increase in current in the forward bias region preceding the NDR effect (0 < VDS < Vpeak), also shows a negligible temperature dependence. However, beyond the NDR effect, the current flow is governed by thermionic emission and is highly sensitive to changes in temperature (Figure S6, inset). The results in Figures 2b,d and S6 suggest that the vdW gap between MoS2/WSe2 alongside the contribution of F–N tunneling is critical.

Next, we integrated 10 layers (3.4 nm) of h-BN between MoS2 and WSe2. The insertion of h-BN as a tunnel barrier serves as an insulating spacer that enables precise band alignment.17,29,30 The insulating nature of h-BN results in sharper band edges for both MoS2 and WSe2. Consequently, the energy levels of the VB and CB experience a sharp transition at the MoS2/h-BN and WSe2/h-BN interfaces, resulting in a well-defined tunnel barrier. However, at the same time, it requires extra energy for the electrons to tunnel through the barrier. Also, due to additional stacking steps during fabrication and natural defects in the h-BN crystal, unintentional trap sites may be involved.31 The difference in the transport behavior between two devices with and without the h-BN tunnel barrier at RT is shown in Figure 3a. Both devices show clear NDR behavior. However, the device with the h-BN tunnel barrier (left y axis, orange) displays a substantial increase (2 orders of magnitude) in Ipeak compared to the device without the tunnel barrier (right y axis, green). Additionally, we observe an increase in the VDS, from 2.35 to 4.1 V, required to reach the Ipeak. We attribute this to the presence of an additional tunnel barrier (h-BN), which necessitates a higher voltage for carriers to reach the opposite side (WSe2) of the energy band.

Figure 3.

The role of the h-BN tunnel barrier. (a) I–V curves with h-BN tunnel barrier (orange) and without tunnel barrier (green). (b) ln(IDS/VDS2) versus 1/VDS plot depicting DT for the device with an h-BN tunnel barrier. (c) Energy band diagram of MoS2/WSe2 heterojunction with h-BN tunnel barrier. The drawing is based on VGS > 0 and 0 < VDS < Vpeak conditions. (d) NDR behavior of the device with h-BN tunnel barrier at 9 K and RT.

To explore the mechanism for higher Ipeak, the I–V curve in the forward bias region (0 < VDS < Vpeak) is studied. Unlike the F–N tunnelling observed in Figure 2d, Figure 3b follows a logarithmic slope, meaning the device incorporating the h-BN tunnel barrier operates via direct tunnelling (DT).32 The DT current can be expressed as

The possible energy band alignment due to DT transport through the h-BN tunnel barrier is shown in Figure 3c. Although precise band alignment is difficult to extract and varies from study to study,1,13,27 we can imagine the presence of inelastic tunnelling such as phonon-assisted, trap-assisted, or Shockley–Read–Hall tunnelling.13,33,34 To obtain more insight, we plotted the NDR behavior of the h-BN tunnel barrier device at 9 K and RT for comparison (Figure 3d). It shows a distinct increase in the current at RT, and such a temperature-dependent enhancement is absent in devices without an h-BN tunnel barrier (Figure S6). This leads to a higher Ipeak and a larger peak-to-valley current ratio (PVCR) at higher temperatures due to thermally enhanced inelastic tunnelling. Thus, we believe that combined effects including the sharp band edges as well as inelastic tunneling through the h-BN barrier are important for the enhanced Ipeak.

The properties of devices with the h-BN tunnel barrier were further examined by varying VGS. Figure 4a shows an OM image of a typical device. The three-layer thickness of WSe2 enables effective gate tunability of the Fermi level, while the effect of the VGS on the relatively thick (10 layers) MoS2 is small. The thicknesses of the layers measured by atomic force microscopy (AFM) topography are presented in Figure S7. Electrical bias was applied to the Pt contact connected to WSe2, while the current was collected from the In/Au contact on MoS2. The gate bias was applied by global VGS (SiO2/Si). The VGS dependence of the NDR at RT is plotted in Figure 4b. With increasing VGS, the NDR becomes more pronounced, resulting in higher current levels.12,25 This behavior can be attributed to the accumulation of electrons in MoS2 as VGS > 0, providing a large number of carriers available for tunnelling when a forward bias is applied.

Figure 4.

VGS-dependent NDR with h-BN tunnel barrier. (a) OM image of the heterostructure. The scale bar is 10 μm. (b) VGS-dependent NDR. (c) VGS-dependent PVCR and the (d) benchmark of Jpeak versus PVCR for various reported 2D NDR devices based on tunnelling that operate at RT. The transverse tunnelling transistor31 is not included in this plot due to a different operation mechanism and lack of device size information.

The energy band alignment of the WSe2/h-BN/MoS2 device under varying applied VDS is illustrated in Figure S8. When reverse bias (VDS < 0) is applied, it allows the tunnelling of electrons from filled states in WSe2 through the h-BN barrier to reach the unoccupied states in the MoS2 CB. This tunnelling phenomenon results in a sharp increase in current as a larger negative VDS is applied. Conversely, when positive voltage (VDS > 0) is applied, the direction of carrier injection reverses. Electrons in the MoS2 CB tunnel through the barrier to reach the WSe2, leading to an inelastic tunnelling current. This current continues to increase until it reaches the maximum value, Ipeak. Beyond Vpeak, electrons from MoS2 face the midband gap state of the WSe2, where no density of states exists. Thus, the current decreases. Notably, some hot electrons may still overcome this barrier and contribute to the valley current (Ivalley). Subsequently, when thermionic emission provides sufficient energy for MoS2 electrons to transit to the WSe2 CB, as in a normal diode, the current once again begins to rise.

We extracted the PVCR, which exhibits an increasing trend as VGS increases (Figure 4c). The overall PVCR value is not exceptionally high due to the presence of a substantial Ivalley. This can be attributed to a high probability of inelastic tunneling and thermally excited electrons across the tunnel barrier. Consequently, this results in a relatively small overall PVCR value. Nonetheless, the increase in Ipeak surpasses the rise in Ivalley, leading to an elevation in PVCR as VGS increases.

To benchmark our results, in Figure 4d we have plotted the Jpeak (peak current density, Ipeak/device working area) and PVCR from other devices based on the heterostructure of 2D semiconductors.1,2,8−12,25,30,35,36 Among various types of devices employing different 2D materials, principles, and environments, we have selected devices based on tunneling that operate at RT. Our devices exhibit a large Jpeak of 2420 A/cm2. A further increase in PVCR could be accomplished by exploring materials with different band gaps and higher doping levels, as well as carefully controlling the inelastic tunneling to minimize the Ivalley. It is noteworthy that the transverse tunnelling transistor demonstrated by Xiong et al.31 using black phosphorus exhibits a large Ipeak and PVCR simultaneously. Employing transverse tunneling may be an alternative route to improve the PVCR.

In summary, our findings demonstrate a high Ipeak NDR device by using vdW heterostructures. The utilization of In/Au and Pt vdW contacts facilitates the effective formation of the p–n junction. The devices show NDR, facilitated by F–N tunneling through a triangular barrier induced by applied VGS. Furthermore, integration of the h-BN tunnel barrier leads to improved NDR because of sharp band edges as well as inelastic tunnelling. This result yields high Ipeak values. These results pave the way for potential applications in logic devices and oscillators.

Acknowledgments

We acknowledge funding from European Research Council (ERC) Advanced Grant under the European Union’s Horizon 2020 Research and Innovation Programme (grant agreement GA 101019828-2D-LOTTO]), EPSRC (EP/T026200/1, EP/T001038/1). Also, K.W. and T.T. acknowledge support from the JSPS KAKENHI (grant numbers 21H05233 and 23H02052) and World Premier International Research Center Initiative (WPI), MEXT, Japan. This work was supported by the Henry Royce Institute for advanced materials through the Equipment Access Scheme enabling access to the Cryo Probe Station at Cambridge; Cambridge Royce facilities grant EP/P024947/1 and Sir Henry Royce Institute - recurrent grant EP/R00661X/1).

Supporting Information Available

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acs.nanolett.3c04607.

Role of h-BN as a substrate, temperature-dependent transport of MoS2 and WSe2 with vdW contacts, OM image of the Cr/Au device, VGS-dependent I–V curves of the MoS2/WSe2 heterostructure with vdW contacts and Cr/Au contacts, VDS-dependent transfer curves of the MoS2/WSe2 heterostructure, temperature-dependence of the NDR device, thickness of each layer of the heterostructure, energy band diagram of the heterojunction, OM and I–V characteristics of additional NDR devices, experimental methods (PDF)

Author Contributions

M.C. designed and supervised the project. J.H.K. fabricated samples, performed experiments, and analyzed the data. S.S. and Y.W. supported the data analysis. T.T. and K.W. provided the bulk h-BN crystals. J.H.K. and M.C. wrote the manuscript with support from S.S. and Y.W. All authors discussed the results and commented on the manuscript.

The authors declare no competing financial interest.

Supplementary Material

References

- Nourbakhsh A.; Zubair A.; Dresselhaus M. S.; Palacios T. Transport Properties of a MoS2/WSe2 Heterojunction Transistor and Its Potential for Application. Nano Lett. 2016, 16, 1359–1366. 10.1021/acs.nanolett.5b04791. [DOI] [PubMed] [Google Scholar]

- Seo S.; et al. A Van Der Waals Reconfigurable Multi-Valued Logic Device and Circuit Based on Tunable Negative-Differential-Resistance Phenomenon. Adv. Mater. 2022, 34, 2202799. 10.1002/adma.202202799. [DOI] [PubMed] [Google Scholar]

- Lin J. C.; et al. Porous Silicon NDR-Based High Power RF Oscillator Diode. IEEE Electron Device Lett. 2017, 38, 701–704. 10.1109/LED.2017.2692768. [DOI] [Google Scholar]

- Woo G.; Kim T.; Yoo H. Band-to-Band Tunneling Control by External Forces: A Key Principle and Applications. Adv. Electron Mater. 2023, 9, 2201015. 10.1002/aelm.202201015. [DOI] [Google Scholar]

- Mehdi I.; Haddad G. I.; Mains R. K. Performance Criteria for Resonant Tunneling Diodes as Millimeter-Wave Power Sources. Microw Opt Techn Let 1989, 2, 172–175. 10.1002/mop.4650020509. [DOI] [Google Scholar]

- Zhang Z. H.; et al. Toward High-Peak-to-Valley-Ratio Graphene Resonant Tunneling Diodes. Nano Lett. 2023, 23, 8132–8139. 10.1021/acs.nanolett.3c02281. [DOI] [PMC free article] [PubMed] [Google Scholar]

- Geim A. K.; Grigorieva I. V. Van der Waals heterostructures. Nature 2013, 499, 419–425. 10.1038/nature12385. [DOI] [PubMed] [Google Scholar]

- Fan S. D.; et al. Tunable Negative Differential Resistance in van der Waals Heterostructures at Room Temperature by Tailoring the Interface. ACS Nano 2019, 13, 8193–8201. 10.1021/acsnano.9b03342. [DOI] [PubMed] [Google Scholar]

- Cong X. N.; et al. Efficiently band-tailored type-III van der Waals heterostructure for tunnel diodes and optoelectronic devices. Nano Res. 2022, 15, 8442–8450. 10.1007/s12274-022-4463-7. [DOI] [Google Scholar]

- Yan R. S.; et al. Esaki Diodes in van der Waals Heterojunctions with Broken-Gap Energy Band Alignment. Nano Lett. 2015, 15, 5791–5798. 10.1021/acs.nanolett.5b01792. [DOI] [PubMed] [Google Scholar]

- Na J.; Kim Y.; Smet J. H.; Burghard M.; Kern K. Gate-Tunable Tunneling Transistor Based on a Thin Black Phosphorus-SnSe2 Heterostructure. ACS Appl. Mater. Inter 2019, 11, 20973–20978. 10.1021/acsami.9b02589. [DOI] [PMC free article] [PubMed] [Google Scholar]

- Shim J.; et al. Phosphorene/rhenium disulfide heterojunction-based negative differential resistance device for multi-valued logic. Nat. Commun. 2016, 7, 13413. 10.1038/ncomms13413. [DOI] [PMC free article] [PubMed] [Google Scholar]

- Roy T.; et al. Dual-Gated MoS2/WSe2 van der Waals Tunnel Diodes and Transistors. ACS Nano 2015, 9, 2071–2079. 10.1021/nn507278b. [DOI] [PubMed] [Google Scholar]

- Wang Y.; et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 2019, 568, 70–74. 10.1038/s41586-019-1052-3. [DOI] [PubMed] [Google Scholar]

- Wang Y.; et al. P-type electrical contacts for 2D transition-metal dichalcogenides. Nature 2022, 610, 61–66. 10.1038/s41586-022-05134-w. [DOI] [PubMed] [Google Scholar]

- Illarionov Y. Y.; et al. The role of charge trapping in MoS2/SiO2 and MoS2/hBN field-effect transistors. 2D Mater. 2016, 3, 035004. 10.1088/2053-1583/3/3/035004. [DOI] [Google Scholar]

- Knobloch T.; et al. The performance limits of hexagonal boron nitride as an insulator for scaled CMOS devices based on two-dimensional materials. Nat. Electron 2021, 4, 98–108. 10.1038/s41928-020-00529-x. [DOI] [Google Scholar]

- Schranghamer T. F.; et al. Ultrascaled Contacts to Monolayer MoS2 Field Effect Transistors. Nano Lett. 2023, 23, 3426–3434. 10.1021/acs.nanolett.3c00466. [DOI] [PubMed] [Google Scholar]

- Oberoi A.; et al. Toward High-Performance p-Type Two-Dimensional Field Effect Transistors: Contact Engineering, Scaling, and Doping. ACS Nano 2023, 17, 19709–19723. 10.1021/acsnano.3c03060. [DOI] [PubMed] [Google Scholar]

- Kong L. G.; et al. Doping-free complementary WSe2 circuit via van der Waals metal integration. Nat. Commun. 2020, 11, 1866. 10.1038/s41467-020-15776-x. [DOI] [PMC free article] [PubMed] [Google Scholar]

- Zatko V.; et al. Band-Gap Landscape Engineering in Large-Scale 2D Semiconductor van der Waals Heterostructures. ACS Nano 2021, 15, 7279–7289. 10.1021/acsnano.1c00544. [DOI] [PubMed] [Google Scholar]

- Liu C. S.; et al. Various and Tunable Transport Properties of WSe2 Transistor Formed by Metal Contacts. Small 2017, 13, 1604319. 10.1002/smll.201604319. [DOI] [PubMed] [Google Scholar]

- Kim C.; et al. Fermi Level Pinning at Electrical Metal Contacts of Monolayer Molybdenum Dichalcogenides. ACS Nano 2017, 11, 1588–1596. 10.1021/acsnano.6b07159. [DOI] [PubMed] [Google Scholar]

- Pudasaini P. R.; et al. High-performance multilayer WSe2 field-effect transistors with carrier type control. Nano Res. 2018, 11, 722–730. 10.1007/s12274-017-1681-5. [DOI] [Google Scholar]

- Afzal A. M.; et al. High performance and gate-controlled GeSe/HfS2 negative differential resistance device. RSC Adv. 2022, 12, 1278–1286. 10.1039/D1RA07276E. [DOI] [PMC free article] [PubMed] [Google Scholar]

- Simmons J. G. Generalized formula for the electric tunnel effect between similar electrodes separated by a thin insulating film. J. Appl. Phys. 1963, 34, 1793–1803. 10.1063/1.1702682. [DOI] [Google Scholar]

- Doan M. H.; et al. Charge Transport in MoS2/WSe2 van der Waals Heterostructure with Tunable Inversion Layer. ACS Nano 2017, 11, 3832–3840. 10.1021/acsnano.7b00021. [DOI] [PubMed] [Google Scholar]

- Srivastava P. K.; et al. Van der Waals Broken-Gap p-n Heterojunction Tunnel Diode Based on Black Phosphorus and Rhenium Disulfide. ACS Appl. Mater. Inter 2019, 11, 8266–8275. 10.1021/acsami.8b22103. [DOI] [PubMed] [Google Scholar]

- Britnell L.; et al. Field-Effect Tunneling Transistor Based on Vertical Graphene Heterostructures. Science 2012, 335, 947–950. 10.1126/science.1218461. [DOI] [PubMed] [Google Scholar]

- Movva H. C. P.; et al. Room Temperature Gate-tunable Negative Differential Resistance in MoS2/hBN/WSe2 Heterostructures. 74th Annual Device Research Conference, June 19–22, 2016; Institute of Electrical and Electronics Engineers (IEEE), 2016; pp 1–2. 10.1109/DRC.2016.7548486. [DOI] [Google Scholar]

- Xiong X.; et al. A transverse tunnelling field-effect transistor made from a van der Waals heterostructure. Nat. Electron 2020, 3, 106–112. 10.1038/s41928-019-0364-5. [DOI] [Google Scholar]

- Ahmed F.; Choi M. S.; Liu X.; Yoo W. J. Carrier transport at the metal-MoS2 interface. Nanoscale 2015, 7, 9222–9228. 10.1039/C5NR01044F. [DOI] [PubMed] [Google Scholar]

- Lee C. H.; et al. Atomically thin p–n junctions with van der Waals heterointerfaces. Nat. Nanotechnol 2014, 9, 676–681. 10.1038/nnano.2014.150. [DOI] [PubMed] [Google Scholar]

- Hansma P. K. Inelastic Electron-Tunneling. Phys. Rep. 1977, 30, 145–206. 10.1016/0370-1573(77)90054-0. [DOI] [Google Scholar]

- Fan S.; Yun S. J.; Yu W. J.; Lee Y. H. Tailoring Quantum Tunneling in a Vanadium-Doped WSe2/SnSe2 Heterostructure. Adv. Sci. 2020, 7, 1902751. 10.1002/advs.201902751. [DOI] [PMC free article] [PubMed] [Google Scholar]

- Wang J. X.; et al. Vertical WS2/SnS2 van der Waals Heterostructure for Tunneling Transistors. Sci. Rep 2018, 8, 17755. 10.1038/s41598-018-35661-4. [DOI] [PMC free article] [PubMed] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.