Abstract

Low voltage DC microgrids (LVDC) are on rise, because of increase in usage of electronics-based utility loads. However, the protection and safety aspects of these grids remain unresolved due to the fault current magnitude, unnecessary tripping, and blinding of protection. In this paper, an adaptive differential protection system incorporated with an advanced graph algorithm is proposed for DC microgrid. This graph algorithm is a combination of Fenwick tree and Bidirectional Dijkstra algorithm. Fenwick tree algorithm is used to determine the network configuration and Bidirectional Dijkstra algorithm is used to determine the least distance from the fault location to the nearest distributed generations. The developed protection scheme is applied to a 7 bus, 400 V DC microgrid setup using Real Time simulator (control hardware in loop) to detect and clear the faults such as kilometric faults, and cross-country faults. In terms of efficiency, the proposed algorithm demonstrates superiority over the conventional algorithm by detecting and rectifying faults in 384 μs.The results depict the robustness of the protection setup in clearing the faults rapidly with minimum network disconnection.

Keywords: Bidirectional Dijkstra algorithm, Distributed generations (DG), DC microgrids, Fault detection, Fenwick algorithm, Protection controller (PC)

Nomenclature

A. VARIABLES

- Iph

Photo-current of a module

- Irs

Reverse saturation current of a module

- IPV

Output current of a PV module

Pitch angle

- Io

Saturation current of a module

- NS, Np

Number of cells connected in series and parallel

- Rs

Series Resistance

- Pω

wind power generated

- ρ

air density

- Ar

blade area

- V

Wind Speed

- Cp

Power Coefficient

- S

Blade Span Area

- α

Angle of attack

- λ

Tip speed ratio

Minimum and Maximum state of charge of Battery system

B. ACRONYMS

- LVDC

Low voltage DC microgrids

- DG

Distributed Generation

- DCMG

DC Microgrid

- HRF

High Resistance Faults

- LSTM

Long Short-Term Memory

- SVM

Support Vector Machines

- HMM

Hidden Markov Model

- SVC

Support Vector Classifier

- NC

Nearest Centroid

- MLP

Multi-layer Perceptron

- V2G

vehicle-to-grid

- ESS

Energy Storage System

- CS

compressed sensing

- RT

Regression Tree

- MILP

mixed-integer linear programming

- MDS

Multi-energy Distribution Systems

- AB

Active Bus

- SP

Shortest Path

- BS

Battery System

- PV

Photovoltaic

- PMSG

Permanent Magnet Synchronous Generator

- WECS

Wind Energy Conversion System

- SOC

State of Charge

- BSREFCAP

Reference capacity of Battery System

- PBS, -PBS

Charging and Discharging capacity of Battery System

- PCC

Point of Common Coupling

- MPPT

Maximum Power Point Tracking

- EKF

Extended Kalman Filter

- FGI

Fuzzy Granulation Intervel

- MST

Minimum Spanning Tree

- LED

Light Emitting Diode

- CHIL

Control Hardware in loop

- VUTH

Upper Threshold Voltage

- VLTH

Lower Threshold Voltage

- PPVMAX

Maximum power from PV generation

- VMP

Voltage at maximum point

- IMP

Current at maximum point

- VOC

Open circuit voltage

- ISC

Short circuit current

1. Introduction

The gradual increase of carbon traces in the atmosphere due to burning of fossil fuels in conventional power plants has led to the development of modern power networks like microgrids with high penetration of renewable energy sources [1]. With substantial rise in electronic appliances utilizing DC power, the concept of a DC microgrid (DCMG) has gained importance [2]. Standalone DC microgrids support rural electrification in locations that do not have a centralized grid. Though microgrids are resilient, many issues such as power quality problems, stability, power flow control, energy management, protection issues, and integration of multiple DG units affect the grid compatibility and its efficacy. Especially, the implementation of microgrids pose some technical glitches at the protection level [3]. If microgrids are not sufficiently safeguarded in case of faults, the resilience is uncertain [4]. Hence the magnitude of fault current, protection blinding, false tripping, and unsynchronized reclosing are the common issues to be addressed [5]. In DC systems, the absence of zero crossing renders fault prediction inherently tedious and challenging. In the conventional protection strategies, relay settings need not be adaptable due to the presence of unidirectional power flow in various fault conditions whereas, for microgrid structures with bi-directional power flow, relay settings are to be synchronized in order to overcome the uncertainties such as false tripping and protection blinding [6]. Various protection schemes such as over-current protection [7], resistance-based protection [8], differential protection [[9], [10]], protection based on travelling waves [11] are recommended for the improvement of DC microgrid protection.

Protection strategies reported in literature have few technical challenges in protecting the DC microgrid. The initial spike in DC fault current is significant, and the rate of increase in fault current attributable to the integration of distributed generation, energy storage systems, and power electronic switches is also substantial. Also, the issues associated with the protection schemes due to more sensitivity to white noise and undetectable high resistance faults (HRF) [12] are still not addressed or unsolved. These issues necessitate rapid fault determination and interruption in order to evade the risk for electronic equipment and distributed generations [13]. A non-unit protection approach for DC microgrids based on the initial and subsequent derivatives of the current was proposed in Ref. [14]. The limitations of this protection scheme are lack of flexibility for various configurations and the dependency of derivative of line current and fault resistance. Additionally, this method is very sensitive to noisy currents. Subsequently in Ref. [15], consideration on both derivative and integral current were taken for ring DC type to limit the sensitivity towards current noise. In Ref. [16], Differential protection schemes were proposed for DC microgrid where the method requires communication infrastructure and synchronized measurements. Unsynchronized measurements may result in false tripping and dependency of communication leads to the requirement of high bandwidth communication for data transfer which is an additional cost to protection setup. The communication of relay blocking and tripping can ease the grid protection and automate the system without human intervention unless it becomes a permanent fault condition.

A fast fault detection scheme in Ref. [17] is employed by calculating and fixing the threshold using the relay current distortion which paves way to identify the DC faults in islanded DC microgrid. But to avoid repeated false tripping, concentration on relay coordination is most needed. Shabani et al. [18] proposed an adaptive communication-based over-current relay for fundamental and secondary protection of LVDC microgrid that works on distinct settings for the operating modes. For high-resistance faults, the over-current relay coordination performance is constrained. In contrast, Md Rifat Kaisar Rachi et al. [19] considers wave energy converter as renewable for standalone DC microgrid and the protection coordination is carried out by using inverse time current curve to identify the faults. However, it has not been analyzed for different fault scenarios, such as reverse fault conditions and high impedance faults. Abha Saxena et al. [20] proposed a rapid and efficient differential current measurement with decision tree algorithm for fault diagnosis and taxonomy respectively. In Ref. [21], the detection of fault location using support vector machine is proposed and the results are randomly sectionalized into subsets with respect to fault current. If the sample size is substantial, the algorithm takes longer time to function and the purpose of fault detection is underestimated.

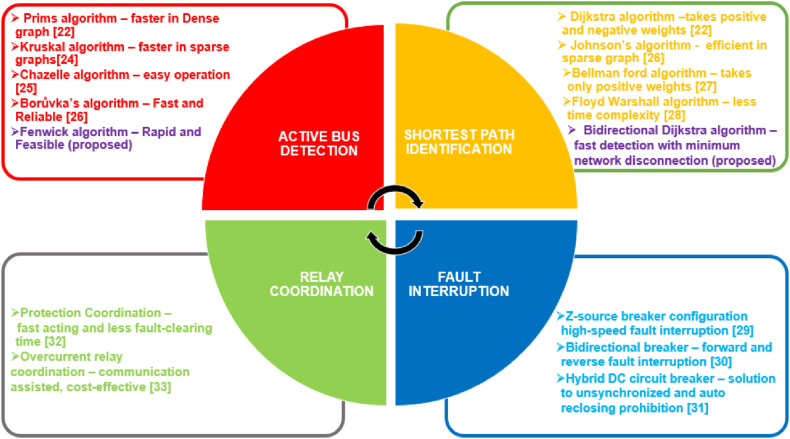

In contrast to above methods, active bus (AB) detection [22,24] and shortest path (SP) identification [22,[26], [27], [28]] are presented to facilitate a rapid fault interruption in power driven grids. In Ref. [22], implementation of data structure algorithm for protection of microgrid is carried out with the central controller. This controller finds the active buses using prims algorithm and minimal distance of faulted path using Dijkstra's algorithm. The time complexity calculation for Prims and Kruskal algorithm, are termed as O(V2) and O (E log V) respectively where V is the number of vertices. The time complexity may differ due to the insertion of values in queue. These schemes rely on adaptive relay setting and local measurements of the system. Also, usually the kilometric fault occurs in short line having a distance of about less than 5 kms. This occurrence of fault usually happens in DC microgrid as the entire islanded grid is constructed only within few kilometers of distance. In addition, the importance of protecting a grid against cross-country fault is much more essential. Fig. 1 shows the four stages of protection incorporated in various DC microgrid topologies in literature.

Fig. 1.

Literature on active bus and path identification in DC microgrid topologies [[22], [23], [24], [25], [26], [27], [28], [29], [30], [31], [32], [33]].

In recent research, machine learning approaches such as Bayesian neural networks, long short-term memory (LSTM) networks, and support vector machines (SVM) techniques are dominantly used in fault detection in DC microgrids because they yield accurate results. In Ref. [34], a recurrent neural network and a decision tree-based classifier are used to trace faults and detect disturbances in the system. While the fault identification study yields precise results, consideration of DC components is very limited. A hidden Markov model (HMM) based approach [35] is employed in diagnosing the Intel Arc system to accurately detect series arc faults in DC systems. The fault detection accuracy is 98.3 %, and the average detection time to discern the fault behavior is 57.1 ms, which is a strong indicator of performance. In Ref. [36], a comparison of various algorithms, such as SVC, Bernoulli Naive Bayes, Decision Trees, NC, and MLP, is conducted to detect and classify faults in DC systems. The analysis reveals that the MLP algorithm achieves almost 99 % efficiency in detecting the fault location. A DC microgrid is modeled [37] with PV panels, a V2G charging station, and an ESS to detect faults using CS and RT techniques combined with matrix features and an LSTM model. The DC faults are validated, resulting in fault detection within 1 ms with an accuracy of 93 %. In Ref. [38], a Transfer Learning scheme is utilized to generate faulted data, which is then trained without the need for any historical data. This approach was analyzed and verified in a microgrid. The fault detection and isolation method respond to faults within 1 ms, achieving an accuracy of around 90 %, as concluded after various fault examinations. Though the use of machine learning algorithms to protect DC microgrids is a recent advancement, considering the dynamics of DG, addressing simultaneous fault conditions and adhering to industrial standards are still in the early stages of development using machine learning techniques.

A Multi-Energy Ship microgrid structure with flexible voyage and thermal loads is proposed [39]. Various uncertainties are addressed using a two-stage RO approach to coordinate all onboard units across different timescales, which includes day-ahead scheduling and 30-min scheduling. The objective is to minimize the ship's operating cost throughout the voyage using a MILP algorithm and comparison is made through existing ship operating benchmarks. A empirical restoration approach for coordinating multi-stage dispatch decisions within a distributed MDS is assessed in Ref. [40]. Initially, the operation of the MDS is modeled, considering constraints from both power and thermal networks. To handle nonlinearities in the district thermal network model, auxiliary flow variables are introduced, significantly reducing computational burdens. Uncertainties from disasters, loads, and renewable generation outcomes are managed using a two-stage stochastic programming method, coordinating pre-restoration and real-time stage measures. To expedite the solution process, a distributed algorithm called progress hedging to splits the large-scale problem into diverse segregations and compared to traditional restoration benchmarks. These coordination techniques can be used to avoid false tripping and blinding of protection.

From the summary of literature, it is understood that, it is pivotal to identify the fault in microsecond when higher fault current magnitude injection take place in grid connected or islanded mode, in order to ensure the avoidance of electrical grid blackout. This led to the implementation of data structure and graph theory algorithms in microgrid for fault current prediction and faulted bus identification in lesser time interval. The need for predicting the specified branch and its faulted bus in short span resulted in the acquisition of cascaded algorithms to prevent sympathetic tripping and blinding of protection in efficient manner.

Thus, the new topology of Fenwick aided bidirectional Dijkstra algorithm is proposed for detecting kilometric and cross-country faults and the analysis is carried out in seven bus DC microgrid configuration to prove that the running time of the algorithm does not impact much with network configuration. The placement of DGs is based on the optimal location from where the maximum generation is produced and evenly distributed, DC load pattern and demand requirement [22]. The inbuilt PC with the proposed algorithm detects the active bus and shortest path for detecting the fault.

Fast prefix sum calculation of voltage and current derivative in nanoseconds and storage of data in stack in microseconds are prime factors for choosing Fenwick algorithm in order to find the active nodes (buses) in the network. Due to renewable integration in grids, both forward and reverse directions of voltage and current flow has to be considered. Bidirectional algorithm is one such algorithm that aids to determine the faults occurring in both the directions.

The paper consortium with novelty are as follows.

-

1.

An adaptive protection method is proposed using (i) Fenwick tree algorithm to find the active buses and (ii) bidirectional Dijkstra algorithm to determine the shortest path of the faulted point to the nearest DG using differential current data monitored by each relay interfaced with protection controller.

-

2.

The proposed protection method is implemented in a DC microgrid and tested its efficacy for various faulty conditions such as kilometric faults (Line-Line (L-L) or pole to pole fault, Line-Ground (L-G) or pole to ground fault), multi-faults, cross-country fault and reverse fault conditions.

-

3.

The proposed algorithm is tested and analyzed in control hardware in loop using real time simulator, considering the dynamics of distributed energy resources integration into the grid and load dynamics. This evaluation proves its effectiveness in maintaining system stability under various uncertainties.

This article is organized in the following way. In second section, the description on modeling the standalone seven bus DC microgrid system and the performance of distributed generation during fault is analyzed. The proposed algorithm and its functionality are postulated in third Section. The fourth section investigates and analyzes the supremacy of the proposed technique and fifth section extravagates comparison of different case studies using different algorithm with proposed work in simulation and control hardware in loop results using OPAL real time simulator. Conclusion and future improvements are discussed in sixth section.

2. Modeling and fault analysis of standalone seven BUS DC microgrid system

2.1. Modeling of 7 bus DC microgrid system

The seven-bus system comprises a 1 kW capacity of Photovoltaic (PV) system, 3.2 kW capacity fixed-speed Permanent Magnet Synchronous Generator (PMSG) based Wind Energy Conversion System (WECS), a 180 Ah capacity BESS, and DC resistive loads.

2.1.1. PV modeling

Among the renewable energy resources, the power from photovoltaic is most predominantly consumed by industries and local loads. Due to its facile installation and maintenance, this intermittent source is more preferrable in configuring microgrid structures. The output of PV cell depends on the insolation level and temperature coefficient. The PV array specifications are presented in Table 1.

Table 1.

Simulation parameters of standalone DC microgrid [2].

| Parameters | Ratings |

|---|---|

| DC grid Voltage | 400 V |

| Rated Power | 5 kW |

| Battery Capacity | 96 V, 180 A h. |

| PV Generation | 1 kW |

| Maximum Power from PV Generation (PPVmax) | 250 W |

| Voltage at maximum power (Vmp) | 31.1 V |

| Current at maximum power (Imp) | 8.05 A |

| Open circuit voltage of PV (Voc) | 37.8 V |

| Short circuit current PV (Isc) | 8.28 A |

| Irradiation Level | 100 W/m2 |

| Optimum temperature | 25 °C |

| 4 modules in series & 1 module in parallel | 4*1 |

| PMSG based WECS | 3.2 kW |

| Pitch angle (β) | 0° |

| Wind speed (V) | 9 m/s |

| Line Length | 1 km |

| Resistance | 121 mΩ/km |

| Inductance | 0.97 mH/km |

| Line Capacitance | 12 μF/km |

| Switching Frequency | 25 kHz |

| LC Filter | 47uH and 220 μF |

Considering Vpv = Voc, Np = 1 and Ns = 36, the PV module is designed [23] based on the given equation for IPV which can be written as,

| (1) |

where Iph represents the photo-current of a module, Irs denotes the reverse saturation current of a module, IPV signifies the output current of a PV module as given in Eq. (1), Io stands for the saturation current of a module, Ns indicates the number of cells connected in series and Rs is series resistance, respectively. Also, Io varies with temperature of a cell. Depending on the voltage and current requirement, the proposed PV array consists of 24 PV modules integrated to extract an output voltage of 400 V. The solar irradiance and cell temperature is maintained at 1000 W/m2, and 25 °C respectively. PV panels are connected with 4 modules in series and 1 in parallel connected to a common bus interfaced with DC – DC converter in which the output voltage is incremented. Based on Kirloskar solar panel specification, the PV has been modeled using MATLAB Simulink.

2.1.2. Wind modeling

In a PMSG, the permanent magnet in the rotor provides the field excitation. Considering a fixed speed wind turbine, the rated wind speed is taken as 12 m/s with pitch angle 0°. The aerodynamic model of a wind turbine is given by

| (2) |

| (3) |

where Pω is the wind power generated as mentioned in Eq. (2), ρ is air density, Ar is the blade area, V denotes the wind speed, Cp represents the power coefficient, S stands for Blade span Area, Tm is mechanical torque as given in Eq. (3), α signifies the angle of attack, β indicates pitch angle and λ specifies tip speed ratio. The torque generated by the wind turbine is then directed to the PMSM generator, which converts the mechanical energy to 3-phase electrical energy as shown in Fig. 4. The fixed-speed PMSG wind turbine is designed to produce a filtered and rectified output of 400 V.

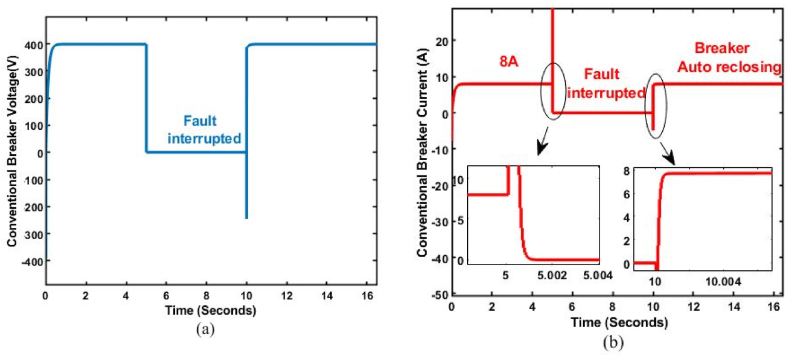

Fig. 4.

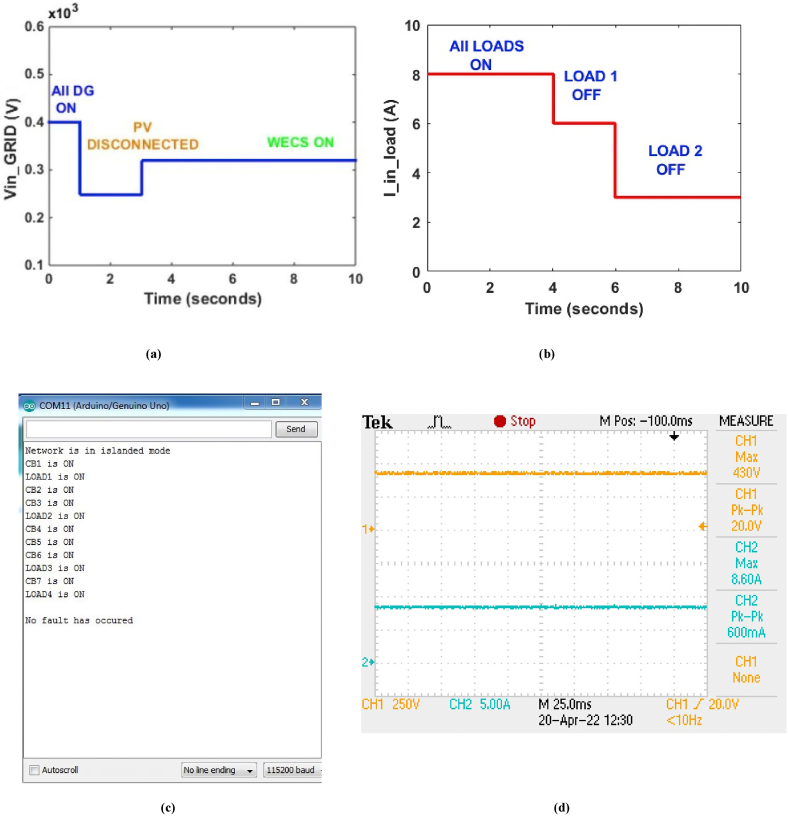

(a) Voltage and (b) Current response of conventional bidirectional breaker.

2.1.3. Battery modeling

The Lithium-ion battery pack of 180 A h with bidirectional converter is designed with state of charge (SOC) of 80 % for the microgrid configuration of 400 V. Battery System (BS) works based on energy demand, if the load increases and goes beyond the supply then BESS supply power to meet the required demand. For power conversion applications, a bidirectional DC to DC converter is used. A DC source is connected to the sepic converter to charge the battery using bidirectional converter and the battery discharging takes place when the DC input of sepic converter is disconnected. In order to mitigate the risks associated with over-charging and over-discharging, it is crucial to meticulously control the SOC of the BS. The SOC of the BS, denoted as SOCBS, is calculated using Eq. (4), where BSREFCAP represents the reference capacity of the BS, VBS is the voltage of the BS, and SOCBS is constrained within the limits of SOCBS_MIN and SOCBS_MAX as defined in Eq. (5). The power of the BS, denoted as PBS, indicates charging when positive and discharging when negative. Charging and discharging powers of the BS are restricted by PBS_MAX and -PBS_MAX, respectively, as stated in Eq. (6), to safeguard the BS from operating at excessively high current levels [44]. The battery power and terminal voltage of battery are estimated using Eqs. (7), (8).

| (4) |

| (5) |

| (6) |

The battery power can be estimated as

| (7) |

Since the battery terminal voltage is

| (8) |

2.1.4. Overall DC microgrid modeling

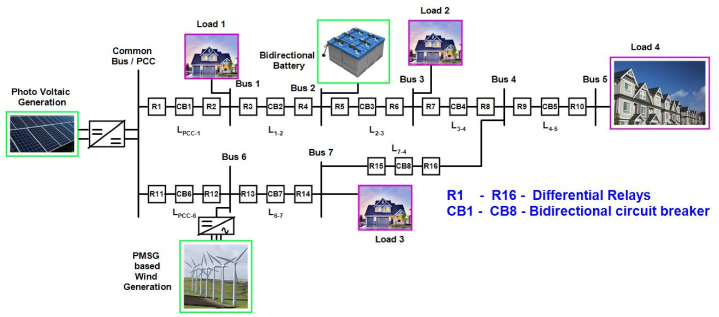

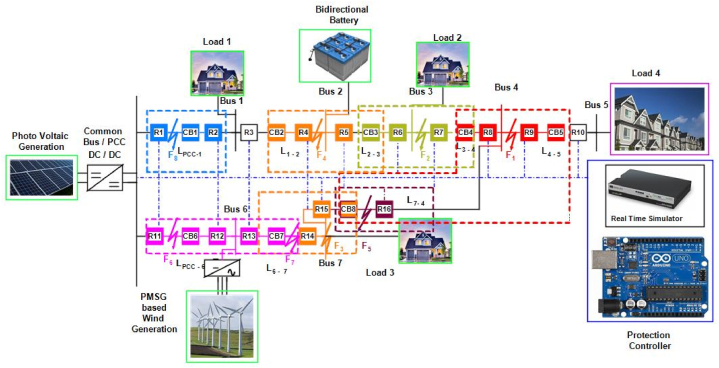

The proposed seven-bus DC microgrid system is illustrated in Fig. 2. The Common bus/Point of common coupling (PCC), connected with the PV and DC-DC converter, facilitates connectivity with all nodes present in the grid. The transmission line between every bus is considered to be 1 km apart. Buses 1, 3, 5, and 7 are connected to loads to distribute the generated power. Additionally, bus 2 is linked to a bidirectional battery system for energy storage, and bus 6 is integrated with PMSG based WECS and a rectifier for effective interfacing. During normal operating condition, the power flows from common bus interfaced with PV towards Bus 5 in feeder 1 and the common bus to bus 7 in feeder 2. When PV power is unavailable, the battery discharges, redirecting power flow from Bus 2 to Bus 1 via the common bus. Table 1 displays the parameters of the standalone DC microgrid.

Fig. 2.

Modelling of proposed Seven bus DC microgrid system.

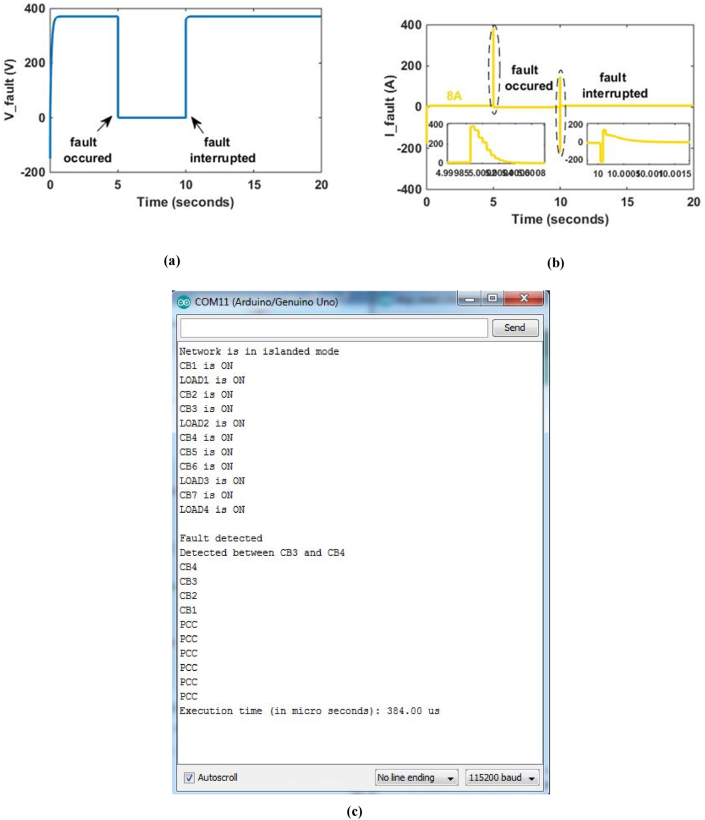

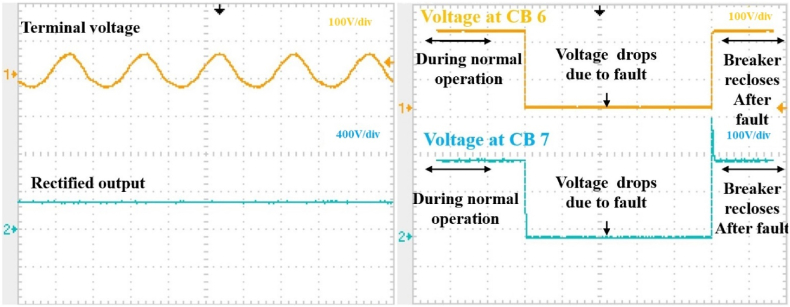

2.2. Fault analysis

The common faults encountered in DC systems include line-to-line and line-to-ground faults. Fig. 3 illustrates the implementation and operation of a conventional bidirectional breaker in the seven-bus DC microgrid system. In the event of a line-line fault near bus 4, the bus 4 becomes inactive, redirecting the fault current along three paths: the transmission lines L4-5, L3-4, and L4-7. Consequently, the corresponding conventional bidirectional breakers CB5, CB4, and CB8, located in these transmission lines, are triggered to operate and reclose. Notably, CB5 interrupts the fault in 2 ms, followed by reclosing within 3 ms as depicted in the voltage and current responses of the conventional bidirectional breaker [45] illustrated in Fig. 4(a) and (b). The total duration for fault detection and interruption by conventional bidirectional breakers, currently estimated at around 5 ms, is regarded as relatively prolonged. Additionally, these breakers trip based on fixed thresholds in relay settings, lacking the capacity to dynamically adapt to changes in noise levels, diverse fault conditions, or dynamic fault resistances. The efficacy of a protection strategy is defined by its ability to minimize network disconnection and fault interruption time amidst fault scenarios. However, due to the absence of a grid monitoring system, the breakers near the faulted zone trip off upon fault occurrence. This limitation underscores the drawback of implementing conventional bidirectional breakers without grid monitoring or protection controllers.

Fig. 3.

Fault response of conventional bidirectional breaker when implemented in seven bus DC microgrid.

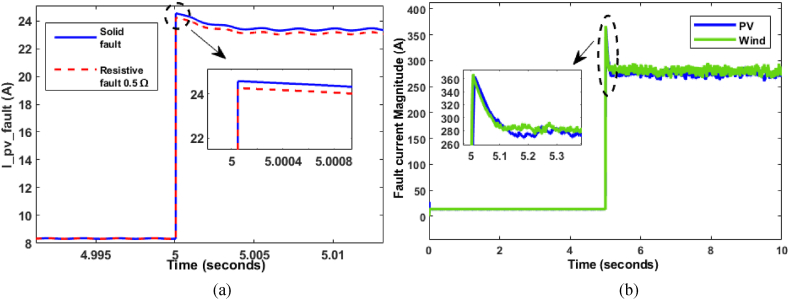

In the event of a line-to-line fault occurrence in DC microgrid, fault currents in PV units often closely resemble normal operating currents, particularly in maximum power point tracking (MPPT) mode, which complicates fault identification solely based on current levels [42]. In the case of a line-to-ground fault within the DC microgrid, the current from PV and PMSG based WECS to the fault becomes negligible, posing challenges in fault detection for such occurrences. In order to ascertain the peak fault current values associated with PV and PMSG based WECS, various faults are insisted at the terminals of both PV and wind generation. As illustrated in Fig. 5 (a), the peak fault current magnitude during solid and resistive fault are 24 A and 23 A respectively. Additionally, in the event of a line-to-line fault, peak fault currents surge to 360 A for both PV and PMSG based WECS as shown in Fig. 5(b). This consistent approach allows for the meticulous analysis of fault current magnitudes, thereby facilitating the estimation of adaptive relay settings for solid and resistive fault scenarios within PV and PMSG based WECS system.

Fig. 5.

Line to line fault analysis (a) PV current (b) Fixed speed PMSG based WECS current.

3. Rationale of the proposed work

3.1. Necessity for finding the active bus and shortest path

To enhance the accuracy of fault location and the minimize the fault interruption time within the DC microgrid, it is crucial to determine the active bus (generation bus or load bus) and identify the shortest path from the faulted area to the nearest operating distributed generation (DG). By understanding the network topology through data structure algorithms, it becomes possible to optimize the rerouting of power flows, thereby reducing losses and enhancing overall system efficiency. Consequently, the identification of active buses and shortest paths contributes to the reliable and resilient operation of the microgrid, reinforcing its capacity to deliver stable and sustainable electric supply.

3.2. Existing algorithms to determine the active bus and shortest path

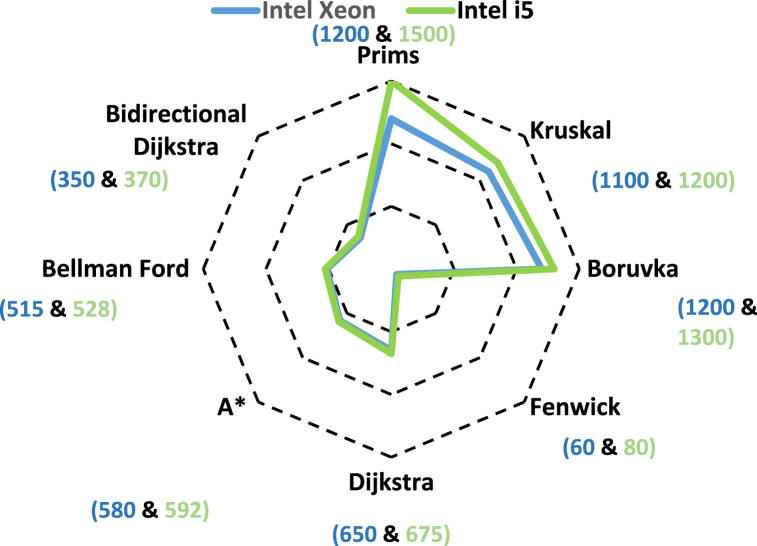

The existing algorithms to identify the active bus and shortest path from faulted point to nearest distributed generation for AC microgrids are detailed in Refs. [[22], [23], [24], [25], [26], [27], [28]]. In Ref. [22], Prim's algorithm is utilized to identify active nodes/buses, while the Floyd-Warshall algorithm is implemented to determine the minimal distance path from the fault to the nearest distributed generation. This involves computing all potential minimal distance paths and subsequently comparing them to identify the optimal route, which may result in a longer fault interruption duration. In Ref. [24], an approach to ascertain the fault interruption with minimal number of loads disconnection is emphasized in radial network topology employed to identify active buses using Kruskal's and Prim's algorithms. Fault clearance with minimal disconnection of loads is achieved through Dijkstra's and Floyd-Warshall algorithms. The study indicates that Prim's algorithm performs more efficiently in dense graphs, while the Floyd-Warshall algorithm excels in sparse graphs. Although the effectiveness of the graph theory algorithm has been demonstrated in extensive networks, real-time testing utilizing Typhoon or Opal RT hardware-in-loop is imperative to assess system efficiency under various fault scenarios. Table 2 presents the processor running times for detecting the active bus and shortest path in existing literature studies focusing on AC networks. It offers a comprehensive analysis of fault location and interruption times for established algorithms, including Prims, Kruskal, Boruvka, Dijkstra, Floyd-Warshall, and Bellman-Ford algorithms.

Table 2.

Existing protection algorithms in literature for active bus and shortest path identification for AC network.

| ALGORITHM | AC MICROGRID |

||||||

|---|---|---|---|---|---|---|---|

| Active bus identification |

ALGORITHM | Shortest path Identification |

|||||

| BUS NETWORK |

PROCESSOR USED |

EXECUTION TIME (μs) |

BUS NETWORK |

PROCESSOR USED |

EXECUTION TIME (μs) |

||

| Prims [ 22] | 21 Bus [22] | AMD A10 | 15000 | Dijkstra's [24] | 39 Bus | Intel i5 | 293 |

| Intel i3 | 13000 | Intel Celeron | 903 | ||||

| 39 Bus [24] | Intel i5 | 622 | |||||

| Intel Celeron | 1257 | ||||||

| Kruskal [24] | 39 Bus [24] | Intel i5 | 666 | Floyd Warshall [24] | 39 Bus | Intel i5 | 4369 |

| Intel Celeron | 1635 | Intel Celeron | 21806 | ||||

| Boruvka [26] | 7 Bus [28] | AMD A10 | 15000 | Bellman-Ford [27] | 40 Bus | Intel i5 | 28056 |

| Intel i3 | 13000 | Intel Celeron | 29543 | ||||

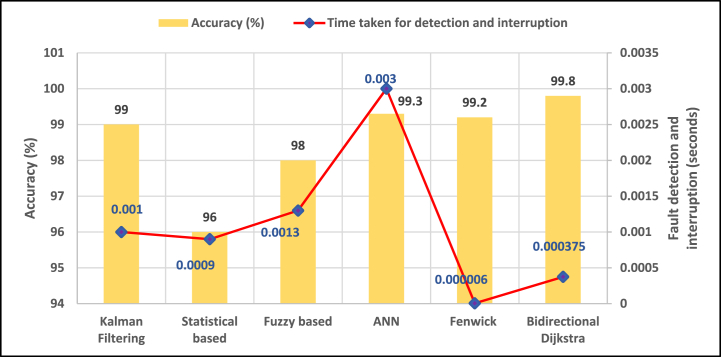

In [46], an approach utilizing the Extended Kalman filter (EKF) is introduced for the exclusive detection of various DC faults from current signals within the MVDC networks. The current measurement from positive and negative poles undergoes processing by the EKF, leading to the generation of cumulative residuals and the DC distortion factor as indices for fault detection. However, an analysis of the effects of grid assets is not included in this study. The authors of [47], presents an adaptive scheme based on statistical Fano factor analysis for the precepting and Sorting of faults, aimed at enlightening sensor tolerance capability where this method utilizes line end current datas. In Ref. [48], a method for diagnosing line faults based on fuzzy granulation interval (FGI) with a reduced number of sensors is introduced. Specifically, it relies on positive pole current and bus-side voltage measurements shared with the converter controller. Additionally, a new NPG fault detection index interval range is developed, utilizing the disparity between interval boundaries. This method accurately identifies abnormal post-fault voltage fluctuations, enabling the detection of negative-to-ground faults within 1.5 ms. However, its effectiveness in networks other than ring structures remains uncertain. The Pseudo-data-driven-based scheme [49] and ANN-based scheme [50] exhibit similar functions, as demonstrated in Table 3. Both methods demonstrate moderate fault action prediction, which consequently leads to prolonged fault current interruption times. Therefore, these parameters are duly considered in the development of the proposed novel algorithm-based method for fault detection and interruption. Table 3 gives the detailed conceptual information on the existing benchmark strategies for DC network.

Table 3.

Existing protection algorithm in literature as benchmark strategies for DC network.

| Parameters | Kalman Filtering based [46] | Statistical based [47] | Fuzzy based [48] | Pseudo data based [49] | ANN [50] |

|---|---|---|---|---|---|

| Fault Action | Rapid | Moderate | Rapid | Moderate | Moderate |

| Time taken for detection and interruption | 1msec | <1 ms | <1.5s | 75s | 3 ms |

| Computational efficiency | High | High | High | Moderate | High |

| System resilience to fault | ✓ | ✓ | ✓ | ✗ | ✗ |

| Noise taken in to reckoning | ✓ | ✓ | ✓ | ✓ | ✓ |

| Assets contemplation | ✗ | ✗ | ✓ | ✗ | ✗ |

| Precision Accuracy (%) | 99 | 96 | 98 | 97.5 | 99.3 |

| Applicable Topology | All Topology | Only Ring | Only Ring | Only Meshed | Only Meshed |

3.3. Uniqueness of proposed algorithm

In the proposed work, two new algorithms are implemented for active bus and shortest path identification. The Fenwick algorithm is employed for active/inactive bus detection due to its advanced features, which include summing up the preceding voltage and current values and its derivatives with respect to time and saving the data for every nanosecond. This makes the fault prediction easier by setting a threshold for every microsecond in a range of 10 times the voltage and current differential value stored in the system. The system can make decisions autonomously based on the program fed into the protection controller for the fault scenarios such as cross-country faults, multi fault analysis and kilometric faults. As the existing literature [[22], [23], [24], [25], [26], [27], [28], [29]] does not give importance of reverse fault current, cross-country faults and multi fault analysis, this work takes an initiative for detecting forementioned faults which occurs in DC microgrid.

The bidirectional Dijkstra algorithm is used to detect minimal distance from faulted point to nearest renewable resource and the reverse fault current caused by DG dominance. The proposed work is one of the initiatives to attain the Sustainable Development Goal in a smart grid environment (SDG 7 access to affordable, reliable, sustainable and modern energy for all).

3.3.1. Fenwick – background

The Fenwick tree was proposed by Peter Fenwick in 1994 and it efficiently performs cumulative sum queries and updates on an array. It. The primary advantage of the Fenwick tree is its ability to handle updates and queries in O(log n) time complexity, where n is the size of the array. The key insight behind the Fenwick tree is exploiting the binary representation of indices to efficiently calculate ranges. Each index in the Fenwick tree corresponds to a range of elements in the original array, and the cumulative sum at each index represents the sum of elements in that range.

3.3.1.1. Representation

A Fenwick tree is represented as an array BIT [] of size n + 1, where n is the size of the original array. This extra space is used to store cumulative sums.

3.3.1.2. Construction

To construct a Fenwick tree, we initialize all the elements of the BIT[] array to 0. Then, for each element arr[i] in the original array, we perform a point update on the Fenwick tree by adding arr[i] to appropriate positions to maintain the cumulative sum property.

3.3.1.3. Point update

Updating an element in the Fenwick tree involves updating its value and also updating other elements in the tree to maintain the cumulative sum property. This is done by adding the new value to the current element and then updating subsequent elements whose ranges overlap with the updated element. The index to update for element arr[i] is calculated using bitwise operations.

3.3.1.4. Range query

Querying the cumulative sum of elements in a range involves traversing the Fenwick tree and summing up the values of specific elements. The range sum query can be performed efficiently by starting from the index corresponding to the right endpoint of the range, then subtracting the cumulative sum of elements before the left endpoint of the range.

3.3.2. Bidirectional Dijkstra algorithm – background

The Bidirectional Dijkstra Algorithm represents an enhancement of Dijkstra's algorithm, which is used to find the shortest paths from a single source vertex to all other vertices in a weighted graph with non-negative edge weights. The Bidirectional Dijkstra Algorithm improves the efficiency of Dijkstra's algorithm by running two simultaneous searches, one from the source vertex towards the target vertex and the other from the target vertex towards the source vertex, until the two searches meet. This can significantly improve the performance, especially in graphs with a large number of vertices or where the distance between the source and target vertices is relatively large.

Initialization: Initialize two priority queues (or heaps), one for the forward search (from source) and one for the backward search (from target). Make the distance as 0 when pointing towards source vertex in the forward search priority queue and infinity in the backward search priority queue. Similarly, make the distance as 0 to the target vertex in the backward search priority queue and infinity in the forward search priority queue. Begin the forward search from the source vertex and the backward search from the target vertex.

Search Iteration: In each iteration, expand the vertex with the smallest tentative distance (computed so far) from both the forward and backward priority queues. Update the tentative distances and parent pointers if a shorter path is found. Check for any overlap between the vertices expanded by the forward and backward searches. If an overlap is found, it indicates a potential shortest path and termination condition.

Termination: The algorithm concludes its execution when the searches converge at a vertex (or a shared set of vertices) that has been explored by both searches. This means that the shortest path between the source and target vertices has been found.

Path Reconstruction: Once the searches meet, reconstruct the minimal distance path from the source to the target vertex by following the parent pointers from the meeting vertex towards the source and from the meeting vertex towards the target.

3.3.3. Step by step algorithm functionality of active bus and shortest path identification in seven bus DC microgrid network

The Fenwick tree algorithm begins by selecting a starting bus as a connected node, noting the distances between buses as weights. The direction of power flow establishes the 7-bus system as a directed graph.

Step 1: Defining all the buses within the graph.

Step 2: Initially, the minimum spanning tree is formatted as empty, meaning all buses are unconnected. The algorithm iterates through the graph, add up the current value with the next node and calculates the prefix sum to find the closest bus.

Step 3: Simultaneously, the Point Update and Query functions stack the updated values of differential voltage and current in the network in order to fix up relay threshold setting.

Step 4: This process repeats until the last bus is reached. The output returned is the Minimum Spanning Tree (MST) with a time complexity of O(log n)

The detailed steps of Bidirectional Dijkstra algorithm are.

Step 5: On continuation to Fenwick network configuration datas, the active bus and inactive bus are noted and the iteration starts from the inactive bus.

Step 6: Proceed with all the weighted edges, which represent distances connected to the common bus, and predict the smallest weight as the distance from fault point to nearest operating distributed generations. As per the objective function of the shortest path problem formation of Bidirectional Dijkstra algorithm which is given in the below equation (4), the shortest path from the faulted point is calculated

| D = min(P) | (4) |

where, D - distance from the point of fault occurrence to DG and P - number of paths between each bus.

Step 7: Labeling the least faulted path connecting the bus that finally trips the corresponding breaker in the faulted path

Step 8: Repeat steps 2 and 3 continuously until all the buses becomes active using auto reclosing of breakers after the fault.

Step 9: Repeats the same procedure in reverse search path for determining reverse fault conditions, thereby, the corresponding breaker trips. This demonstrates that the algorithm functions effectively for both forward and reverse fault conditions by utilizing backward search to determine the shortest distance for reverse current flow in the grid.

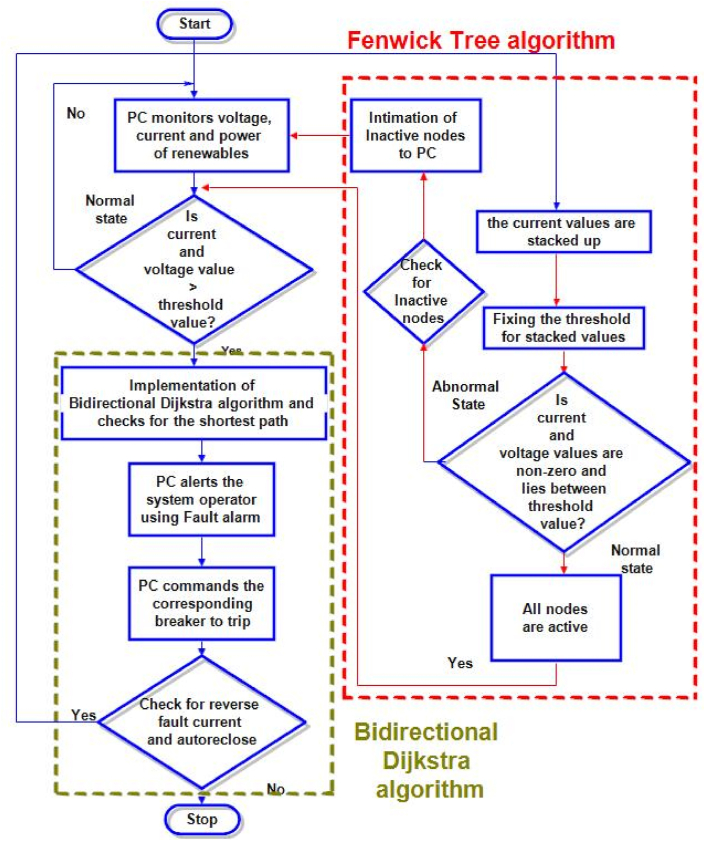

The suggested Fenwick aided bidirectional Dijkstra method provides precise solution for fault detection and interruption with minimum network disconnections. The algorithm detects both kilometric or line faults, bus faults, cross country fault and reverse fault based on the adaptive relay setting. Fig. 6 explains the algorithm functionality of active bus and shortest path identification. The protection controller monitors the voltage and current of each distributed generation in the network. Meanwhile, the line current difference measured using differential relays present at two ends of the line and the line current difference are checked by protection controller. Further, the difference in line current lies below or above the threshold value; the Fenwick tree algorithm simultaneously identifies the status of active and inactive buses. Thereby, the shortest path is identified using the bidirectional Dijkstra algorithm from the commands of protection controller on occurrence of fault. The role of the protection controller within the seven-bus system is facilitated by the proposed algorithm implemented in Python scripts, aimed at achieving an effective bidirectional response in the relays. Subsequently, the relays operate in accordance with this response, which is subsequently portrayed on the fault identification board through an Arduino controller. The adaptive relay setting works based on the commands from the protection controller and if there's any abnormalities found, immediately the inactive buses are noted by Fenwick and fault location is estimated, thereby the shortest path is identified by bidirectional Dijkstra algorithm and the corresponding breaker trips. These operations are orchestrated within the protection controller framework, employing Python code to exemplify their reliability and adaptability.

Fig. 6.

Proposed algorithm functionality of active bus and shortest path identification.

4. Results and discussion

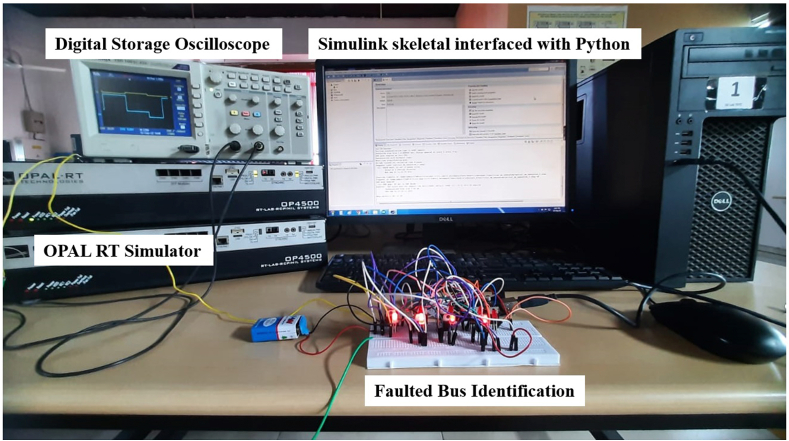

This study is further advanced using Opal RT real-time simulator, employing an external control strategy known as Control Hardware in Loop (CHIL) testing to analyze the system performance in conjunction with the proposed algorithm. The simulation schematics, developed in MATLAB and interfaced with Python, are transmitted to a host system configured with an Intel Xeon processor, which is connected to the Opal RT simulator. The hardware mode of protection controller is an Arduino UNO microchip (AVR) serves as a connector between the host system and the fault identification demonstration board. The Arduino controller transmits signals externally to a breadboard setup to define the status of active and inactive buses for every nanosecond based on the proposed algorithm. An external control circuit, featuring LEDs to denote active bus identification, operates based on commands from a protection controller interfaced with a Python program. The visualization of the relay signals of seven bus system are demonstrated in the breadboard setup using light emitting diode (LED) and voltage regulator (LM708) as in Fig. 7.

Fig. 7.

Control Hardware in loop testing of proposed algorithm implemented in Opal RT.

4.1. Performance under no fault cases

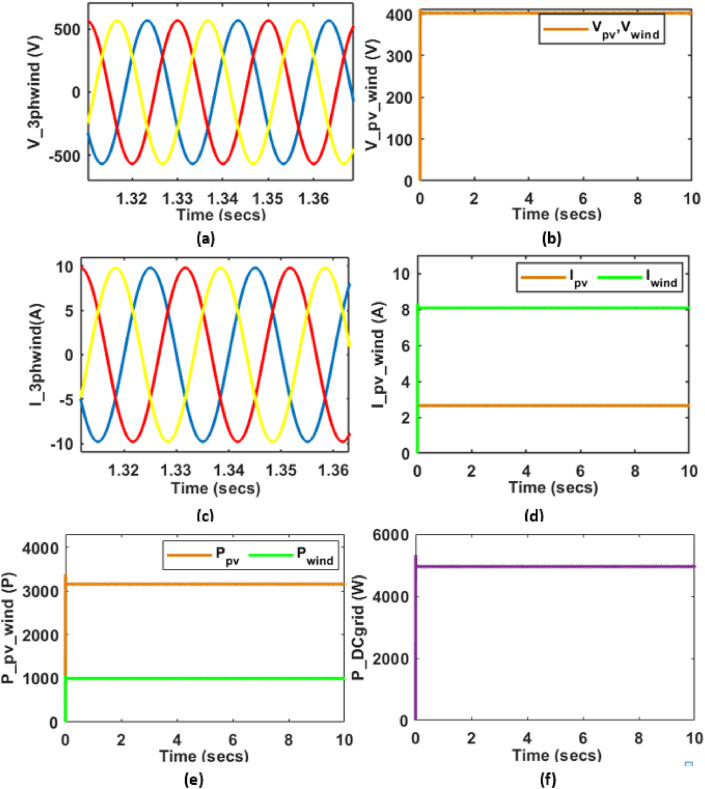

During normal operating conditions, the voltage, current, and their differences are monitored at each bus and transmission line within the grid and the simulation results reflecting the normal operating conditions of Distributed Generators (DGs), BS and the DC grid are illustrated in Fig. 8. Specifically, the three-phase voltage and current of PMSG based WECS are presented in Fig. 8(a) and (c), while the DC voltage and current of PV systems, as well as the rectified DC voltage and current of PMSG based WECS, are depicted in Fig. 8(b) and (d), respectively. Furthermore, the extracted power from PMSG based WECS, PV systems, and the DC grid is demonstrated in Fig. 8(e and f).

Fig. 8.

Simulation results of seven bus system during normal operating conditions (a)PMSG WECS 3Φ voltages (b) rectified DC voltage of PMSG WECS and PV (c) PMSG WECS 3Φ current (d) rectified DC current of PMSG WTG and PV (e & f) Power from PMSG WECS, PV & DC grid.

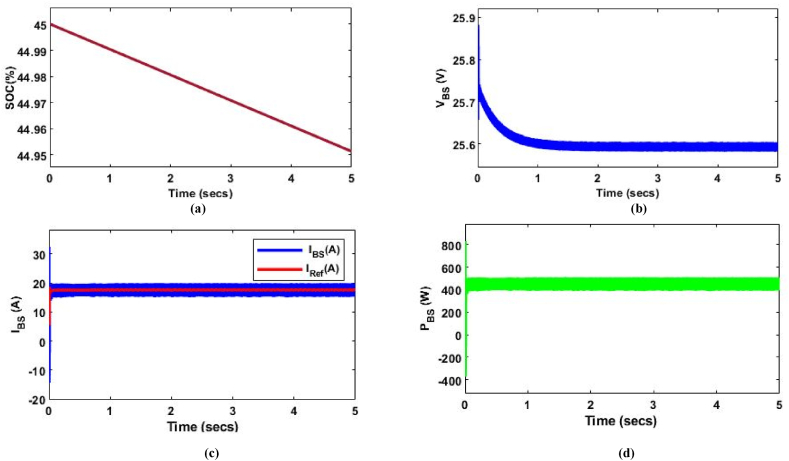

Also, this competent protection algorithm is framed to discriminate between a fault and normal operating conditions. The scenarios devoid of faults, encompassing load uncertainty, DG uncertainty, and DG outages, were simulated within a 7-bus DC system, with results depicted in Fig. 10. Specifically, the SOC in percentage, battery voltage, battery current and battery power during discharging conditions is illustrated in Fig. 9 (a, b, c & d). The consideration of DG and load uncertainty manifests in various scenarios, including the presence of all DGs, PV disconnection, and grid operation solely relying on PMSG based WECS are shown in Fig. 10 (a & b). Notably, the outcomes of the Fenwick-assisted bidirectional Dijkstra algorithm from the protection controller during normal operating conditions, along with real-time simulator results projected through the DSO, are displayed in Fig. 10 (c & d). Consequently, the Fenwick tree algorithm proficiently detects active buses within the network, leading to the determination that no fault is detected as in Fig. 10 (d).

Fig. 10.

No fault cases (a) DG uncertainty (b) Load uncertainty (c) Results of Fenwick assisted bidirectional Dijkstra algorithm from protection controller (d) Real time results depicted in DSO using OPAL RT.

Fig. 9.

No fault cases (a) SOC Percentage (b) Battery Voltage VBS (c) Battery current IBS (d) Battery Power PBS.

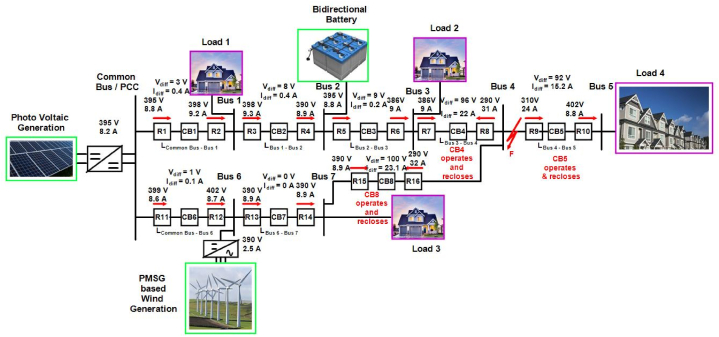

4.2. Performance under kilometric faults (line-line faults)

A Line-to-Line fault, denoted as F1, occurs at the L4-5 segment, which interfaces with relays R9 and R10 in a seven-bus islanded DC microgrid, as illustrated in Fig. 11. In this setup, the inactive buses are automatically identified as the LEDs turn off based on the voltage and current threshold values calculated by Fenwick tree, as depicted in the faulted bus identification setup shown in Fig. 7. The voltage and current present in R8 and R9 are 330 V and 22 A, and 310 V and 24 A, respectively. The relay voltage and current difference, and its threshold are calculated using the Fenwick tree algorithm, followed by the identification of the shortest path using the Bidirectional Dijkstra algorithm. The conventional protection schemes trace the fault path as mentioned in Table 4: Path 1 from Bus 4 - Bus 7 - Bus 6 - common bus, with a path weight of 3; 2) from Bus 4 - Bus 3 - Bus 2 - Bus 1 - common bus, with a path weight of 4. In the 7-bus DCMG network, the suggested algorithm identifies the active buses as Bus 3, 2, and 1 and determines the shortest path as 4-7-6-common bus, with a path weight of 3. In the identified shortest path, the corresponding circuit breaker interrupts the fault before it affects the nearest operating DG (PMSG based WECS), which is verified through Opal RT control hardware in loop testing.

Fig. 11.

Various fault analysis in Seven bus DC microgrid system.

Table 4.

Existing protection algorithm in literature as benchmark strategies for DC network.

| S. No. | Fault | Fault Current Path | CB operates and recloses |

|---|---|---|---|

| 1 | Line to Line fault F1 | Fault Path 1: Bus 4 - Bus 3 -Bus 2 -Bus 1 - Common Bus | CB4, CB5 |

| Fault Path 2: Bus 4 - Bus 3 -Bus 7 -Bus 6 - Common Bus | CB8 | ||

| 2 | Line to Ground fault F2 | Fault Path 1: Bus 3 - Bus 2 -Bus 1 - Common Bus | CB3 |

| Fault Path 2: Bus 3 – Bus 4 -Bus 7 -Bus 6 - Common Bus | CB4 | ||

| 3 | Multi fault F3 & F4 | Fault Path 1: Bus 1 - Common Bus | CB2, CB3 |

| Fault Path 2: Bus 7 -Bus 6 - Common Bus | CB8 | ||

| 4 | Fault with different resistances F5 | Fault Path 1: Bus 4 – Bus 3 -Bus 2 - Bus 1 - Common Bus | CB4, CB5 |

| Fault Path 2: Bus 7 -Bus 6 - Common Bus | CB8 | ||

| 5 | Converter Effects during F6 & F7 | Fault Path 1: F6 - Common Bus | CB6 |

| Fault Path 2: Bus 6 - Common Bus | CB7 | ||

| 6 | Line to Line Fault F8 with Variation in different irradiation level of PV | Fault Path: R1 – Common Bus | CB1 |

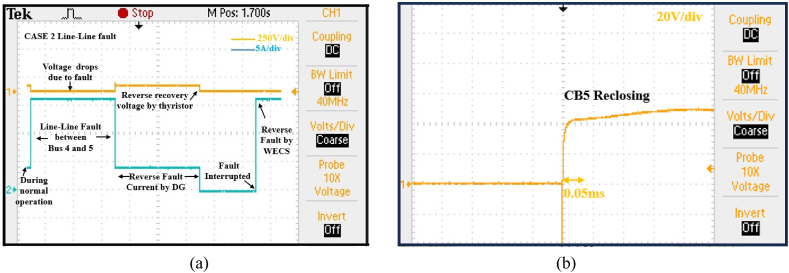

The DSO results, as depicted in Fig. 12, evaluate the algorithm-based protection which illustrates the voltage drops to zero during the occurrence of the line-line fault, followed by the manifestation of reverse recovery voltage in the DC transmission line. The fault current is promptly interrupted by the proposed algorithm, leading to the trip of its corresponding breaker, CB5 and recloses at 0.05 ms. Consequently, it effectively interrupts the reverse fault triggered by other DGs and PMSG based WECS, substantiating its efficiency and reliability.

Fig. 12.

Results of (a) Line – line Fault detection and (b) CB5 Breaker Reclosing in Seven bus DC microgrid system.

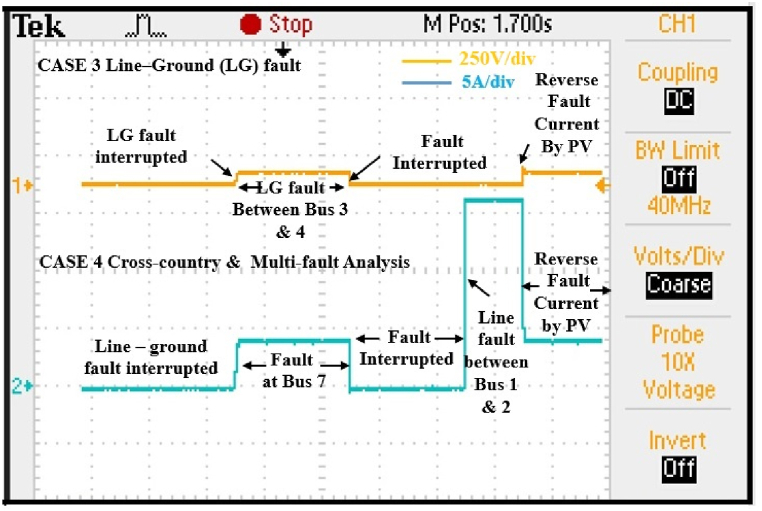

4.3. Line-ground faults

To validate the proposed algorithm functionality for Line to ground fault F2 on the line L3-4, a fault resistance (Rf = 0.1Ω) were simulated and it is depicted in Fig. 11. The current difference between the lines is measured using DC current differential relays R7, R8 and R5, R6 which senses the fault and the protection controller simultaneously act based on the results from Fenwick tree algorithm in finding active nodes. Thereby, it determines the corresponding shortest path as ‘Bus 3-2-1-common bus’ which concludes the least distance as 3 and it is identified by bidirectional Dijkstra algorithm. The voltage response during line to ground fault is portrayed in Fig. 12(a). As depicted in Fig. 13(b and c), the occurrence of fault interruption at t = 5.000384 s signifies the operational speed of the proposed algorithm in detecting the L-G fault within 384 μs, demonstrating notably rapid responsiveness. The real time result from Opal RT control hardware in loop testing, the exact location of fault is determined and the status of the breaker with interruption time is clearly portrayed in Fig. 13(c). As the proposed algorithm works for reverse fault that is contributed by DGs, is also interrupted by bidirectional Dijkstra algorithm as case 3 shown in Fig. 14. The fault current contribution shown in Fig. 15 case 3 results in summing up of actual fault current from F2 and fault current produced by DGs. On comparing with simulation results, the fault current difference reaches the value of 190 A in a shorter period (within 10 ms), and it is further interrupted by circuit breaker CB4 as portrayed in Fig. 13 (b). The reclosing operation of breaker after interruption settles to a nominal value of 8 A. The systems line current in L4-5 is around 8.8 A. So, the peak fault current is almost 25 times the nominal value.

Fig. 13(a).

Voltage and (b) current profile of Seven bus DC microgrid system during Line – ground fault (c) Results of Line – ground fault detection by protection controller in Seven bus DC microgrid system.

Fig. 14.

Simulation and real time results of Multi - fault and cross – country fault detection in Seven bus DC microgrid system.

Fig. 15.

Results of proposed algorithm implemented in Opal RT (a) Detection of PV noise and its resulted voltage at CB1 (b) Detection of Wind noise and its resulted voltage at CB7.

4.4. Performance under multi-faults and cross-country faults

The multi fault scenario is addressed in Fig. 11 where the initial occurrence of line to ground fault is interrupted followed by fault at bus 7. The cross-country faults are the faults which occurs at two lines or two buses or with fault at line and bus simultaneously. The seven-bus system is analyzed with fault F3 and F4 at bus 7 and line to line fault at L1-2 simultaneously where the fault chooses downstream path. Notably, there are two ways to reach the PV source. Path 1 follows Bus 1- common bus with a resultant distance of 2 and Path 2 follows Bus 6- common bus with a resultant distance of 2. As the distance are same for two paths, it reconsolidates to provide the tripping signal to both CB2 and CB7 simultaneously. The fault current due to F3 at bus 7 is interrupted by CB7 within 14 μs and the fault due to F4 at L1-2 is interrupted by CB2 within 10 μs. These results are portrayed in Fig. 14. Though this fault condition is rare in case, the proposed algorithm works faster in detecting and interrupting the fault in less than 25 μs? The proposed algorithm works for forward and reverse fault condition where the existing PV produce reverse fault of 4 A and this has been identified and interrupted by proposed algorithm with corresponding breaker CB2.

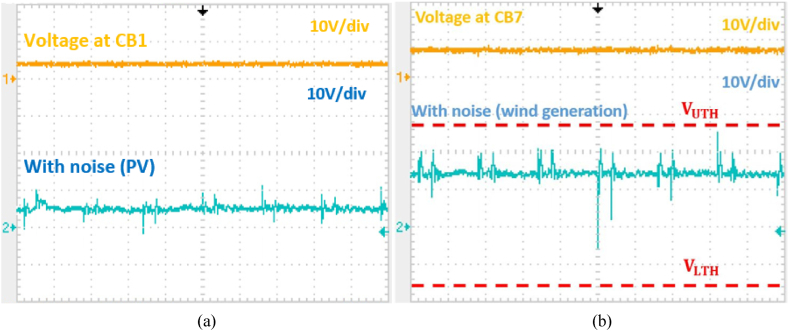

4.5. Performance under noise

In real-time scenarios, the contemplation of an ideal system devoid of noise proves unattainable. Hence, it becomes imperative to scrutinize the influence of noise on fault detection methods. Despite of many dynamic factors that replicates the intermittency of renewables in simulation, white noise in wind generation is most dominant constraint of DER's transient analysis [41,43]. The noise analysis has been conducted, demonstrating the adaptability and resilience of the system with the proposed algorithm. Based on real-time specifications of PV and wind generation, the maximum noise-withstanding capability is determined to be 35 db. Subsequently, subjecting the system to white Gaussian noise intensities of 25 dB and 35 dB applied to PV and PMSG based WECS respectively, yields values falling within the upper threshold (VUTH) and lower threshold (VLTH) boundaries. Consequently, the effectiveness of the proposed algorithm is evidenced by its ability to differentiate between noise presence and fault occurrence. Fig. 15(a and b) illustrates the voltage outcomes at CB1 and CB7, showcasing the efficacy of the proposed algorithm in discerning discrepancies between noise stemming from PV and wind sources and actual faults. Furthermore, upon surpassing these limits, the proposed algorithm initiates necessary actions, considering both voltage and current dynamics.

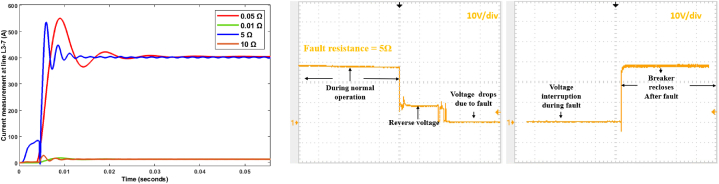

4.6. Performance analysis with different fault resistances

In DC microgrids, line-to-line and line-to-ground faults exhibit low impedance and high impedance, respectively. Nevertheless, line-to-line faults have increasingly manifested as more severe and detectable compared to line-to-ground faults. The protective devices must be coordinated to address both types of faults, considering the distinct fault characteristics and threshold settings [42]. The system is subjected to varying fault resistances for low-impedance (line-to-line) faults, and the ensuing results are discussed herein. A line-to-line fault (F5) is initiated in the line 4−7 at time t = 0.0001 s for the system as described in Fig. 11 and value of fault resistance considered are ranges from 0.05 to 10 Ω and the fault current magnitude measured at line 4–7 is shown in Fig. 16 (a). As the fault chooses downstream path often, there are two ways to reach the source. Path 1 follows Bus 4 - Bus 3- Bus 2- Bus 1- common bus with a resultant distance of 4 and Path 2 follows Bus 7 - Bus 6- common bus with a resultant distance of 3. So, it is obvious the bidirectional Dijkstra chooses path 2 as it provides the shortest distance from faulted point to operating DG compared to path 1. Also, the presence of PMSG based WECS in path 2 is very closer than the presence of bidirectional battery in path 1. The corresponding voltage interrupted and breaker closing at CB8 are delineated in Fig. 16 (b) and (c), respectively. The existence of current rise and voltage drop are detected when the fault is initiated. Furthermore, the auto reclosing of CB8 takes place at 20 μs. This proves the proposed system's viability and reliability.

Fig. 16.

(a) Current at line 4–7 when subjected to different resistive faults (b) Voltage profile during fault interruption at L7-4 by breaker CB8 (c) Voltage profile during breaker CB8 reclosing.

4.7. Converter effects on occurrence of fault at line LPCC-6 and L6-7

The converter connected to the renewables does not have much impact. When a fault F6 occurs at the line connecting the common bus/PCC and bus 6 as shown in Fig. 11, immediately the CB6 trips which makes the voltage drop to zero, and thereby the reclosing of the breaker takes place after the interruption of the fault. Similarly, when a fault F7 occurs at line 6–7, immediately the CB7 trips based on the relay communication and commands from the protection controller as shown in Fig. 17 (b). However, this does not affect the power electronic converter due to the presence of a protection controller that monitors the entire grid parameters in nanoseconds. The terminal voltage of wind generation and the output of the rectifier portrayed in Fig. 17 (a & b) proves that the fault does not affect the converters present in the grid.

Fig. 17.

(a) Line voltage of wind turbine and its rectified output during the occurrence of fault at line LPCC-6 and L6-7 (b) Voltage interrupted and reclosing taking place at CB6 and CB7.

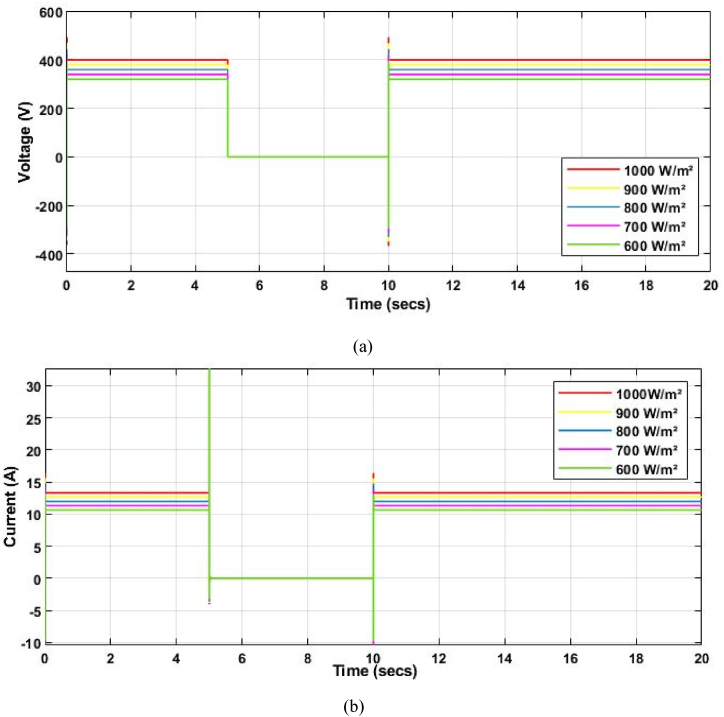

4.8. Analysis on different irradiation level of PV

The PV system is analyzed under various irradiation levels [51] ranging from 600 W/m2 to 1000 W/m2 for a temperature of 25 °C within the proposed DC microgrid system. During this analysis, a line-to-line fault is introduced for a duration of 5 s near relay R1, denoted as F8 as shown in Fig. 11. The faulted path of fault F8 is towards common bus. So, the breaker CB1 trips and recloses after the fault is interrupted. The voltage spike is due to the presence of power electronic switches in the breaker. The proposed algorithm demonstrates its flexibility in adapting for different irradiation levels and effectively distinguishing between faults and variations in irradiation. Consequently, this analysis underscores the capability of the proposed algorithm to operate seamlessly despite uncertainties in PV output voltage and current as illustrated in Fig. 18. During the breaker interrupting and reclosing period, the volatge stress across the power electronic switches cause voltage and current spike in the breaker resulting in longer arcing period and interruption time.

Fig. 18.

Evaluation of proposed algorithm for different irradiation levels of PV.

5. Comparison of the proposed with existing algorithms

After evaluating the performance of the proposed system in terms of accuracy and fault interruption time compared to a standard benchmark system, it is evident that the efficiency of the proposed algorithm demonstrates its rapidity and adaptability in DC systems, as illustrated in Fig. 19. The VI profile abnormalities and Vdiff and Idiff of relay points for threshold fixation under different fault operating conditions for seven bus DC microgrid system are highlighted and listed in Table 5, Table 6. The voltage and current variances across various relay points are measured and the Fenwick tree approach sets the threshold limits for the relay settings. Whenever algorithm predicts maximum variation in relay voltage and current against predefined values, the signal from Fenwick activates bidirectional Dijkstra algorithm to estimate the shortest path. A comparative analysis is conducted to evaluate fault detection and interruption using both existing and proposed algorithms in the seven bus DC microgrid system, as presented in Table 7, Table 8. On implementing these algorithms, the running time for AC microgrid as shown in Table 2 is very high compared to the implementation in DC microgrid. Notably, the proposed novel implementation of Fenwick and bidirectional Dijkstra algorithm in DC microgrid provides the execution time in less than 400 μs. On comparing the prims, Kruskal, Boruvka and Fenwick in Table 7 and it is realized that Fenwick finds the status of grid within 60 and 80 μs for 7 bus DC system using the processor Intel Xeon and i5 respectively. Similarly, from the results of shortest path algorithms shown in Table 8, the bidirectional Dijkstra finds the path within 350 and 384 μs for 7 bus DC system using the processor Intel Xeon and i5 respectively as shown in Fig. 13(c). The results elaborated in the below Table 7, Table 8 proves the proposed algorithm's efficiency with existing algorithms as in Table 2. In 7 bus DC microgrid, the effectiveness of Fenwick tree algorithm is estimated in contrast to the active bus detection methods existing using Prims, Kruskal, and Boruvka algorithm.

Fig. 19.

Assessment on Accuracy and Fault interruption time of proposed with standard benchmark system.

Table 5.

V &I profile of 7-bus differential relays.

| Operating Conditions/Relay Points | R1 |

R2 |

R3 |

R4 |

R5 |

R6 |

R7 |

R8 |

R9 |

R10 |

R11 |

R12 |

R13 |

R14 |

R15 |

R16 |

||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| V(V) | I(A) | V(V) | I(A) | V(V) | I(A) | V(V) | I(A) | V(V) | I(A) | V(V) | I(A) | V(V) | I(A) | V(V) | I(A) | V(V) | I(A) | V(V) | I(A) | V(V) | I(A) | V(V) | I(A) | V(V) | I(A) | V(V) | I(A) | V(V) | I(A) | V(V) | I(A) | |

| Normal Operating Conditions | 382 | 7.9 | 382 | 8 | 382 | 7.5 | 400 | 8 | 404 | 8.7 | 400 | 8.9 | 400 | 8.9 | 380 | 8.6 | 380 | 8.6 | 402 | 8.8 | 380 | 7.5 | 400 | 8 | 403 | 8.2 | 400 | 7.5 | 400 | 7.5 | 392 | 7.5 |

| Line-line fault F1 | 393 | 11 | 399 | 12 | 399 | 9 | 399 | 12 | 398 | 54 | 400 | 60 | 400 | 60 | 330 | 22 | 310 | 24 | 402 | 8.8 | 393 | 11 | 399 | 12 | 393 | 9 | 399 | 12 | 393 | 12 | 290 | 25 |

| Line-ground fault F2 | 393 | 11 | 399 | 12 | 393 | 9 | 399 | 12 | 398 | 13 | 180 | 224 | 200 | 202 | 380 | 12 | 380 | 9.9 | 402 | 8.8 | 393 | 11 | 399 | 12 | 393 | 11 | 399 | 12 | 393 | 12 | 402 | 8.8 |

| Multi-fault & cross-country fault F3 & F4 | 393 | 8 | 399 | 8 | 393 | 9 | 152 | 122 | 398 | 13 | 399 | 12 | 399 | 12 | 380 | 12 | 382 | 9.9 | 402 | 8.7 | 393 | 12 | 402 | 8.8 | 300 | 9 | 209 | 52 | 393 | 11 | 399 | 12 |

| Line-line resistive fault of F5 | 388 | 8.8 | 399 | 9.2 | 393 | 9 | 404 | 11 | 400 | 8 | 399 | 12 | 399 | 12 | 405 | 12.2 | 402 | 11.9 | 402 | 11.7 | 402 | 12 | 402 | 8.8 | 400 | 9 | 402 | 8.8 | 393 | 11 | 263 | 39 |

| Converter performance analysis F6 & F7 | 408 | 8.8 | 399 | 10.8 | 402 | 11.9 | 404 | 11 | 407 | 7.8 | 399 | 12 | 399 | 12 | 405 | 12.2 | 393 | 9 | 402 | 11.7 | 402 | 12 | 332 | 8.8 | 400 | 9 | 330 | 63 | 393 | 11 | 405 | 12.4 |

Table 6.

Vdiff and Idiff of relay points for threshold fixation.

| Operating Conditions/Relay Points | R1∼R2 |

R3∼R4 |

R5∼R6 |

R7∼R8 |

R9∼R10 |

R11∼R12 |

R13∼R14 |

R15∼R16 |

||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Vdiff (V) | Idiff (A) | Vdiff (V) | Idiff (A) | Vdiff (V) | Idiff (A) | Vdiff (V) | Idiff (A) | Vdiff (V) | Idiff (A) | Vdiff (V) | Idiff (A) | Vdiff (V) | Idiff (A) | Vdiff (V) | Idiff (A) | |

| Normal Operating Conditions | 0 | 0.1 | 18 | 0.5 | 4 | 0.2 | 20 | 0.3 | 22 | 0.5 | 20 | 0.5 | 3 | 0.7 | 8 | 0 |

| Line-line fault F1 | 6 | 6 | 6 | 3 | 2 | 6 | 78 | 14 | 92 | 15.2 | 6 | 1 | 6 | 3 | 103 | 13 |

| Line-ground fault F2 | 6 | 6 | 6 | 3 | 218 | 211 | 180 | 190 | 22 | 1.1 | 6 | 1 | 6 | 3 | 9 | 3.2 |

| Multi-fault & cross-country fault F3 & F4 | 6 | 0 | 241 | 113 | 1 | 1 | 19 | 0 | 20 | 1.2 | 9 | 3.2 | −91 | 43 | 6 | 1 |

| Line-line resistive fault of F5 | 1 | 0.4 | 11 | 2 | 1 | 4 | 6 | 0.2 | 0 | 0.2 | 0 | 3.2 | 2 | 0.2 | 130 | 28 |

| Converter performance analysis F6 &F7 | 9 | 2 | 2 | 0.9 | 8 | 4.2 | 6 | 0.2 | 9 | 2.7 | 70 | 3.2 | 70 | 56 | 12 | 1.4 |

Table 7.

Execution time of proposed algorithm for active node identification for kilometric fault and cross-country faults in DC microgrid.

| ALGORITHM | ACTIVE NODE IDENTIFICATION |

||

|---|---|---|---|

| DC BUS NETWORK |

PROCESSOR USED |

EXECUTION TIME (μs) |

|

| Prims | 7 Bus | Intel Xeon E3-1225 V3 @ 3.20 GHz | 1200 |

| Intel i5 | 1500 | ||

| Kruskal | 7 Bus | Intel Xeon E3-1225 V3 @ 3.20 GHz | 1100 |

| Intel i5 | 1200 | ||

| Boruvka | 7 Bus | Intel Xeon E3-1225 V3 @ 3.20 GHz | 1200 |

| Intel i5 | 1300 | ||

| Fenwick (proposed) | 7 Bus | Intel Xeon E3-1225 V3 @ 3.20 GHz | 60 |

| Intel i5 | 80 | ||

Table 8.

Execution time of proposed algorithm for shortest path identification for kilometric fault and cross-country faults in DC microgrid.

| ALGORITHM | SHORTEST PATH IDENTIFICATION |

||

|---|---|---|---|

| DC BUS NETWORK |

PROCESSOR USED |

EXECUTION TIME (μs) |

|

| Dijkstra's | 7 Bus | Intel Xeon E3-1225 V3 @ 3.20 GHz, | 650 |

| Intel i5 | 675 | ||

| Floyd Warshall | 7 Bus | Intel Xeon E3-1225 V3 @ 3.20 GHz | 580 |

| Intel i5 | 592 | ||

| Bellman-Ford | 7 Bus | Intel Xeon E3-1225 V3 @ 3.20 GHz | 515 |

| Intel i5 | 528 | ||

| Bidirectional Dijkstra (proposed) | 7 Bus | Intel Xeon E3-1225 V3 @ 3.20 GHz | 350 |

| Intel i5 | 384 | ||

From Fig. 20 comparison using radial chart, it is understood that the proposed Fenwick tree with bidirectional algorithm takes least time in detecting and interrupting a fault. As the bounce in radial diagram is closer enough to center point for both processors, it concludes that the execution time does not depend on the system scaling but it rather depends on the algorithm and processor used. Also, the values pointing towards the closest center point is the optimal least solution comparatively with other algorithms.

Fig. 20.

Radial chart comparison of existing and proposed algorithm.

The proposed protection algorithm adapts to all DC microgrid configurations. As the complexity and scalability of the grid increases, the grid needs more attention. Therefore, it is recommended to install additional protection controllers, but the rapidity of the algorithm will never change for any complex structure because of the time complexity O(log(n)).

This approach is viable to islanding mode where the rural electrification can be promoted. This paper focusses on islanded DC microgrid configuration and the stored line and bus data requires more storage capacity that has to be stacked in the cloud. The memory allocated for these data sets is more leading to enforced flashing of memory.

6. Conclusion

Design and implementation of an effective protection scheme for a microgrid is a challenging task owing to its dynamic structure and bidirectional power flow operation. Since traditional protection schemes are not appropriate for such conditions, this article has proposed a proficient adaptive protection scheme that can operate bidirectionally and segregate the faulted zone in a minimal period of time using a protection controller. The controller incorporates two novel algorithms, referred to as “Fenwick” and " bidirectional Dijkstra” specifically designed to provide continuous monitoring of both active and inactive buses, detection of fault occurrences, and identification of fault branches. The least distance path between a faulted point to the closest distributed generations is found by utilizing the Fenwick-aided bidirectional Dijkstra algorithm, which is fed to the processor using Python scripts. This algorithm clears the fault with minimum load disconnection and minimum fault clearing time. Notably, the fault detection and fault clearance time using the proposed algorithm is 384 μs. The efficiency of the proposed algorithm is verified by comparing with existing algorithms using control hardware in loop testing in Opal RT simulator for various fault conditions such as bus faults, kilometric or line faults, cross-country faults, multi fault and reverse fault scenarios. The suggested protection system can be applied to numerous DC microgrid configurations with high power ratings as future extension of work, due its supremacy and robustness towards variable operating conditions. This research work was carried out in Real Time simulator platform in Smart Grid Laboratory at Vellore institute of Technology.

Funding

The research work received no external funding, but the APC was funded by Vellore Institute of Technology, Chennai, India.

Data availability statement

The data included in this article is cited in the reference. The details can be visulaized in the reference article.

CRediT authorship contribution statement

S. Faazila Fathima: Writing – original draft, Methodology, Investigation, Formal analysis, Data curation, Conceptualization. Premalatha L: Writing – review & editing, Visualization, Validation, Supervision, Project administration. Prithviraj Yuvaraj: Software, Resources.

Declaration of competing interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

Acknowledgments

We express our gratitude to Vellore Institute of Technology, Chennai, India for funding the article processing fee.

Biographies

S. Faazila Fathima received her Bachelor of Engineering degree from Anna University, Chennai, in 2012, followed by a Master of Technology degree from B.S. Abdur Rahman University, Chennai, in 2014. Currently, she is employed as a research associate at Vellore Institute of Technology, Chennai, while concurrently pursuing her Ph.D. Additionally, she was honored with the Raman Research Award in 2021 by the Vellore Institute of Technology, Chennai, in recognition of her research contributions. Her areas of expertise encompass the protection of DC microgrids, optimization algorithms in data science, and artificial intelligence. Email: faazila91@gmail.com.

L. Premalatha (Corresponding Author) received both her Bachelor of Engineering degree in Electrical and Electronics and her Master of Engineering in Power Systems from Thiagarajar College of Engineering, Madurai, India, in 1995 and 1997, respectively. Subsequently, she earned her Ph.D. in Electrical Engineering from Anna University, Chennai, India, in 2009. Following her doctoral studies, she was awarded a post-doctoral fellowship from the University of Malaya, Kuala Lumpur, in 2013, where she remained affiliated during 2013–14. Accumulating over 25 years of teaching experience at both undergraduate and postgraduate levels, she possesses more than 18 years of research expertise. Her scholarly contributions include over 60 publications across various international journals and conferences, alongside serving as a reviewer for several academic journals and conferences. She has successfully completed several government-funded projects and recently secured a patent. Currently, she is working as a Professor in the School of Electrical Engineering at Vellore Institute of Technology, Chennai, India, focusing her research on the application of power electronics in power systems, renewable energy sources integration into the grid, power quality issues, and the utilization of IoT and machine learning in power systems. For further contact, her email address is premalatha.l@vit.ac.in

Prithviraj Yuvaraj pursuing his Bachelor of Tech in Electrical Engineering at Vellore Institute of Technology, Chennai, Tamil Nadu, India. He is actively engaged in various projects aligned with his research interests, which include Microgrid Protection, machine learning techniques, robotics, and computer vision. For further communication, he can be reached via email at prithviraj.yuvaraj@gmail.com.

References

- 1.Shaukat N., et al. Decentralized, democratized, and decarbonized future electric power distribution grids: a survey on the paradigm shift from the conventional power system to micro grid structures. IEEE Access. 2023;11:60957–60987. doi: 10.1109/ACCESS.2023.3284031. [DOI] [Google Scholar]

- 2.Hamanah W.M., Hossain M.I., Shafiullah M., Abido M.A. AC microgrid protection schemes: a comprehensive review. IEEE Access. 2023;11:76842–76868. doi: 10.1109/ACCESS.2023.3298306. [DOI] [Google Scholar]

- 3.Shi Zhongsheng, et al. Development of 3-phase fault detection, protection, and automation application with the present of DG in AC power system using GOOSE protocol. Heliyon. March 2024;0(0) doi: 10.1016/j.heliyon.2024.e27482. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 4.Gao J., Li X., Xin M., Yu Y., Xu C. An adaptive protection scheme for power systems considering the effects of HVDC interfaced distributed generations. IEEE Access. 2022;10:10210–10218. doi: 10.1109/ACCESS.2022.3144638. [DOI] [Google Scholar]

- 5.Tiwari Shankarshan Prasad, Koley Ebha, Ghosh Subhojit. Communication-less ensemble classifier-based protection scheme for DC microgrid with adaptiveness to network reconfiguration and weather intermittency. Sustainable Energy, Grids and Networks. 2021;26 doi: 10.1016/j.segan.2021.100460. [DOI] [Google Scholar]

- 6.Faazila Fathima S., Premalatha L. Protection strategies for ac and DC microgrid – a review of protection methods adopted in recent decade. IETE J. Res. 2021;69:6573–6589. doi: 10.1080/03772063.2021.1990140. [DOI] [Google Scholar]

- 7.Bamshad A., Ghaffarzadeh N. A novel smart overcurrent protection scheme for renewables-dominated distribution feeders based on quadratic-level multi-agent system (Q-MAS) Electr.Engg. 2023;105:1497–1539. doi: 10.1007/s00202-023-01741-6. [DOI] [Google Scholar]

- 8.Rao G.K., Jena P. Fault detection in DC microgrid based on the resistance estimation. IEEE Syst. J. 2022;16:1009–1020. https://doi:10.1109/JSYST.2020.3046054 [Google Scholar]

- 9.Li M., Zhang D., Lu S., Tang X., Phung T. Differential evolution-based overcurrent protection for DC microgrids. Energies. 2021;14:5026. doi: 10.3390/en14165026. [DOI] [Google Scholar]

- 10.Chauhan P., Gupta C.P., Tripathy M. High speed fault detection and localization scheme for low voltage DC microgrid. Int. J. Electr. Power Energy Syst. 2023;146 doi: 10.1016/j.ijepes.2022.108712. [DOI] [Google Scholar]

- 11.Kant K., Ansari S., Gupta O.H. An advanced short-circuit protection scheme for a bipolar DC microgrid. Front. Energy Res. 2023;11:1–14. doi: 10.3389/fenrg.2023.1100789. [DOI] [Google Scholar]

- 12.Jiang S., Fan C., Huang N., Zhu Y., He M. “A fault location method for DC lines connected with DAB terminal in power electronic transformer. IEEE Trans. Power Deliv. Feb. 2019;34(1):301–311. doi: 10.1109/TPWRD.2018.2867851. [DOI] [Google Scholar]

- 13.Yehia D.M., Mansour D.A. Modeling and analysis of superconducting fault current limiter for system integration of battery banks. IEEE Trans. Appl. Supercond. 2018;28 doi: 10.1109/TASC.2018.2814398. [DOI] [Google Scholar]

- 14.Meghwani A., Srivastava S.C., Chakrabarti S. A non-unit protection scheme for DC microgrid based on local measurements. IEEE Trans. Power Deliv. 2017;32:172–181. doi: 10.1109/TPWRD.2016.2555844. [DOI] [Google Scholar]

- 15.Meghwani A., Gokaraju R., Srivastava S.C., Chakrabarti S. Local measurements based backup protection for DC microgrids using sequential analyzing technique. IEEE Syst. J. 2020;14:1159–1170. doi: 10.1109/JSYST.2019.2919144. [DOI] [Google Scholar]

- 16.Monadi M., Gavriluta C., Luna A., Candela J.I., Rodriguez P. Centralized protection strategy for medium voltage DC microgrids. IEEE Trans. Power Deliv. 2017;32:430–440. doi: 10.1109/TPWRD.2016.2600278. [DOI] [Google Scholar]

- 17.Yugeswar Reddy O., Chatterjee Soumesh, Chakraborty Ajoy Kumar, Ratan Bhowmik Arup. Rapid fault identification in standalone DC Microgrids. Simulat. Model. Pract. Theor. 2022;116 doi: 10.1016/j.simpat.2022.102489. [DOI] [Google Scholar]

- 18.Shabani, Mazlumi K. Evaluation of a communication-assisted overcurrent protection scheme for photovoltaic-based dc microgrid. IEEE Trans. Smart Grid. 2020;11:429–439. doi: 10.1109/TSG.2019.2923769. [DOI] [Google Scholar]

- 19.Rachi M.R.K., Khan M.A., Husain I. Local measurement-based protection coordination system for a standalone DC microgrid. IEEE Trans. Ind. Appl. 2021;57:5332–5344. doi: 10.1109/TIA.2021.3091945. [DOI] [Google Scholar]

- 20.Saxena, Sharma N.K., Samantaray S.R. An enhanced differential protection scheme for LVDC microgrid. IEEE Journal of Emerging and Selected Topics in Power Electronics. 2022;10:2114–2125. doi: 10.1109/JESTPE.2022.3144300. [DOI] [Google Scholar]

- 21.Bayati N., Balouji E., Baghaee H.R., et al. Locating high-impedance faults in DC microgrid clusters using support vector machines. Appl. Energy. 2022;308:1–11. doi: 10.1016/j.apenergy.2021.118338. [DOI] [Google Scholar]

- 22.Gnana Swathika O.V., Hemamalini S. Prims-aided dijkstra algorithm for adaptive protection in microgrids. IEEE Journal of Emerging and Selected Topics in Power Electronics. 2016;4:1279–1286. doi: 10.1109/JESTPE.2016.2581986. [DOI] [Google Scholar]

- 23.Pandiarajan N., Muthu R. Mathematical modelling of photovoltaic module with Simulink. 1st Int Conf Electr Energy Syst ICEES. 2011:258–263. [Google Scholar]

- 24.Saluja J., Biswas S., Roy S., Swathika O.V.G. Performance analysis of graph algorithms for microgrid protection. J. Telecommun. Electron. Comput. Eng. 2018;10:115–118. [Google Scholar]

- 25.Swathika O.V.G., Hemamalini S., Haritha Ashre T. Chazelle-dijkstra method using fibonacci heaps algorithm for identifying shortest path in microgrids. Int. J. Simulat. Syst. Sci. Technol. 2017;17:21.1–21.5. doi: 10.5013/IJSSST.a.17.41.21. [DOI] [Google Scholar]

- 26.Swathika O.V.G., Divakaran A., Hemamalini S. Hybrid Boruvka - johnson's Algorithm for shortest path identification in reconfigurable microgrids. J. Telecommun. Electron. Comput. Eng. 2017;9:63–66. [Google Scholar]

- 27.Swathika O.V., et al. Shortest path identification in reconfigurable microgrid using hybrid bellman ford-dijkstra’s algorithm. Adv. Sci. Lett. 2016;22:2932–2935. [Google Scholar]

- 28.Swathika O.V.G., Hemamalini S. Graph theory and optimization algorithms aided adaptive protection in reconfigurable microgrid. J Electr Eng Technol. 2020;15:421–431. doi: 10.1007/s42835-019-00197-8. [DOI] [Google Scholar]

- 29.Chang H., Sennett B.R., Avestruz A.-T., Leeb S.B., Kirtley J.L. Analysis and design of DC system protection using Z-source circuit breaker. IEEE Trans. Power Electron. 2016;31:1036–1049. doi: 10.1109/TPEL.2015.2415775. [DOI] [Google Scholar]

- 30.Li T., Li Y., Liu N. A new topological structure of Z-source DC circuit breaker. IEEE Trans Circuits Syst II Express Briefs. 2022;69:3294–3298. doi: 10.1109/TCSII.2022.3156575. [DOI] [Google Scholar]

- 31.Ajmal C.N.M., Raghavendra I.V., Naik S., Ray A., Krishnamoorthy H.S. A modified hybrid DC circuit breaker with reduced arc for low voltage DC grids. IEEE Access. 2021;9:132267–132277. doi: 10.1109/ACCESS.2021.3115456. 10.1109/ACCESS.2021.3115456. [DOI] [Google Scholar]

- 32.Kim S., Ulissi G., Kim S.-N., Dujic D. Protection coordination for reliable marine DC power distribution networks. IEEE Access. 2020;8:222813–222823. doi: 10.1109/ACCESS.2020.3043515. [DOI] [Google Scholar]

- 33.Shabani A., Mazlumi K. Evaluation of a communication-assisted overcurrent protection scheme for photovoltaic-based DC microgrid. IEEE Trans. Smart Grid. 2020;11:429–439. doi: 10.1109/TSG.2019.2923769. [DOI] [Google Scholar]