Abstract

This paper presents a passive Envelope Detector (ED) to be used for reception of OOK-modulated signals, such as in Wake-Up Receivers employed within Wireless Sensor Networks, widely used in the IoT. The main goal is implementing a temperature compensation mechanism in order to keep the passive ED input resistance roughly constant over temperature, making it a constant load for the preceding matching network and ultimately keeping the overall receiving chain sensitivity constant over temperature. The proposed ED was designed using STMicroelectronics 90 nm CMOS technology to receive 1 kbps OOK-modulated packets with a 433 MHz carrier frequency and a 0.6 V supply. The use of a block featuring a Proportional-to-Absolute Temperature (PTAT) current yields a 5 dB reduction in sensitivity temperature variation across the −40 °C to 120 °C range. Moreover, two different implementations were compared, one targeting minimal mismatch and the other one targeting minimal area. The minimal area version appears to be better in terms of estimated overall chain sensitivity at all temperatures despite a higher sensitivity spread.

Keywords: envelope detector, temperature compensation, ultra-low-power, wake-up receivers (WuRXs)

1. Introduction

Envelope Detectors (EDs) are used in several applications involving an incoming high-frequency amplitude modulated signal whose envelope needs to be extracted.

A usage example for EDs is that of Wake-Up Receivers (WuRXs), widely employed in the Internet of Things (IoT). IoT nodes are organized in subnetworks, the Wireless Sensor and Actuator Networks (WSAN), typically composed of a central node; the gateway, which manages all communication within the network; and several end nodes communicating wireless.

In such nodes, the transceiver is typically the most power-hungry section, and a popular power reduction method is the use of WuRXs. The WuRX is an always-on ultra-low-power additional receiver, which can be integrated in end nodes to continuously monitor the channel instead of the main transceiver and activate the rest of the node only when a Wake-Up packet is received from the gateway. This approach allows event-driven, asynchronous communication [1,2,3,4,5,6,7].

Despite its noise sensitivity, low-power applications mostly use OOK modulation, which is the simplest kind of Amplitude Shift Keying modulation, the digital form of Amplitude Modulation [1,8]. The modulating signal is a square wave: the carrier is present during the transmission of a logic 1, whereas there is no carrier during the transmission of a logic 0. It is frequently employed in communication, such as RF and optical communication, thanks to its simplicity and spectral efficiency.

OOK demodulation is easily carried out by leveraging the second-order non-linearities of MOSFETs in subthreshold, which is also beneficial for low-power operation. Two approaches are available [9], the active [10,11] and the passive one [12,13,14,15,16,17,18,19,20,21]. Unlike in active EDs, in passive ones, demodulating MOSFETs or off-the-shelf diodes (in the case of discrete-component solutions) are biased with zero current and the RF signal is coupled to MOSFET terminals by capacitances. No static current results in an inherent absence of flicker noise. This directly translates into an enhanced sensitivity, i.e., the minimum input power that can be correctly detected. Yet, a trade-off exists between the propagation delay and the rectification gain [1]. Then, the demodulation mechanism of passive EDs is heavily dependent on the input RF frequency due to the presence of the coupling and filtering capacitances. Finally, more constraints exist in terms of the maximum input power that can be correctly received than for active EDs (Section 3.4) [11].

For optimal communication, ED operation needs to be reliable in all settings, where environmental conditions, such as temperature, may vary widely. Therefore, it is advisable to implement some sort of compensation in order for the ED to be fully functional in every condition. This paper accomplishes this task by adding a nanowatt temperature compensation block to a passive ED for robust operation in case of significant temperature variations. Two different versions are implemented, the first targeting minimal mismatch and the second targeting minimal area, for comparison in terms of room temperature sensitivity and sensitivity spread due to mismatch.

This paper is organized as follows: Section 2 presents the architectural choices for the passive ED with the Proportional-to-Absolute Temperature (PTAT) compensation block, comparing them with other EDs in the literature. In Section 3, the passive ED is thoroughly described, from the basic structure presented in [12] to the proposed temperature compensation mechanism and the reasons and consequences for choosing a differential approach. Section 4 shows the validation of the proposed temperature compensation mechanism as well as the comparison between the two implementations. Finally, Section 5 concludes the paper.

2. State-of-the-Art Passive EDs with Temperature Compensation

As mentioned in the Introduction, the demodulation mechanism leverages the second-order non-linearities of MOSFETs in subthreshold [10]. The standard passive ED is a Dickson charge pump composed of diode-connected MOSFETs biased with zero static current and capacitances.

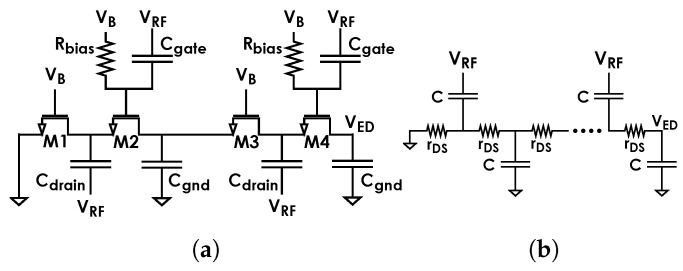

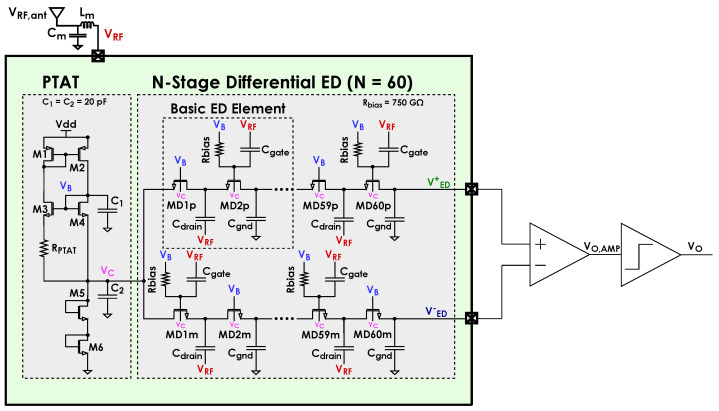

The proposed ED employs the variation presented in [12] and shown in Figure 1a, where voltage is generated by an additional PTAT block as in Figure 2. The impedance seen at the RF input is the parallel connection between a resistance and a capacitance and is matched to the antenna impedance by a matching network. The temperature compensation mechanism operates through a dedicated block aiming at temperature dependence reduction for so that the temperature dependence of matching network gain is also minimized. As detailed in Section 3.2, this ultimately reduces the temperature dependence of the overall receiving chain sensitivity.

Figure 1.

(a) Passive ED as in [12] and (b) estimation of its propagation delay.

Figure 2.

Proposed ED with temperature compensation [22].

Temperature compensation techniques have already been presented. An alternative approach employing a different additional block was proposed in [15]. It requires both enhancement and depletion MOSFETs as it leverages the threshold difference between them and demonstrates a reduction in sensitivity temperature dependence over a −10 °C to 50 °C operating temperature range.

Moreover, a structure similar to the one proposed in this paper, employing a PTAT current for the biasing of self-mixer gate terminals, was proposed in [16]. Yet, a discussion of sensitivity dependence over temperature is missing.

In [17], a dedicated block is used to drive diode bulk terminals so as to make their threshold voltage, thus their channel resistance, constant over temperature with the ultimate aim of a constant ED bandwidth. The operating temperature range is −10 °C to 40 °C.

Ref. [18] targets operating temperatures between −30 °C and 70 °C. It focuses on temperature and supply robust voltage and current references, as well as comparator threshold adjustments by means of a capacitive digital-to-analog converter for temperature compensation.

Finally, ref. [19] relies on a charge-transfer summation amplifier following the ED for temperature robustness across a −40 °C to 85 °C operating temperature range.

Table 1 compares the different implementations addressing sensitivity robustness through a Figure of Merit, which represents the inverse of the mean sensitivity variation across 1 °C ). As a result, our implementation shows FoM performances aligned with the state-of-the-art [18] over a wider temperature range.

Table 1.

Temperature stability comparison table with the state-of-the-art.

3. ED and PTAT Block Description

3.1. ED Model and Receiving Chain Sensitivity Optimization

For the sake of clarity, this subsection summarizes the features of the employed ED architecture just as in [12]. Its topology (Figure 1a) is a variation of the Dickson charge pump. The following is based on the standard subthreshold current model for the MOSFET-based diodes:

| (1) |

where

| (2) |

is the aspect ratio of the MOSFET and is a technological parameter. Assuming an input OOK-modulated signal , where is the envelope signal and is equal to when a ‘1’ is transmitted and equal to 0 when a ‘0’ is transmitted, the output amplitude is [12]

| (3) |

where N is the number of diode stages, n is the non-ideality factor of the diodes and is the thermal voltage.

Figure 3 shows the typical receiving chain of an ultra-low-power system, such as that of a WuRX, excluding the final digitizing element. It is composed of a matching network, ED and baseband amplifier. As mentioned, at RF, the ED can be seen as a load composed of a resistance and a capacitance in parallel, and , for the preceding matching network. This implies that the matching network is designed based on and values. The values for , and of Figure 2 are mainly determined by the RF frequency they need to correctly transfer to the internal diode nodes and filter out, respectively. Assuming , and to be big enough with respect to the of the diodes and to have negligible parasitics, , where is the channel resistance of diodes, and , where is the parasitic capacitance of the RF input pad.

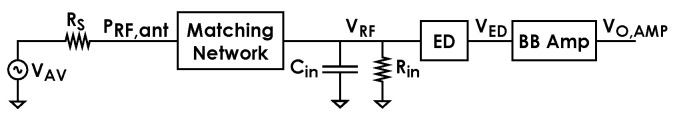

Figure 3.

The typical WuRX chain excluding the final digitizing element, as in [12].

The delay introduced by the ED and, thus, its maximum operating bitrate, can be found by applying the open circuit time constant method to the equivalent circuit in Figure 1b, assuming all capacitances to have the same value. This yields [20]

| (4) |

Therefore, is almost proportional to the cube of N, which results in any increase in N having a strong impact on the delay introduced by the circuit.

As mentioned, Figure 3 shows the typical receiving chain of an ultra-low-power system excluding the final digitizing element. This is useful to estimate the overall chain sensitivity [12]. The following analysis is carried out assuming the matching condition to be met. First, the input power is , where is the resistance of the source. This implies the voltage amplitude virtually needed within the generator before is . The peak-to-peak signal at the output of the matching network is then , with being the matching network gain. Since it is the most practical implementation for the matching network, a commercial component simple LC network such as the one shown in Figure 2 shall be considered in the following, yielding [12]

| (5) |

where is the Q factor of the matching network inductance. Necessary conditions for high are low and high at the target RF carrier frequency.

The peak-to-peak signal at the output of the ED is from (3). Since the diodes have no flicker noise, the noise power at the output of the ED is , where is the Boltzmann constant and is the ED noise bandwidth, which is ideally equal to bitrate . Then, the SNR at the ED output is

| (6) |

Thus, the SNR ultimately does not depend on N.

The ED is followed by a baseband amplifier with Noise Factor , which can be expressed as

| (7) |

where is the integrated noise at the amplifier output due to the amplifier itself, G is the amplifier voltage gain and is as defined previously. Assuming to be the minimum required SNR at the output of the baseband amplifier, the overall chain sensitivity can be calculated as

| (8) |

where depends on through (5).

This expression as a function of has a minimum [12], and the optimum must be chosen accordingly in order to optimize chain sensitivity. As mentioned, in (6) does not depend on N, whereas a big value for N is desirable for a small (7), as directly degrades sensitivity (8). This poses a trade off between sensitivity and bitrate, which is closely linked to the propagation delay the ED introduces , as in (4). Moreover, a big value for N also results in a high , thus degrading . Therefore, N becomes an important design parameter in a complicated trade-off, as it affects , , and [1].

This leads to the choice of an optimum , . Thanks to the possibility of setting the of the diodes, can be found through the following formula:

| (9) |

given that [12] and where are the diodes.

Ultimately, by setting the appropriate diode , it is possible to set the correct for chain sensitivity optimization. All useful formulas for sensitivity optimization are reported in Table 2.

Table 2.

Useful formulas for sensitivity optimization—Section 3.1.

| ED input resistance | |

| ED input capacitance | |

| Matching network gain | |

| Single-ended ED output voltage | |

| ED delay | |

| Sensitivity |

3.2. Temperature Compensation through the PTAT Block

Actually, as in (8) depends on temperature through as well, which in turn is inversely proportional to the baseband output resistance . Therefore, the integrated noise at the output of the ED becomes

| (10) |

which is independent of .

As for of the baseband amplifier following the ED, we shall assume the amplifier to be standard, for instance a common-source with an active load, with negligible residual flicker noise and transconductance , for the sake of simplicity, and to operate in the subthreshold region. Let us also assume the baseband amplifier to have a bandwidth close to bitrate , which is in turn close to the ED noise bandwidth . In this case, (7) results in

| (11) |

If N or are big enough, e.g., a is enough for a and (see Section 4.2.1), is close enough to unity at room temperature and its variations with temperature are negligible.

This results in , as in (5), being the only element with a dependence on in (8). In turn, is a very rapidly varying function of temperature T through as in (9), which ultimately results in

| (12) |

The purpose of the proposed compensation mechanism is to make , and thus , constant with temperature leaving . No further attempt has been made to cancel this residual temperature dependence. An additional effect is making constant as well.

The following analysis is carried out assuming a small input signal, i.e., close to sensitivity, resulting in source voltages roughly equal to for all diodes. As illustrated in Figure 2, the PTAT block generates a for the diodes so as to make their , and thus , roughly constant with T. This also results in a roughly constant so that no changes to the matching network are required in case of temperature changes. The compensation mechanism is again based on the standard subthreshold current model for the diodes (1), (2). The PTAT provides the diodes with the same as , i.e., . Assuming the diodes to have a small and assuming the difference in between the diodes and not to significantly affect ,

| (13) |

From (1), assuming , the bias current of is

| (14) |

Substituting (14) in (13), and again assuming the difference in between the diodes and not to significantly affect ,

| (15) |

Due to the 1:1 mirror –, the bias current of is equal to that of and is

| (16) |

Therefore, combining (16) with (15), it is possible to prove that

| (17) |

which shows that is theoretically not a function of T. A simple start-up circuit, shown in Figure 2 for the sake of simplicity, is also included to push the PTAT block away from its zero-current stable DC operating point and push it to the actual DC operating point it was designed for.

3.3. ED Differential Approach

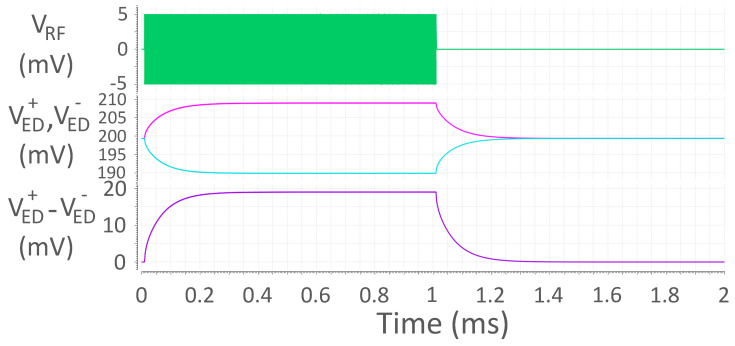

The addition of the PTAT block causes its own noise, which includes both thermal and flicker—unlike that of the ED—to propagate through the signal chain. In order to prevent a heavy degradation in the achievable chain sensitivity, a differential approach was chosen: the implemented ED features two identical chains, each of which has N diodes, connected to the PTAT cell instead of one, as shown in Figure 2. The noise due to the PTAT cell is then seen as common-mode at the output of the ED and, thus, gets canceled out by a subsequent ideal differential amplifier. The differential circuit has an output signal

| (18) |

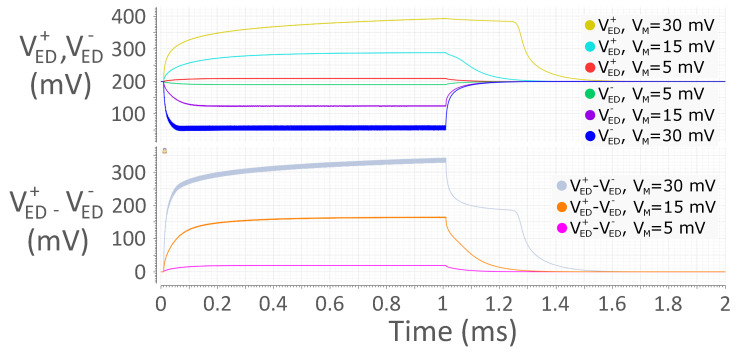

an input resistance and an input capacitance , which yields the same SNR at the ED output as in the single-ended case. Sample simulated waveforms are shown in Figure 4. The envelope of the incoming OOK-modulated signal is extracted with both polarities, by the positive diode chain and by the negative diode chain. The output is then read differentially, .

Figure 4.

Sample simulated waveforms in a differential passive ED for = 5 mV. From top to bottom: ED input signal , ED single-ended outputs and , and ED differential output .

Moreover, switching to a differential approach causes no increases in power consumption due to the zero-current biasing of the diodes. Since the two chains work independently, the system does not get slowed down either.

Finally, it shall be proven that the noise factor of the amplifier is the same when adopting a differential approach as it is in the single-ended case. The same assumptions as those in Section 3.2—a standard baseband amplifier, for instance, a common-source with an active load, operating in the subthreshold region with negligible residual flicker noise and transconductance —are supposed to hold. In the differential case and assuming the comparison to be carried out at total current consumption parity, (7) results in

| (19) |

which is the same as in the single-ended case (11).

This shows that no degradation occurs in the overall SNR at the amplifier output by adopting the differential approach.

3.4. Maximum Input Power

A major drawback of passive EDs is the existence of a typically low maximum input power. This occurs both in single-ended structures employing a positive chain, as in Figure 5 shows, and in differential structures, as proven by . This Figure portrays for = 5 mV, 15 mV and 30 mV in red, light blue and yellow, respectively, and for = 5 mV, 15 mV and 30 mV in green, violet and blue, respectively, on top; further, it displays differential output for = 5 mV, 15 mV and 30 mV in pink, orange and gray, respectively, at the bottom. The yellow trace on top, i.e., for = 30 mV, demonstrates that the shape of features a delayed transition to ‘0’ when the input power is too high. This issue extends to the differential output signal , as depicted by the gray trace at the bottom of the same Figure, as well as to the amplifier and comparator outputs. This is due to the body effect affecting diodes.

Figure 5.

Sample simulated waveforms in a differential passive ED for = 5 mV, 15 mV and 30 mV. From top to bottom: ED single-ended outputs and , ED differential output . The picture shows ED output distortion due to increased input power.

Let us consider the positive diode chain in Figure 2. All diodes have their body terminal connected to ; however, when a ‘1’ is being received, their source voltage becomes farther and farther from , moving along the chain towards the output. This implies a more and more positive is applied to the diodes moving along the chain, resulting in a higher and higher threshold voltage . Actually, the higher the input power, the stronger is this effect. At a certain point, the capacitance discharge occurring at the end of the reception of the ‘1’ becomes so difficult that it takes a non-negligible percentage of the bit-time to complete, resulting in output distortion.

If the differential approach is taken, this effect also concerns the negative diode chain in the opposite way. As a matter of fact, a more and more negative is applied to the diodes moving along the chain, resulting in a lower and lower threshold voltage . When the reception of the ‘1’ ends, capacitance discharge on this side becomes very fast, contributing to differential signal distortion.

Possible countermeasures include connecting diode source terminals to their bulk terminals and reducing the number of stages on the fly when the input power is high. The former solution may be very detrimental to sensitivity as it would cause a capacitive divider between and bulk parasitics in diodes having the RF signal applied to their source. The latter may be risky as well, since the switches to perform the operation may be critical in terms of capacitance, leakage or noise.

4. Implementation Criteria

4.1. Parameter Optimization

Detailed study of this ED architecture has shown there are two different sources for loss of signal within the ED with respect to the theoretical value for (3). The first one is MOSFET junction leakage within the diodes, whereas the second one is non-perfect coupling of the input signal to the internal gate and drain nodes. These phenomena directly translate into a reduction in the gain of the ED, which was modeled as a multiplication of the theoretical gain by a factor independent of N, yielding

| (20) |

and ultimately, at room temperature,

| (21) |

The MOSFET type featuring the lower n available within the chosen technology has been selected in order to maximize ED output amplitude, as in (20). Also, a high resistivity resistor with low temperature coefficient is needed for . The same holds for if implemented as an actual resistor.

As for capacitors, the choice of type and polarity for and may have a critical impact on sensitivity. Unless parasitics towards ground are negligible with respect to the nominal capacitance value or are evenly distributed between the two terminals of the capacitors, it is necessary to determine on which side it is best to leave most of the parasitics themselves—towards the RF input or the internal diode nodes. If non-negligible coupling capacitor parasitics are placed towards the RF input, a significant increase in the overall input capacitance of the ED, , may occur, ultimately reducing the matching network gain (5). On the other hand, if non-negligible coupling capacitor parasitics are placed towards the internal diode nodes, capacitive dividers may result in a loss of signal at the diode terminals themselves. It is possible to determine which of the two situations is best by simulation. In both our versions, an assessment of this aspect has led us to place most of and parasitics, which amount to roughly one third of their nominal capacitance value, towards the RF input. Capacitor losses, in particular on , also need to be assessed.

First, a preliminary design was carried out based on the formulas reported in Section 3.1, with an value close enough to unity in the whole operating temperature range and the following remarks, with reference to Figure 2:

High L in and for good mirroring.

High W in and for low to make room for and .

and highest possible allowed by the technology considering area occupation to minimize the static current of the PTAT block.

Lowest possible for effectively cutting the chosen carrier RF frequency.

Lowest possible and for effectively coupling the input signal to the internal diode nodes at the chosen carrier RF frequency.

However, mismatch between the diodes and MOSFET may negatively affect temperature compensation precision. Let us assume that a difference exists between the average threshold voltage of the diodes and that of MOSFET , , due to mismatch. Since mismatch is random, can have both signs. Equation (15) then becomes

| (22) |

so the difference between the actual and the ideal one is

| (23) |

The error in corresponding to a 1- error in is then

| (24) |

where is the well-known Pelgrom coefficient [23]. Equation (24) shows that it is beneficial to increase to ultimately reduce temperature compensation degradation due to . This poses a design trade-off between , and thus , and .

Since the equations for and are somewhat ideal, parameter optimization has to be performed based on chain sensitivity optimization and temperature compensation afterwards. As for diode area, a minimal for the diodes translates into a smaller , which requires smaller and values at a parity of signal coupling at diode terminals, and thus a smaller . This results in a higher gain at parity, from (5). On the other hand, a non-minimal for the diodes is required to increase temperature compensation accuracy (24), thus reducing sensitivity spread, even if pad parasitics may significantly contribute to .

4.2. Two Implemented Versions

The proposed ED has been designed using an STMicroelectronics 90 nm CMOS technology with a 0.6 V supply voltage to receive 1 kbps OOK-modulated signals with a 433 MHz carrier frequency. Two different versions are provided in order to gain further insight into implementation criteria: version 1 with minimized effects of mismatch on temperature compensation, thus sensitivity, and version 2 with minimized and area.

4.2.1. Version 1, Minimal Mismatch

This version has been designed with non-minimal diode . Its calculated optimal at room temperature is roughly . N = 60 has been chosen based on the trade-off between an value close to unity and manageable and values—see Section 3.1. The theoretical for each diode stage results from the optimal and the chosen N. The actual value is . The dimensions of the diodes are W = 450 nm × 2 and L = 450 nm. The values for the filtering and coupling capacitors are = 36 fF implemented as 1.2-V poly-on-pplus capacitors. The simulated is 1.68 pF. has been implemented as a diode-connected MOSFET with a null . According to simulations, factor k is roughly 0.75. The dimensions of are W = 450 nm and L = 450 nm, whereas has the same dimensions as the diodes, . A 100 nA biasing current in the baseband amplifier following the ED, which translates into a in the chosen technology, would yield in the worst case, namely, for , i.e., at 120 °C when the PTAT block is not used. This confirms that can be considered roughly equal to unity when calculating . The PTAT block, start-up included, consumes 6 nW at 20 °C, 1.4 nW at −40 °C and 12.2 nW at 120 °C.

4.2.2. Version 2, Minimal Area

This version has been designed with minimal diode . Its calculated optimal at room temperature is roughly again with N = 60 diode stages, resulting in a theoretical and an actual for each diode. The dimensions of the diodes are W = 120 nm and L = 100 nm. The values for the filtering and coupling capacitors are = 13 fF implemented as 1.2-V poly-on-pplus capacitors. The simulated is 0.62 pF. has been implemented as a diode-connected MOSFET with a null . According to simulations, factor k is roughly 0.75, around the same as for version 1 since junction losses are lower due to a lower diode area, but non-perfect coupling of the input signal to the internal gate and drain nodes is more significant due to smaller coupling capacitors. The dimensions of are W = 450 nm and L = 100 nm, whereas those of are W = 450 nm × 2, L = 100 nm and . Again, a 100 nA biasing current in the baseband amplifier following the ED is supposed in order to assume as roughly equal to unity in all cases. The PTAT block, start-up included, consumes 14 nW at 20 °C, 3.9 nW at −40 °C and 33.8 nW at 120 °C.

4.3. Temperature Compensation Validation

The aim of this section is the validation of the temperature compensation mechanism, i.e., proving its functionality and the performance benefits its use brings to the ED in terms of reduction in the chain sensitivity temperature variation. This has been carried out using the minimal mismatch version, as in Section 4.2.1.

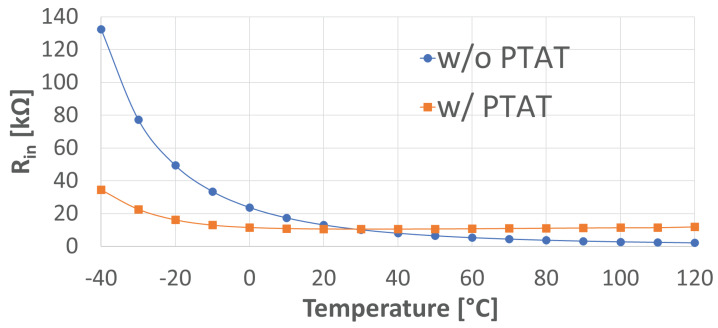

The temperature compensation mechanism proves to be effective in reducing the variations of , which is a very rapidly varying function of temperature without the use of the PTAT, as shown in (9). Figure 6 shows the simulated : variations are significantly smaller with the use of the PTAT block than without its use. It is important to note that, even with the use of the PTAT block, is not completely flat across the operating temperature range, most likely due to the fact that the assumptions used, especially that for which the difference in between the diodes and does not significantly affect , are not entirely met.

Figure 6.

Version 1 simulated with and without the use of the PTAT block.

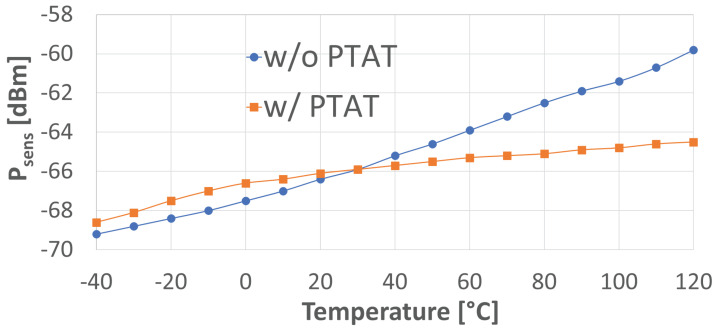

According to [12], at the theoretical sensitivity, the SNR at the output of the amplifier is equal to . With reference to Figure 3, the values for corresponding to the theoretical sensitivity are estimated through simulations. Figure 7 shows the values for corresponding to , i.e. , when the PTAT block is used and when it is not used. In both cases, of the subsequent amplifier is considered equal to unity, as mentioned above. The input matching network is a standard LC network with [12], whereas is assumed equal to 3 pF, where 1.68 pF and is supposed to be close to 1.3 pF, which is plausible. ED noise bandwidth is around 1 kHz, i.e., around . When the PTAT block is not used, and are set to the values corresponding to those set by the PTAT block at room temperature. Simulations were carried out from −40 °C to 120 °C and show that the use of the PTAT block has a positive impact on the stability of sensitivity over temperature, actually yielding a 5 dB reduction in sensitivity temperature variation across the operating range, as reported in Figure 7. As a matter of fact, the worst impact of the lack of compensation appears to be at high temperatures, most likely due to the fact that, here, without PTAT is lower than its nominal designed value, i.e., at 20 °C, drastically reducing as in (5). This also explains why sensitivity is affected very little at low temperatures.

Figure 7.

Version 1 simulated with and without the use of the PTAT block.

4.4. Implementation Comparison

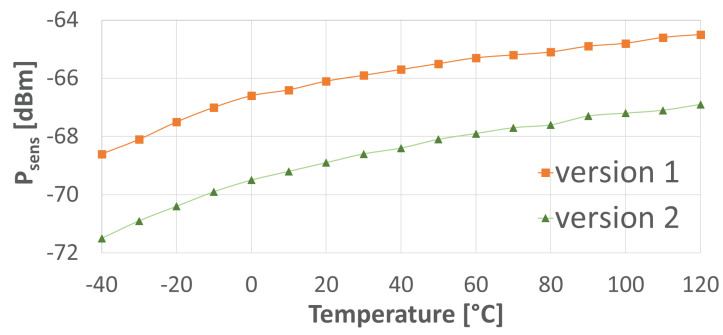

A comparison between the two implemented versions is carried out in terms of estimated overall chain sensitivity. Figure 8 reports the values for with the use of the PTAT block employing versions 1 and 2, again assuming pad parasitics to be around 1.3 pF. The nominal sensitivity trend across temperature looks similar in the two cases, but sensitivity is better for version 2, i.e., with minimal diodes, as the corresponding curve is shifted downwards by an amount of 2–3 dBs. We carried out 100-run Monte Carlo simulations of versions 1 and 2 of the ED at 120 °C, which for both designs is the worst-case scenario in terms of sensitivity. They demonstrated a 1- sensitivity spread of 0.44 dB and 1.09 dB for versions 1 and 2, respectively, indicating the overall superior sensitivity performance of version 2.

Figure 8.

Simulated of versions 1 and 2, both with the use of the PTAT block.

Table 3 summarizes the main results for the two versions.

Table 3.

Comparison table between the two implemented versions.

| Version 1 | Version 2 | |

|---|---|---|

| Target bitrate [kbit/s] | 1 | 1 |

| Power consumption at 20 °C [nW] | 6 | 14 |

| Diode dimensions [nm] | (450 × 2)/450 | 120/100 |

| Coupling capacitances [fF] | 36 | 13 |

| [pF] | 3 | 1.9 |

| at 20 °C [k] | 10.7 | 10 |

| for −40 ÷ 120 °C [k] | 24 | 13.7 |

| at 20 °C [dBm] | −66.1 | −68.9 |

| for −40 ÷ 120 °C [dB] | 4.6 | 4.6 |

| at 120 °C [dB] | 0.4 | 1.1 |

5. Conclusions

EDs are often used in communication applications, such as in Wake-Up Receivers, which are widely employed in IoT Wireless Sensor Networks. The target of this paper is to develop a passive ED with a temperature compensation mechanism in order to reduce the overall receiving chain sensitivity loss due to temperature changes. This is accomplished by keeping the input resistance of the ED constant with temperature with the aim of making it a constant load for the preceding matching network.

The central idea of the paper has been proven through a design in an STMicroelectronics 90 nm CMOS technology, receiving 1 kbps OOK-modulated packets with a 433 MHz carrier frequency and a 0.6 V supply. The use of the PTAT block yields a 5 dB reduction in sensitivity temperature variation across the −40 °C to 120 °C range. Moreover, two different implementations were compared, one targeting minimal mismatch and the other one targeting minimal area. The minimal area version appears to be better in terms of estimated overall chain sensitivity at all temperatures, despite a higher sensitivity spread.

Abbreviations

The following abbreviations are used in this manuscript:

| ED | Envelope Detector |

| OOK | On–Off Keying |

| WuRX | Wake-Up Radio Receivers |

| IoT | Internet of Things |

| PTAT | Proportional-to-Absolute Temperature |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor |

| SNR | Signal-to-Noise Ratio |

| NF | Noise Figure |

Author Contributions

“State-of-the-Art Passive EDs with Temperature Compensation”, all authors; “ED and PTAT Block Description”–“ED model and receiving chain sensitivity optimization”, A.M.E., M.D. and L.P.; “ED and PTAT Block Description”–“Temperature compensation through the PTAT block”, all authors; “ED and PTAT Block Description”–“ED differential approach”, A.M.E., M.D., L.P., E.F.S. and A.G.; “ED and PTAT Block Description”–“Maximum input power”, A.M.E., M.D., L.P., E.F.S. and A.G.; “Implementation Criteria”, all authors; “Conclusion”, all authors. All authors have read and agreed to the published version of the manuscript.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Data is contained within the article.

Conflicts of Interest

Authors Alessia Maria Elgani, Matteo D’Addato, Roberto Canegallo and Giulio Ricotti were employed by the company STMicroelectronics. The remaining authors declare that the research was conducted in the absence of any commercial or financial relationships that could be construed as a potential conflict of interest.

Funding Statement

This research received no external funding.

Footnotes

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

References

- 1.Mercier P., Calhoun B., Wang P.-H., Dissanayake A., Zhang L., Hall D., Bowers S. Low-Power RF Wake-Up Receivers: Analysis, Tradeoffs, and Design. IEEE Open J. Solid-State Circuits Soc. 2022;2:144–164. doi: 10.1109/OJSSCS.2022.3215099. [DOI] [Google Scholar]

- 2.Kandris D., Nakas C., Vomvas D., Koulouras G. Applications of Wireless Sensor Networks: An Up-to-Date Survey. Appl. Syst. Innov. 2020;3:14. doi: 10.3390/asi3010014. [DOI] [Google Scholar]

- 3.Pizzotti M., Perilli L., Del Prete M., Fabbri D., Canegallo R., Dini M., Masotti D., Costanzo A., Franchi Scarselli E., Romani A. A Long-Distance RF-Powered Sensor Node with Adaptive Power Management for IoT Applications. Sensors. 2017;17:1732. doi: 10.3390/s17081732. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 4.You S., Eshraghian J.K., Iu H.C., Cho K. Low-Power Wireless Sensor Network Using Fine-Grain Control of Sensor Module Power Mode. Sensors. 2021;21:3198. doi: 10.3390/s21093198. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 5.Perilli L., Scarselli E.F., La Rosa R., Canegallo R. Wake-Up Radio Impact in Self-Sustainability of Sensor and Actuator Wireless Nodes in Smart Home Applications; Proceedings of the 2018 Ninth International Green and Sustainable Computing Conference (IGSC); Pittsburgh, PA, USA. 22–24 October 2018. [Google Scholar]

- 6.Polonelli T., Niculescu V., Burger T., Magno M. A −79 dBm μ-Watt Wake-Up Receiver for Energy Efficient ISM and LoRa Communication; Proceedings of the 2024 IEEE International Instrumentation and Measurement Technology Conference (I2MTC); Glasgow, UK. 20–23 May 2024. [Google Scholar]

- 7.D’Addato M., Elgani A.M., Perilli L., Franchi Scarselli E., Gnudi A., Canegallo R., Ricotti G. A Gated Oscillator Clock and Data Recovery Circuit for Nanowatt Wake-Up and Data Receivers. Electronics. 2021;10:780. doi: 10.3390/electronics10070780. [DOI] [Google Scholar]

- 8.Taris T., Kraimia H., Belot D., Deval Y. An FSK and OOK Compatible RF Demodulator for Wake Up Receivers. J. Low Power Electron. Appl. 2015;5:274–290. doi: 10.3390/jlpea5040274. [DOI] [Google Scholar]

- 9.Zaraket E., Murad N.M., Yazdani S.S., Rajaoarisoa L., Ravelo B. An overview on low energy wake-up radio technology: Active and passive circuits associated with MAC and routing protocols. J. Netw. Comput. Appl. 2021;190:103140. doi: 10.1016/j.jnca.2021.103140. [DOI] [Google Scholar]

- 10.Elgani A.M., Renzini F., Perilli L., Franchi Scarselli E., Gnudi A., Canegallo R., Ricotti G. A Clockless Temperature-Compensated Nanowatt Analog Front-End for Wake-Up Radios Based on a Band-Pass Envelope Detector. IEEE Trans. Circuits Syst. I Regul. Pap. 2020;67:2612–2624. doi: 10.1109/TCSI.2020.2987850. [DOI] [Google Scholar]

- 11.Elgani A.M., D’Addato M., Perilli L., Franchi Scarselli E., Canegallo R. Design and Characterization of an Active Low-Pass Envelope Detector for Wake-Up Radio Receivers; Proceedings of the 2022 17th Conference on Ph.D Research in Microelectronics and Electronics (PRIME); Villasimius, Italy. 12–15 June 2022. [Google Scholar]

- 12.Mangal V., Kinget P. Sub-nW Wake-Up Receivers With Gate-Biased Self-Mixers and Time-Encoded Signal Processing. IEEE J. Solid-State Circuits. 2019;54:3513–3524. doi: 10.1109/JSSC.2019.2941010. [DOI] [Google Scholar]

- 13.Moody J., Bassirian P., Roy A., Liu N., Barker S., Calhoun B., Bowers S. Interference Robust Detector-First Near-Zero Power Wake-Up Receiver. IEEE J. Solid-State Circuits. 2019;54:2149–2162. doi: 10.1109/JSSC.2019.2912710. [DOI] [Google Scholar]

- 14.Dissanayake A., Moody J., Bishop H., Truesdell D., Muhlbauer H., Lu R., Gao A., Gong S., Calhoun B., Bowers S. A −108 dBm Sensitivity, −28 dB SIR, 130 nW to 41 μW, Digitally Reconfigurable Bit-Level Duty-Cycled Wakeup and Data Receiver; Proceedings of the 2020 IEEE Custom Integrated Circuits Conference (CICC); Boston, MA, USA. 22–25 March 2020. [Google Scholar]

- 15.Liu L., Xie S., Liao X., Qin Z., Wang J. A 0.3-V, —75.8-dBm Temperature-Robust Differential Wake-Up Receiver for WSNs. Sensors. 2022;22:20593–20602. doi: 10.1109/JSEN.2022.3205063. [DOI] [Google Scholar]

- 16.Mangal V., Kinget P. An ultra-low-power wake-up receiver with voltage-multiplying self-mixer and interferer-enhanced sensitivity; Proceedings of the 2017 IEEE Custom Integrated Circuits Conference (CICC); Austin, TX, USA. 30 April–3 May 2017. [Google Scholar]

- 17.Jiang H., Wang P.-H., Gao L., Pochet C., Rebeiz G., Hall D., Mercier P. A 22.3-nW, 4.55 cm2 Temperature-Robust Wake-Up Receiver Achieving a Sensitivity of —69.5 dBm at 9 GHz. IEEE J. Solid-State Circuits. 2020;55:1530–1541. doi: 10.1109/JSSC.2019.2948812. [DOI] [Google Scholar]

- 18.Shen X., Duvvuri D., Bassirian P., Bishop H., Liu X., Dissanayake A., Zhang Y., Blalock T., Calhoun B., Bowers S. A 184-nW, —78.3-dBm Sensitivity Antenna-Coupled Supply, Temperature, and Interference-Robust Wake-Up Receiver at 4.9 GHz. IEEE Trans. Microw. Theory Tech. 2022;70:744–757. doi: 10.1109/TMTT.2021.3127550. [DOI] [Google Scholar]

- 19.Huang K.-K., Brown J., Collins N., Sawyer R., Yahya F., Wang A., Roberts N., Calhoun B., Wentzloff D. A Fully Integrated 2.7 μW —70.2 dBm-Sensitivity Wake-Up Receiver with Charge-Domain Analog Front-End, —16.5 dB-SIR, FEC and Cryptographic Checksum; Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC); San Francisco, CA, USA. 13–22 February 2021. [Google Scholar]

- 20.Liao X., Xie S., Xu J., Liu L. A 0.4 V, 6.4 nW, —75 dBm Sensitivity Fully Differential Wake-Up Receiver for WSNs Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2022;69:2794–2804. doi: 10.1109/TCSI.2022.3163801. [DOI] [Google Scholar]

- 21.Fromm R., Kanoun O., Derbel F. An Improved Wake-Up Receiver Based on the Optimization of Low-Frequency Pattern Matchers. Sensors. 2023;23:8188. doi: 10.3390/s23198188. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 22.D’Addato M., Elgani A.M., Perilli L., Franchi Scarselli E., Gnudi A., Canegallo R., Ricotti G. A 54.8-nW, 256-bit Codeword Temperature-Robust Wake-Up Receiver minimizing False Wake-Ups for Ultra-Low-Power IoT Systems; Proceedings of the 2022 IEEE International Conference on Electronics, Circuits and Systems (ICECS); Glasgow, UK. 24–26 October 2022. [Google Scholar]

- 23.Pelgrom M.J.M., Duinmaijer A.C.J., Welbers A.P.G. Matching properties of MOS transistors. IEEE J. Solid-State Circuits. 1989;24:1433–1439. doi: 10.1109/JSSC.1989.572629. [DOI] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Data Availability Statement

Data is contained within the article.