Abstract

This paper presents a compact V-band low-noise amplifier (LNA) featuring temperature compensation, implemented in a 130 nm SiGe BiCMOS process. A negative temperature coefficient bias circuit generates an adaptive current for temperature compensation, enhancing the LNA’s temperature robustness. A T-type inductive network is employed to establish two dominant poles at different frequencies, significantly broadening the amplifier’s bandwidth. Over the wide temperature range of −55 °C to 85 °C, the LNA prototype exhibits a gain variation of less than 1.5 dB at test frequencies from 40 GHz to 65 GHz, corresponding to a temperature coefficient of 0.01 dB/°C. At −55 °C, 25 °C, and 85 °C, the measured peak gains are 25.5 dB, 25 dB, and 24.4 dB, respectively, with minimum noise figures (NF) of 3.0 dB, 3.5 dB, and 4.2 dB, and DC power consumptions of 22.3 mW, 27.6 mW, and 34.4 mW. Moreover, the total silicon area of the LNA chip is 0.37 mm2, including all test pads, while the core area is only 0.09 mm2.

Keywords: millimeter-wave (mm-wave), V-band, SiGe BiCMOS, temperature compensation, low-noise amplifier

1. Introduction

The V-band spans a wide frequency spectrum from 40 GHz to 75 GHz, making it an ideal candidate for short-range communications and satellite detection due to its short wavelength and sensitivity to atmospheric conditions [1]. These applications have driven the increasing demand for V-band front-end modules, particularly in the 60 GHz band, which has been standardized by IEEE 802.15.3c [2,3]. Given the complex environments encountered in satellite detection and communications, minimizing receiver performance fluctuations across varying ambient temperatures is crucial to ensuring stable and reliable millimeter-wave (mm-wave) front ends. As the first active component in a millimeter-wave receiver, the low-noise amplifier (LNA) amplifies weak signals received by the antenna while suppressing noise in subsequent stages, ensuring a good signal-to-noise ratio. Consequently, high-performance LNAs with robust temperature tolerance have garnered significant attention.

III-V compound processes, such as indium phosphide (InP) and gallium arsenide(GaAs), are known for their high electron mobility, low-noise figure (NF), and high-power density, making them perfect for mm-wave applications, especially in the design of LNAs and power amplifiers (PAs), where they offer exceptional performance. For example, a 50–75 GHz broadband LNA using the 35 nm InP HEMT process was developed, providing a gain of 15–25 dB and an optimal NF of up to 2.2 dB [4]. Using self-biasing and negative feedback techniques, Macro et al. implemented two broadband LNAs in the V-band and Q-band with a 70 nm GaAs process [5,6]. The V-band LNA achieved an NF of less than 1.7 dB and a gain of 15 dB, while the Q-band LNA achieved an NF of less than 1.55 dB and a peak gain of 19 dB. While compound-based LNAs offer superior performance, they generally come with higher power consumption and manufacturing costs, and they lag behind CMOS/SiGe BiCMOS processes in terms of integration and compatibility [7].

Due to aggressive device scaling, CMOS/SiGe BiCMOS technology has become a strong competitor to III-V group semiconductors for high-performance, cost-effective mm-wave integrated circuits. Silicon-based LNAs in V-band are published in [8,9,10,11,12,13,14], with most of the literature providing measured results at room temperature (25 °C) [8,9,10,11], leaving their temperature tolerance unknown. Xu et al. implemented a 60 GHz wideband LNA using an advanced 22 nm FD-SOI process. Benefiting from gain distribution techniques, this LNA achieved a 3 dB bandwidth of 18.5 GHz and a peak gain of 20.2 dB, with a minimum noise figure (NF) of 3.3 dB and power consumption of 8.1 mW. Through innovations in topology and circuit bias point design, the work in [9] reported an ultra-low-power wideband CMOS LNA in the V-band, consuming only 8.6 mW at 60 GHz with a low supply voltage of 0.8 V. It achieved a peak gain of 20.4 dB, though the NF of 5 dB leaves room for improvement. Leveraging digitally controlled current reuse, Chang et al. [10] developed a low-power CMOS digitally controlled variable-gain LNA, achieving a gain control range of 6.6–19.8 dB with a 3 dB bandwidth of over 10 GHz. However, while optimizing for low power and wideband performance, compromises were made in NF and input return loss. References [12,13,14] propose LNAs with temperature tolerance characteristics. By utilizing a bias circuit based on current mirrors and operational amplifiers (OPAMPs), these designs effectively mitigate the gain reduction of the LNA caused by rising temperatures. The prototype of the 60 GHz LNA shows a gain variation of less than 1.7 dB over the temperature range of −20 °C to 100 °C, with a 3 dB bandwidth exceeding 11.5 GHz, although the peak gain is only 9.9 dB. Reference [13] describes a G-band SiGe BiCMOS LNA that employs a bias network based on positive temperature coefficient (PTAT) and negative temperature coefficient (CTAT) resistors. This prototype exhibits a gain variation of less than 2.2 dB in the frequency range of 180–210 GHz over temperatures from −20 °C to 80 °C, with a total power consumption of 35 mW. A standardized temperature compensation design method for mm-wave amplifier design is presented in reference [14], which adjusts the bias circuit by optimizing the reference voltage. This method has been validated in a Ka-band amplifier, although the temperature compensation bias circuit is relatively complex and occupies a significant area.

In this paper, a SiGe BiCMOS V-band wideband LNA with excellent temperature tolerance is proposed, featuring high gain, low noise, and a compact core area. The design employs a current mirror-based adaptive temperature compensation circuit that is simple, easy to implement, and has a small footprint, effectively counteracting temperature-induced variations in gain and NF. Furthermore, a T-type pole-tuning network significantly extends the LNA’s bandwidth. The paper is organized as follows: Section 2 details the circuit design of the proposed LNA; Section 3 presents experimental results to verify the design methodology; and the conclusions are summarized in Section 4.

2. Circuit Analysis and Design

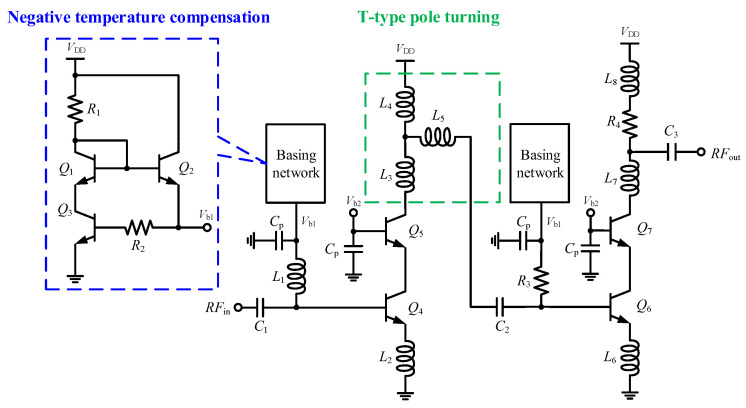

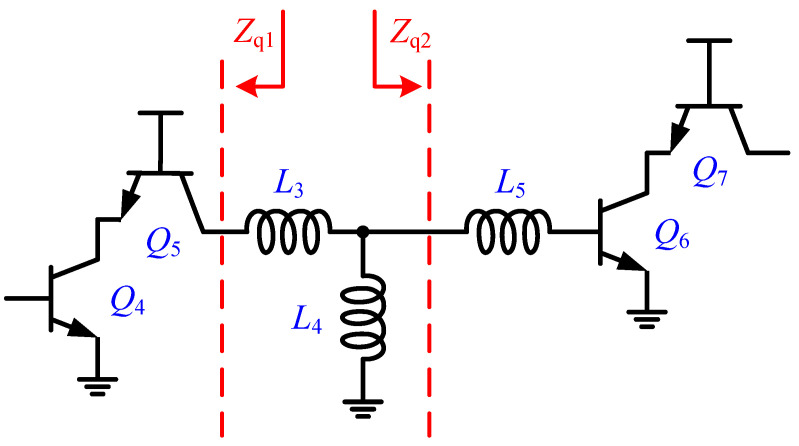

Figure 1 illustrates the circuit diagram of the proposed V-band temperature-compensated LNA, which consists of two cascaded common emitter–common base (CE-CB) amplifier stages, a T-type pole tuning network, and a temperature-compensated bias circuit. The CE-CB topology was chosen over common emitter (CE) and common base (CB) configurations because it offers higher voltage gain, better reverse isolation, and the ability to simultaneously optimize noise figure and power matching. The T-type pole tuning network, made up of inductors L3, L4, and L5, is used for interstage matching in the LNA, allowing for adjustment of the high- and low-frequency dominant poles to achieve a flat wideband gain–frequency response. To counteract performance degradation due to temperature variations, a negative temperature coefficient bias circuit generates an adaptive bias current for the base terminals of heterojunction bipolar transistors (HBTs) Q4 and Q6, significantly improving the LNA’s temperature robustness.

Figure 1.

Schematic of the proposed LNA.

2.1. Size of Transistor and Bias Conditions

It is crucial to determine the sizes and biasing conditions of the active devices before designing the passive components, which ultimately influence the overall performance, such as the minimum noise figure (NFmin), maximum gain (Gmax), and input 1 dB compression point (IP1dB). For LNA designs based on current-restricted HBTs, the current density (JC) comprehensively reflects the size and biasing state. According to [15], at the same frequency, transistors of different sizes can achieve NFmin or Gmax at the same current density. JC of HBTs can be expressed by emitter current per emitter length, written as follows:

| (1) |

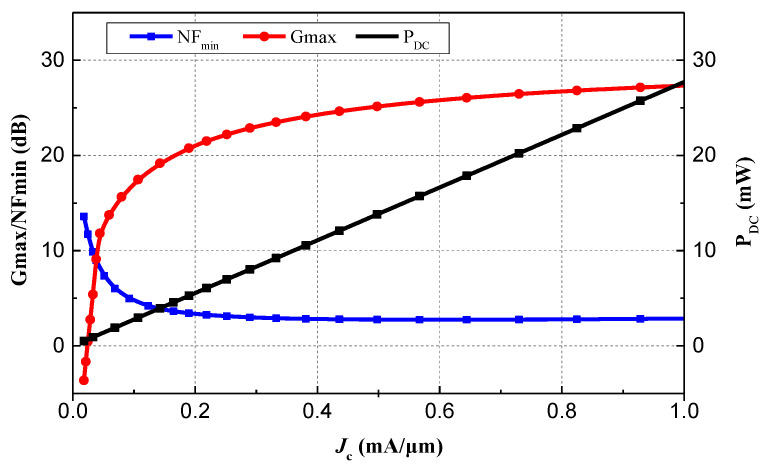

The emitter width of HBTs is typically selected to be a minimum of 120 nm for optimal high-frequency performance. Noting that in addition to Gmax and NFmin, the power consumed (PDC) should also be considered. The variation of Gmax, NFmin, and PDC verse current density when LE = 8 um at a frequency of 60 GHz is shown in Figure 2. To comprehensively evaluate the effect of JC on the overall performance of the LNA, a figure of merit (FoM) is introduced, which can be expressed as follows:

| (2) |

Figure 2.

Simulated Gmax, NFmin, and PDC with variations of JC at 60 GHz and 25 °C when LE = 8 μm.

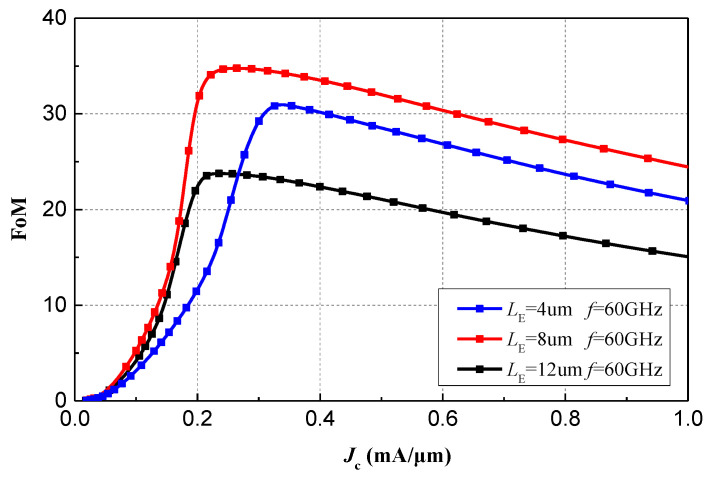

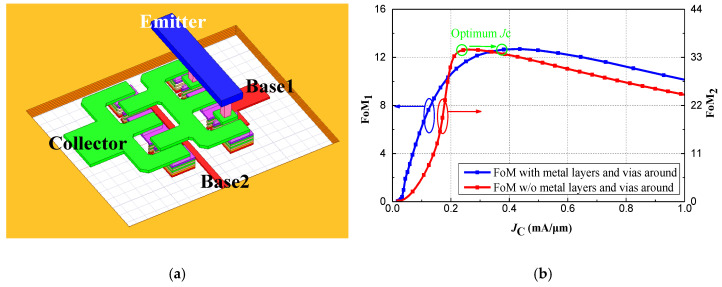

By analyzing the JC and FoM values at different emitter lengths, the optimal device size and biasing state for the desired operating frequencies can be determined. As shown in Figure 3, the HBT device with an emitter length of LE = 8 μm achieves a better FoM at an approximate current density of 0.24 mA/μm compared to sizes of LE = 4 μm and LE = 12 μm. Furthermore, in the V-band frequencies, the parasitic parameters caused by the metal interconnections and vias of the HBT devices cannot be overlooked. Therefore, it is necessary to model the passive interconnects surrounding the HBT devices and perform full-wave electromagnetic simulations. Considering the current handling capacity of a single HBT device, a parallel configuration of multiple small-sized transistors is preferred while maintaining the same emitter length. The CB-CE stage employs a parallel and staggered layout of four HBTs with an emitter length of 4 μm, which is also modeled in 3D using full-wave electromagnetic simulation software, as shown in Figure 4a. Figure 4b compares the modeled FoM1 of the interconnect lines around the HBT device with the unmodeled FoM2. It is evident that significant parasitic effects degrade the FoM, with the optimal current density increasing from 0.24 mA/μm to 0.38 mA/μm. Therefore, after considering the design requirements, the current density for the first phase is ultimately set at 0.32 mA/μm.

Figure 3.

Simulated FoM with variations of JC at 60 GHz and 25 °C under different LE.

Figure 4.

(a) The 3D model of first stage of LNA; (b) Comparation between FoM1 and FoM2 with variations of JC at 60 GHz and 25 °C when LE = 8 μm.

2.2. Interstage Bandwidth Extension

The L-shaped and Π-shaped pole tuning networks have been proven to be effective means of bandwidth extension and are widely used in broadband LNA designs [16,17]. In this design, a T-type inductive pole tuning network is employed for interstage matching to achieve bandwidth extension.

Figure 5 presents the schematic of the inter-stage T-type pole turning network. Zq1 denotes the output impedance of the first stage. To illustrate the effects of L3 and L4 on the two main poles: PoleL and PoleH, combining L5 of the T-type matching network with the input impedance of the second-stage cascode into Zq2. Zq1 and Zq2 can be expressed as follows:

| (3) |

| (4) |

where ro4/5 and Cbe5/6 are the equivalent output resistors of Q4/5 and the equivalent input parasitic capacitors of Q5/6, respectively, while gm5/6 is the transconductance of Q5/6. Noting that, the Zq1 features capacitive characteristics, while the Zq2 features inductive characteristics, and we define Zq1 = Rq1 + 1/sCq1 and Zq2 = Rq2 + sLq2 for analytical convenience. Then the simplified Av(s) of the two-stage cascode can be expressed as follows:

| (5) |

Figure 5.

The schematic of the inter-stage T-type network.

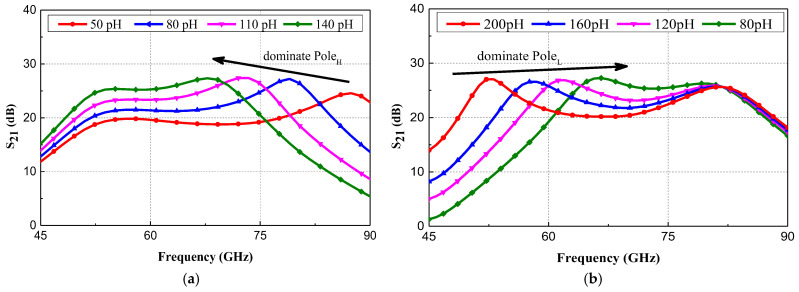

The denominator of Figure 5 features two poles that are mainly dominated by L3 and L4. Figure 6 show the graphical analysis through S-parameter simulations that demonstrate the changes of the dominate PoleL and PoleH with the variations of L3 and L4. The increase of L3 will move PoleH to lower frequency with minimal impact on PoleL. In contrast, the decrease of L4 will move PoleL to a higher frequency with minimal impact on PoleH. Thus, a wideband gain–frequency response can be realized by carefully designing the parameters of the T-type inductive network to tune the positions of the high-frequency and low-frequency dominant poles.

Figure 6.

(a) S21 of the proposed LNA when L3 vary from 50 to 140 pH; (b) S21 of the proposed LNA when L4 vary from 50 to 140 pH.

2.3. Negative Temperature Coefficient Compensation Circuit

Due to the inherent factors of the silicon-based process, thermal variation will inevitably cause unexpected changes in the electron mobility and threshold voltage of the transistors, which will also affect the LNA performance. HBT devices are current-controlled devices, and the variations in collector current caused by temperature change are more pronounced. Therefore, a robust design that stabilizes gain over a wider temperature range is desirable.

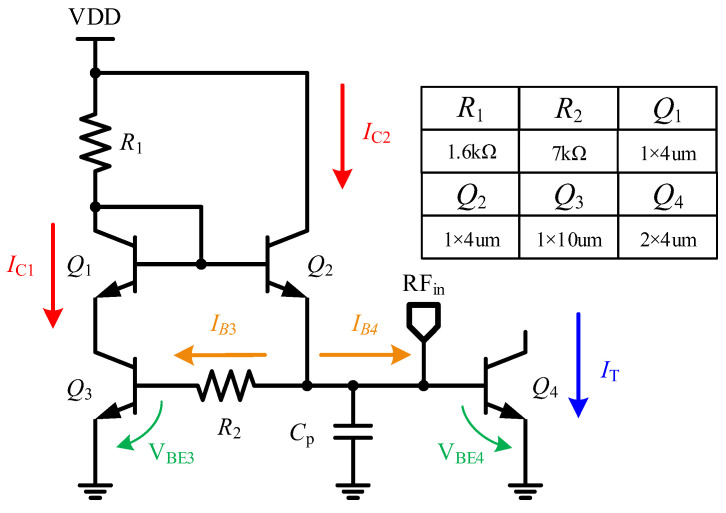

Figure 7 is the schematic of the biasing circuit and the parameters of the HBT and resistors in the proposed LNA. The collector current of Q4 can be expressed as follows:

| (6) |

where VT = KT/q, and the saturation current IS4 ∝ μKTni2. For convenience, q and k can be regarded as fixed coefficients, T is the absolute temperature, μ represents the carrier mobility, and ni denotes the intrinsic carrier concentration of silicon. Noting that μ ∝ μ0T1+m, ni2 ∝ T3exp(−Eg/KT) [18]. Then IS4 can be expressed as follows:

| (7) |

where b is regarded as a proportion factor; and Eg and m are assumed to be constant and the values of these in HBT are approximately 1 eV and −1.5, respectively. Substituting (7) into (6) we obtain the following:

| (8) |

Figure 7.

The schematic of the NTC biasing circuit in the proposed LNA.

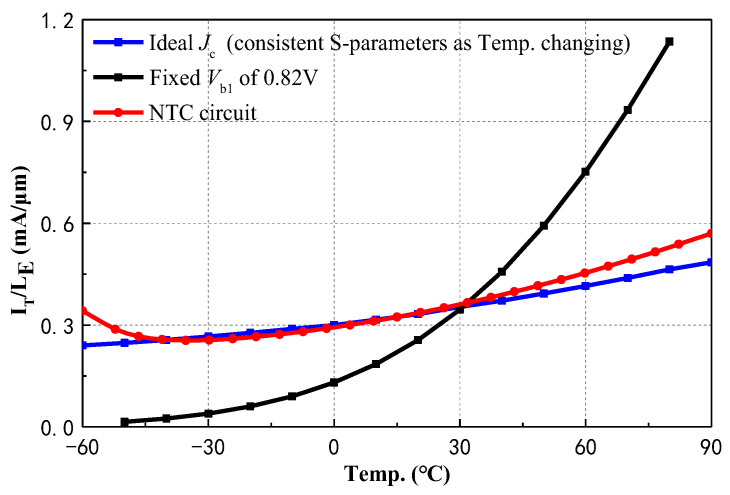

From (7) and (8), high sensitivity of IS4 to temperature greatly affects robustness of HBT to temperature. It is essential to introduce a compensation biasing circuit with a negative temperature coefficient (NTC) to ensure Q4 operates at an optimal JC as the temperature changes and, referring to the method in [14], the optimal JC at each temperature should be obtained first. As shown in Figure 8, the blue curve represents the ideal JC that obtained through simulations to ensure the same S-parameter at each temperature. The black curve illustrates the JC with temperature without the temperature compensation circuit. Although the optimal JC is achieved at 25 °C, there are significant variations in JC with temperature fluctuations, leading to considerable deviations from the ideal curve. The red curve represents the JC after implementing the NTC circuit. While there are slight deviations from the ideal curve at −60 °C and 90 °C, the fitting is ideal within the range of −55 to 85 °C, which indicates that the S-parameters will not experience significant variations.

Figure 8.

Comparison of JC in basing situations of fixed Vb1, NTC circuit, and ideal JC.

In Figure 7, R2 is a resistor that exhibits good temperature characteristics, and Cp is bypass capacitance to minimize the influence of the biasing circuit. R1, Q1, and Q2 form a conventional current mirror structure. So, assuming IE2 = nIE1 and n is a constant that shows slight sensitive to temperature. Q4 relies on the base current IB4 to control the collector current IT, with a current gain of β4. Therefore, Equation (6) can be derived.

| (9) |

The KVL equation between Q3 and Q4 can be derived as follows:

| (10) |

IT can be derived by substituting (6) and (9) into (10), as follows:

| (11) |

The temperature-sensitive parameters, IE and IS, cancel the effect of T in IE4IS3/IE3IS4. Additionally, the slow variation of logarithmic ln(IE4IS3/IE3IS4) with T also reduces the impact of the temperature.

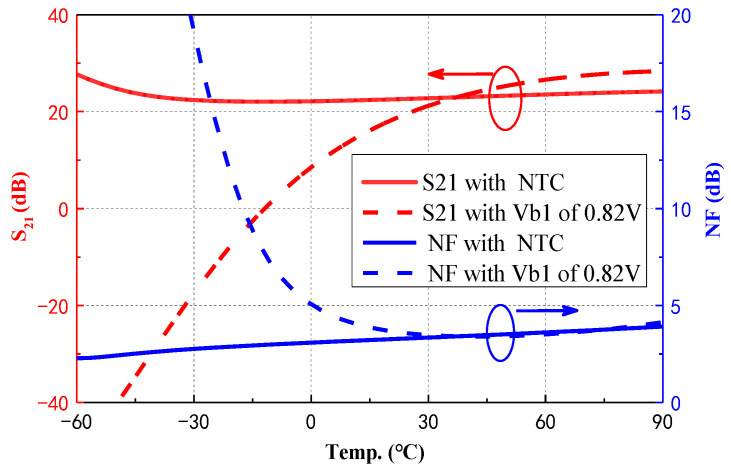

To intuitively demonstrate the compensatory effects of the proposed NTC on the LNA performance, Figure 9 presents simulated results of small-signal gain (S21) and NF as a function of temperature at a fixed bias voltage under NTC conditions at an operating frequency of 55 GHz. In the uncompensated scenario, the gain and noise figure of the LNA sharply degrade as the temperature drops to around −15 °C, primarily due to the pronounced temperature sensitivity of the HBT devices. In contrast, with the implementation of the proposed NTC, both gain and NF remain stable over a broad temperature range from −60 °C to 90 °C, demonstrating remarkable robustness.

Figure 9.

Comparison between simulated S21 and NF in basing situations of fixed Vb1 and NTC at 55 GHz.

3. Experimental Validation and Results

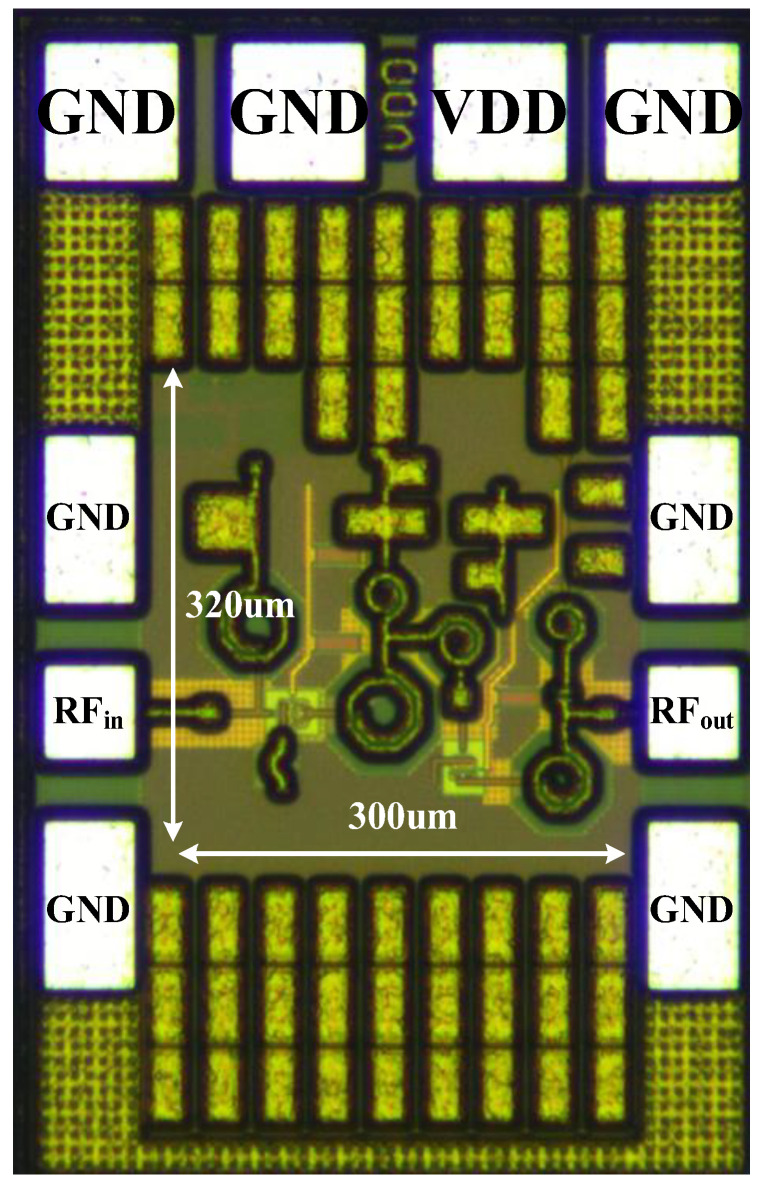

The proposed temperature compensation LNA is fabricated using a 0.13 μm SiGe BiCMOS process. Figure 10 shows the die micrograph of the proposed LNA. The whole chip occupies a silicon area of 0.49 mm × 0.76 mm including all testing pads and a core area of 0.3 mm × 0.32 mm.

Figure 10.

Microphotograph of the LNA chip.

An MPI TS200-SE probe station equipped with ground–signal–ground (G-S-G) probes with a 150 µm pitch was used for on-wafer testing and the calibration was performed using the standard short-open-load-through (SOLT) method. The S-parameters of LNA were measured using a Keysight PNA-X N5247B network analyzer(Keysight Technologies, Inc., Santa Rosa, CA, USA) with a maximum frequency range of 10 MHz to 67 GHz. Due to the limited calibration accuracy of the PNA-X N5247B network analyzer near its upper frequency limit of 67 GHz, the measurements in this work were conducted between the range of 40 GHz and 65 GHz.

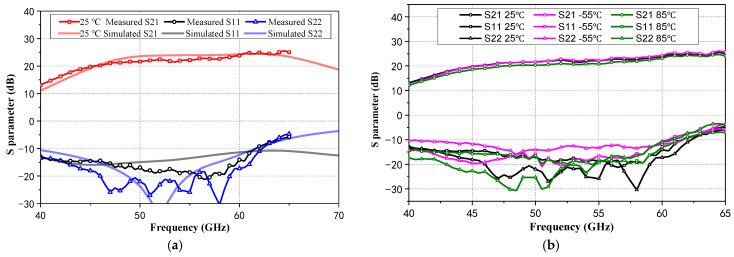

Figure 11a presents the comparison between simulated and measured S-parameters at 25 °C, which exhibits similar trends. From measured results, the LNA achieves a peak gain of 25 dB, a 3 dB bandwidth exceeding 11 GHz, and both S11 and S22 are better than −10 dB within 40~61 GHz. The measured S-parameters of the proposed LNA at −55 °C, 25 °C, and 85 °C are demonstrated in Figure 11b. Owing to the NTC basing network, the LNA’s measured S-parameters exhibit excellent robustness to temperature, with ΔGain less than 1.5 dB over 40~65 GHz.

Figure 11.

(a) Comparison between simulated and measured S-parameters at 25 °C; (b) Measured S-parameters from the proposed LNA at −55 °C, 25 °C, and 85 °C.

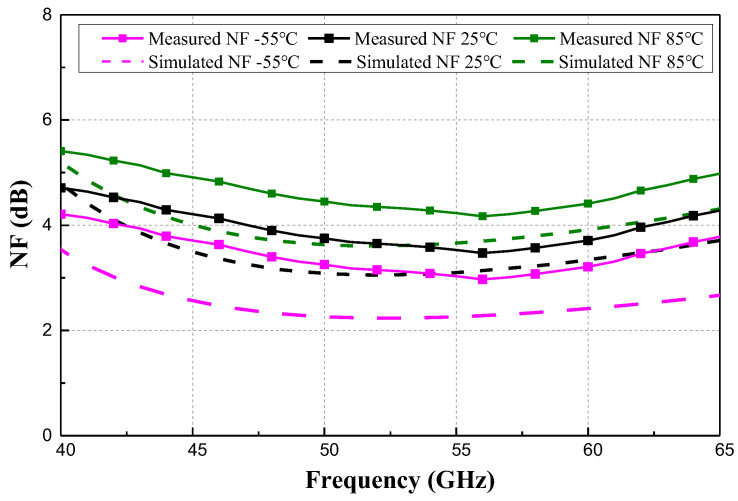

Figure 12 shows the measured and simulated NF of the proposed LNA at −55 °C, 25 °C, and 85 °C. At 25 °C and 85 °C, the measured results match well with the simulation. However, at −55 °C, the measured NF exhibits a deviation of 0.7 dB from the simulation. One factor for the discrepancy could be the decreasing of measured S21 at −55 °C compared to the simulation one, which leads to inadequate noise suppression.

Figure 12.

Simulated and measured NF at −55 °C, 25 °C, and 85 °C.

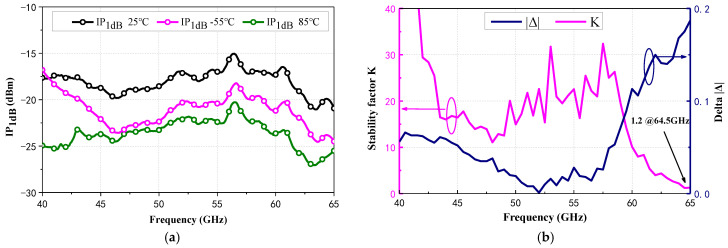

Figure 13a displays the measured input 1 dB compression point (IP1dB), which indicates the amplifier’s linearity. Unlike the measured S-parameters, the IP1dB is optimal at 25 °C. This could be attributed to two factors: (1) A high gain at −55 °C will sacrifice linearity. (2) The use of an NTC basing network, which adjusts JC to ensure good consistency in the S-parameters across −55~85 °C, may not be optimal for linearity. Within the measured frequency range of 40 to 65 GHz, the stability factor Kf was consistently greater than 1.2, while the delta Δ remained under 1. These results demonstrate that the proposed wideband LNA achieved stability in all operating conditions.

Figure 13.

(a) Measured IP1dB at −55 °C, 25 °C, and 85 °C; (b) Measured stability factor K and delta |△|.

Table 1 summarizes the performance of the proposed LNA and compares it with other recently reported LNAs. The temperature compensation circuits proposed in references [12,14] effectively improve the LNA performance, but their designs are relatively complex and occupy a large area, while also significantly degrading other LNA parameters. The 60 GHz LNA in reference [12] experiences a 2.1 dB degradation in NF at high temperatures. The size of the temperature compensation circuit in reference [14] is 0.168 mm2, accounting for one-third of the total chip area. The LNA reported in [19] experienced a 5 dB gain degradation at temperatures ranging from −5 to 85 °C, indicating significant room for improvement. The proposed LNA exhibits good stability in key performance metrics, such as gain, NF, and bandwidth, when facing variations in environmental temperature, with a compact core area of only 0.09 mm2. Compared to LNAs without temperature compensation, such as [9,10,20], the proposed LNA shows superior gain and bandwidth at room temperature. Furthermore, it maintains a high gain of over 20 dB with a less than 1.5 dB variation across a temperature range of −55 to 85 °C. Due to system design specifications requiring a 3.3 V operating voltage, the proposed LNA exhibits relatively high-power consumption.

Table 1.

Performance summary and comparison with reported V-band LNAs and temperature compensation amplifier.

| Ref. | Process | Temp. (°C) | Peak Gain (dB) | ΔGain (dB) | Temp. Coefficient ΔGainmax/S21 RT/ΔT (dB/°C) [12] |

BW3dB

(GHz) |

BW5dB

(GHz) |

IP1dB

(dBm) |

NFmin

(dB) |

PDC (mW) |

Core Area (mm2) |

|---|---|---|---|---|---|---|---|---|---|---|---|

| [12] | 65 nm CMOS | −20 | 10.4 | <1.7 | 1.4 × 10−3 | >11 (56~67) * |

>13.5 (53.5~67) * |

\ | \ | \ | 0.72 & |

| 25 | 9.9 | >11.5 (55.5~67) |

>13.5 (53.5~67)* |

\ | 3.9 | 17.2 | |||||

| 100 | 8.8 | >11.5 (55.5~67) |

>13.5 (53.5~67) * |

\ | 6.0 | 23.4 | |||||

| [14] | 90 nm CMOS |

−45 | 23.6 | <1.2 | 0.29 × 10−3 | N/A | N/A | \ | \ | \ | 0.5 & |

| 25 | 23.8 | 4 (24.5~28.5) |

5 (24~29) * |

\ | \ | 25.2 | |||||

| 125 | 23 | N/A | N/A | \ | \ | \ | |||||

| [19] | 90 nm CMOS |

−5 | 22.5 | <5 | 2.6 × 10−3 | 10 (55~65) * |

>11 (54~65) * |

\ | \ | \ | 1.06 & |

| 25 | 21 | 8 (55~63) * |

>11 (54~65) * |

−20 * | 6.5 | 49 | |||||

| 85 | 17.5 | 11 (54~65) * |

>12.5 (52.5~65) * |

\ | \ | \ | |||||

| [9] | 45 nm RF-SOI |

25 | 20.4 | \ | \ | 13.6 (54.4~68) |

18 (53~71) |

−23.6 | 5 | 8.6 | 0.138 |

| [10] | 40 nm CMOS |

25 | 19.8 | \ | \ | 10 (55~65) |

13 (54~67) |

−29.5 | 6 | 18 | 0.22 & |

| [20] | 65 nm CMOS |

25 | 12.8 | \ | \ | 10 (55~65) |

>12 (54~66) |

\ | 3.6 | 8.8 | 0.33 |

| This work |

130

nm

BiCMOS |

− 55 | 25.5 | <1.5 | 0.4 × 10 − 3 |

>13

(52~65) |

>18.5

(46.5~65) |

− 20 | 3.0 | 22.3 | 0.09 |

| 25 | 25 |

>11

(54~65) |

>19.5

(45.5~65) |

− 17.5 | 3.5 | 27.6 | |||||

| 85 | 24.4 |

>10

(55~65) |

>18

(47~65) |

− 22.5 | 4.2 | 34.4 |

* Estimated values from papers; & DC pads are included.

4. Conclusions

An adaptive temperature compensation technology has been successfully implemented in a compact V-band wideband LNA fabricated using a 130 nm SiGe BiCMOS process. This innovation enables the LNA to exhibit excellent temperature robustness over a broad range from −55 °C to 85 °C. The V-band LNA demonstrates a gain variation of less than 1.5 dB, an NF variation of less than 1.2 dB, and an IP1dB variation of less than 5 dBm over measured frequencies from 40 GHz to 65 GHz. The measured DC power consumptions at −55 °C, 25 °C, and 85 °C are 22.3 mW, 27.6 mW, and 34.4 mW, respectively, with a supply voltage of 3.3 V. At room temperature, the LNA demonstrates a gain of 25 dB, an NF of 3.5 dB, and an IP1dB of −17.5 dBm. The LNA chip has a total silicon area of 0.37 mm2, including all test pads, with the core area being only 0.09 mm2.

Author Contributions

Conceptualization, Y.S. and J.L.; methodology, Y.S. and W.Z.; writing—original draft, Y.S.; data curation, W.Z. and J.-Y.D.; formal analysis, J.-Y.D.; writing—review and editing, Y.S., J.L., and Q.C.; supervision, J.L. and Q.C.; project administration, J.L. and Q.C. All authors have read and agreed to the published version of the manuscript.

Data Availability Statement

The data presented in this work are available within the article.

Conflicts of Interest

The authors declare no conflicts of interest.

Funding Statement

This research was supported in part by the National Key Research and Development Program of China under grant 2023YFB3811503, in part by the Zhejiang Provincial Natural Science Foundation of China under grant LQ23F040009, and in part by the State Key Laboratory of Millimeter Waves, Southeast University under grant K202316.

Footnotes

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

References

- 1.Frounchi M., Coen C., Cheon C.D., Lourenco N., Williams W., Cressler J.D. A V-Band SiGe image-reject receiver front-end for atmospheric remote sensing; Proceedings of the 2018 IEEE BiCMOS Compound Semiconductor Integrated Circuits and Technology Symposium; San Diego, CA, USA. 15–17 October 2018; pp. 223–226. [Google Scholar]

- 2.Hansen J. A novel stochastic millimeter-wave indoor radio channel model. IEEE J. Sel. Areas Commun. 2002;20:1240–1246. doi: 10.1109/JSAC.2002.801227. [DOI] [Google Scholar]

- 3.IEEE Standard for Information Technology—Local and Metropolitan Area Networks—Specific Requirements—Part 15.3: Amendment 2: Millimeter-Wave-Based Alternative Physical Layer Extension. IEEE Standards Association; Piscataway, NJ, USA: 2009. [Google Scholar]

- 4.Samoska L.A., Varonen M., Kangaslahti P., Fung A., Gawande R., Soria M., Lai R., Sarkozy S. V-band MMIC LNAs and mixers for observing the early universe; Proceedings of the 2016 41st International Conference on Infrared, Millimeter, and Terahertz waves (IRMMW-THz); Copenhagen, Denmark. 25–30 September 2016; pp. 1–2. [Google Scholar]

- 5.Polli G., Vittori M., Ciccognani W., Colangeli S., Costanzo F., Salvucci A., Limiti E. Ka-/V-band self-biased LNAs in 70 nm GaAs/InGaAs Technology; Proceedings of the 2018 14th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME); Prague, Czech Republic. 2–5 July 2018; pp. 197–200. [Google Scholar]

- 6.Vittori M., Polli G., Ciccognani W., Colangeli S., Salvucci A., Limiti E. Q-band self-biased MMIC LNAs using a 70 nm InGaAs/AlGaAs process; Proceedings of the 2017 IEEE Asia Pacific Microwave Conference (APMC); Kuala Lumpur, Malaysia. 13–16 November 2017; pp. 630–633. [Google Scholar]

- 7.Cressler J.D., Niu G. Silicon-Germanium Heterojunction Bipolar Transistors. Artech House; Norwood, MA, USA: 2003. [Google Scholar]

- 8.Xu X., Wagner J., Carta C., Ellinger F. A 60 GHz Broadband LNA With Joined Variable Gain Control and Switching in 22 nm FD-SOI. IEEE Access. 2024;12:111627–111637. doi: 10.1109/ACCESS.2024.3441853. [DOI] [Google Scholar]

- 9.Moody J., Lepkowski S., Forbes T.M. A Low Power V-Band LNA with Wide Supply Voltage Range Exploiting Complementary Current Reuse and Power Efficient Bias Point; Proceedings of the IEEE MTT-S International Microwave Symposium; San Diego, CA, USA. 11–16 June 2023; pp. 135–138. [Google Scholar]

- 10.Chang Y.-T., Lu H.-C. A V-Band Low-Power Digital Variable-Gain Low-Noise Amplifier Using Current-Reused Technique with Stable Matching and Maintained OP1dB. IEEE Trans. Microw. Theory Tech. 2019;67:4404–4417. doi: 10.1109/TMTT.2019.2938752. [DOI] [Google Scholar]

- 11.Frounchi M., Cressler J.D. A SiGe Millimeter-Wave Front-End for Remote Sensing and Imaging; Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC); Los Angeles, CA, USA. 4–6 August 2020; pp. 227–230. [Google Scholar]

- 12.Kawai S., Wang T., Mitomo T. A Temperature Variation Tolerant 60 GHz Low Noise Amplifier with Current Compensated Bias Circuit; Proceedings of the IEEE Asian Solid-State Circuits Conference (A-SSCC); Singapore. 11–13 November 2013; pp. 429–432. [Google Scholar]

- 13.Urain A., Del Río D., Torres R., Berenguer R. A G-Band SiGe BiCMOS LNA With an On-Chip and Compact Temperature Compensation Biasing Circuit; Proceedings of the IEEE/MTT-S International Microwave Symposium; San Diego, CA, USA. 11–16 June 2023; pp. 1132–1135. [Google Scholar]

- 14.Qi Q., Chen Z. A K -Band CMOS Amplifier with Temperature Compensation for Gain Variation Reduction. IEEE Microw. Wirel. Compon. Lett. 2018;28:150–152. doi: 10.1109/LMWC.2017.2786658. [DOI] [Google Scholar]

- 15.Dickson T.O., Yau K.H.K., Chalvatzis T., Mangan A.M., Laskin E., Beerkens R. The invariance of characteristic current densities in nanoscale MOSFETs and its impact on algorithmic design methodologies and design porting of Si(Ge) (Bi)CMOS high-speed building blocks. IEEE J. Solid-State Circuits. 2006;41:1830–1845. doi: 10.1109/JSSC.2006.875301. [DOI] [Google Scholar]

- 16.Khanpour M., Tang K.W., Garcia P., Voinigescu S.P. A wideband W-band receiver front-end in 65-nm CMOS. IEEE J. Solid-state Circuits. 2008;43:1717–1730. doi: 10.1109/JSSC.2008.926738. [DOI] [Google Scholar]

- 17.Tomkins A., Garcia P., Voinigescu S.P. A passive W-band imaging receiver in 65-nm bulk CMOS. IEEE J. Solid-state Circuits. 2010;45:1981–1991. doi: 10.1109/JSSC.2010.2058150. [DOI] [Google Scholar]

- 18.Wang R., Zhu W., Wang Y. An Adaptive Analog Temperature Compensated W-Band Front-End with ±0.0033 dB/°C Gain Variation Across −30 °C to 120 °C. IEEE Trans. Circuits Syst. II Express Briefs. 2024;71:542–546. doi: 10.1109/TCSII.2023.3313815. [DOI] [Google Scholar]

- 19.Shin S., Leung M., Hsiao S. A Temperature Variation Compensated 60-GHz Low-Noise Amplifier in 90-nm CMOS technology; Proceedings of the Asia-Pacific Microwave Conference; Melbourne, VIC, Australia. 5–8 December 2011; pp. 211–214. [Google Scholar]

- 20.Yaghoobi M., Yavari M., Kashani M.H., Ghafoorifard H., Mirabbasi S. A 55–64-GHz Low-Power Small-Area LNA in 65-nm CMOS With 3.8-dB Average NF and ∼12.8 dB Power Gain. IEEE Microw. Wirel. Compon. Lett. 2019;29:128–130. doi: 10.1109/LMWC.2018.2890484. [DOI] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Data Availability Statement

The data presented in this work are available within the article.