Abstract

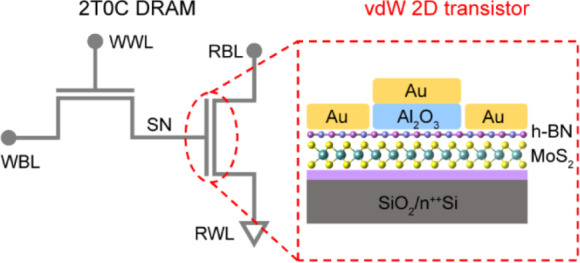

Dynamic random access memory (DRAM) has been a cornerstone of modern computing, but it faces challenges as technology scales down, particularly due to the mismatch between reduced storage capacitance and increasing OFF current. The capacitorless 2T0C DRAM architecture is recognized for its potential to offer superior area efficiency and reduced refresh rate requirements by eliminating the traditional capacitor. The exploration of two-dimensional (2D) materials further enhances scaling possibilities, though the absence of dangling bonds complicates the deposition of high-quality dielectrics. Here, we present a hexagonal boron nitride (h-BN)-assisted process for one-step transfer of van der Waals dielectrics and electrodes in 2D transistors with clean interfaces. The transferred aluminum oxide (Al2O3), formed by oxidizing aluminum (Al), exhibits exceptional flatness and uniformity, preserving the intrinsic properties of the 2D semiconductors without introducing doping effects. The MoS2 transistor exhibits an extremely low interface trap density of about 3 × 1011 cm–2 eV–1 and a leakage current density down to 10–7 A cm–2, which enables effective charge storage at the gate stack. This method allows for the simultaneous fabrication of two damage-free MoS2 transistors to form a capacitorless 2T0C DRAM cell, enhancing compatibility with 2D materials. The ultralow leakage current optimizes data retention and power efficiency. The fabricated 2T0C DRAM exhibits a rapid write speed of 20 ns, long data retention exceeding 1,000 s, and low energy consumption of approximately 0.2 fJ per write operation. Additionally, it demonstrates 3-bit storage capability and exceptional stability across numerous write/erase cycles.

Keywords: capacitorless DRAM, 2D transistor, one-step transfer approach, vdW dielectric, h-BN tunneling layer

Introduction

Dynamic random access memory (DRAM) has long been the main memory in modern computing systems, but it now faces significant challenges as technology scales down. The mismatch between reduced storage capacitance and increasing OFF current presents obstacles in maintaining performance and efficiency.1 Capacitorless 2T0C DRAM architecture is recognized for its potential in DRAM technology because of superior area efficiency and reduced refresh rate requirements.2−4 By eliminating the traditional capacitor, capacitorless DRAM allows for the creation of higher-density memory arrays, enabling more data to be stored within a smaller physical footprint. Additionally, the exploration of two-dimensional (2D) materials offers exciting possibilities for further scaling down and achieving monolithic three-dimensional integration.5−8 These advancements could revolutionize DRAM technology, providing a pathway to overcome current limitations and meet the growing demands of modern computing applications, particularly in data-intensive fields like artificial intelligence.

Unfortunately, the inherent absence of dangling bonds of 2D materials poses a great challenge for the deposition of high-quality dielectrics on the surface of 2D semiconductors.9−13 Researchers have explored various techniques to deposit high-quality dielectric layers on 2D materials, such as plasma pretreatment and inducing defect sites.14−17 However, these methods often introduce trap states and damage the 2D lattices, degrading their physical properties. Using buffer layers has been considered to preserve the intrinsic properties of 2D materials, but these layers often lack stability and have low dielectric constants, affecting gate controllability.18−22 Aluminum oxide (Al2O3) can be easily formed by oxidation of aluminum (Al) with a low intrinsic defect density and consequently fewer defects at the interface between oxide and semiconductor, which minimizes the number of sites where charge carriers can be trapped. Additionally, with a wide bandgap of approximately 7 eV, Al2O3 offers excellent insulating properties and low leakage currents, which are essential for memory devices as they extend the retention of memory cells by preventing unintended charge loss.

In this work, we investigate a hexagonal boron nitride (h-BN)-assisted van der Waals (vdW) integration strategy for fabricating damage-free 2D transistors with pristine interfaces. The Al deposited on the monolayer h-BN is completely oxidized to Al2O3 through an annealing process and then stacked onto the 2D semiconducting channel via a one-step transfer process. This method separates high-energy deposition process from 2D materials, resulting in damage-free transistors with clean metal/2D and dielectric/2D interfaces. The resulting MoS2 transistors demonstrate intrinsic properties without doping effects, including a high ON/OFF ratio up to 108, a low leakage current of ∼10–7 A cm–2, a small subthreshold swing (SS) of 84 mV dec–1, and extremely low interface trap density of about 3 × 1011 cm–2 eV–1. The monolayer h-BN tunneling layer also reduces the Schottky barrier height (SBH) to 98 meV. We successfully fabricated a 2T0C DRAM cell with two top-gate MoS2 transistors. The ultralow leakage current of the MoS2 transistor greatly enhances data retention, achieving a rapid write operation of 20 ns and data retention exceeding 1,000 s. This result demonstrates the potential of MoS2-based transistors in advancing DRAM technology.

Results and Discussion

One-Step Transfer of van der Waals Dielectrics and Electrodes Assisted by Monolayer h-BN

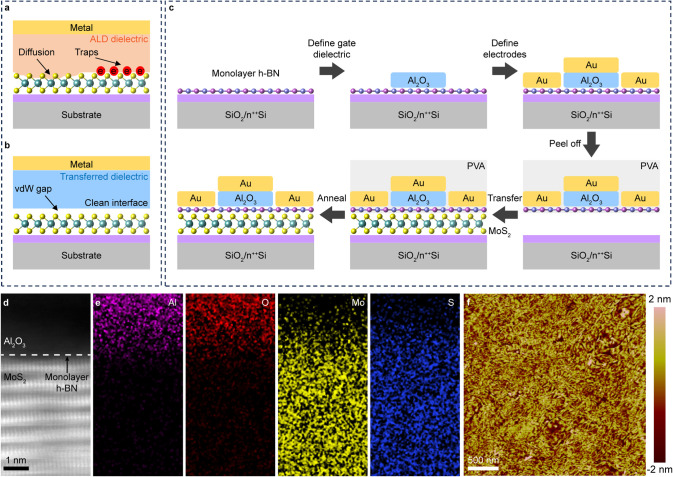

A crucial challenge in fabricating 2D top-gate transistors is achieving a high-quality, reliable gate dielectric layer that can effectively control the electronic properties of the 2D material channel.23−26 Direct deposition of dielectric layers on the surface of 2D materials using atomic layer deposition (ALD) often results in the generation of interface traps and diffusion (Figure 1a).18,27,28 These defects can degrade the electrical performance of the device, leading to increased SS and hysteresis. Researchers have established vdW contact at the metal/semiconductor interfaces by transfer techniques, which results in a clean interface without chemical disorder and Fermi-level pining.29−32 We can also extend this strategy to transfer dielectric onto 2D semiconductors and create a clean dielectric/semiconductor interface (Figure 1b). Here, we adopted a monolayer h-BN as an interlayer for transferring dielectrics. The presence of h-BN weakens the strong adhesion between the dielectric/electrodes and SiO2 substrate, facilitating the ease of the transfer process. In addition, the insulating characteristics of h-BN suppresses current leakage.

Figure 1.

h-BN-assisted one-step dielectric/electrodes stack transfer process for damage-free top-gate transistors. (a) Cross-sectional view of top-gate MoS2 transistors with ALD dielectric. (b) Cross-sectional view of top-gate MoS2 transistors with transferred dielectric. (c) Schematic of the Al2O3 dielectric and Au electrodes transfer process for vdW integrated top-gate transistors. (d) High-resolution cross-section TEM image of the vdW integrated Al2O3/h-BN/MoS2 interfaces. (e) EDS mapping showing the elemental distribution of Al2O3/MoS2. (f) AFM image of the backside of peeled-off Au/Al2O3. The root-mean-square roughness is 0.8 nm.

Figure 1c schematically illustrates the transfer process of the dielectric/electrode stack. We selected Al2O3 as the gate dielectric due to its high dielectric constant, high breakdown voltage, and thermal stability.33 First, an Al film was patterned onto the monolayer h-BN using e-beam evaporation followed by a liftoff process. Then, the Al film was annealed in the air for oxidation and stress relaxation. The absence of a characteristic peak of Al at 72 eV in the X-ray photoelectron spectroscopy (XPS) spectrum is indicative of the complete oxidation of Al (Figure S1). Second, the source, drain, and gate electrodes were defined by standard photolithography and e-beam evaporation process at the same time. Thus, the complete device structure (dielectric and electrodes) was obtained on the SiO2 sacrificial substrate (Figure S2a). Third, the dielectric/electrode stack was peeled off from the substrate with the h-BN interlayer, because of the weak interaction between h-BN and substrate (Figure S2b). Next, the device stack was aligned and physically laminated on the exfoliated MoS2 flake by using a transfer platform. Finally, the poly(vinyl alcohol) (PVA) film was removed by deionization water. The fabricated device was annealed at 200 °C in vacuum to improve the contacts (Figure S2c,d).

This vdW integration method can create an atomically flat and clean dielectric/semiconductor interface, which can be confirmed by the cross-sectional TEM image (Figure 1d). The atomically flat and clean interface is crucial for damage-free transistors with minimum interface trap states. The energy dispersive spectrometer (EDS) mapping shows the elemental distributions of Al, O, Mo, and S in the corresponding area (Figure 1e). This elemental mapping confirms that the Al is uniformly oxidized and does not diffuse into MoS2. After peeling off the device stack from the sacrificial SiO2 substrate, we conducted an AFM examination of the backside of the dielectric region of the device stack. This analysis revealed an exceptionally flat surface characterized by a root-mean-square surface roughness of 0.8 nm (Figure 1f). This ultraflatness is attributed to the presence of the monolayer h-BN and the inherently smooth surface of the sacrificial substrate. The exceptional flatness of this surface suggests its potential to achieve intimate contact with MoS2, thereby enhancing the device performance.

Electrical Characteristics of Damage-Free MoS2 Transistors

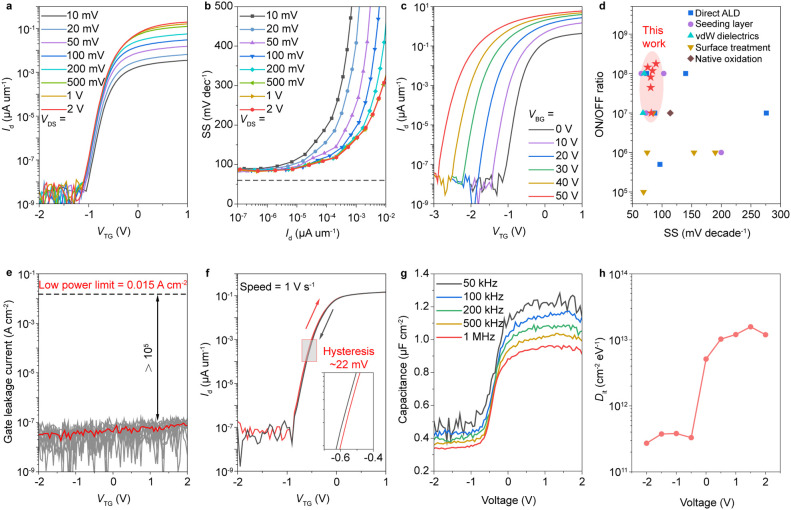

By employing this transfer methodology, the Al2O3 dielectric is physically laminated on the exfoliated MoS2 with a weak vdW force, thereby preserving the intrinsic properties of MoS2. The top-gate MoS2 transistor, featuring a transferred dielectric/electrodes stack, exhibits exceptional gate tunability. The transferred Al2O3-gated MoS2 transistor shows a high ON/OFF ratio of 107 at a drain-source voltage of 1 V (Figure 2a). The OFF current is less than 0.1 pA, which indicates the high quality of thermally oxidized Al2O3. The device exhibits steep switching in the subthreshold region. Generally, SS quantifies the efficiency with which a transistor transitions from the OFF state to the ON state in response to the gate voltage and is given by the following equation:13

| 1 |

where kB is the Boltzmann’s constant, T is the absolute temperature, q is the elementary charge, Cit is the capacitance of interface traps, Cox is the gate oxide capacitance, and Cdep is the depletion layer capacitance and is considered as zero in the subthreshold region due to complete depletion of the atomically thin channel. For an ideal 2D FET, the interface-trap density is negligible. This allows SS to reach its lowest limit of ∼60 mV dec–1 at room temperature, which represents the most efficient switching behavior for the transistor.

Figure 2.

Electrical characteristics of damage-free top-gate MoS2 transistor. (a) Transfer curves of the vdW integrated damage-free top-gate transistor with different drain voltages. (b) Extracted SS at different channel currents of the top-gate MoS2 transistor. The black dashed line corresponds to the lower limit of 60 mV dec–1 at room temperature. (c) Transfer curves of the vdW integrated damage-free top-gate transistor under various back-gate voltages. (d) Comparison of the ON/OFF ratio and SS of our top-gate MoS2 transistor and other high-κ dielectric MoS2 transistor.14−17,19−22,25,28,35−39 The red stars represent measurements taken at different back gate voltages (0, 10, 20, 30, 40, and 50 V). (e) Gate leakage current density of the MoS2 transistor. The red line represents the average leakage current density of ten devices (gray lines). The black dashed line represents the low-power limit of 0.015 A cm–2. (f) Dual sweep transfer curve of the damage-free top-gate transistor at a speed of 1 V s–1. Back gate voltage and drain voltage are 0 and 1 V, respectively. The insert is a magnified view of the transfer curve in the gray box, indicating a hysteresis of ∼22 mV. (g) Capacitance–voltage (C–V) of the MoS2/h-BN/Al2O3 structure on a quartz substrate. (h) Extracted trap density as a function of top-gate voltage.

However, most top-gate 2D FETs have high interface trap densities caused by the dielectric deposition process, resulting in high SS values. Our device demonstrates a small SS of 84 mV dec–1 (Figure 2b), indicative of a low interface defect density. Without any back gate voltage, the device exhibits an ON/OFF ratio of 107 and an ON-current of 0.4 μA μm–1 (Figure S3a). The relatively low ON-current can be attributed to the ungated regions that exist between the gate electrode and the contact electrodes. Increasing the back gate voltage enhances both the ON-current and the ON/OFF ratio, thereby confirming the dual-gate controllability of the device (Figures 2c and S3b). Figure 2d provides a comparative analysis of the ON/OFF ratio and SS of our device with recently reported high-κ dielectric-gated MoS2 transistor fabricated using various methods, such as ALD and seeding layer. The small SS value observed in our transferred Al2O3-gated MoS2 transistor can be attributed to the superior interface quality achieved through this transfer method, which notably avoids the introduction of impurities at the interface.

Leakage current is a crucial parameter in evaluating gate dielectrics within field-effect transistors. To assess the insulating properties of the transferred Al2O3, we measured the gate leakage current of our top-gate MoS2 transistor (Figure 2e). The observed ultralow gate leakage current density of <10–7 A cm–2 is well below the low-power limit for complementary metal-oxide-semiconductor devices, significantly reducing the static power consumption of our devices. Figure 2f shows the dual sweep transfer curve of the fabricated top-gate MoS2 transistor, indicating a small hysteresis of 22 mV. The small hysteresis can also be ascribed to the superior interface quality. Maintaining high-quality interfaces is of paramount importance for achieving high performance in 2D FETs. To quantitatively analyze the interface trap density Dit, high-low frequency capacitance–voltage (C–V) measurement was performed (Figure 2g). Dit can be calculated by the following equations:

| 2 |

| 3 |

where Cit is the capacitance of interface traps, and CLF and CHF are the capacitances measured at low and high frequencies, respectively. The extracted Dit shows an interface trap density of about 3 × 1011 cm–2 eV-1 in the accumulation region (Figure 2h). The relatively low interface trap density, compared to ALD dielectrics (which are usually greater than 2 × 1012 cm–2 eV-1),34−36 corroborates the electronically pristine interfaces achieved through the damage-free vdW fabrication approach.

Reducing Contact Resistance with Monolayer h-BN as a Tunneling Layer

When a 2D semiconductor contacts a three-dimensional (3D) metal, the Fermi level at the interface is typically pinned at a specific energy level within the bandgap of the 2D semiconductor. This pinning effect remains relatively invariant with respect to the work function of the contact metal, resulting in a high SBH and elevated contact resistance. To mitigate the effects of Fermi level pinning at the interface between a 2D semiconductor and a 3D metal, researchers demonstrated an approach involving the insertion of an ultrathin tunneling layer between them.40 Therefore, one reason for selecting monolayer h-BN to facilitate the transfer of the device stack is its capability to function as a tunneling layer, which reduces the SBH and consequently lowers the contact resistance. To analyze the SBHs of Au and h-BN/Au contacts, back-gated MoS2 transistors with/without the h-BN tunneling layer were fabricated on the SiO2/n++Si substrate. Transfer curves of the MoS2 transistors at different temperatures are shown in Figure S4. According to the thermionic emission theory, the current of the transistor (ID) can be written as

| 4 |

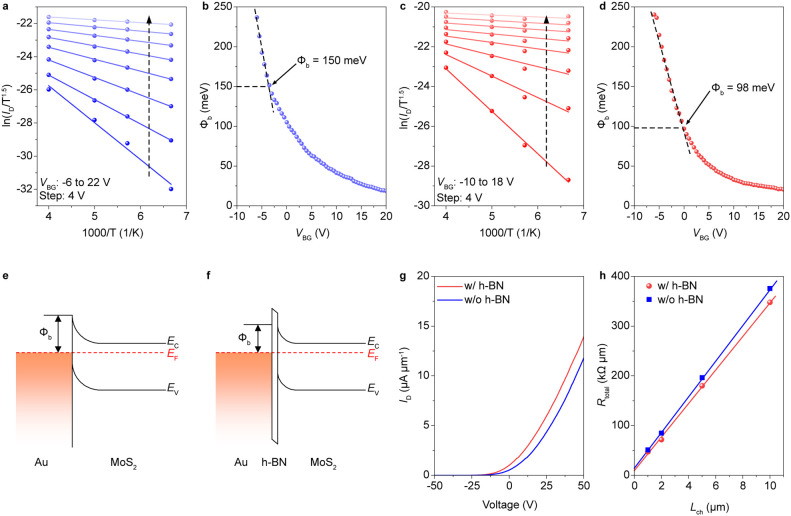

where A*2Dis the 2D equivalent Richardson constant, T is the absolute temperature, ΦB is effective barrier height, kB is the Boltzmann constant, q is the electronic charge and VDS is the drain to source voltage. The thermionic emission current dominates the current in the transistor when the back gate voltage (VBG) is lower than the flat-band voltage (VFB). However, when VGS exceeds VFB, a significant thermally assisted tunneling current emerges, leading to nonlinear behavior in ΦB-VGS plot. At VGS = VFB, SBH can be determined by observing the transition point where the relationship between barrier height and VGS changes from linear to nonlinear. To obtain the barrier heights, the values of ln(ID/T1.5) are plotted at fixed VDS of 1 V with different gate voltages (Figure 3a and 3c). The slopes extracted from the Arrhenius plot exhibit a linear relationship with VDS, as shown in Figure S4c,d. The y-intercept of Figure S4c,d, denoted by S0, represents the extrapolated slope value at VDS = 0 V. The energy barrier height is then determined by Φb = −1000S0kB/q. The resulting energy barrier heights at various gate voltages are plotted in Figure 3b,d. For comparison, the SBHs are extracted to be 150 meV without the h-BN tunneling layer and 98 meV with a monolayer h-BN tunneling layer. These SBHs may be underestimated due to the long channel length.42 However, through the controlled device structure with and without h-BN layer, the reduced value for the monolayer h-BN/Au contact confirms that h-BN tunneling layer can effectively decrease the SBH.

Figure 3.

Monolayer h-BN serves as a tunneling layer to reduce the SBH and contact resistance. (a) The Arrhenius plot of back-gated MoS2 transistor with transfer Au electrodes at VDS = 1 V. (b) The extracted energy barrier height at different back gate voltages. (c) The Arrhenius plots of back-gated MoS2 transistor with transfer h-BN/Au electrodes at VDS = 1 V. (d) The extracted energy barrier height at different back gate voltages. (e) Band diagram for Au contact, MIGS results in a high SBH. (f) Band diagram for h-BN/Au contact, the Schottky barrier is reduced by minimizing the penetration of MIGS. (g) Transfer curves of MoS2 transistors with Au or h-BN/Au contacts. (h) Comparison of the contact resistances of the MoS2 transistors with/without the h-BN tunneling layer.

As the semiconductor contacts the metal, the metal’s wave function penetrates the semiconductor. This penetration induces rehybridization of the semiconductor’s wave function, resulting in the formation of gap states within the semiconductor’s bandgap, as illustrated in Figure 3e.41 Introducing a monolayer h-BN tunneling layer reduces metal-induced gap states (MIGS) without altering the MoS2 bands, while effectively lowering the SBH by modifying the band alignment at the interface (Figure 3f). For the metal/insulator/semiconductor contact, the contact resistance is determined by the Schottky barrier and tunneling resistance with the latter being relatively small due to the atomic thickness (∼0.42 nm) of the monolayer h-BN.43 The most intuitive manifestation of the reduction in contact resistance is the increase in ON-current. Figure 3g shows the transfer curves of back-gated MoS2 transistors on SiO2 substrates. With the monolayer h-BN, the ON-current of the MoS2 transistor shows an increase from 11 μA μm–1 to 15 μA μm–1. Transfer curves of the MoS2 transistors with varying channel lengths are presented in Figure S5. The contact resistance is further extracted by the transmission line method and shown in Figure 3h. The device with the monolayer h-BN contact exhibits a smaller contact resistance of 4.7 kΩ μm compared to 7.1 kΩ μm for the direct Au contact.

High-Performance 2T0C DRAM Based on Damaged-Free Top-Gate MoS2 Transistors

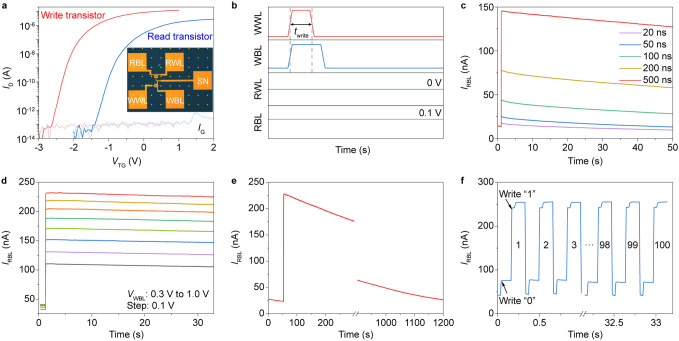

The h-BN-assisted vdW dielectric/electrode transfer method enables the fabrication of transistors with ultralow leakage current, which is crucial for extending DRAM retention time. Utilizing this one-step transfer method, we simultaneously fabricated two damage-free MoS2 transistors to construct a 2T0C DRAM cell. Compared to conventional 2T0C DRAM fabrication processes, which require steps such as photolithography, metallization, and etching, this vdW integration method shows greater compatibility with 2D materials (Figure S6).44 The insert of Figure 4a presents the optical image of the 2T0C DRAM cell, which comprises a write transistor and a read transistor. In this configuration, the drain of the write transistor is connected to the gate of the read transistor. The gate capacitance of the read transistor is used for charge storage. As illustrated in the circuit diagram in Figure S7, the write and read operations of the 2T0C DRAM cell are separated. The state of the DRAM can be read by monitoring the channel current of the read transistor, thereby ensuring that the stored charge in the gate capacitor remains undisturbed. Figure 4a shows the transfer curves of the two transistors within the 2T0C DRAM cell. The corresponding output curves of the two devices are shown in Figure S8. Both transistors exhibit exceptionally low leakage currents, which is advantageous for prolonging data retention time. It is noteworthy that the MoS2 channel of the write transistor is thicker (∼6 nm) than that of the read transistor, to achieve a higher ON state current and thereby enhance the write speed. Conversely, the MoS2 channel of the read transistor is designed to be thinner (∼3.5 nm), ensuring operation within the subthreshold region at a gate voltage of 0 V, which optimizes the sense margin. It is important to note that an excessively positive or negative threshold voltage of the read transistor will reduce the sense margin.

Figure 4.

Electrical performances of the 2T0C DRAM. (a) Transfer curves of the write and read MoS2 transistors. The inset shows the optical image of the 2T0C DRAM cell with two MoS2 transistors. The channel width/length of the write and read transistors are 14 μm/10 μm and 7 μm/10 μm, respectively. (b) Timing diagram of the write and read operations for 2T0C DRAM. (c) IRBL as a function of read time following the writing of data “1”, with the write pulse width varying from 20 to 500 ns. The amplitude of the write pulse is fixed to be 1 V. (d) Data retention of 3-bit DRAM with VWBL ranging from 0.3 to 1.0 V. (e) IRBL evolution of the fabricated 2T0C DRAM, following the writing of data “1”, demonstrates a retention time exceeding 1,000 s. (f) 100 times write and erase operations of data “1”. Each conducted with a pulse width of 60 ms and pulse amplitude of 1 V.

Figure 4b illustrates the timing diagrams that delineate the write and read operations for the 2T0C DRAM cell. To continuously monitor the stored charge in the storage node, the read bit line (RBL) and read word line (RWL) were set to 0.1 and 0 V, respectively. During a write “1” operation, the write bit line (WBL) was set to a longer pulse duration than the write word line (WWL) to prevent charge leakage. First, we performed a write speed test on the 2T0C DRAM cell. Following a 20 ns write pulse, the IRBL response for data “0” and data “1” exhibits a distinguishable difference, as shown in Figure 4c. The calculated energy consumed during a write operation is approximately 0.2 fJ, indicating that our device can operate with extremely low power consumption. When we extend the write duration time from 20 to 500 ns, the current level of data “1” also increases. This rapid write speed is intrinsically linked to the high ON-current of the write transistor. However, the assessment of nanosecond-level write speed is influenced by RC delay in the interconnects, which may result in a reduction in writing efficiency.

A longer write pulse duration of 10 ms to the DRAM results in a high current level of 230 nA. This large state difference also facilitates multilevel storage capability within a single DRAM cell. By fixing the VWWL at 1 V with a write pulse duration of 10 ms and varying the VWBL from 0.3 to 1 V in increments of 0.1 V, eight distinct memory states are achieved, as illustrated in Figure 4d. The output current IRBL demonstrates eight distinct levels, which remain stable throughout the entire measurement period of 30 s. To evaluate the data retention time of the 2T0C DRAM, IRBL over time is recorded after write “1”, as shown in Figure 4e. The sense margin between logic “1” and “0” reaches 200 nA after write operation, attributed to the suitable VTH of the read transistor. Following the write “1” operation, the IRBL gradually decreases due to the extremely small leakage current of the top-gate MoS2 transistors. Nevertheless, even after 1,000 s, data “1” and data “0” remain distinguishable. Based on the observed long data retention of this 2T0C DRAM, the leakage current is calculated to be less than 1.34 × 10–15 A. As a storage device, DRAM requires frequent write and erase operations. Therefore, we conducted 100 write and erase cycles, as depicted in Figure 4f. The current levels corresponding to data “1” and data “0” exhibited negligible changes, thereby demonstrating the device’s exceptional stability.

Conclusion

In conclusion, the h-BN-assisted vdW integration strategy presents a great advancement in the fabrication of damage-free top-gate 2D transistors with pristine interfaces. By employing a monolayer h-BN as a buffer layer, this method effectively separates the high-energy deposition processes from the 2D materials, thereby preserving their intrinsic properties. The resulting MoS2 top-gate transistors exhibit remarkable electrical performance, including a high ON/OFF ratio up to 108, small SS of 84 mV dec–1, low leakage current of approximately 10–7 A cm–2, and very low interface trap density of about 3 × 1011 cm–2 eV–1. Additionally, the reduced SBH and lower contact resistance achieved through this approach further enhance device performance. Furthermore, the successful demonstration of a 2T0C DRAM cell with two top-gate MoS2 transistors underscores the potential of this technology in improving DRAM performance, particularly in terms of data retention and write speed. These findings highlight the promise of vdW integration techniques in advancing the capabilities of next-generation electronic devices, particularly those utilizing 2D materials.

Experimental Section

The h-BN (Sixcarbon Technology Shenzhen), grown via chemical vapor deposition (CVD) on copper foil, was transferred onto a sacrificial SiO2/Si substrate using a wet transfer method. Subsequently, the sample was annealed under a mixed flow of H2/N2 at 350 °C for 3 h to release strain and remove any PMMA residue.45 The bulk MoS2 samples were purchased from HQ Graphene, and few-layer MoS2 flakes were mechanically exfoliated onto SiO2/n++Si substrates.

Photolithography was utilized to define the gate dielectric region, followed by the deposition of an approximately 20 nm Al layer using an electron-beam evaporator at a pressure of 10–6 Torr and a deposition rate of 0.3 Å/s. This was followed by a liftoff process. The Al was then annealed in air at 400 °C for 3 h to form a uniform Al2O3 dielectric layer. Subsequently, 40 nm Au source, gate, and drain electrodes were patterned using photolithography and deposited via an electron-beam evaporator.

To fabricate the device, a PVA film was employed to mechanically peel off the dielectric/electrode stack. The PVA film, along with the dielectric/electrode stack, was affixed to a polydimethylsiloxane (PDMS) stamp, which was attached to a glass slide. Using a 2D materials transfer platform, the dielectric/electrode stack and the MoS2 flake were precisely aligned. The dielectric/electrode stack, along with the PVA, were then adhered to the MoS2 flake. The devices were heated to 68 °C for 3 min to facilitate the release of the PDMS. The PVA film was subsequently dissolved using deionized water. Finally, the devices underwent annealing in a vacuum at 200 °C for 2 h to enhance the contact quality. The same method was used to fabricate Au/MoS2/h-BN/Al2O3/Au device on quartz substrate for the C–V test.

The cross-sectional sample of the MoS2/h-BN/Al2O3 stack was prepared using a Helios 5 CX DualBeam focused ion beam. STEM characterization and EDS analyses were carried out on a ThermoFisher Scientific Spectra 300 TEM with an accelerating voltage of 300 kV. To determine the roughness of the surface at the interface between Al2O3 and MoS2, the Al2O3 was peeled off using PVA and subsequently placed on top of PDMS. The surface was then scanned using a Bruker MultiMode 8 scanning probe microscope.

Electrical characterization was performed in a Lakeshore TTPX probe station using a Keithley 4200A SCS parameter analyzer at atmospheric conditions. The 2T0C DRAM measurements were conducted with a Keysight B1500A semiconductor characterization system, while the pulse voltage was applied using the SPGU module.

Acknowledgments

This work is supported by MOST National Key Technologies R&D Programme (2022YFA1203804), National Natural Science Foundation of China (62425405), Research Grant Council of Hong Kong (15301322 and CRS_PolyU502/22), and the Hong Kong Polytechnic University (WZ4X and CD9J).

Supporting Information Available

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsnano.4c15750.

XPS of the Al2O3 film; optical images of the device stacks during the transfer process; output curves of the damage-free MoS2 transistor; transfer curves of the MoS2 transistors under different temperatures; transfer curves of the MoS2 transistors with different channel lengths; DRAM fabrication process; 2T0C DRAM circuit diagram; output curves of the two damage-free MoS2 transistors in one 2T0C DRAM cell (PDF)

Author Contributions

Y.C. conceived the concept and supervised the project. J.G. and Y.C. designed the fabrication process. J.G., C.W., and J.Y. fabricated the devices. J.G. and T.W. contributed to the device measurement and data analysis. Z.L. performed the Atomic Force Microscope characterization. X.C. and Y.Z. performed the STEM characterization and EDS analysis. J.G and Y.C. wrote the paper. All the authors discussed the results and reviewed the paper.

The authors declare no competing financial interest.

Supplementary Material

References

- Duan X.; Huang K.; Feng J.; Niu J.; Qin H.; Yin S.; Jiao G.; Leonelli D.; Zhao X.; Jing W.; et al. , Novel Vertical Channel-All-Around(CAA) IGZO FETs for 2T0C DRAM with High Density beyond 4F2 by Monolithic Stacking. In 2021 IEEE International Electron Devices Meeting (IEDM). IEEE, 2021, pp 10.5.1–10.5.4. [Google Scholar]

- Hu Q.; Gu C.; Li Q.; Zhu S.; Liu S.; Li Y.; Zhang L.; Huang R.; Wu Y. True Nonvolatile High-Speed DRAM Cells Using Tailored Ultrathin IGZO. Adv. Mater. 2023, 35 (20), 2210554. 10.1002/adma.202210554. [DOI] [PubMed] [Google Scholar]

- Hu Q.; Li Q.; Zhu S.; Gu C.; Liu S.; Huang R.; Wu Y.; Optimized IGZO FETs for Capacitorless DRAM with Retention of 10 ks at RT and 7 ks at 85 °C at Zero Vhold with Sub-10 ns Speed and 3-bit Operation. In 2022 International Electron Devices Meeting (IEDM). IEEE, 2022, pp 26.6.1–26.6.4.. [Google Scholar]

- Lu W.; Zhu Z.; Chen K.; Liu M.; Kang B. M.; Duan X.; Niu J.; Liao F.; Dan W.; Wu X. S.; et al. , First Demonstration of Dual-Gate IGZO 2T0C DRAM with Novel Read Operation, One Bit Line in Single Cell, ION = 1500 μA/μm@VDS = 1V and Retention Time > 300s. In 2022 International Electron Devices Meeting (IEDM), IEEE, 2022, pp 26.4.1–26.4.4. [Google Scholar]

- Das S.; Sebastian A.; Pop E.; McClellan C. J.; Franklin A. D.; Grasser T.; Knobloch T.; Illarionov Y.; Penumatcha A. V.; Appenzeller J.; Chen Z.; Zhu W.; Asselberghs I.; Li L.-J.; Avci U. E.; Bhat N.; Anthopoulos T. D.; Singh R. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 2021, 4 (11), 786–799. 10.1038/s41928-021-00670-1. [DOI] [Google Scholar]

- Fiori G.; Bonaccorso F.; Iannaccone G.; Palacios T.; Neumaier D.; Seabaugh A.; Banerjee S. K.; Colombo L. Electronics based on two-dimensional materials. Nat. Nanotechnol. 2014, 9 (10), 768–779. 10.1038/nnano.2014.207. [DOI] [PubMed] [Google Scholar]

- Jayachandran D.; Pendurthi R.; Sadaf M. U. K.; Sakib N. U.; Pannone A.; Chen C.; Han Y.; Trainor N.; Kumari S.; Mc Knight T. V.; Redwing J. M.; Yang Y.; Das S. Three-dimensional integration of two-dimensional field-effect transistors. Nature 2024, 625 (7994), 276–281. 10.1038/s41586-023-06860-5. [DOI] [PubMed] [Google Scholar]

- Pendurthi R.; Sakib N. U.; Sadaf M. U. K.; Zhang Z.; Sun Y.; Chen C.; Jayachandran D.; Oberoi A.; Ghosh S.; Kumari S.; Stepanoff S. P.; Somvanshi D.; Yang Y.; Redwing J. M.; Wolfe D. E.; Das S. Monolithic three-dimensional integration of complementary two-dimensional field-effect transistors. Nat. Nanotechnol. 2024, 19 (7), 970–977. 10.1038/s41565-024-01705-2. [DOI] [PubMed] [Google Scholar]

- Kim H. G.; Lee H.-B.-R. Atomic Layer Deposition on 2D Materials. Chem. Mater. 2017, 29 (9), 3809–3826. 10.1021/acs.chemmater.6b05103. [DOI] [Google Scholar]

- Lu Z.; Chen Y.; Dang W.; Kong L.; Tao Q.; Ma L.; Lu D.; Liu L.; Li W.; Li Z.; et al. Wafer-scale high-κ dielectrics for two-dimensional circuits via van der Waals integration. Nat. Commun. 2023, 14 (1), 2340. 10.1038/s41467-023-37887-x. [DOI] [PMC free article] [PubMed] [Google Scholar]

- Xu Y.; Liu T.; Liu K.; Zhao Y.; Liu L.; Li P.; Nie A.; Liu L.; Yu J.; Feng X.; Zhuge F.; Li H.; Wang X.; Zhai T. Scalable integration of hybrid high-κ dielectric materials on two-dimensional semiconductors. Nat. Mater. 2023, 22 (9), 1078–1084. 10.1038/s41563-023-01626-w. [DOI] [PubMed] [Google Scholar]

- Meng K.; Li Z.; Chen P.; Ma X.; Huang J.; Li J.; Qin F.; Qiu C.; Zhang Y.; Zhang D.; Deng Y.; Yang Y.; Gu G.; Hwang H. Y.; Xue Q.-K.; Cui Y.; Yuan H. Superionic fluoride gate dielectrics with low diffusion barrier for two-dimensional electronics. Nat. Nanotechnol. 2024, 19 (7), 932–940. 10.1038/s41565-024-01675-5. [DOI] [PubMed] [Google Scholar]

- Wang L.; Wang P.; Huang J.; Peng B.; Jia C.; Qian Q.; Zhou J.; Xu D.; Huang Y.; Duan X. A general one-step plug-and-probe approach to top-gated transistors for rapidly probing delicate electronic materials. Nat. Nanotechnol. 2022, 17 (11), 1206–1213. 10.1038/s41565-022-01221-1. [DOI] [PubMed] [Google Scholar]

- Wang X.; Zhang T.-B.; Yang W.; Zhu H.; Chen L.; Sun Q.-Q.; Zhang D. W. Improved integration of ultra-thin high-k dielectrics in few-layer MoS2 FET by remote forming gas plasma pretreatment. Appl. Phys. Lett. 2017, 110 (5), 053110. 10.1063/1.4975627. [DOI] [Google Scholar]

- Young C. D.; Zhao P.; Bolshakov-Barrett P.; Azcatl A.; Hurley P. K.; Gomeniuk Y. Y.; Schmidt M.; Hinkle C. L.; Wallace R. M. (Invited) Evaluation of Few-Layer MoS2 Transistors with a Top Gate and HfO2 Dielectric. ECS Trans. 2016, 75 (5), 153. 10.1149/07505.0153ecst. [DOI] [Google Scholar]

- Bolshakov P.; Zhao P.; Azcatl A.; Hurley P. K.; Wallace R. M.; Young C. D. Improvement in top-gate MoS2 transistor performance due to high quality backside Al2O3 layer. Appl. Phys. Lett. 2017, 111 (3), 032110. 10.1063/1.4995242. [DOI] [Google Scholar]

- Wang J.; Li S.; Zou X.; Ho J.; Liao L.; Xiao X.; Jiang C.; Hu W.; Wang J.; Li J. Integration of High-k Oxide on MoS2 by Using Ozone Pretreatment for High-Performance MoS2 Top-Gated Transistor with Thickness-Dependent Carrier Scattering Investigation. Small 2015, 11 (44), 5932–5938. 10.1002/smll.201501260. [DOI] [PubMed] [Google Scholar]

- Sheng Y.; Chen X.; Liao F.; Wang Y.; Ma J.; Deng J.; Guo Z.; Bu S.; Shen H.; Bai F.; et al. Gate Stack Engineering in MoS2 Field-Effect Transistor for Reduced Channel Doping and Hysteresis Effect. Adv. Electron. Mater. 2021, 7 (7), 2000395. 10.1002/aelm.202000395. [DOI] [Google Scholar]

- Bolshakov P.; Khosravi A.; Zhao P.; Hurley P. K.; Hinkle C. L.; Wallace R. M.; Young C. D. Dual-gate MoS2 transistors with sub-10 nm top-gate high-k dielectrics. Appl. Phys. Lett. 2018, 112 (25), 253502. 10.1063/1.5027102. [DOI] [Google Scholar]

- Lin G.; Zhao M.-Q.; Jia M.; Zhang J.; Cui P.; Wei L.; Zhao H.; Johnson A. T. C.; Gundlach L.; Zeng Y. Performance enhancement of monolayer MoS2 transistors by atomic layer deposition of high-k dielectric assisted by Al2O3 seed layer. J. Phys. D: Appl. Phys. 2020, 53 (10), 105103. 10.1088/1361-6463/ab605b. [DOI] [Google Scholar]

- Li W.; Zhou J.; Cai S.; Yu Z.; Zhang J.; Fang N.; Li T.; Wu Y.; Chen T.; Xie X.; Ma H.; Yan K.; Dai N.; Wu X.; Zhao H.; Wang Z.; He D.; Pan L.; Shi Y.; Wang P. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2019, 2 (12), 563–571. 10.1038/s41928-019-0334-y. [DOI] [Google Scholar]

- Liu K.; Jin B.; Han W.; Chen X.; Gong P.; Huang L.; Zhao Y.; Li L.; Yang S.; Hu X.; Duan J.; Liu L.; Wang F.; Zhuge F.; Zhai T. A wafer-scale van der Waals dielectric made from an inorganic molecular crystal film. Nat. Electron. 2021, 4 (12), 906–913. 10.1038/s41928-021-00683-w. [DOI] [Google Scholar]

- Yang S.; Liu K.; Xu Y.; Liu L.; Li H.; Zhai T. Gate Dielectrics Integration for 2D Electronics: Challenges, Advances, and Outlook. Adv. Mater. 2023, 35 (18), 2207901. 10.1002/adma.202207901. [DOI] [PubMed] [Google Scholar]

- Zou X.; Huang C.-W.; Wang L.; Yin L.-J.; Li W.; Wang J.; Wu B.; Liu Y.; Yao Q.; Jiang C.; Wu W.-W.; He L.; Chen S.; Ho J. C.; Liao L. Dielectric Engineering of a Boron Nitride/Hafnium Oxide Heterostructure for High-Performance 2D Field Effect Transistors. Adv. Mater. 2016, 28 (10), 2062–2069. 10.1002/adma.201505205. [DOI] [PubMed] [Google Scholar]

- Zou X.; Wang J.; Chiu C.-H.; Wu Y.; Xiao X.; Jiang C.; Wu W.-W.; Mai L.; Chen T.; Li J.; Ho J. C.; Liao L. Interface Engineering for High-Performance Top-Gated MoS2 Field-Effect Transistors. Adv. Mater. 2014, 26 (36), 6255–6261. 10.1002/adma.201402008. [DOI] [PubMed] [Google Scholar]

- Liu Y.; Huang Y.; Duan X. Van der Waals integration before and beyond two-dimensional materials. Nature 2019, 567 (7748), 323–333. 10.1038/s41586-019-1013-x. [DOI] [PubMed] [Google Scholar]

- Guo Y.; Wei X.; Shu J.; Liu B.; Yin J.; Guan C.; Han Y.; Gao S.; Chen Q. Charge trapping at the MoS2-SiO2 interface and its effects on the characteristics of MoS2 metal-oxide-semiconductor field effect transistors. Appl. Phys. Lett. 2015, 106 (10), 103109. 10.1063/1.4914968. [DOI] [Google Scholar]

- Luo P.; Liu C.; Lin J.; Duan X.; Zhang W.; Ma C.; Lv Y.; Zou X.; Liu Y.; Schwierz F.; Qin W.; Liao L.; He J.; Liu X. Molybdenum disulfide transistors with enlarged van der Waals gaps at their dielectric interface via oxygen accumulation. Nat. Electron. 2022, 5 (12), 849–858. 10.1038/s41928-022-00877-w. [DOI] [Google Scholar]

- Wang J.; Cai L.; Chen J.; Guo X.; Liu Y.; Ma Z.; Xie Z.; Huang H.; Chan M.; Zhu Y.; et al. Transferred metal gate to 2D semiconductors for sub-1 V operation and near ideal subthreshold slope. Sci. Adv. 2021, 7 (44), eabf8744 10.1126/sciadv.abf8744. [DOI] [PMC free article] [PubMed] [Google Scholar]

- Wang J.; Guo X.; Yu Z.; Ma Z.; Liu Y.; Lin Z.; Chan M.; Zhu Y.; Wang X.; Chai Y. Low-Power Complementary Inverter with Negative Capacitance 2D Semiconductor Transistors. Adv. Funct. Mater. 2020, 30 (46), 2003859. 10.1002/adfm.202003859. [DOI] [Google Scholar]

- Wang J.; Guo X.; Yu Z.; Ma Z.; Liu Y.; Chan M.; Zhu Y.; Wang X.; Chai Y.; Steep Slope p-type 2D WSe2 Field-Effect Transistors with Van Der Waals Contact and Negative Capacitance. In 2018 IEEE International Electron Devices Meeting (IEDM). IEEE, 2018, pp 22.3.1–22.3.4. [Google Scholar]

- Qi D.; Li P.; Ou H.; Wu D.; Lian W.; Wang Z.; Ouyang F.; Chai Y.; Zhang W. Graphene-Enhanced Metal Transfer Printing for Strong van der Waals Contacts between 3D Metals and 2D Semiconductors. Adv. Funct. Mater. 2023, 33 (27), 2301704. 10.1002/adfm.202301704. [DOI] [Google Scholar]

- Kawaharamura T.; Uchida T.; Sanada M.; Furuta M. Growth and electrical properties of AlOx grown by mist chemical vapor deposition. AIP Adv. 2013, 3 (3), 032135. 10.1063/1.4798303. [DOI] [Google Scholar]

- Zeng D.; Zhang Z.; Xue Z.; Zhang M.; Chu P. K.; Mei Y.; Tian Z.; Di Z. Single-crystalline metal-oxide dielectrics for top-gate 2D transistors. Nature 2024, 632 (8026), 788–794. 10.1038/s41586-024-07786-2. [DOI] [PMC free article] [PubMed] [Google Scholar]

- Liu H.; Ye P. D. MoS2 Dual-Gate MOSFET With Atomic-Layer-Deposited Al2O3 as Top-Gate Dielectric. IEEE Electron Device Lett. 2012, 33 (4), 546–548. 10.1109/LED.2012.2184520. [DOI] [Google Scholar]

- Hu Y.; Jiang H.; Lau K. M.; Li Q. Chemical vapor deposited monolayer MoS2 top-gate MOSFET with atomic-layer-deposited ZrO2 as gate dielectric. Semicond. Sci. Technol. 2018, 33 (4), 045004. 10.1088/1361-6641/aaaa5f. [DOI] [Google Scholar]

- Radisavljevic B.; Radenovic A.; Brivio J.; Giacometti V.; Kis A. Single-layer MoS2 transistors. Nat. Nanotechnol. 2011, 6 (3), 147–150. 10.1038/nnano.2010.279. [DOI] [PubMed] [Google Scholar]

- Wang H.; Yu L.; Lee Y.-H.; Shi Y.; Hsu A.; Chin M. L.; Li L.-J.; Dubey M.; Kong J.; Palacios T. Integrated Circuits Based on Bilayer MoS2 Transistors. Nano Lett. 2012, 12 (9), 4674–4680. 10.1021/nl302015v. [DOI] [PubMed] [Google Scholar]

- Li W.; Fan D.; Shao L.; Huang F.; Liang L.; Li T.; Xu Y.; Tu X.; Wang P.; Yu Z.; et al. , High-Performance CVD MoS2 Transistors with Self-Aligned Top-Gate and Bi Contact. In 2021 IEEE International Electron Devices Meeting (IEDM). IEEE, 2021, pp 37.3.1–37.3.4. [Google Scholar]

- Wang J.; Yao Q.; Huang C.-W.; Zou X.; Liao L.; Chen S.; Fan Z.; Zhang K.; Wu W.; Xiao X.; Jiang C.; Wu W.-W. High Mobility MoS2 Transistor with Low Schottky Barrier Contact by Using Atomic Thick h-BN as a Tunneling Layer. Adv. Mater. 2016, 28 (37), 8302–8308. 10.1002/adma.201602757. [DOI] [PubMed] [Google Scholar]

- Lee S.; Tang A.; Aloni S.; Philip Wong H. S. Statistical Study on the Schottky Barrier Reduction of Tunneling Contacts to CVD Synthesized MoS2. Nano Lett. 2016, 16 (1), 276–281. 10.1021/acs.nanolett.5b03727. [DOI] [PubMed] [Google Scholar]

- Nipane A.; Teherani J. T.; Ueda A. Demystifying the role of channel region in two-dimensional transistors. Appl. Phys. Express 2021, 14 (4), 044003. 10.35848/1882-0786/abf0e1. [DOI] [Google Scholar]

- Kim K. K.; Hsu A.; Jia X.; Kim S. M.; Shi Y.; Hofmann M.; Nezich D.; Rodriguez-Nieva J. F.; Dresselhaus M.; Palacios T.; Kong J. Synthesis of Monolayer Hexagonal Boron Nitride on Cu Foil Using Chemical Vapor Deposition. Nano Lett. 2012, 12 (1), 161–166. 10.1021/nl203249a. [DOI] [PubMed] [Google Scholar]

- Hu Q.; Gu C.; Zhu S.; Li Q.; Tong A.; Kang J.; Huang R.; Wu Y. Capacitorless DRAM Cells Based on High-Performance Indium-Tin-Oxide Transistors With Record Data Retention and Reduced Write Latency. IEEE Electron Device Lett. 2023, 44 (1), 60–63. 10.1109/LED.2022.3225263. [DOI] [Google Scholar]

- Fukamachi S.; Solís-Fernández P.; Kawahara K.; Tanaka D.; Otake T.; Lin Y.-C.; Suenaga K.; Ago H. Large-area synthesis and transfer of multilayer hexagonal boron nitride for enhanced graphene device arrays. Nat. Electron. 2023, 6 (2), 126–136. 10.1038/s41928-022-00911-x. [DOI] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.