Abstract

Developing a low-temperature and cost-effective manufacturing process for energy-efficient and high-performance oxide-thin-film transistors (TFTs) is a crucial step toward advancing next-generation device applications such as wearable and flexible electronics. Among several methods, a liquid-metal printing technique is considered a promising, cost-effective oxide semiconductor process due to its inherent advantages, such as vacuum-free, low-thermal budget, high throughput, and scalability. In this study, we have developed a pressure-assisted liquid-metal printing technique enabling the low-temperature synthesis of polycrystalline wide bandgap n-channel oxide-TFTs. The n-channel oxide TFTs based on ~3 nm-thick β-Ga2O3 channels exhibited good TFT switching properties with a threshold voltage of ~3.8 V, a saturation mobility of ~11.7 cm2 V−1 s−1, an on/off-current ratio of ~109, and a subthreshold slope of ~163 mV/decade. We also observed p-channel operation in the off-stoichiometric GaOx channels fabricated at high-pressure conditions. Toward oxide-based circuit applications, we developed high-performance oxide-TFT-based inverters. While our approach can promote the advancement of low-temperature manufacturing for oxide TFT technology, further work will be necessary to confirm the role of the applied pressure in the β-Ga2O3 crystallization process.

Subject terms: Electronic devices, Nanoscale devices

Oxide-based thin film transistors (TFTs) hold promise for low-power electronics, but their fabrication usually requires high temperatures. Here, the authors report a low-temperature pressure-assisted liquid-metal printing method to fabricate high-performance β-Ga2O3 TFTs and logic inverters.

Introduction

The demand for sustainable high-performance electronic devices and integrated circuits has been on the rise, especially for advanced device applications such as flexible displays1, lightweight wearable electronics and sensors2,3, electronic skin4,5, Internet of Things6, and back-end-of-line (BEOL)-compatible transistors for three-dimensional highly-integrated circuits7. To develop these device applications, it is crucial to explore low-temperature semiconductor device fabrication processes that not only reduce production costs but also minimize the environmental impact of electronic devices, significantly contributing to the development of sustainable electronics. Therefore, enormous efforts to develop semiconductor materials and device processing have been devoted to paving the way for the realization of environmentally friendly and cost-effective sustainable electronics8–16.

In recent years, a variety of semiconductor materials such as organics and oxide semiconductors have been developed for low-temperature and cost-effective processing such as solution process and ink-jet printing8–15,17. Among these materials, ionic metal-oxide semiconductors, composed of post-transition metals, such as a-In-Ga-Zn-O (a-IGZO), In2O3, ZnO, SnO2 have emerged as promising electronic materials to develop low-temperature processed and cost-effective, ubiquitous electronics. In general, it is well-known that structural defects are a common issue in low-temperature material/device processing, causing severe degradation of electrical properties in conventional semiconductors. However, n-type oxide semiconductors are less sensitive to structural defects due to their unique electronic structure nature, and electron transport is not significantly hindered18. This advantage offers a great opportunity to develop low-temperature processed electronic devices.

Currently, there have been significant advancements in the development of solution-processed oxide-based thin-film transistors (oxide TFTs), leading to several high-performance n-channel oxide TFTs19–25. However, an additional device fabrication process, such as post-thermal annealing, is generally required to achieve a device-quality semiconducting channel for TFT applications. A post-annealing process for oxides typically involves relatively high temperatures (usually between 300–600 °C) and can potentially negate the advantages of oxide semiconductors for low-temperature processed electronic devices19–22,24,25. Additionally, precise control of the processing atmosphere is often necessary, even in solution processes25,26. As a result, there is a high demand for oxide-based device processing at low temperatures, vacuum-free, and non-controlled atmospheric circumstances.

β-gallium oxide (β-Ga2O3) is a well-known n-type wide-bandgap oxide semiconductor with ultra-large wide-bandgap nature of 4.4–4.9 eV and relatively high electron mobility of 100–200 cm2 V−1 s−127–30 for a wide field of device applications such as deep-ultraviolet (DUV) optoelectronics31–33, power electronics operated in high-electrical fields (~MV/cm) and high-temperature devices (250–300 °C)34–36. The wide-bandgap nature of Ga2O3 is especially advantageous for designing devices capable of operating in harsh environments, such as extreme environment sensors, space-based applications, and terrestrial applications. Additionally, β-Ga2O3 is expected to develop energy-efficient operable transistors with low power consumption due to the low-channel leakage (i.e., off-current) nature originating from the low intrinsic carrier concentration and wide-bandgap. Therefore, Ga2O3 holds promise as a semiconductor material for microelectronics, and several demonstrations of high-performance β-Ga2O3 transistors have already been achieved. Current research on β-Ga2O3 transistors primarily focuses on metal-oxide-semiconductor field-effect transistor (MOSFET) structures using bulk single-crystal wafers for power devices. However, developing β-Ga2O3 TFTs remains challenging due to the high-temperature process required for β-Ga2O3 film growth in conventional physical vapor deposition (PVD) methods. Nevertheless, low-temperature processes for Ga2O3 TFTs show promise for various practical applications, such as low-power switching devices and solar-blind deep-ultraviolet photodetectors, originating from their ultra-wide-bandgap nature.

To date, high-performance Ga2O3 transistors use electron-doped single-crystal β-Ga2O3 channels, grown at a high temperature of >600 °C34,35,37,38 and prepared using a mechanical exfoliation process39–41. Recently, amorphous and polycrystalline β-Ga2O3 TFTs have also been demonstrated, but achieving good TFT device operations still requires high process temperatures (200–900 °C)42–45. Moreover, the mobility of the previously reported Ga2O3 TFTs is only limited to <2 cm2 V−1 s−1, which is insufficient for high-performance device applications42–45. Thus, developing a low-temperature process for β-Ga2O3 thin film with high mobility is critical to advancing the field of ultra-wide-bandgap oxide semiconductor electronic devices. Furthermore, Ga2O3 emerges as the next promising channel material in TFT technology to significantly reduce off-current and power consumption compared to the currently commercialized a-IGZO TFTs.

In this work, we proposed a solvent-free, vacuum-free, pressure-assisted liquid metal printing method called PA-LMP to fabricate high-performance β-Ga2O3 TFTs. The liquid metal printing (LMP) method is proposed for forming high-quality crystalline oxide materials with superior electrical properties compared to conventional physical/chemical vapor thin-film deposition, owing to its distinct thermodynamic pathway17,46. Therefore, the LMP method has already been demonstrated to develop high-mobility Indium-based n-channel oxide TFTs46. Here, the PA-LMP approach, which involves applying external uniaxial pressure during oxide skin formation on liquid metal, is demonstrated to directly form high-quality polycrystalline β-Ga2O3 nanosheets at a low temperature of 150 °C under a non-controlled ambient air atmosphere, exhibiting high-performance transistor operation. The presented n-channel β-Ga2O3 TFTs exhibited superior electrical characteristics with a high saturation mobility of 11.7 cm2 V−1 s−1, on/off-current ratio of ~109, and subthreshold swing of 163 mV·decade−1. Additionally, we successfully demonstrated a zero-VGS-load NMOS inverter composed of enhancement/depletion-mode β-Ga2O3 TFTs and an all-oxide-based CMOS inverter using liquid metal printed p-channel SnO TFTs. These inverters operated in rail-to-rail full-swing voltage transfer operations with high voltage gain and low static power dissipation.

Results and discussion

Liquid-metal printing for Ga2O3 growth and characterization

A family of Ga2O3 is known to consist of five crystalline polymorphic forms, namely α, β, γ, δ, and ε phases. The monoclinic β-Ga2O3 phase is the most stable, with lattice constants of a = 1.22 nm, b = 0.30 nm, and c = 0.58 nm, and it exhibits good thermal stability33,47 (as shown in Fig. 1b). Figure 1b summarizes the transformation relationships among the five polymorphic forms of Ga2O3 under equilibrium conditions. The α and γ forms are metastable and can be easily formed from GaO hydrate and gel forms and then transform into β-phase. However, to achieve the β-Ga2O3 phase from these metastable phases, a high-temperature process of at least 300 °C is required48.

Fig. 1. Pressure-assisted liquid-metal printing for β-Ga2O3 thin-film transistors (TFTs).

a Motivation and purpose for developing low-temperature processed wide-bandgap Ga2O3 TFTs. b Phase transformation relationship for Ga2O3 polymorphism. c Schematic and photographs of the developed pressure-assisted liquid metal printing routes for Ga2O3 nanosheet fabrication.

On the other hand, β-Ga2O3 thin film can be directly grown by several PVD techniques, such as sputtering and pulsed laser deposition. However, high-temperature substrate heating and post-deposition annealing, typically over 500 °C, are required for the thin-film growth process44,49. These results imply that low-temperature growth of β-Ga2O3 is very challenging in conventional thin-film growth approaches. The liquid metal printing approach can form crystalline and highly conductive oxide films upon deposition, avoiding insulating intermediate phases and eliminating the thermodynamic barriers posed by precursor decomposition17,46, which is typical in the traditional approach to growing β-Ga2O3. The traditional processes involve the formation of GaO hydrate and gel forms, which then transform into the β-phase during subsequent processing. (Fig. 1b) We believe the oxidation process of the liquid metal presents different thermodynamic barriers and pathways for growing oxide materials, potentially making it easier to produce high-quality oxide materials at lower process temperatures. Furthermore, additional energy sources to modify thermodynamic parameters for crystallization are needed to overcome this issue and lower the growth temperature. It is considered that the external environmental pressure is a typical fundamental thermodynamic parameter and kinetic variable for the free energy change of the materials system defined by ΔGf = Δ(E + PV) – TΔS, where E is internal energy, P is pressure, V is volume, T is temperature, and S is entropy50. External pressure provides the opportunity to facilitate the crystallization process of oxide materials and lowers the crystallization temperature51. Therefore, we developed a method for low-temperature growth of β-Ga2O3 using external uniaxial pressure-liquid metal printing.

Figure 1c shows a schematic illustration of the PA-LMP method for fabricating Ga2O3 nanosheets under ambient air. The liquid-metal printing process was performed at 150 °C under an external uniaxial pressure of approximately 29 kPa. (printing process temperatures (Tp) of 150 °C and process pressure (Pp) of 29 kPa) The process steps are described in detail in Supplementary Fig. 1. The nanometer-thin surface oxide of liquid Ga is formed by self-limiting Cabrera–Mott oxidation in the ambient air to grow the Ga2O3 nanosheets. The optical microscope images and photographs of the Ga2O3 grown by previously reported LMP52–55 and the proposed PA-LMP method show that these samples exhibit large-scale Ga2O3 nanosheets with dimensions of around 1 × 1 cm2. (Fig. 1a, b) (The schematic of the conventional LMP is shown in Supplementary Fig. 2) The entire laterally large Ga2O3 layer is continuous and without significant holes and cracks under optimized synthesis operations. (Supplementary Fig. 3 shows additional optical microscope images of the Ga2O3 nanosheet fabricated by the different printing process parameters.) Fig. 2a, b displays an atomic force microscopy (AFM) image of nanosheets grown by the previously reported and proposed PA-LMP method. The edge step-height profile of these nanosheets found that the thickness was approximately 3.0 nm for both films. The root-mean-square of surface roughness (RRMS) of the Ga2O3 nanosheets grown using LMP and PA-LMP methods were measured to be approximately 1.16 and 0.64 nm, respectively, comparable to the RRMS of SiO2 surface (approximately 1.0 nm). These results suggest that the surface roughness of the Ga2O3 nanosheets is primarily due to the underlying SiO2/Si substrate. Moreover, the presented Ga2O3 nanosheets were homogeneously and conformally grown on the substrates. Therefore, it was also confirmed that the developed pressure-assisted liquid-metal printing enabled the direct printing of large-area oxide materials onto various substrates, including SiO2/Si, III-V (GaAs), transparent glass, paper, and flexible plastic substrates like PET, allowing the development of versatile applications by integrating diverse functional materials and substrates (Supplementary Fig. 4).

Fig. 2. Material and electrical characterization of Ga2O3 films.

Optical microscopy image and atomic force microscopy (AFM) image (including cross-sectional step-height profile) for the Ga2O3 nanosheet were prepared by a conventional liquid metal printing (LMP) (without applied printing process pressure) and b pressure-assisted liquid metal printing (PA-LMP) methods (applied printing process temperatures (Tp) of 150 °C and printing process pressure (Pp) of 129 kPa). c Schematics of the device structure of the GaOx thin-film transistors (TFTs). d Typical transfer characteristics for the Ga2O3 TFTs prepared by LMP (Tp of 150 °C and Pp of 0 kgf/cm2)) and PA-LMP (Tp of 150 °C and Pp of 129 kPa) methods. (IDS: drain currents, VDS: drain-to-source voltage, VGS: gate bias) The channel width (W) and length (L) of TFTs are 300 and 100 µm, respectively. e Magnified view of the linear regime in the typical output characteristics for the Ga2O3 TFT. f Typical output characteristics for the Ga2O3 TFT. g Low-magnified high-resolution transmission electron microscopy (HRTEM) images of the Ga2O3 nanosheet synthesized by the conventional LMP route. (without applied printing process pressure) Corresponding h high-magnified HRTEM image and i selected area electron diffraction (SAED) pattern. j Low-magnified HRTEM images of Ga2O3 nanosheet synthesized by the pressure-assisted liquid-metal route. (Tp of 150 °C and Pp of 129 kPa) Corresponding k high-magnified HRTEM image and l SAED pattern.

We fabricated inverted-staggered (i.e., bottom-gate and top-contact) structured TFT devices using the Ga2O3 nanosheets as a channel layer on thermally-oxidized SiO2/p+-Si substrate (Fig. 2c). The SiO2 served as the gate oxide with a thickness of 150 nm, while the p + -Si acted as the gate electrode. The ITO was used as the source/drain electrode for the Ga2O3 TFTs to form ohmic contacts33,56,57. The channel width (W) and length (L) are 300 and 100 µm, respectively. The optical microscopy image and scanning electron microscopy (SEM) image of the Ga2O3 TFT are shown in Supplementary Fig. 5. Figure 2d displays the transfer characteristics of the Ga2O3 nanosheet TFTs fabricated by the conventional LMP and PA-LMP methods. In the case of the Ga2O3 fabricated by conventional LMP, the drain current was comparable to the background current level (~pA) of our device measurement system, and no TFT action was observed. This indicates that the LMP-grown nanosheet is electrically insulating.

In contrast, the PA-LMP-grown Ga2O3 channel (Tp of 150 °C and Pp of 129 kPa) exhibits desirable n-channel TFT operation, in which the drain currents (|IDS|), measured by the drain-to-source voltage (VDS), increase upon applying negative gate bias (VGS). The output characteristics show ohmic liner-relations at small VDS regions and clear pinch-off behavior with the IDS saturation, confirming that the device operation follows the standard MOSFET model (Fig. 2e, f). The key TFT device characteristics (i.e., saturation mobility (μsat), linear mobility (μlin), s-value, and threshold voltage (Vth)) were determined as the following: the μsat, μlin are estimated by the following equation, ), , respectively, where Cox is the gate insulator capacitance per unit area. The subthreshold slope (s-value) is extracted from the slope in the semi-logarithmic plot with . A reasonable high μsat of 11.7 cm2 V−1 s−1 and μlin of 10.2 cm2 V−1 s−1 was obtained for the PA-LMP fabricated TFTs. The Vth is determined from the intercept of a straight-line fit of the (IDS)1/2 − VGS plot and estimated 3.8 V, indicating that the device operates in enhancement mode, the “normally-off” operation, which is preferred for low-power analogs/digital circuits. The device also exhibits a small s-value of 163 mV dec−1. Trap-state density (Dit) is estimated from the s-values using the following relation: , where e is the elementary electric charge, kB is the Boltzmann constant, T is the temperature, Cox is the gate capacitance per area. The Dit was estimated as 2.53 × 1011 cm−2 eV−1, which is a significant improvement over previously reported Ga2O3 TFTs with the Dit of ~1012 cm−2 eV−1. Importantly, the presented β-Ga2O3 nanosheet TFTs exhibit higher mobility and lower Dit with a much lower process temperature compared to reported Ga2O3 TFTs fabricated by traditional thin-film processing. (Supplementary Table 1 for the summary of device performance for previously reported Ga2O3 TFTs). These findings demonstrate that the PA-LMP method produces a high-quality Ga2O3 semiconductor nanosheet with a low defect density at a low temperature. In addition, the off-current density of the presented TFT devices is estimated to be ~3 × 10−15 A/μm, limited by the measurement instrument. The leakage current of the Ga2O3 TFTs is potentially even lower than that of commercial a-IGZO TFT devices (~10−18 A/μm)58,59 in display applications. This is attributed to the wider bandgap nature of the Ga2O3 channel compared to a-IGZO. The device-to-device statistical analysis was also performed using ten working devices on a single substrate, and the results are summarized in Supplementary Fig. 6. The average values of μsat of 5.02 ± 4.05 cm2 V−1 s−1, μlin of 4.21 ± 5.87 cm2 V−1 s−1s-values of 0.19 ± 0.12 V·dec−1, Vth of 3.61 ± 2.99 V, and log(Ion/Ioff) of 8.09 ± 1.54 were obtained. (Supplementary Figs. 6–8 provides a detailed discussion about the device uniformity) Furthermore, we observed no significant degradation in the device characteristics of the Ga2O3 TFTs even after 1 month of storage under a non-controlled ambient atmosphere, confirming the environmental stability of the devices in the air. (Supplementary Fig. 9 for the environmental stability test for Ga2O3 TFTs) The photoresponse property of Ga2O3 TFTs was also evaluated. No photoresponse was observed under green, blue, or UV light illuminations, which can be attributed to the wide-bandgap nature of Ga2O3. (Supplementary Fig. 10).

From the output characteristics, the output resistance of 1/gd, where gd is the output conductance, was evaluated as >80 MΩ (Supplementary Fig. 11a). We also calculated the transconductance, gm, and the 1/gd as a function of VGS (Supplementary Fig. 11b). The intrinsic gain, defined as Ai = gm/gd, was as high as 1000 at VDS of 30 V, significantly higher than that for other source-gate oxide TFTs (Schottky-barrier oxide TFTs)60–62 and one order of magnitude higher than that for traditional ohmic contact IGZO TFTs. (Supplementary Fig. 11c) The high gains in the presented Ga2O3 TFTs guarantee the high potential of amplifier applications with better circuit stability and signal-to-noise ratio in digital/analog circuits. Moreover, good current saturation characteristics are immune to wide-range VDS modulation, making it a promising candidate for use as a current source in pixel circuits.

We also investigated the effect of post-thermal annealing atmospheres on the ultrathin Ga2O3 TFTs fabricated by PA-LMP. We observed that the TFT characteristics remain almost unchanged during annealing up to a temperature of 200 °C. (Supplementary Fig. 12). On the other hand, vacuum annealing (~10−5 mTorr) improved the TFT mobility but also exhibited a negative Vth shift with the increase of off-current. This observation is attributed to the generation of extra carriers due to oxygen vacancy formation by vacuum annealing.

We analyzed the nanosheet structures grown by the conventional LMP and PA-LMP methods using transmission electron microscopy (TEM). (TEM sample preparation procedure was provided in Supplementary Fig. 13). Figure 2g shows a TEM image of the Ga2O3 nanosheet grown by the LMP method. The corresponding high-resolution TEM (HRTEM) image reveals no lattice-ordered structure in the LMP-grown nanosheet. (Fig. 2h) The corresponding selected area electron diffraction (SAED) pattern confirmed a halo pattern (Fig. 2i). These observations conclude that the nanosheet prepared by the LMP method is amorphous, which agrees with the previous reports52,63–65. Since amorphous semiconductor includes high-density tail-state defects13, the nanosheet is speculated to involve high-density electron traps. Therefore, the LMP-grown amorphous GaOx exhibited a high-resistive state. We also attempted to improve the electrical properties of the amorphous GaOx nanosheets by post-thermal annealing at temperatures ranging from 200 to 400 °C. However, all devices remained insulative in the presented annealing conditions (Supplementary Fig. 14). To achieve a crystalline β-Ga2O3 phase, high-temperature annealing at temperatures above 500 °C may be required, as reported in previous studies44,64,66. However, high-temperature annealing may cause serious off-chemical stoichiometry, which can lead to the failure of TFT operations in the presented nanosheet channel.

In contrast, a distinct polycrystalline feature, i.e., ordered atomic alignment, for the PA-LMP-grown nanosheet (Tp of 150 °C and Pp of 129 kPa) was observed in the TEM analysis (Fig. 2j and Supplementary Fig. 15a for the low-magnified HRTEM images of the Ga2O3 nanosheet). The HRTEM image also showed the crystal lattice structure with internal spacings of ~0.362 and ~0.263 nm, which are assigned to the (201) and (−111) planes, respectively, of the monoclinic β-Ga2O3 crystal structure. (Fig. 2k) The corresponding SAED pattern is shown in Fig. 2i, and exhibits spots indexed to the (−111), (201), (−311), and (400) crystal plans. The observation concluded that the presented nanosheet was randomly oriented β-Ga2O3 crystals. In addition, we performed TEM analysis for the Ga2O3 nanosheet prepared using the PA-LMP approach with different process parameters to confirm the direct growth of β-Ga2O3 crystals. (Supplementary Figs. 15–17) The energy-dispersive X-ray spectroscopy (EDX) chemical composition mapping analysis also finds that the Ga/O atomic ratio is ~0.64, which is close to the ideal stoichiometry of Ga2O3 (Supplementary Fig. 18). The grazing incidence X-ray diffraction (GIXRD) analysis also supported that the Ga2O3 nanosheets prepared by the PA-LMP method were polycrystalline β-Ga2O3. (Supplementary Fig. 19) Furthermore, we conducted a cross-sectional TEM analysis for the Ga2O3 nanosheet prepared using the liquid metal printing approach on the Si/SiO2. The Ga2O3 nanosheet was prepared at the Tp of 150 °C, and the Pp of 129 kPa, exhibiting a high TFT mobility of 8–10 cm2 V−1 s−1. The distinct polycrystalline nature of β-Ga2O3 was also observed, providing direct evidence that liquid metal printing can grow crystalline β-Ga2O3 on the SiO2/Si substrate. (Supplementary Figs. 20–23) X-ray photoemission spectroscopy (XPS) analysis also confirmed that this material is Ga2O3 with the Ga3+ oxidation state. (Supplementary Fig. 24) Based on the material characterization discussed above, the developed PA-LMP method directly grows crystalline β-Ga2O3 with device quality at less than 150 °C.

We believe that the nature of oxidation of the liquid metal has a different thermodynamic barrier and path to grow oxide materials, potentially making it easier to grow high-quality oxide materials at lower process temperatures compared to other material growth approaches17,46. Crystalline β-Ga2O3 has been successfully synthesized using liquid metal printing, achieved by scraping off the parent metal layer under stress at a process temperature of 200 °C67. Given that the thermodynamic barrier and pathway may lower when employing liquid metal oxidation, the crystallization of the Ga2O3 phase could potentially be induced by various factors, such as heat, pressure, and stress, to lower the energy barriers for crystallization. Furthermore, our findings suggest that the effects of nanoscale confinement crystal growth and external pressure may influence the facilitation of low-temperature crystallization for the β-Ga₂O₃ phase. It is well-known that nucleation is the initial critical process for crystallization, so reducing the free energy barriers of the nucleation process is essential. In general, free energy barriers for homogeneous () and heterogeneous nucleations () are defined by

| 1 |

Where γ is the interfacial energy. is a function related to the contact angle θ as

| 2 |

In the developed PA-LMP method, the contact angle is nearly zero since the liquid metal is confined in the nanogap that two substrates generate. Confined systems are expected to influence crystallization processes significantly. As the volume of the confining space decreases, the role of the surface becomes increasingly essential in such constrained systems. To achieve low-temperature growth, crystallization in highly confined nanogap regions (nanoscale confinement) provides the potential approach to lower the energy barrier by reducing the reactive surface area of nuclei, thereby decreasing the surface energy penalty. Additionally, nanoscale confinement can alter the nucleation pathway, further reducing the overall energy barrier68,69. Previous studies have explored crystallization and phase transitions under nanoscale confinement70–72. For example, ref. 70 applied classical nucleation theory to investigate nucleation during the solidification and melting phase transitions of germanium (Ge) within nanoscale confinement between two planar surfaces. They found that nanoscale confinement significantly lowers nucleation temperatures of Ge for solid and liquid phases, with a 5.0 nm gap reducing nucleation temperature by up to 350 °C. A detailed discussion of two-dimensional crystallization in the nanoscale confined space is provided in the Supplementary Information.

Moreover, it is widely accepted that external pressure impacts the thermodynamic driving forces for crystal nucleation and growth processes. The pressure (P) on the nucleation activation energy, ΔG*, can be expressed as73

| 3 |

where, where Gc and Ga are the Gibbs free energies of the crystalline and amorphous phases, respectively, γ is interfacial energy and is not sensitive to pressure, is the difference in molar volumes between the crystalline phase (Vc) and the amorphous phase (Va). Based on previously reported experimental results, the film density of amorphous GaOx was determined to be approximately 5.2–5.4 g·cm⁻³[ 43,74, which is lower than that of β-Ga2O3 (density of ~5.95 g·cm⁻³)75–77. In this case, i.e., , since the smaller molar volume of the crystalline phase compared to the amorphous phase () and As a result, our findings suggest that pressure may also facilitate crystallization by potentially reducing the nucleation activation energy. Further research is required to validate the impact of applied pressure on the β-Ga₂O₃ crystallization process.

Effect of the printing process on Ga₂O₃ transistor performance

Figure 3a illustrates the variation of transfer curves for the ultrathin β-Ga2O3 TFTs grown by the PA-LMP under a pressure of 29 kPa at different printing process temperatures. (Supplementary Fig. 26 shows the transfer characteristics for linear regions. (VDS = 1 V)) When the device was fabricated at 30 °C, the channel showed highly conducting behavior with an electrical conductivity of 28.3 S·m−1, but the device exhibited negligible field-effect current modulation. Decent TFT actions with an on/off current ratio of 105 were observed when the channels were grown at process temperatures above 80 °C. Furthermore, the TFT mobility was improved by raising the process temperature up to 150 °C. However, a large positive Vth shift to 58 V was observed for the device fabricated at a high temperature of 200 °C, indicating that the high-temperature process under a pressure of 29 kPa resulted in poor TFT performances. The fundamental device parameters (μsat, μlin, s-value, Vth, and on/off current ratio) are also summarized in Fig. 3b–e. The data were analyzed using 16 representative working devices from different samples.

Fig. 3. Effect of the printing process on Ga2O3 thin-film transistor (TFT) performance.

a Variation of transfer characteristics for the Ga2O3 nanosheet TFTs with different printing process temperatures under the uniaxial process pressure of 29 kPa. The corresponding TFT parameters b saturation mobility (μsat) and linear mobility (μlin), c subthreshold swing (s-value) and trap-state density (Dit), d threshold voltage (Vth), and e on/off current ratio are plotted. f Variation of transfer characteristics for the Ga2O3 TFTs with different process pressures under the printing process temperature of 150 °C. Corresponding TFT parameters g μsat and μlin, h s-value and Dit, i Vth, and j on/off current ratio are plotted. (The error bars are calculated using data from 16 representative working devices across different samples).

The temperature at which the gallium oxide skin is formed on the Ga liquid surface metal plays a critical role in the oxidation process. Our observations suggest that the low process temperature of 30 °C may not be sufficient to form Ga2O3 phases using the PA-LMP method with a printing process pressure of 29 kPa, resulting in high-density Ga metal impurity and highly conductive channels in the as-prepared device. From the TEM characterization, it was also confirmed that Ga-rich GaOx with embedded Ga metal in nanosheets grown by the printing process at the Tp of 30 °C and the Pp of 29 kPa. (Supplementary Figs. 27, 28) Interestingly, the devices after post-thermal annealing showed p-channel operation with a small on/off current ratio (Supplementary Fig. 29). The origin of the p-type behavior is not yet clear, but we speculate that the p-type behavior may relate to low-valence Ga(I)-based metastable phases formation, such as GaO or Ga2O, which possibly have the VBM structure composed of spherical Ga 5s orbital. Further investigation of the origin of p-type behavior in gallium oxide is required.

On the other hand, a high-temperature printing process of PA-LMP is sufficient to oxidize gallium metal and form the Ga2O3 phase. However, the poor TFT performance was observed during the high-temperature process at 200 °C under a pressure of 29 kPa (Tp of 200 °C and Pp of 29 kPa). This is primarily caused by (1) the carrier concentration, resulting from oxygen vacancies, can be decreased through compensation by oxygen-containing annealing effect in the ambient air atmosphere, while (2) excessive oxygen defects, which function as acceptor-like defects, are introduced during oxygen-containing air annealing. Therefore, the optimal process temperature for β-Ga2O3 TFTs was found to be between 80–150 °C for the PA-LMP. We also fabricated TFTs using the channels prepared by the conventional LMP method at high temperatures of up to 200 °C and measured their electrical characteristics. However, no field-effect modulation was observed in any of the devices, indicating that the Ga2O3 fabricated LMP is electrically insulating regardless of the process temperature. (Supplementary Fig. 30).

Figure 3f shows the variation in transfer characteristics with different process pressures, with a process temperature of 150 °C. (Supplementary Fig. 26 also shows the transfer characteristics for linear (VDS = 1 V) region.) The performance of TFTs was found to improve with increasing external pressure, with the most significant improvement observed at uniaxial pressure of 129 kPa. The most optimized TFT switching properties were achieved under this condition, with high μsat of 11.7 cm2 V−1 s−1, large on/off current ratio of ~109, and small subthreshold slope of 137 mV·decade−1, and Vth of ~4 V. The device exhibits clockwise hysteresis originating from electron traps, but the hysteresis window was improved to 0.1 V under high-pressure conditions (Supplementary Fig. 31). The key device parameters (μsat, μlin, s-value, Vth, and on/off current ratio) are also summarized in Fig. 3g–j. The data were analyzed using 16 representative working devices from different samples. The average values of μsat of 8.24 ± 1.78 cm2 V−1 s−1, μlin of 7.34 ± 1.96 cm2 V−1 s−1, s-values of 125 ± 23.6 mV dec−1, Vth of 4.73 ± 1.10 V, and log(Ion/Ioff) of 9.22 ± 0.43 were obtained under the temperature of 150 °C and the pressure of 129 kPa. (Tp of 150 °C and Pp of 129 kPa) At high-pressure conditions (206 kPa), the device operation switched from n-channel to p-channel devices, suggesting the formation of low valance Ga(I) under high-pressure conditions. The optical microscope images of these samples with different process conditions, which we investigated for their electrical properties, are also shown in Supplementary Fig. 3. Furthermore, the AFM image reveals the effect of the applied pressure on the surface morphology, as discussed in the Supplementary Figs. 32, 33.

Figure 4 summarizes the TFT operations fabricated by different process pressures and temperature conditions in the PA-LMP route. All The transfer characteristics are presented in Supplementary Fig. 34. Regardless of the nanosheet growth conditions, conventional LMP-grown nanosheets were electrically insulating amorphous gallium oxide, which was in good agreement with previous reports64,78. In contrast, the PA-LMP directly synthesized a semiconducting polycrystalline β-Ga2O3 channel in the range of the Tp of 80–200 °C with the Pp of 29 kPa and in the range of the Tp 150–200 °C with the Pp of 129 kPa. The polycrystalline nature of β-Ga2O3 is confirmed by both GIXRD and TEM characterization. (Supplementary Figs. 15–17, 19). The performance of TFT degraded with a positive threshold voltage shift during the high-temperature process at 200 °C under pressures of 29 and 129 kPa, respectively. The reason is suspected to be a decrease in carrier concentration originating from oxygen vacancies and the introduction of excessive oxygen defects functioning as acceptor-like defects during annealing in oxygen-containing air. Interestingly, amorphous films grown at high pressure of 206 kPa with the process temperature of 150 and 200 °C exhibited p-type behavior. We suspect these materials result from the slight oxidation of Ga metal, leading to off-stoichiometric GaOx materials. These materials might include low-valence Ga(I)-based metastable phases, possibly with a VBM structure composed of spherical Ga 5s orbitals contributing to the p-type behavior. Further study is required to investigate these materials. We notice that there are reports of Ga ultrathin film growth using a similar liquid metal printing method79,80. These results corroborate our findings that liquid metal printing can form off-stoichiometric GaOx through slight oxidation of Ga metal under an air atmosphere.

Fig. 4. Electrical properties of Ga2O3 films grown by liquid-metal printing.

Summary of the electrical properties of the gallium oxide nanosheet channel grown using the pressure-assisted liquid-metal route under various printing process conditions of uniaxial pressures and temperatures.

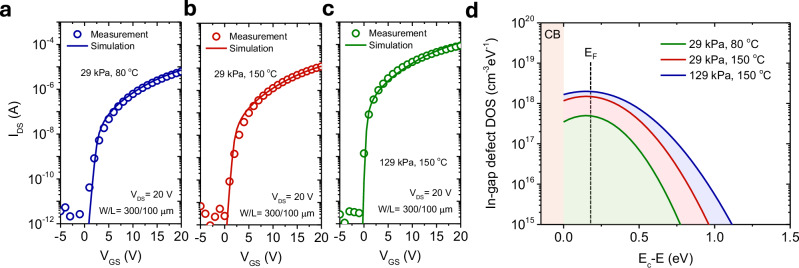

To gain further insight into the variation of TFT characteristics, we performed the Technology Computer-Aided Design (TCAD) device simulation to extract the subgap defect density of the state (DOS) profile. Figure 5a–c shows the measured and simulated transfer curves of Ga2O3 TFTs with different process conditions. Only parameter optimization for the subgap acceptor-like defect density of state (DOS) can reproduce the measured transfer curves, indicating that the variation in TFT characteristics under different process parameters mainly originates from the change in subgap defect DOS in the Ga2O3 channels. The extracted subgap defect DOS near the conduction band (CB) of Ga2O3 TFTs under different process conditions are shown in Fig. 5d. (Supplementary Table 3 provides the parameters of the TFT simulations). We found that all the measured I-V curves were reproduced by only optimizing the acceptor-like defect (i.e., electron trap defect) with Gaussian distribution type,

| 4 |

where NGD is the state densities at the central energy EGA of the Gaussian distribution, Ec is the conduction band edge energy for the reference zero point, EGA is the central energy of , WGD is the characteristic decay energy. Due to the polycrystalline nature of the Ga2O3, we opted not to employ the acceptor-like exponential DOS to fit the measured I-V curves that are used for the tail states near the conduction for the amorphous silicon (a-Si:H) and amorphous IGZO81. All the devices show a low carrier concentration of 5.5 × 1014 cm3 due to the ultra-wide gap nature of Ga2O3.

Fig. 5. TCAD simulation of Ga2O3 thin-film transistors (TFTs).

Comparison of measured (symbols) and simulated (lines) transfer curves with VDS = 20 V for the Ga2O3 TFTs with different printing process conditions. (a Tp of 80 °C, Pp of 29 kPa, b Tp of 150 °C, Pp of 29 kPa, c Tp of 150 °C, Pp of 129 kPa). d Corresponding in-gap density of states (DOS) profiles for the Ga2O3 nanosheet channels for different printing process conditions. Fermi level (EF) lies at Ec − EF = 0.23 eV. (Ec: conduction band edge energy, CB:conduction band.) TCAD simulations were conducted to extract the in-gap defect DOS profile in Ga2O3 TFTs. The measured I-V curves were accurately modeled by optimizing only the acceptor-like defects (electron trap states) using a Gaussian distribution, , where NGD is the state densities at the central energy EGA of the Gaussian distribution, Ec is the conduction band edge energy for the reference zero point, EGA is the central energy of , WGD is the characteristic decay energy.

We observed shallow acceptor-like defect states located at 0.15 eV below the conduction band (Ec − 0.15 eV) in the Ga2O3. TFTs. These acceptor-like defect states primarily function as electron traps in the n-channel oxide TFT devices. The physical origin of these shallow acceptor-like defect states remains elusive; however, we suspect these defects result from Ga vacancies or weakly bonded (excess) oxygen defects43,82,83. The Ga2O3 TFT fabricated with the low-pressure condition (Tp of 80 °C, Pp of 29 kPa) exhibited a relatively high density of shallow acceptor-like defect states of 2 × 1018 cm−3 eV−1 and remained unchanged even in the device fabricated at 150 °C. (150 °C, 29 kPa) On the other hand, we found that the high-pressure condition (150 °C, 129 kPa) effectively reduced the shallow subgap acceptor-like defect DOS to 5 × 1017 cm−3 eV−1, resulting in better TFT performances with higher mobility. This acceptor-like defect reduction makes moving the Fermi level toward the mobility edge easier, achieving band-like conduction and explaining the higher mobilities observed in these TFTs.

We also found that the shallow subgap defect DOS significantly impacts the on-current and s-value but does not affect the turn-on voltage, resulting from the enhancement mode operation. The Dit, estimated from the s-values of the experimental transfer characteristics, are 5.37 × 1011 cm−2 eV−1 (80 °C, 29 kPa), 4.78 × 1011 cm−2 eV−1 (150 °C, 29 kPa), and 1.93 × 1011 cm−2 eV−1 (150 °C, 129 kPa) for these three process conditions, respectively. The shallow subgap defect DOS for all these three conditions we attained from the TCAD simulation correspond to area densities of 6 × 1011 cm−2 eV−1 (80 °C, 29 kPa), 4.5 × 1011 cm−2 eV−1 (150 °C, 29 kPa) and 1.8 × 1011 cm−2 eV−1 (150 °C,129 kPa), respectively, considering the Ga2O3 thickness of 3 nm. These values are consistent with those calculated from experimental s-values.

Circuits based on Ga2O3 thin-film transistors

Since ultrathin oxide channels improve gate controllability and low-off current characteristics of the TFTs, developing a low-power inverter is highly expected for next-generation energy-efficient oxide electronics. We developed oxide-TFT-based inverter circuits, including NMOS and CMOS circuits, using ultrathin Ga2O3 TFTs. The Ga2O3 nanosheets used for the NMOS and CMOS circuits demonstration were grown using the Tp of 150 °C and Pp of 29 kPa. Figure 6a shows the typical transfer characteristics for a zero-VGS NMOS, consisting of the enhancement and depletion-mode TFTs as the driver and load, respectively. The depletion-mode TFTs were fabricated by performing post-thermal annealing under vacuum conditions at 100°C. The effect of vacuum annealing is discussed in Supplementary Fig. 12. The depletion-mode TFTs showed the μsat of 0.8 cm2 V−1 s−1, s-value of 1.6 V·decade−1, Vth of −4.5 V, and on/off current ratio of ~107. The corresponding TFT performances for enhancement-mode TFTs show the μsat of 2.6 cm2 V−1 s−1, s-value of 0.28 mV·decade−1, Vth of 6 V, and on/off current ratio of ~108, respectively. Figure 6b shows a typical voltage transfer characteristic (VTC) of the NMOS inverter, which is the Vout as a function of the Vin with VDD. The inset illustrates the equivalent circuit diagram of the zero-VGS-load NMOS inverter. The output voltage switches from high to low, confirming a clear inverting action with the full-voltage swing. The average voltage gain of the NMOS inverters was 16.9, 45.1, 64.0, 80.5, and 106.4 at VDD from 5 to 25 V (Fig. 6c), respectively, comparable to the previously reported oxide-NMOS inverters84–86 (Supplementary Fig. 35 for statistical results on the gain of the NMOS inverter, and Supplementary Table 4 for the NMOS inverter summary) Fig. 6d also shows the corresponding supply currents (IDD) as functions of Vin. The static currents (Vin = 0 V or Vin = VDD) are lower than 2.4 nA, and the static power dissipation, which is defined by Pstatic = VDD (Istatic_low+Istatic_high)/2, is 28 nW per logic gate at VDD of 25 V. The Pout is estimated as <43 nW per logic gate, confirming that a nanowatt power source can operate the presented inverter (Fig. 6e). The noise margin (NM) is estimated using the maximum equal criterion method and obtained at 57.2% of the ideal value (VDD/2). This indicates that the device has sufficient NM for most static logic applications (Fig. 6f). The dynamic switching was also demonstrated to indicate the potential for circuit applications by further optimizing the dimensions of the devices. (Supplementary Fig. 36). The enhancement-load inverter, which consists of two enhancement-mode TFTs, was also demonstrated (Supplementary Fig. 37 for the detailed inverter performance).

Fig. 6. Ga2O3 transistor-based N-channel Metal-Oxide-Semiconductor (NMOS) inverter.

An NMOS inverter is a logic circuit built using an n-channel MOSFET (NMOS transistor) and a pull-up resistor or load transistor. a Typical transfer characteristics for the depletion-mode and enhancement-mode Ga2O3 TFTs. (The Ga2O3 nanosheets used for the NMOS circuits demonstration were grown using the Tp of 150 °C, Pp of 29 kPa. The depletion-mode TFTs were fabricated by performing post-thermal annealing under vacuum conditions at 100 °C.) b Voltage transfer characteristic (VTC) of the Ga2O3 TFT-based NMOS inverter. c corresponding voltage gains of the Ga2O3 TFT-based NMOS inverter. Inset: schematic circuit diagram of the zero-VGS-load NMOS inverter composed of enhancement/depletion-mode Ga2O3 TFTs. d Corresponding supply currents (IDD). e Output-power consumption (Pout) for the Ga2O3 TFT-based NMOS inverter. f Butterfly curves for noise margin (NM) of the Ga2O3 TFT-based NMOS inverter. (Vin: input voltage, Vout: output voltage, VDD: supply voltage).

All-oxide-CMOS inverter circuits were also developed using n-type ultrathin Ga2O3 TFT and p-type ultrathin SnO TFT, which is also fabricated by a liquid-metal printing technique. The detailed fabrication procedure of p-channel SnO TFTs can be found in our previous work55. The typical transfer characteristics of both the ultrathin p-channel SnO TFT and n-channel Ga2O3 TFT used in the oxide-TFT-based CMOS inverter are shown in Fig. 7a. The n-channel Ga2O3 TFT exhibits the μsat of 1.5 cm2 V−1 s−1, s-value of 0.27 V dec.−1, Vth of 6 V, and on/off current ratio of ~108. The corresponding TFT performances for p-channel SnO TFT are the μsat of 0.2 cm2 V−1 s−1, s-value of 1.9 V·decade−1, Vth of −20 V, and the on/off current ratio of ~105, respectively. The inset of Fig. 7b is the schematic circuit diagram of the CMOS inverters. Figure 7b presents the typical voltage transfer characteristic of the CMOS inverter, where the output voltage switches from high to low, confirming a clear inverting action with the full-voltage swing. The average voltage gain of the inverter was estimated as 38, 50, 79, 110, and 149 at VDD from 10 to 50 V (Fig. 7c), respectively, which is nearly comparable to the previously reported values for oxide-based CMOS inverters87–90. (Supplementary Fig. 35 for statistical results on the gain of the CMOS inverter, and Supplementary Table 5 for the CMOS inverter summary) The IDD of the ultrathin p-SnO/n-Ga2O3 TFT-based CMOS inverter as a function of Vin is shown in Fig. 7d. The static currents are lower than 1 nA, leading to the low static power dissipation of 20 nW per logic gate at a VDD of 50 V. The Pout is smaller than 84 nW per logic gate, which indicates that this CMOS inverter can be operated by the nanowatt power source. (Fig. 7e) This demonstrates the high potential of atomically thin oxide-TFT-based inverter circuits for next-generation energy-efficient thin-film electronics.

Fig. 7. N-Ga2O3/p-SnO transistor-based complementary metal-oxide-semiconductor (CMOS) inverter.

A CMOS inverter is a logic circuit consisting of a p-channel MOSFET (PMOS) as the pull-up device and an n-channel MOSFET (NMOS) as the pull-down device. a Typical transfer characteristics of the ultrathin p-channel SnO TFT with VDS = −20 V and n-channel Ga2O3 TFTs at VDS = 20 V. (The Ga2O3 nanosheets used for the CMOS circuits demonstration were grown using the Tp of 150 °C, Pp of 29 kPa.) b Voltage transfer characteristics (VTC). c Corresponding voltage gains for the p-SnO/n-Ga2O3 TFT-based CMOS inverter. Inset: schematic of the corresponding oxide-TFT-based CMOS inverter circuit. d Corresponding supply currents (IDD). e Output-power consumption (Pout) for p-SnO/n-Ga2O3 TFT-based CMOS inverter.

The uniaxial pressure-assisted liquid-metal printing approach using nanoscale confinement growth was developed for low-temperature processed n-channel β-Ga2O3 TFTs for energy-efficient and cost-effective next-generation ubiquitous sustainable electronics. The presented growth method successfully fabricated device-quality crystalline β-Ga2O3 nanosheet at low temperatures (<150 °C) under vacuum-free, solvent-free, and non-controlled ambient air conditions. The n-channel TFTs based on β-Ga2O3 nanosheet exhibited high performance with a reasonably high mobility of 11.7 cm2 V−1 s−1, an on/off-current ratio of ~109, and a small subthreshold slope of 163 mV·decade−1, which is the best device performance for low-temperature-processed Ga2O3 TFTs to date. We also observed p-channel operation in the off-stoichiometric GaOx channels fabricated at high-pressure conditions. Toward the oxide-based circuit application, we demonstrated low-power and all-oxide-based zero-VGS-load NMOS and CMOS inverters using metal-liquid printing derived Ga2O3 nanosheet channel oxide-TFTs. These inverters showed full-voltage swing characteristics and high energy-efficient operation with low static power dissipations. Our work demonstrates the high potential of β-Ga2O3 for high-performance n-channel oxide TFTs and offers a promising approach for the development of sustainable oxide-TFT technology for next-generation electronics.

Methods

Synthesis of gallium oxide nanosheet

Atomically thin Ga2O3 nanosheets were fabricated by printing the oxide skin from the liquid gallium (Ga) metal. The liquid Ga metal was prepared by melting elemental Ga (99.99% purity, Shot Metals) inside a glass vial on a hot plate at 50 °C in ambient air.

To fabricate the nanosheets, a liquid droplet of the liquid Ga metal (with a size of ~1 to ~5 mm) was placed on a SiO2/Si substrate using a pipette, and the substrate with liquid metal droplet was heated to the desired process temperature (80–200 °C), which is above the melting point of the liquid Ga metal. The surface of a SiO2/Si substrate was treated with O2 plasma (rf power = 70 W for 1 min) and preheated to the desired process temperature (80–200 °C) before a liquid Ga droplet was dropped on it. During the printing process, a second substrate (also treated with O2 plasma and preheated to process temperature) was pressed onto the center of the droplet to spread the liquid alloy homogeneously between the two substrates. The two substrates were kept at process temperature (80–200 °C) and under uniaxial vertical pressure for the gallium oxide nanosheet growth for 3 min. When the printing process time was too long (>10 min), the channel exhibited insulating behavior, rendering the TFTs inoperative. (Supplementary Fig. 38) After the squeezing step with uniaxial vertical pressure, the top substrate was lifted vertically and separated without lateral slippage. Then, homogeneous ultrathin Ga2O3 nanosheets were exfoliated onto both substrates. The strong van der Waals bond between the oxide skin and the substrate facilitated the delamination of the oxide.

Metal inclusions attached to the exfoliated nanosheets could be removed by gently rubbing the SiO2/Si wafer, which was submerged in ethanol, with a soft wiping tool (cotton bud). The Ga2O3 nanosheets were found to be firmly attached to the SiO2 surface due to strong van der Waals adhesion between the nanosheets and the substrate, and they remained intact throughout the cleaning procedure. The large area atomically thin Ga2O3 nanosheets exceeding several centimeters in lateral dimensions could be fabricated efficiently using this method.

TEM sample preparation procedure

First, the TEM grid was placed on top of the glass slide and preheated to process temperature (80–200 °C), which is above the melting point of the liquid Ga metal. Note that we did not perform O2 plasma treatment for the TEM sample, as we did for the Ga2O3 nanosheet on the SiO2/Si substrate.

To fabricate the nanosheets, a liquid droplet of Ga metal (with a size of <1 mm) was pipetted onto a TEM grid, and the TEM grid/glass slide with the liquid metal droplet was kept heated at 50 °C to prevent the liquid Ga from solidifying. During the printing process, we used SiO2/Si as the top substrate (preheated to process temperature (80–200 °C)), pressing it onto the center of the droplet to spread the liquid alloy homogeneously between the TEM grid and SiO2/Si substrates. The TEM grid and SiO2/Si substrates were kept at process temperature (80–200 °C) under uniaxial vertical pressure for gallium oxide nanosheet growth for 3 min.

After the squeezing step with uniaxial vertical pressure, the top SiO2/Si substrate and TEM grid were carefully separated. We then used a soft wiping tool (cotton bud) to remove Ga liquid inclusions directly by gentle rubbing. It is important to note that we did not immerse the sample in ethanol, as we did for the Ga2O3 nanosheet on the SiO2/Si substrate. Following the printing process, we observed that most carbon films were broken. During TEM analysis, we looked for nanosheets suspended and connected/supported by the bar of the TEM grid for detailed analysis. (Supplementary Fig. 13).

Materials characterization

The surface structure of the nanosheet was analyzed using both optical microscopy and atomic force microscopy (AFM). The nanosheet thickness was determined by measuring the height of the patterned edge using AFM. The detailed crystal structures of the Ga2O3 nanosheets were examined using high-resolution transmission electron microscopy (HRTEM) with an acceleration voltage of 200 keV. The selected area electron diffraction (SAED) pattern was obtained using fast Fourier transform (FFT).

Thin-film transistor fabrication and electrical characterization

Thin-film transistors (TFTs) were fabricated with inverted-staggered structures, i.e., bottom-gate and top source/drain contacts. The 150-nm-thick thermal-oxidized SiO2/n+-Si substrates were used as the gate oxide and gate electrode. The channel area was patterned using photolithography and defined by chemical wet-etching with 1 mol/l of diluted HNO3 solution. The source and drain electrodes were made of ohmic contact 40-nm-thick indium tin oxide (ITO), which was deposited by pulsed laser deposition (PLD) with an oxygen partial pressure of 2 × 10−4 Pa at room temperature. The channel length (L) and the width (W), which are defined by metal mask processing, were 100 and 300 μm, respectively. The electrical characteristics were measured using the semiconductor parameter analyzer at room temperature in the dark.

Device simulation

Two-dimensional simulations of the TFTs cross-section were conducted using a 2D ATLAS TCAD simulator (Silvaco) to gain insight into the electronic and defect structures of TFTs. The simulations utilized the same configuration and materials as the TFT devices. The parameters used in the simulations are listed in Supplementary Table 3. The detailed code for the TCAD simulation is available upon request.

Supplementary information

Acknowledgements

This work was partly supported by faculty start-up funds at UC San Diego.

Author contributions

K.N. conceived the concept and supervised the project. C.-H.H. designed the experiments and carried out material growth, device fabrication, and characterization. R.-H.C. and Y.-L.C. conducted material characterization, including TEM, AFM, and XPS. C.-H.H. and K.N. analyzed the results and contributed to writing the manuscript.

Peer review

Peer review information

Nature Communications thanks the anonymous reviewers for their contribution to the peer review of this work. A peer review file is available.

Data availability

Relevant data supporting the key findings of this study are available within the article and the Supplementary Information file. All raw data generated during the current study are available from the corresponding authors upon request.

Competing interests

The authors declare no competing interests

Footnotes

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

The online version contains supplementary material available at 10.1038/s41467-025-57200-2.

References

- 1.Heremans, P. et al. Mechanical and electronic properties of thin‐film transistors on plastic, and their integration in flexible electronic applications. Adv. Mater.28, 4266–4282 (2016). [DOI] [PubMed] [Google Scholar]

- 2.Sun, Y. & Rogers, J. A. Inorganic semiconductors for flexible electronics. Adv. Mater.19, 1897–1916 (2007). [Google Scholar]

- 3.Gao, W., Ota, H., Kiriya, D., Takei, K. & Javey, A. Flexible electronics toward wearable sensing. Acc. Chem. Res.52, 523–533 (2019). [DOI] [PubMed] [Google Scholar]

- 4.Chortos, A., Liu, J. & Bao, Z. Pursuing prosthetic electronic skin. Nat. Mater.15, 937–950 (2016). [DOI] [PubMed] [Google Scholar]

- 5.Hammock, M. L., Chortos, A., Tee, B. C. K., Tok, J. B. H. & Bao, Z. 25th anniversary article: the evolution of electronic skin (e‐skin): a brief history, design considerations, and recent progress. Adv. Mater.25, 5997–6038 (2013). [DOI] [PubMed] [Google Scholar]

- 6.Papadopoulos, N. et al. Touchscreen tags based on thin-film electronics for the internet of everything. Nat. Electron.2, 606–611 (2019). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 7.Son, Y., Frost, B., Zhao, Y. & Peterson, R. L. Monolithic integration of high-voltage thin-film electronics on low-voltage integrated circuits using a solution process. Nat. Electron.2, 540–548 (2019). [Google Scholar]

- 8.Sirringhaus, H. et al. High-resolution inkjet printing of all-polymer transistor circuits. Science290, 2123–2126 (2000). [DOI] [PubMed] [Google Scholar]

- 9.Klauk, H., Zschieschang, U., Pflaum, J. & Halik, M. Ultralow-power organic complementary circuits. Nature445, 745–748 (2007). [DOI] [PubMed] [Google Scholar]

- 10.Yan, H. et al. A high-mobility electron-transporting polymer for printed transistors. Nature457, 679–686 (2009). [DOI] [PubMed] [Google Scholar]

- 11.Gelinck, G., Heremans, P., Nomoto, K. & Anthopoulos, T. D. Organic transistors in optical displays and microelectronic applications. Adv. Mater.22, 3778–3798 (2010). [DOI] [PubMed] [Google Scholar]

- 12.Sirringhaus, H. 25th anniversary article: organic field‐effect transistors: the path beyond amorphous silicon. Adv. Mater.26, 1319–1335 (2014). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 13.Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature432, 488–492 (2004). [DOI] [PubMed] [Google Scholar]

- 14.Fortunato, E., Barquinha, P. & Martins, R. Oxide semiconductor thin‐film transistors: a review of recent advances. Adv. Mater.24, 2945–2986 (2012). [DOI] [PubMed] [Google Scholar]

- 15.Wang, Z., Nayak, P. K., Caraveo‐Frescas, J. A. & Alshareef, H. N. Recent developments in p‐Type oxide semiconductor materials and devices. Adv. Mater.28, 3831–3892 (2016). [DOI] [PubMed] [Google Scholar]

- 16.Hosono, H. How we made the IGZO transistor. Nat. Electron.1, 428–428 (2018). [Google Scholar]

- 17.Scheideler, W. J. & Subramanian, V. How to print high-mobility metal oxide transistors—Recent advances in ink design, processing, and device engineering. Appl. Phys. Lett.121, 220502 (2022). [Google Scholar]

- 18.Kamiya, T. & Hosono, H. Material characteristics and applications of transparent amorphous oxide semiconductors. NPG Asia Mater.2, 15–22 (2010). [Google Scholar]

- 19.Lee, D. H., Chang, Y. J., Herman, G. S. & Chang, C. H. A general route to printable high‐mobility transparent amorphous oxide semiconductors. Adv. Mater.19, 843–847 (2007). [Google Scholar]

- 20.Kim, M.-G. et al. High-performance solution-processed amorphous zinc− indium−tin oxide thin-film transistors. J. Am. Chem. Soc.132, 10352–10364 (2010). [DOI] [PubMed] [Google Scholar]

- 21.Han, S.-Y., Herman, G. S. & Chang, C.-h Low-temperature, high-performance, solution-processed indium oxide thin-film transistors. J. Am. Chem. Soc.133, 5166–5169 (2011). [DOI] [PubMed] [Google Scholar]

- 22.Kim, M.-G., Kanatzidis, M. G., Facchetti, A. & Marks, T. J. Low-temperature fabrication of high-performance metal oxide thin-film electronics via combustion processing. Nat. Mater.10, 382–388 (2011). [DOI] [PubMed] [Google Scholar]

- 23.Banger, K. et al. Low-temperature, high-performance solution-processed metal oxide thin-film transistors formed by a ‘sol–gel on chip’process. Nat. Mater.10, 45–50 (2011). [DOI] [PubMed] [Google Scholar]

- 24.Rim, Y. S. et al. Boost up mobility of solution‐processed metal oxide thin‐film transistors via confining structure on electron pathways. Adv. Mater.26, 4273–4278 (2014). [DOI] [PubMed] [Google Scholar]

- 25.Xu, W., Li, H., Xu, J.-B. & Wang, L. Recent advances of solution-processed metal oxide thin-film transistors. ACS Appl. Mater. Interfaces10, 25878–25901 (2018). [DOI] [PubMed] [Google Scholar]

- 26.Thomas, S. R., Pattanasattayavong, P. & Anthopoulos, T. D. Solution-processable metal oxide semiconductors for thin-film transistor applications. Chem. Soc. Rev.42, 6910–6923 (2013). [DOI] [PubMed] [Google Scholar]

- 27.Lorenz, M., Woods, J. & Gambino, R. Some electrical properties of the semiconductor β-Ga2O3. J. Phys. Chem. Solids28, 403–404 (1967). [Google Scholar]

- 28.Ma, N. et al. Intrinsic electron mobility limits in β- Ga2O3. Appl. Phys. Lett.109, 212101 (2016). [Google Scholar]

- 29.Oishi, T., Koga, Y., Harada, K. & Kasu, M. High-mobility β- Ga2O3 single crystals grown by edge-defined film-fed growth method and their Schottky barrier diodes with Ni contact. Appl. Phys. Express8, 031101 (2015). [Google Scholar]

- 30.Tsao, J. et al. Ultrawide‐bandgap semiconductors: research opportunities and challenges. Adv. Electron. Mater.4, 1600501 (2018). [Google Scholar]

- 31.Tippins, H. Optical absorption and photoconductivity in the band edge of β- Ga2O3. Phys. Rev.140, A316 (1965). [Google Scholar]

- 32.Orita, M., Ohta, H., Hirano, M. & Hosono, H. Deep-ultraviolet transparent conductive β-Ga2O3 thin films. Appl. Phys. Lett.77, 4166–4168 (2000). [Google Scholar]

- 33.Pearton, S. et al. A review of Ga2O3 materials, processing, and devices. Appl. Physics Rev.5, 011301 (2018). [Google Scholar]

- 34.Higashiwaki, M. et al. Depletion-mode Ga2O3 metal-oxide-semiconductor field-effect transistors on β Ga2O3 (010) substrates and temperature dependence of their device characteristics. Appl. Phys. Lett.103, 123511 (2013). [Google Scholar]

- 35.Wong, M. H., Sasaki, K., Kuramata, A., Yamakoshi, S. & Higashiwaki, M. Field-plated Ga2O3 MOSFETs with a breakdown voltage of over 750 V. IEEE Electron Device Lett.37, 212–215 (2015). [Google Scholar]

- 36.Lei, D., Han, K., Wu, Y., Liu, Z. & Gong, X. Investigation on temperature dependent DC characteristics of gallium oxide metal-oxide-semiconductor field-effect transistors from 25 °C to 300 °C. Appl. Phys. Express12, 041001 (2019). [Google Scholar]

- 37.Higashiwaki, M., Sasaki, K., Kuramata, A., Masui, T. & Yamakoshi, S. Gallium oxide (Ga2O3) metal-semiconductor field-effect transistors on single-crystal β- Ga2O3 (010) substrates. Appl. Phys. Lett.100, 013504 (2012). [Google Scholar]

- 38.Chabak, K. D. et al. Enhancement-mode Ga2O3 wrap-gate fin field-effect transistors on native (100) β-Ga2O3 substrate with high breakdown voltage. Appl. Phys. Lett.109, 213501 (2016). [Google Scholar]

- 39.Hwang, W. S. et al. High-voltage field effect transistors with wide-bandgap β- Ga2O3 nanomembranes. Appl. Phys. Lett.104, 203111 (2014). [Google Scholar]

- 40.Zhou, H., Maize, K., Qiu, G., Shakouri, A. & Ye, P. D. β-Ga2O3 on insulator field-effect transistors with drain currents exceeding 1.5 A/mm and their self-heating effect. Appl. Phys. Lett.111, 092102 (2017). [Google Scholar]

- 41.Zhou, H. et al. High-performance depletion/enhancement-mode β-Ga2O3 on insulator (GOOI) field-effect transistors with record drain currents of 600/450 mA/mm. IEEE Electron Device Lett. 38, 103–106 (2016). [Google Scholar]

- 42.Thomas, S. R. et al. High electron mobility thin-film transistors based on Ga2O3 grown by atmospheric ultrasonic spray pyrolysis at low temperatures. Appl. Phys. Lett.105, 092105 (2014). [Google Scholar]

- 43.Kim, J. et al. Conversion of an ultra-wide bandgap amorphous oxide insulator to a semiconductor. NPG Asia Mater.9, e359 (2017). [Google Scholar]

- 44.Yoon, Y., Kim, M. J., Cho, B. J., Shin, M. & Hwang, W. S. An 8-nm-thick Sn-doped polycrystalline β- Ga2O3 MOSFET with a “normally off” operation. Appl. Phys. Lett.119, 122103 (2021). [Google Scholar]

- 45.Purnawati, D., Bermundo, J. P. & Uraoka, Y. Insulator-to-semiconductor conversion of solution-processed ultra-wide bandgap amorphous gallium oxide via hydrogen annealing. Appl. Phys. Express15, 024003 (2022). [Google Scholar]

- 46.Hamlin, A. B., Ye, Y., Huddy, J. E., Rahman, M. S. & Scheideler, W. J. 2D transistors rapidly printed from the crystalline oxide skin of molten indium. npj 2D Mater. Appl.6, 16 (2022). [Google Scholar]

- 47.Zhang, J., Shi, J., Qi, D.-C., Chen, L. & Zhang, K. H. Recent progress on the electronic structure, defect, and doping properties of Ga2O3. APL Mater.8, 020906 (2020). [Google Scholar]

- 48.Roy, R., Hill, V. G. & Osborn, E. F. Polymorphism of Ga2O3 and the System Ga2O3—H2O. J. Am. Chem. Soc.74, 719–722 (1952). [Google Scholar]

- 49.Matsuzaki, K. et al. Field-induced current modulation in epitaxial film of deep-ultraviolet transparent oxide semiconductor Ga2O3. Appl. Phys. Lett.88, 092106 (2006). [Google Scholar]

- 50.Gaskell, D. R. & Laughlin, D. E. Introduction to the Thermodynamics of Materials (CRC Press, 2017).

- 51.Adrjanowicz, K., Grzybowski, A., Grzybowska, K., Pionteck, J. & Paluch, M. Effect of high pressure on crystallization kinetics of van der Waals liquid: an experimental and theoretical study. Crystal Growth Design14, 2097–2104 (2014). [Google Scholar]

- 52.Zavabeti, A. et al. A liquid metal reaction environment for the room-temperature synthesis of atomically thin metal oxides. Science358, 332–335 (2017). [DOI] [PubMed] [Google Scholar]

- 53.Datta, R. S. et al. Flexible two-dimensional indium tin oxide fabricated using a liquid metal printing technique. Nat. Electron.3, 51–58 (2020). [Google Scholar]

- 54.Zavabeti, A. et al. High-mobility p-type semiconducting two-dimensional β-TeO2. Nat. Electron.4, 277–283 (2021). [Google Scholar]

- 55.Huang, C.-H., Tang, Y., Yang, T.-Y., Chueh, Y.-L. & Nomura, K. Atomically thin tin monoxide-based p-channel thin-film transistor and a low-power complementary inverter. ACS Appl. Mater. Interfaces13, 52783–52792 (2021). [DOI] [PubMed] [Google Scholar]

- 56.Oshima, T. et al. Formation of indium–tin oxide ohmic contacts for β-Ga2O3. Jpn. J. Appl. Phys.55, 1202B1207 (2016). [Google Scholar]

- 57.Carey, P. H., IV. et al. Improvement of Ohmic contacts on Ga2O3 through use of ITO-interlayers. J. Vac. Sci. Technol. B35, 061201 (2017).

- 58.Hosono, H. & Kumomi, H. Amorphous Oxide Semiconductors: IGZO and Related Materials for Display and Memory (John Wiley & Sons, 2022).

- 59.Kim, T. et al. Progress, challenges, and opportunities in oxide semiconductor devices: a key building block for applications ranging from display backplanes to 3D integrated semiconductor chips. Adv. Mater.35, 2204663 (2023). [DOI] [PubMed] [Google Scholar]

- 60.Lee, S. & Nathan, A. Subthreshold Schottky-barrier thin-film transistors with ultralow power and high intrinsic gain. Science354, 302–304 (2016). [DOI] [PubMed] [Google Scholar]

- 61.Jiang, C. et al. Printed subthreshold organic transistors operating at high gain and ultralow power. Science363, 719–723 (2019). [DOI] [PubMed] [Google Scholar]

- 62.Wang, G. et al. New opportunities for high-performance source-gated transistors using unconventional materials. Adv. Sci.8, 2101473 (2021). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 63.Wurdack, M. et al. Ultrathin Ga2O3 glass: a large‐scale passivation and protection material for monolayer WS2. Adv. Mater.33, 2005732 (2021). [DOI] [PubMed] [Google Scholar]

- 64.Li, J. et al. Template approach to large-area non-layered Ga-group two-dimensional crystals from printed skin of liquid gallium. Chem. Mater.33, 4568–4577 (2021). [Google Scholar]

- 65.Ye, Y., Hamlin, A. B., Huddy, J. E., Rahman, M. S. & Scheideler, W. J. Continuous liquid metal printed 2D transparent conductive oxide superlattices. Adv. Funct. Mater.32, 2204235 (2022). [Google Scholar]

- 66.Battu, A. K. & Ramana, C. V. Mechanical properties of nanocrystalline and amorphous gallium oxide thin films. Adv. Eng. Mater.20, 1701033 (2018). [Google Scholar]

- 67.Li, Q. et al. Gas-mediated liquid metal printing toward large-scale 2D semiconductors and ultraviolet photodetector. npj 2D Mater. Appl.5, 36 (2021). [Google Scholar]

- 68.Kim, D., Lee, B., Thomopoulos, S. & Jun, Y.-S. The role of confined collagen geometry in decreasing nucleation energy barriers to intrafibrillar mineralization. Nat. Commun.9, 1–9 (2018). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 69.Meldrum, F. C. & O’Shaughnessy, C. Crystallization in confinement. Adv. Mater.32, 2001068 (2020). [DOI] [PubMed] [Google Scholar]

- 70.Mastandrea, J. P., Ager, J. W., III & Chrzan, D. C. Nucleation of melting and solidification in confined high aspect ratio thin films. J. Appl. Phys. 122, 105304 (2017).

- 71.Takagi, M. The thickness dependence of the phase transition temperature in thin solid films. J. Phys. Soc. Jpn.55, 3484–3487 (1986). [Google Scholar]

- 72.Zhou, X. et al. Heterogeneous nucleation of Al melt in symmetrical or asymmetrical confined nanoslits. Nanoscale8, 12339–12346 (2016). [DOI] [PubMed] [Google Scholar]

- 73.Wang, W. et al. Effect of pressure on nucleation and growth in the Zr46.75 Ti8.25 Cu7.5 Ni10 Be27.5 bulk glass-forming alloy investigated using in situ X-ray diffraction. Phys. Rev. B68, 184105 (2003). [Google Scholar]

- 74.Zhang, Y., Huang, C. -H. & Nomura, K. High-mobility wide bandgap amorphous gallium oxide thin-film transistors for NMOS inverters. Appl. Phys. Rev.11, 011418 (2024).

- 75.Geller, S. Crystal structure of β‐Ga2O3. J. Chem. Phys.33, 676–684 (1960). [Google Scholar]

- 76.Åhman, J., Svensson, G. & Albertsson, J. A reinvestigation of β-gallium oxide. Acta Crystallogr. Sect. C Cryst. Struct. Commun.52, 1336–1338 (1996). [Google Scholar]

- 77.Poncé, S. & Giustino, F. Structural, electronic, elastic, power, and transport properties of β−Ga2O3 from first principles. Phys. Rev. Res.2, 033102 (2020). [Google Scholar]

- 78.Xing, K. et al. Hydrogen-terminated diamond MOSFETs using ultrathin glassy Ga2O3 dielectric formed by low-temperature liquid metal printing method. ACS Appl. Electron. Mater.4, 2272–2280 (2022). [Google Scholar]

- 79.Kochat, V. et al. Atomically thin gallium layers from solid-melt exfoliation. Sci. Adv.4, e1701373 (2018). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 80.Wundrack, S. et al. Liquid metal intercalation of epitaxial graphene: large-area gallenene layer fabrication through gallium self-propagation at ambient conditions. Phys. Rev. Mater.5, 024006 (2021). [Google Scholar]

- 81.Hsieh, H. -H., Kamiya, T., Nomura, K., Hosono, H. & Wu, C. -C. Modeling of amorphous InGaZnO4 thin film transistors and their subgap density of states. Appl. Phys. Lett. 92, 133503 (2008).

- 82.Korhonen, E. et al. Electrical compensation by Ga vacancies in Ga2O3 thin films. Appl. Phys. Lett. 106, 242103 (2015).

- 83.Varley, J. B., Peelaers, H., Janotti, A. & Van de Walle, C. G. Hydrogenated cation vacancies in semiconducting oxides. J. Phys. Condens. Matter23, 334212 (2011). [DOI] [PubMed] [Google Scholar]

- 84.Nayak, P. K., Wang, Z. & Alshareef, H. N. Indium-free fully transparent electronics deposited entirely by atomic layer deposition. Adv. Mater.28, 7736–7744 (2016). [DOI] [PubMed] [Google Scholar]

- 85.Feng, Z. et al. Fluorination-enabled monolithic integration of enhancement- and depletion-mode indium-gallium-zinc oxide TFTs. IEEE Electron Device Lett.39, 692–695 (2018). [Google Scholar]

- 86.Chang, H., Huang, C.-H. & Nomura, K. Low-temperature solution-processed n-channel SnO2 thin-film transistors and high-gain zero-VGS-load inverter. ACS Appl. Electron. Mater.3, 4943–4949 (2021). [Google Scholar]

- 87.Min, W. K. et al. Switching enhancement via a back-channel phase-controlling layer for p-type copper oxide thin-film transistors. ACS Appl. Mater. Interfaces12, 24929–24939 (2020). [DOI] [PubMed] [Google Scholar]

- 88.Chang, H., Huang, C.-H., Matsuzaki, K. & Nomura, K. Back-channel defect termination by sulfur for p-channel Cu2O thin-film transistors. ACS Appl. Mater. Interfaces12, 51581–51588 (2020). [DOI] [PubMed] [Google Scholar]

- 89.Li, Y. et al. Complementary integrated circuits based on n-type and p-type oxide semiconductors for applications beyond flat-panel displays. IEEE Trans. Electron Devices66, 950–956 (2019). [Google Scholar]

- 90.Joo, H. J. et al. High-gain complementary inverter based on corbino p-type tin mMonoxide and n-type indium-gallium-zinc oxide thin-film transistors. IEEE Electron Device Lett.40, 1642–1645 (2019). [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Supplementary Materials

Data Availability Statement

Relevant data supporting the key findings of this study are available within the article and the Supplementary Information file. All raw data generated during the current study are available from the corresponding authors upon request.