Abstract

Three-dimensional (3D), multi-transistor-layer, integrated circuits represent an important technological pursuit promising advantages in integration density, operation speed, and power consumption compared with 2D circuits. We report fully functional, 3D integrated complementary metal-oxide-semiconductor (CMOS) circuits based on separate interconnected layers of high-mobility n-type indium arsenide (n-InAs) and p-type germanium/silicon core/shell (p-Ge/Si) nanowire (NW) field-effect transistors (FETs). The DC voltage output (Vout) versus input (Vin) response of vertically interconnected CMOS inverters showed sharp switching at close to the ideal value of one-half the supply voltage and, moreover, exhibited substantial DC gain of ≈45. The gain and the rail-to-rail output switching are consistent with the large noise margin and minimal static power consumption of CMOS. Vertically interconnected, three-stage CMOS ring oscillators were also fabricated by using layer-1 InAs NW n-FETs and layer-2 Ge/Si NW p-FETs. Significantly, measurements of these circuits demonstrated stable, self-sustained oscillations with a maximum frequency of 108 MHz, which represents the highest-frequency integrated circuit based on chemically synthesized nanoscale materials. These results highlight the flexibility of bottom-up assembly of distinct nanoscale materials and suggest substantial promise for 3D integrated circuits.

Keywords: 3D, integrated circuits, multilayer assembly, nanoelectronics

Integration of transistors into a single layer is currently the dominant implementation of integrated circuits in electronics. Three-dimensional integrated circuits consisting of multiple transistor layers can, however, offer significant performance advantages, including larger integration density, faster operation speed, and lower power consumption. These benefits have motivated substantial research in the electronics community to realize 3D integrated circuits (1, 2). While these efforts have been based mainly on conventional top-down approaches (1, 2), chemically synthesized semiconductor nanowires (NWs) (3–5) and carbon nanotubes (CNTs) (6–8) offer an attractive alternative approach to construct 3D integrated circuits. Specifically, these nanoscale building blocks can be assembled layer-by-layer into 3D structures, where sequential layers can readily be formed with the same or distinct nanomaterials (9, 10), a capability that is difficult to achieve by conventional top-down approaches (11). In the case of NWs, facile combination of distinct nanoscale materials (12, 13) with widely tunable nanoscale compositions and structures (14, 15) might enable 3D integrated circuits with unique capabilities.

To date, two reports (9, 10) have investigated 3D integration of nanoscale materials. This work has shown that sequential printing of NWs, nanoribbons, and/or CNTs is a viable approach for constructing 3D integrated circuits on conventional and plastic substrates. In addition, complementary metal-oxide-semiconductor (CMOS) configuration was also attained (9). Although these reports represent key steps toward 3D integrated NW and CNT circuits, they fall short of demonstrating features central to CMOS integrated circuits, including (i) control of switching thresholds, (ii) realization of full-swing operation for CMOS devices, and (iii) AC operation at high speed. In this work, we address these central issues through the fabrication and demonstration of functional 3D integrated NW CMOS inverter logic gates and high-frequency ring oscillators.

We use layer-by-layer assembly of indium arsenide (InAs) NW n-type field-effect transistors (n-FETs) (16–18) and germanium/silicon (Ge/Si) core/shell NW p-type FETs (p-FETs) (14, 19, 20) to fabricate vertically interconnected, 3D CMOS inverters and ring oscillators. The choice of a group-III/V material and group-IV heterostructure was motivated by the high-performance demonstrated previously for the corresponding NW FETs (18, 20), the desire to determine whether such distinct materials systems could indeed yield functional circuits through a bottom-up approach, and the corresponding current interest in hetero-integration of these two systems by conventional top-down fabrication to extend scaling in microelectronics (21).

Results and Discussion

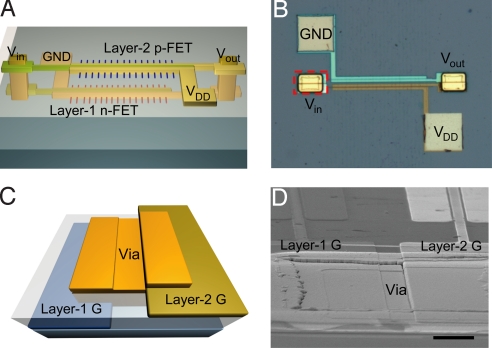

We explored our approach first for vertically interconnected, 3D CMOS inverter logic gates, where InAs NW n-FETs and Ge/Si NW p-FETs were used in the first and second layers, respectively (Fig. 1A). Key steps in the fabrication are as follows (see Materials and Methods). First, the lower layer of InAs NW n-FETs are fabricated by sequential steps of NW contact printing, source/drain (S/D) deposition, atomic layer deposition (ALD) of high-κ dielectric, and top-gate (G) deposition. Second, a low-κ dielectric was deposited to electrically isolate the initial NW FET layer, and then the same steps of NW deposition and fabrication were repeated to define the second layer of NW FETs. p-Ge/Si NWs were used in the second layer. Third, interconnections between NW n-FETs in layer-1 and NW p-FETs in layer-2 were made by combining via dry-etching and metal deposition (see Materials and Methods), in order to form a CMOS inverter.

Fig. 1.

The 3D CMOS circuit and vertical interconnection. (A) Schematic of a two-layer CMOS inverter circuit. Layer-1 and layer-2 are constructed with complementary n-type InAs NWs and p-type Ge/Si core/shell NWs, and vertical interconnections are achieved at the two gate electrodes (input) and the two drain electrodes (output). GND denotes electrical ground. (B) Optical microscope image of vertically interconnected CMOS inverter. Red dashed box indicates via interconnection at the input of CMOS inverter. (C) Side tilted-view schematic drawing (rotated 90° counterclockwise of red dashed box in B) of via interconnection at the input of CMOS inverter. (D) Tilted-view SEM image (rotated 90° counterclockwise of red dashed box in B) of via interconnection at the input of CMOS inverter. (Scale bar: 5 μm.)

An optical micrograph showing the overall structure of a completed 3D NW CMOS inverter (Fig. 1B) shows (i) light-blue first-level and brown second-level NW FET S/D electrodes and (ii) the well-defined interconnections at gate and drain electrodes of FETs in the two layers. A schematic structure of the vertical interconnection between the layer-1 and layer-2 gate electrodes (Fig. 1C) highlights our surface contact strategy for making the vertical interconnection of the non-overlapping gates in the two layers (see Materials and Methods). A scanning electron microscopy (SEM) image of the interconnect region (Fig. 1D) confirms structurally the successful alignment and contact of the two layers.

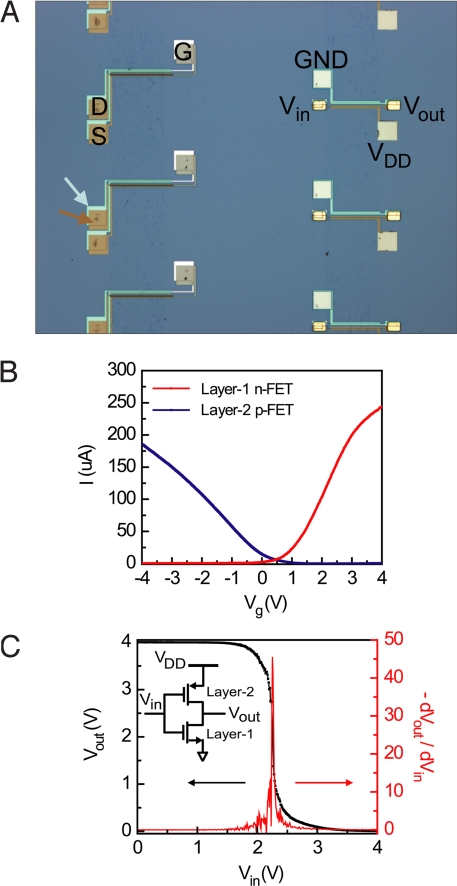

An optical micrograph of a region of a typical 3D NW CMOS chip (Fig. 2A) shows both isolated n- and p-FETs (Fig. 2A, left column) and inverter logic gates (Fig. 2A, right column). The isolated NW FETs were used to characterize sequentially during fabrication the properties of InAs NW n-FETs and then Ge/Si NW p-FETs. Representative transfer characteristics of layer-1 InAs NW n-FETs and layer-2 Ge/Si NW p-FETs (Fig. 2B) show that the n- and p-FETs have similar current levels, with values of 23 and 15 μA, respectively, where |Vgs| = 1 V and |Vds| = 1 V (see Figs. S1 and S2 full device characterization data). We note that the current levels can be readily adjusted by varying the average number of NWs/FET deposited during the printing/deposition step. Furthermore, the intersection point of the two I–Vg transfer curves, ≈0.5 V, corresponds to the ideal value of VDD/2, where VDD = 1 V is the supply voltage for both FETs (22). DC characterization of the Vout versus Vin response for a corresponding vertically interconnected CMOS inverter for VDD = 4 V (Fig. 2C) shows a sharp switching at ≈2.2 V, near the ideal value of VDD/2. The derivative of the data shows a substantial DC gain of ≈45. This gain and the rail-to-rail output switching are consistent with the large noise margin and minimal static power consumption, key characteristics of CMOS (22).

Fig. 2.

Vertically interconnected CMOS inverter. (A) Optical microscope image of isolated n-InAs and p-Ge/Si NW FETs (left column), and two-layer interconnected CMOS inverters (right column). The n-InAs NW FETs were fabricated in layer-1 (light-blue contrast and arrow), and the p-Ge/Si NW FETs were fabricated in layer-2 (light-brown contrast and arrow). (B) I vs. Vg characteristics data recorded from representative InAs layer-1 and Ge/Si layer-2 NW devices with |Vds| = 1 V. The data from the InAs NW FET were recorded before fabrication of the layer-2. (C) Vout vs. Vin (black curve) and gain = dVout/dVin vs. Vin (red curve) for a CMOS inverter at supply voltage, VDD, of 4 V. (Inset) Circuit diagram for the vertically interconnected two-layer CMOS inverter.

This representative result from the 3D CMOS inverters is a significant improvement over the corresponding 3D but pMOS-only inverter, consisting of a p-Ge/Si NW switching FET (layer-1) and a p-Ge/Si NW load FET (layer-2) (Fig. S3), which was constructed for comparison. The pMOS-only inverter has a DC gain of only ≈8 and a nonideal switching threshold of ≈3 V at supply voltage of 4 V. Notably, the nearly ideal behavior, achieved for the 3D CMOS NW inverter, suggests that our bottom-up vertical interconnection approach of high-performance III-V InAs NW n-FET and IV Ge/Si NW p-FETs can be used to realize more complex CMOS integrated circuits.

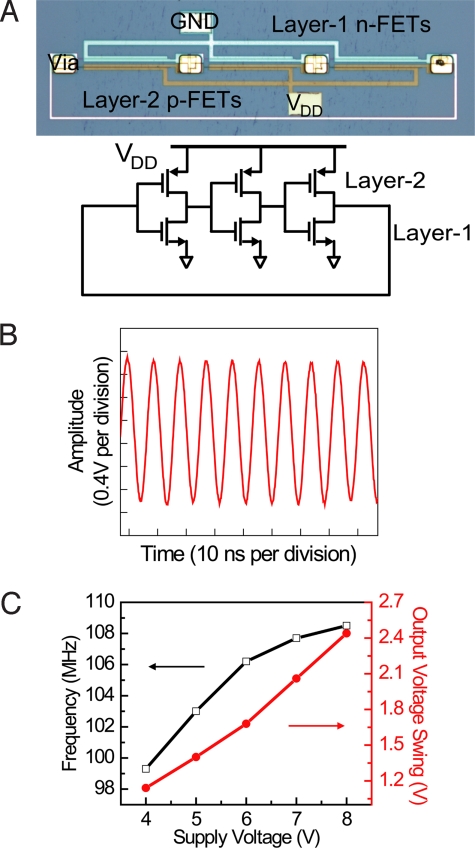

To demonstrate the potential to extend our approach to more complex vertically interconnected, 3D CMOS circuits, we have also fabricated two-layer, three-stage CMOS ring oscillators. An optical micrograph and circuit schematic (Fig. 3A) highlight the three CMOS inverters serially connected in a closed, positive feedback loop, with each inverter consisting of a layer-1 InAs NW n-FET and a layer-2 Ge/Si NW p-FET, which are vertically interconnected. Significantly, measurement of the output signal with a high impedance probe (see Materials and Methods) demonstrates stable, self-sustained oscillations with a maximum frequency of 108 MHz for VDD = 8 V, as shown in Fig. 3B. This oscillation frequency corresponds to a propagation delay of 1.54 ns per stage and is nearly an order of magnitude improvement from the pMOS-only ring oscillator (≈12 MHz; Fig. S4), which we fabricated for comparison. The substantially higher oscillation frequency or decreased inverter delay is due to the larger current-driving capability of the CMOS inverter, in comparison to the pMOS-only inverter. In addition, a higher range of oscillation frequencies, 330–490 MHz, was estimated for our 3D CMOS ring oscillator based on an inverter propagation delay calculation (see SI Text). This analysis suggests that parasitic components of the circuit may be major sources of delay in our experimental results, although future studies focused on detailed circuit simulations may provide further insights on how to improve the performance of our 3D NW-based circuits. Last, our measurements demonstrate that the oscillation frequency and output voltage swing increase with supply voltage (Fig. 3C), showing that these vertically interconnected NW circuits behave as expected for conventional oscillator circuit (22). It is also important to note that the yield of vertically interconnected NW ring oscillators was 80%; of 28 circuits fabricated and tested, 23 were functional. We believe that this represents an important achievement in comparison to previous studies of electronic devices and circuits based on synthesized nanostructures.

Fig. 3.

Vertically integrated CMOS ring oscillator. (A) Optical micrograph and circuit diagram of two-layer, vertically interconnected three-stage CMOS ring oscillator. The layer-1 n-InAs and layer-2 p-Ge/Si NW FETs exhibit light-blue and brown contrast in the image. (B) Amplitude vs. time response recorded at via position by using a high-impedance probe (see Materials and Methods). The supply voltage, VDD, is 8 V, and the self-sustained oscillation frequency is 108 MHz. (C) Oscillation frequency (black curve) and output voltage swing (red curve) vs. supply voltage (VDD) characteristics of the vertically interconnected three-stage CMOS ring oscillator.

These results can be compared to the two previous studies (9, 10) of 3D integrated circuits using nanomaterials. The work in ref. 10 demonstrated layer-by-layer assembly of NW p-FETs, but neither vertical interconnection nor CMOS configuration was achieved. In an important advance, Rogers and coworkers (9) first demonstrated a 3D CMOS inverter based on vertically interconnected n-type Si micrometer-scale ribbon and p-type network single-walled nanotube FET device layers (9). However, these initial studies also had limitations, including nonideal switching, which precludes achieving full advantage of CMOS operation, and substantially lower gain (≈8) than we achieved by using matched high-performance p-Ge/Si and n-InAs NW FETs. In addition, circuits more complex than inverters were not constructed, and AC operation capability, which is essential in almost all practical applications and represents a key advance of the present ring oscillators, was not demonstrated.

In addition, we can compare the high-frequency ring-oscillator performance to previous, less-demanding 2D structures. In particular, work on single CNT-based CMOS ring oscillators (23, 24) achieved, before our work, the highest oscillation frequency, ≈72 MHz, for nanomaterial-based integrated circuits. However, the ambipolar nature of the CNT FETs used to configure inverter elements could cause relatively large leakage currents and nonideal noise margins compared to our NW CMOS inverter units, making fabrication of more complex high-performance circuits increasingly difficult. More importantly, we believe that 3D integration demonstrated in present work represents a key advance for exploring interesting and unique high-performance nanomaterial-based CMOS circuits for the future.

Conclusions

We have demonstrated fully functional 3D CMOS NW integrated circuits based on sequential layer-by-layer assembly of chemically synthesized high-performance NW building blocks followed by interconnection of layers to define final circuits. More specifically, we have used interconnected layer-1 InAs NW n-FETs and layer-2 Ge/Si NW p-FETs to demonstrate 3D CMOS inverters with well-controlled switching thresholds and DC gains up to 45, as well as 3D CMOS ring oscillators with oscillation frequencies up to ≈110 MHz. Our 3D ring oscillator represents the highest-frequency integrated circuit reported for nanoscale materials, and we believe this frequency could be further increased by reducing channel length and parasitic resistance and capacitance of the circuit. More generally, we believe that our bottom-up approach using optimized n- and p-type NW materials suggests substantial promise for several directions, including (i) extension to multiple interconnected layers both for increasing device packing density (1, 2) and to open up design and testing of novel circuit architectures (1, 2), (ii) implementation of 3D interconnected NW circuits on flexible (25–28) and highly curved substrates (29) for high-performance electronics on unconventional substrates, and (iii) exploring general concept of heterogeneous 3D integration of two or more NW and carbon nanotube building blocks for 3D multi-functional nanosystems (11).

Materials and Methods

Synthesis of Ge/Si and InAs NWs.

Epitaxial core/shell Ge/Si NW heterostructures were prepared by the nanocluster catalyzed vapor–liquid–solid (VLS) growth process by using germane and silane reactants as described previously (19). A core diameter of ≈10 nm and a uniform shell thickness of ≈2 nm were used. InAs NWs were grown by the nanocluster catalyzed VLS method using thermal evaporation and transport in a two-zone tube furnace to deliver precursors. Briefly, several grams of InAs powder (99.9999%; Alfa Aesar) was placed in zone I (upstream), and a Si/SiO2 substrate with dispersed 10 nm gold nanoparticles (Ted Pella) was placed 20 cm downstream in zone II of the tube furnace. Temperatures were set to 690 °C (zone I) and 530 °C (zone II), with a total pressure maintained at 2 torr in a 20 standard cubic cm per min flow of H2 gas. Single-crystalline InAs NWs with diameters of ≈20 nm were obtained after 40 min of growth. Independent tuning of source and substrate temperature together with pressure and gas flow were found to be important for realizing controlled synthesis of uniform InAs NWs with improved off-current levels and subthreshold slopes (18).

Contact Printing of NWs.

NWs were transferred from growth substrates to patterned device substrates by a shear printing process, which enables control of the density and alignment of the NWs. First, device substrates (600 nm SiO2 on intrinsic Si) were patterned by photolithography (Shipley S1805) to define the regions where NWs will be deposited (Fig. S5A). The average number of NWs, or NW density, was controlled by adjusting the photoresist trench width and spacing. The trench width and spacing was 4 μm for InAs NWs and 2 μm for Ge/Si NWs; the values were chosen to match the on-current levels of n- and p-type NW FETs. Second, an NW growth substrate was brought into contact with the patterned device substrate (NWs facing the device substrate). A pressure of 0.5–1 kg/cm2 was applied while the NW substrate was slid by 1–3 mm (Fig. S5B). Last, the photoresist layer on device substrate was lifted off in acetone (Fig. S5C). These procedures produced relatively low-density NW arrays: InAs ≈0.1 NW per micrometer and Ge/Si ≈0.2 NW per micrometer.

Multilayer NW Circuit Fabrication.

InAs and Ge/Si NWs were contact-printed onto Si/SiO2 (60,000–160,000 Ω·cm intrinsic Si substrate/600 nm thermal oxide; Nova Electronic Materials) substrate with patterned photoresist spacer layers (10). Ge/Si NWs were printed on the first layer of the interconnected two-layer pMOS circuit, and InAs NWs were printed on the first layer of the interconnected two-layer CMOS circuit. S/D electrodes were patterned by photolithography followed by metallization with Ni (60 nm thickness). A channel length of 1.5 μm and channel width of 200 μm were used as standard FET dimensions, with the NW density adjusted by contact printing. Buffered HF (Transene) and diluted HF (48% HF:deionized water = 1:1,000) solutions were used in ≈3 s etch of the contacts for the Ge/Si and InAs NWs, respectively, immediately before contact metal deposition. Subsequently, the top-gate high-κ dielectric HfO2 film (≈20 nm) was deposited by 150 cycles of ALD at 115 °C, with each cycle consisting of 1 s water-vapor pulse, 5 s N2 purge, 3 s tetrakis(dimethylamino)hafnium [Hf(N(CH3)2)4] pulse, and 5 s N2 purge steps. Cr/Au (5 nm/55 nm) and Ti (100 nm) top-gate metals were evaporated for InAs n-FETs and Ge/Si p-FETs, respectively.

After fabrication of first-layer devices, a SiO2/HfO2 (300/20 nm) bilayer was deposited to electrically isolate the second device layers, where the HfO2 layer served as a convenient barrier for the contact etching step. The second-layer FET fabrication followed steps similar to the first layer: contact-printing Ge/Si NWs, S/D and top-gate fabrication steps. Practically, the second layer devices were offset by 20 μm to avoid any roughness from first-layer fabrication, although we note that standard surface planarization techniques (30) could eliminate this roughness and eliminate the need for the small offset. Last, the upper and lower layers were interconnected. Via holes were formed by removing oxide layers by CF4 reactive ion etching dry-etching process with a double-layer LOR3A/S1813 photoresist as an etch mask, and Cr/Au was then deposited by sputtering to achieve electrical interconnection. We used a surface-contact strategy by designing non-overlapping metal electrodes at via interconnection points (Fig. S6).

Device Measurements.

Measurements were conducted with a probe station (model 12561B; Cascade Microtech) and a semiconductor parameter analyzer (model 4156C; Agilent). Inverter DC measurements were carried out by using a computer-controlled analogue-to-digital converter (model 6030E; National Instruments). Ring-oscillator output voltage was monitored by an oscilloscope (model TDS3012; Tektronix) using a 10 MΩ impedance FET probe (model 34A; Picoprobe), with DC bias voltage applied to the circuit. A bias tee (MiniCircuits) was used between the oscilloscope and high-impedance probe to monitor only high-frequency signals from the ring-oscillator circuit. The 20:1 signal reduction intrinsic to the probe was compensated for in the data presented in Fig. 3 and Fig. S4.

Supplementary Material

Acknowledgments.

This study was supported by Samsung Scholarship, Samsung Foundation of Culture (S.N.), and a contract from MITRE Corporation and the Defense Advanced Research Projects Agency (C.M.L.).

Footnotes

The authors declare no conflict of interest.

This article contains supporting information online at www.pnas.org/cgi/content/full/0911713106/DCSupplemental.

References

- 1.Topol AW, et al. Three-dimensional integrated circuits. IBM J Res Dev. 2006;50:491–506. [Google Scholar]

- 2.Das S, Chandrakasan A, Reif R. Three-dimensional integrated circuits: Performance, design methodology, and CAD tools. Proc IEEE Comput Soc Annu Symp VLSI. 2003;2003:13–18. [Google Scholar]

- 3.Lieber CM. Nanoscale science and technology: Building a big future from small things. MRS Bull. 2003;28:486–491. [Google Scholar]

- 4.Lieber CM, Wang ZL. Functional nanowires. MRS Bull. 2007;32:99–104. [Google Scholar]

- 5.Thelander C, et al. Nanowire-based one-dimensional electronics. Mater Today. 2006;9:28–35. [Google Scholar]

- 6.McEuen PL, Fuhrer MS, Park H. Single-walled carbon nanotube electronics. IEEE Trans Nanotech. 2002;1:78–85. [Google Scholar]

- 7.Avouris P, Chen J. Nanotube electronics and optoelectronics. Mater Today. 2006;9:46–54. [Google Scholar]

- 8.Javey A, Guo J, Wang Q, Lundstrom M, Dai H. Ballistic carbon nanotube field-effect transistors. Nature. 2003;424:654–657. doi: 10.1038/nature01797. [DOI] [PubMed] [Google Scholar]

- 9.Ahn JH, et al. Heterogeneous three-dimensional electronics by use of printed semiconductor nanomaterials. Science. 2006;314:1754–1757. doi: 10.1126/science.1132394. [DOI] [PubMed] [Google Scholar]

- 10.Javey A, Nam S, Friedman RS, Yan H, Lieber CM. Layer-by-layer assembly of nanowires for three-dimensional, multifunctional electronics. Nano Lett. 2007;7:773–777. doi: 10.1021/nl063056l. [DOI] [PubMed] [Google Scholar]

- 11.Lu W, Lieber CM. Nanoelectronics from the bottom up. Nat Mater. 2007;6:841–850. doi: 10.1038/nmat2028. [DOI] [PubMed] [Google Scholar]

- 12.Fan Z, Ho JC, Jacobson ZA, Razavi H, Javey A. Large-scale, heterogeneous integration of nanowire arrays for image sensor circuitry. Proc Natl Acad Sci USA. 2008;105:11066–11070. doi: 10.1073/pnas.0801994105. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 13.Huang Y, Duan X, Lieber CM. Nanowires for integrated multicolor nanophotonics. Small. 2005;1:142–147. doi: 10.1002/smll.200400030. [DOI] [PubMed] [Google Scholar]

- 14.Lauhon LJ, Gudiksen MS, Wang D, Lieber CM. Epitaxial core-shell and core-multishell nanowire heterostructures. Nature. 2002;420:57–61. doi: 10.1038/nature01141. [DOI] [PubMed] [Google Scholar]

- 15.Gudiksen MS, Lauhon LJ, Wang J, Smith DC, Lieber CM. Growth of nanowire superlattice structures for nanoscale photonics and electronics. Nature. 2002;415:617–620. doi: 10.1038/415617a. [DOI] [PubMed] [Google Scholar]

- 16.Bryllert T, Wernersson LE, Froberg LE, Samuelson L. Vertical high-mobility wrap-gated InAs nanowire transistor. IEEE Electron Device Lett. 2006;27:323–325. [Google Scholar]

- 17.Dayeh SA, et al. High electron mobility InAs nanowire field-effect transistors. Small. 2007;3:326–332. doi: 10.1002/smll.200600379. [DOI] [PubMed] [Google Scholar]

- 18.Jiang X, et al. InAs/InP radial nanowire heterostructures as high electron mobility devices. Nano Lett. 2007;7:3214–3218. doi: 10.1021/nl072024a. [DOI] [PubMed] [Google Scholar]

- 19.Lu W, Xiang J, Timko BP, Wu Y, Lieber CM. One-dimensional hole gas in germanium/silicon nanowire heterostructures. Proc Natl Acad Sci USA. 2005;102:10046–10051. doi: 10.1073/pnas.0504581102. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 20.Xiang J, et al. Ge/Si nanowire heterostructures as high-performance field-effect transistors. Nature. 2006;441:489–493. doi: 10.1038/nature04796. [DOI] [PubMed] [Google Scholar]

- 21.Heyns M, Tsai W. Ultimate scaling of CMOS logic devices with Ge and III-V materials. MRS Bull. 2009;34:485–488. [Google Scholar]

- 22.Taur Y, Ning TH. Fundamentals of Modern VLSI Devices. New York: Cambridge Univ Press; 2005. [Google Scholar]

- 23.Chen Z, et al. An integrated logic circuit assembled on a single carbon nanotube. Science. 2006;311:1735–1735. doi: 10.1126/science.1122797. [DOI] [PubMed] [Google Scholar]

- 24.Avouris P, Chen Z, Perebeinos V. Carbon-based electronics. Nat Nanotech. 2007;2:605–615. doi: 10.1038/nnano.2007.300. [DOI] [PubMed] [Google Scholar]

- 25.Friedman RS, McAlpine MC, Ricketts DS, Ham D, Lieber CM. High-speed integrated nanowire circuits. Nature. 2005;434:1085–1085. doi: 10.1038/4341085a. [DOI] [PubMed] [Google Scholar]

- 26.Duan X, et al. High-performance thin-film transistors using semiconductor nanowires and nanoribbons. Nature. 2003;425:274–278. doi: 10.1038/nature01996. [DOI] [PubMed] [Google Scholar]

- 27.Duan X. Assembled semiconductor nanowire thin films for high-performance flexible macroelectronics. MRS Bull. 2007;32:134–141. [Google Scholar]

- 28.McAlpine MC, Ahmad H, Wang D, Heath JR. Highly ordered nanowire arrays on plastic substrates for ultrasensitive flexible chemical sensors. Nat Mater. 2007;6:379–384. doi: 10.1038/nmat1891. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 29.Yu G, Cao A, Lieber CM. Large-area blown bubble films of aligned nanowires and carbon nanotubes. Nat Nanotech. 2007;2:372–377. doi: 10.1038/nnano.2007.150. [DOI] [PubMed] [Google Scholar]

- 30.Plummer JD, Deal MD, Griffin PB. Silicon VLSI Technology. Upper Saddle River, NJ: Prentice Hall; 2000. [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.