Abstract

We present the first, fully-integrated, two-channel implementation of a patch-clamp measurement system. With this “PatchChip” two simultaneous whole-cell recordings can be obtained with rms noise of 8 pA in a 10 kHz bandwidth. The capacitance and series-resistance of the electrode can be compensated up to 10 pF and 100 MΩ respectively under computer control. Recordings of hERG and Nav 1.7 currents demonstrate the system's capabilities, which are on par with large, commercial patch-clamp instrumentation. By reducing patch-clamp amplifiers to a millimeter size micro-chip, this work paves the way to the realization of massively-parallel, high-throughput patch-clamp systems for drug screening and ion-channel research. The PatchChip is implemented in a 0.5 μm silicon-on-sapphire process; its size is 3 × 3 mm2 and the power consumption is 5 mW per channel with a 3.3 V power supply.

Keywords: patch clamp, amplifier, series resistance, integrated circuit, voltage clamp

1. Introduction

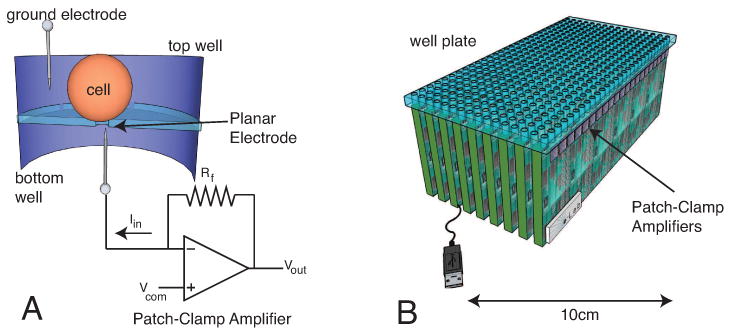

The patch-clamp amplifier is a ubiquitous tool for characterizing ion-channel activity. For the screening of pharmaceutical compounds or the characterization of expressed channels, high-throughput patch-clamp systems are being developed, where recordings are made from cells in each well of a 96 or 384-well plate. In these systems the recording is made not with a glass pipette, but from a planar electrode at the bottom of each well (Fig. 1). An important part of such highly-parallel recording systems is a high-density array of patch-clamp amplifiers. We present here a highly-miniaturized patch-clamp amplifier with complete whole-cell measurement capabilities.

Figure 1.

A - Patch-clamp amplifier performing whole-cell membrane current recording using a planar electrode. The planar electrode replaces the traditional glass micro pipette with a micron sized-aperture that is topologically equivalent to the glass tip of the pipette. Cells are introduced into a well, and when suction is applied, the cells seal into the aperture. Further suction is applied to rupture the cell so that a whole-cell configuration is established. B - Using the amplifiers presented in this paper, it is possible to design a high-throughput, automatic patch-clamp system that operates on entire 384 well plates. The wells on B are identical to the one in A. Requirements for the amplifier are millimeter-size dimensions and minimized heat dissipation, crosstalk and low fabrication cost.

Important constraints in building massively-parallel patch-clamp systems have been the size and cost of the amplifiers, heat dissipation - which restricts the proximity of the amplifiers to the cells - and crosstalk between channels. The integrated “PatchChip” amplifier presented in this paper solves all of these design requirements, and is based on experience from our prototypes [1, 2, 3, 4, 5, 6]. The dual-channel patch-clamp system occupies 3 × 3 mm2 of area and consumes just 5 mW of power per channel. It is fabricated using a standard silicon-on-sapphire fabrication process, which allows parasitic capacitances and cross-talk effects to be minimized.

2. Materials and methods

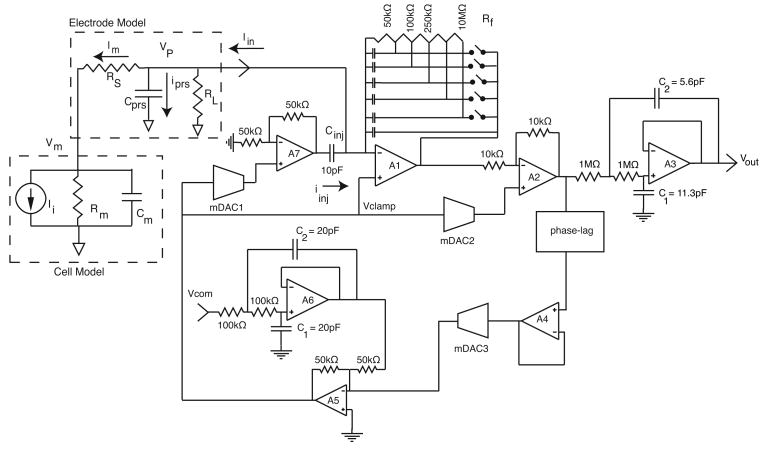

Figure 2 shows a block diagram of one channel of the PatchChip system. The two channels of the system are identical. The main signal path is from the membrane current Iin to the monitor voltage output Vout = IinRf, through operational amplifiers A1, A2, A3.

Figure 2.

One channel of the two-channel integrated patch-clamp system and the electrical model of a cell and pipette electrode. The main signal path is from the membrane current Iin to the monitor voltage output Vout = IinRf, through operational amplifiers A1, A2 and A3. Multiplying digital to analog converter mDAC 1 controls the parasitic capacitive compensation, mDAC 2 provides leak subtraction, mDAC 3 and the phase-lag controller circuit provides series resistance compensation. Input reconstruction and output anti-aliasing filters are also integrated. mDAC 1 and mDAC 2 are voltage-mode, R-2R DACs with R=50 kΩ, minimum gains of 0.5, and resolutions of 8 and 10 bits, respectively. mDAC 3 is a 9-bit hybrid transconductance-mode DAC with a maximum transconductance of 0.2 mS. Typical values of the electrode and cell elements are Cprs=5 pF, RL=100 MΩ, Rs=10 MΩ, Cm=30 pF, Rm=100 MΩ and peak values of Ii are 1-10 nA.

Cells are stimulated by controlling the voltage Vp = Vclamp at the electrode and measuring the resultant ionic current Iin. The goal of the compensation circuits is to allow step changes to be applied to the cell membrane potential Vm while the ionic current Ii is measured. The cell membrane can be modeled as a capacitance Cm in parallel with the membrane resistance Rm. The headstage of the patch-clamp recording system consists of a current-to-voltage transimpedance amplifier A1. The feedback resistor Rf is selectable in eight steps from 50 kΩ to 10MΩ. Small shunt capacitors stabilize the feedback loop while yielding a bandwidth of a minimum of 300 kHz (with Rf = 10 MΩ) when the total capacitance on the input node is 30 pF A difference amplifier A2 subtracts Vclamp from the transimpedance output. The resultant output voltage Vout is proportional to the input current, Iin.

The output filter A3 represents two poles of a three-pole, 20 kHz anti-aliasing filter. The third pole is presented by an external capacitor and is the only “glue” component required for the analog interface between the PatchChip and the external A-D converter. Similarly, the two-pole input reconstruction filter A6, critically-damped with a time constant of 2 μs, smooths the input command signal Vcom delivered directly from an external D-A converter and prevents rapid steps from causing nonlinearities and slew-limiting in the other amplifiers of the system.

2.1. Electrode compensation circuitry

The system compensates for the difference between the actual membrane voltage Vm and the clamping voltage Vclamp due to the voltage drop across the pipette electrode series resistance Rs. The circuit also compensates for the current iprs drawn by the electrode parasitic capacitance Cprs and by and by the seal leakage-resistance RL.

Rs compensation is necessary for two reasons. First, it allows accurate voltage clamping of the membrane by reducing the errors from the voltage drop across the series access resistance Rs. Second, the compensation reduces the time needed to charge Cm enabling the circuit to monitor ion-channel events occurring immediately after changes in Vcom is applied [7]. The drop across Rs is predicted by adding a fraction of Vout to the applied membrane-command potential Vcom by means of amplifier A5, to obtain Vclamp. The fraction of compensated series-resistance is determined by the 9-bit mDAC3, which at full-scale yields compensation for a resistance of 10 × Rf. mDAC3 was designed as a hybrid weighted-resistor and R-2R device to minimize the noise gain of the A5 stage. A passive phase-lag compensation circuit is included in the positive-feedback loop if desired, to improve stability when a high percentage of Rs, e.g. more than 90%, is compensated.

For effective Rs compensation the measured current must be equal to the current Im flowing through Rs. The charging current of the parasitic electrode capacitance Cprs and the current through the leakage conductance RL therefore must first be subtracted from the measurement of Iin. The capacitive-current subtraction is done by injecting a current iinj through an integrated capacitor Cinj of 10 pF. The gain αinj of the amplifier A7 is determined by the 8-bit mDAC1 to be between 1 and 2. The compensated capacitance is equal to (αinj − 1)Cinj.

The differential amplifier A2 is unbalanced when the voltage-output mDAC2 is set to a gain different from its minimum value of 0.5. As its gain increases, subtraction is provided for the excess Iin on the input. The maximum gain of the 10-bit mDAC2 is unity, allowing for compensation of a leakage resistance as high as Rf. All three compensation circuits are controlled using a serial digital control bus. A 64-bit shift register and buffer register store the bit patterns for the mDACs and various switches in one patch-clamp channel.

2.2. Voltage swings and Rf

Modern patch-clamp amplifiers contain an additional “C-Slow” compensation circuit to remove the large current transients due to the charging of the membrane capacitance Cm, which is typically in the range of 20-40 pF. These circuits have been implemented as a first-order state-variable filter [7, 8] in which the time constant is roughly 100 μs to 1 ms. Due to the limited capacitor sizes, and therefore short time constants, that can be realized in a monolithic circuit, we decided not to provide this “slow capacitance” compensation. Instead, this compensation will be provided in software. We rely on the use of a 16-bit or higher resolution A-D converter to digitize the current-monitor signal Vout so that the large charging transients can be subtracted digitally.

In the absence of slow-capacitance compensation, the entire charging current of the membrane capacitance must be injected through the feedback resistor Rf. Thus the voltage swing available at the output of amplifier A1 becomes an important issue. We have used a 3.3 volt silicon-on-sapphire (SOS) process, so that the analog power-supply voltages are ±1.6 V. Although the typical membrane-potential excursions are only in the range ±150 mV, when Rs compensation is in use the excursions of Vp can be an order of magnitude larger.

Consider the case in which a fraction k of the series resistance is compensated. When a voltage step of magnitude ΔVcom is applied to Vcom the effect of the Rs compensation feedback is to produce an initial step ΔVp = ΔVcom/(1 − k). For example, a 150 mV step with k=0.8 (80% compensation) yields an initial step of 750 mV. Even ignoring the current through RL the initial current will be Iin=ΔVp/Rs and will have to be sourced through the feedback resistor Rf. Thus the initial voltage at the output of A1 (Vout,A1) will need to be

| (1) |

If Rf is chosen to be equal to Rs in this example, the initial value of Vout,A1 must be 1.5V, very close to the available supply voltage of 1.6V. To avoid amplifier saturation therefore, two steps must be taken. First, Rf must be kept to a low value, typically 5-10 MΩ in cases where Rs is in this resistance range. Second, amplifier A1 (and also other amplifiers in the circuit) must have a rail-to-rail output swing capability. The characteristics of the operational amplifiers are described in section 2.4.

The low value of the feedback resistor Rf means that the current-monitor signal of the PatchChip will have a substantial contribution from the resistor's thermal noise; in a 10 kHz bandwidth this noise is 4 pA rms when Rf = 10MΩ. The thermal noise arising in Rs is also large, and when its value is equal to Rf, its noise is equal to that from Rf at high frequencies f > fc, where fc = 1/(2πRsCm). When Rs compensation is in use, which in effect increases the recording bandwidth beyond fc, the two resistances Rf and Rs make nearly equal contributions to the noise variance. Thus the low value of Rf does result in increased noise, but the increase is moderate, about a factor of over the theoretical minimum noise due to Rs alone.

2.3. Silicon-on-sapphire technology

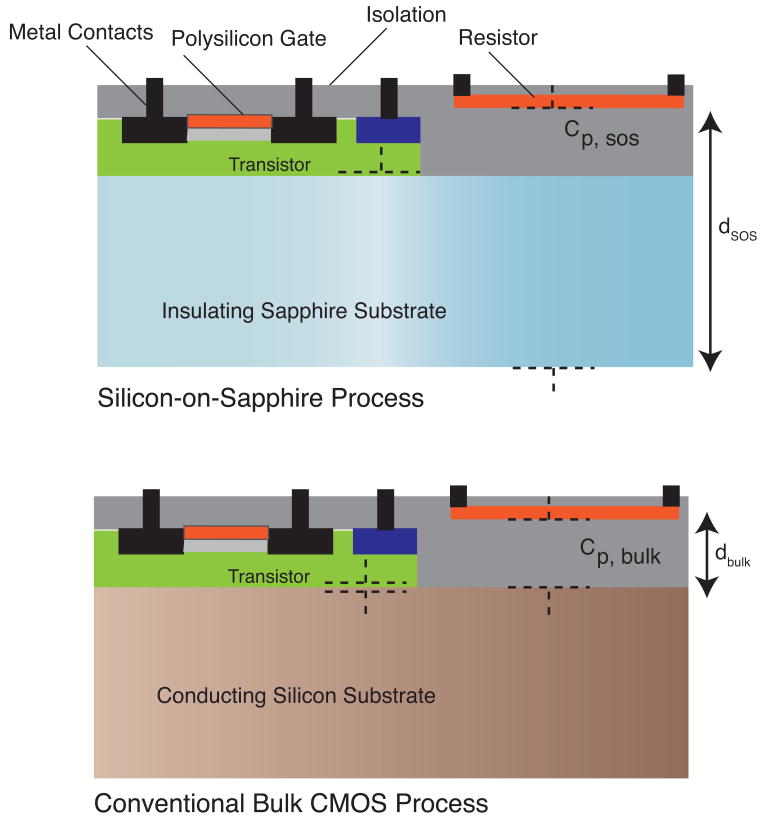

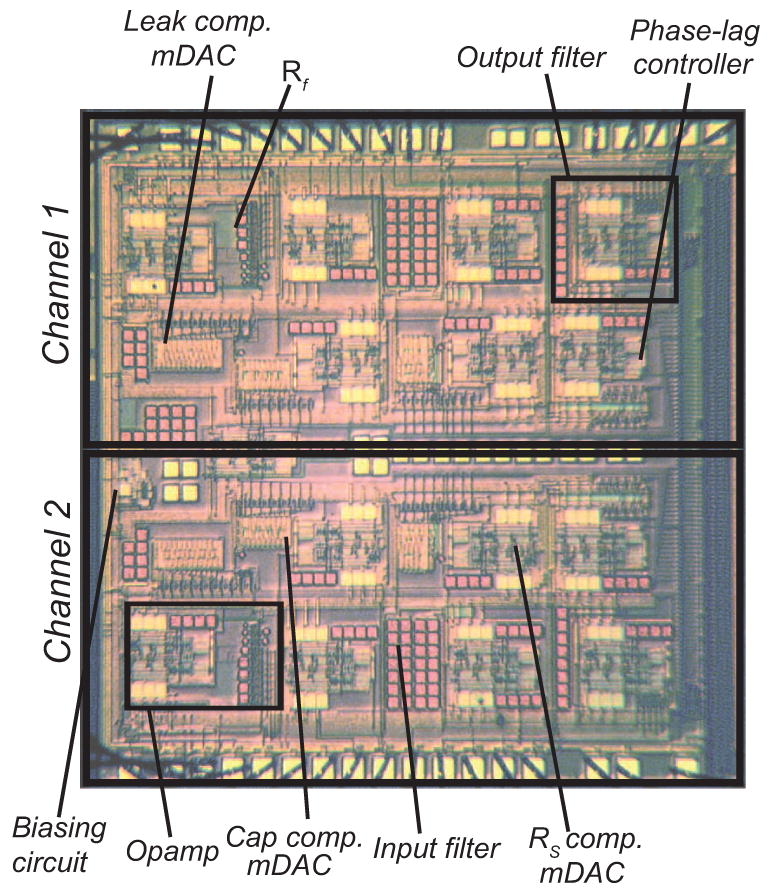

The PatchChip was implemented using the silicon-on-sapphire (SOS) technology. SOS offers several advantages over conventional bulk CMOS technology, as is illustrated in Figure 3. First, the absence of a conducting substrate greatly reduces parasitic capacitance and allows the fabrication of large, nearly-ideal resistors. In conventional bulk-CMOS processes the source and drain of each transistor is isolated from the substrate by a reverse-biased diode; these diodes contribute a considerable capacitance to each such node in the circuit. Even resistor elements, which are isolated from the bulk silicon by oxide layers, show considerable parasitic capacitance because the oxide layers are relatively thin. In SOS on the other hand, transistors and resistors are fabricated on top of the thick sapphire substrate (Figure 3) and therefore experience vastly smaller parasitic capacitances [9]. Second, the non-conducting substrate provides a better means of isolating devices on the substrate, yielding better cross-talk performance between patch-clamp channels. Third, the insulating substrate allows the power supplies for digital and analog parts of this mixed-signal circuit to be separated to obtain better noise performance. Fourth, the lower parasitic capacitance allows SOS devices to perform at faster speeds and lower power than those made using conventional bulk CMOS technology [10]. The final layout of the micro-chip implementing the two-channel patch-clamp system is shown in Figure 4. This layout is the physical implementation of the circuits reported in Figure 2.

Figure 3.

The patch-clamp system was implemented using silicon-on-sapphire (SOS) technology. The insulating substrate in SOS (top) reduces parasitic capacitance and allows fabrication of large resistors to implement Rf with no degradation in frequency response. The insulating substrate reduces crosstalk between channels and allows devices to operate at faster speeds than conventional bulk CMOS technology (bottom).

Figure 4.

A micrograph of the test circuit in silicon-on-sapphire technology. The fabricated die contained two channels and occupied just 3 × 3mm2. Each channel has series resistance, parasitic capacitance and leak compensation capability. After initial setup expenditures, each amplifier costs just a few dollars to manufacture.

2.4. High-performance operational amplifier design

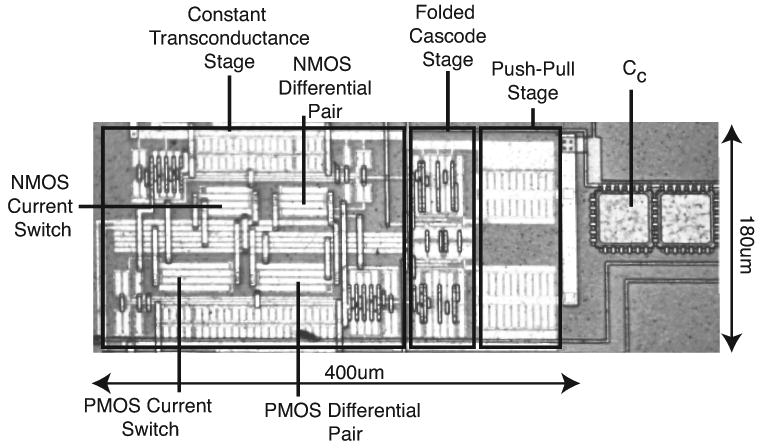

A low-noise, rail-to-rail, constant-transconductance operational amplifier was designed specifically for this system [12]. SOS transistors have low output resistance and therefore yield low voltage gains; we therefore made extensive use of cascode circuits, obtaining with this three-stage design a DC gain of 75 db and a gain-bandwidth product of 12 MHz for unity-gain operation. Figure 5 shows the fabricated operational amplifier, which occupies an area of less than 0.1 mm2. Rail-to-rail operation of the amplifier is needed to maximize voltage swings with the small power-supply voltages. The amplifier reported a of input-referred voltage noise in a bandwidth of 10 kHz, and < 1 mV of input-referred offset, while consuming 1.4 mW of power. Table 1 reports a summary of the amplifier characteristics.

Figure 5.

A die micrograph of the fabricated operational amplifier. The operational amplifier occupies an area of 0.08 mm2 providing rail-to-rail output voltage and constant gain-bandwidth product over the entire rail-to-rail common-mode range. The capacitor Cc is the frequency-compensation capacitor.

Table 1.

Measurement results for the operational amplifier designed for the patch-clamp system. A load resistance of 15kΩ and a 3.3V power supply was used in the measurements. The operational amplifier met all design specifications.

| Die Area | 0.08 mm2 |

|---|---|

| Open Loop Gain | 75 dB |

| Gain-Bandwidth Product | 12 MHz |

| Input-Referred Offset Voltage | 0.4 mV |

| Input Common-Mode Range | 0-3.3 V |

| Output Swing | 0-3.3V |

| Slew Rate | 10V/μs |

| Input-Referred Voltage Noise at 10 kHz | 3 × 10 −9V · Hz −1/2 |

| Quiescent Current | 430 μA |

| Input Capacitance | 2.6 pF |

3. Results

We have extensively tested the electrical properties of the two-channel patch-clamp system, and its functionality in patch-clamp recordings from cells. In these tests the system was controlled and data were acquired using the JClamp patch-clamp software (www.scisoftco.com). The results are comparable to those from commercial non-integrated patch clamp amplifiers.

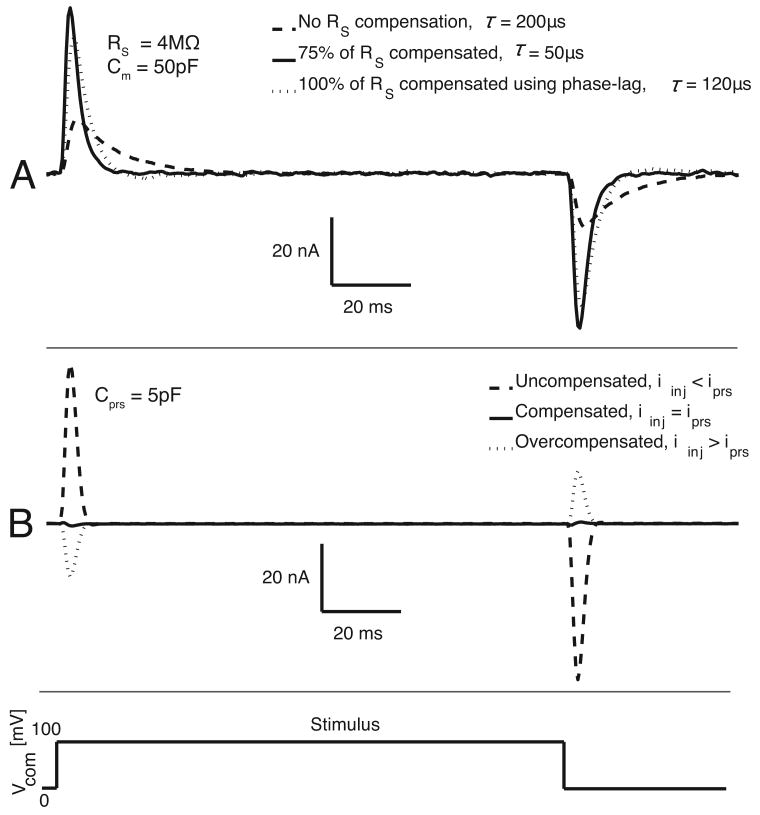

Figure 6-A shows the measured step responses of the series resistance compensation circuit. The time constant τ associated with charging the membrane capacitance Cm through a compensated resistance (RS – Rcomp) when a step Vcom is applied (inset), is given by τ = Cm(RS – Rcomp). Increasing compensation, Rcomp approaches RS and τ decreases, increasing recording bandwidth. Using the series resistance compensation circuit, we compensated 3-4 MΩ of the 4 MΩ electrode series resistance, decreasing the time needed to charge Cm from τ = 200 μs to 50 μs (75% compensation) and about 120 μs (100% compensation). Full resistance compensation can only be obtained with the phase-lag compensation circuit, which yields complete compensation at low frequencies but slows the settling time of the system.

Figure 6.

A- measured response of the series resistance compensation circuit when compensating a 4 MΩ electrode series resistance. The time needed to charge Cm was reduced from τ = 200 μs to 50 μs (75% compensation) and 120 μs (100% compensation with phase-lag). B- measured step response of the electrode capacitive compensation circuit when compensating 5 pF at the input. When uncompensated, the headstage provides the current iprs needed to charge the parasitic capacitance. This current appears as spikes in the current monitor signal. When properly compensated, iprs = iinj and the spikes do not appear. When overcompensated, iinj > iprs and the spikes reverse polarity.

Figure 6-B shows the measured step response of the electrode capacitive compensation circuit. When uncompensated, the headstage provides the current iprs needed to charge the parasitic capacitance. This current appears as spikes in the current-monitor signal with the same polarity as Vcom. When properly compensated, the spikes are greatly reduced in size.

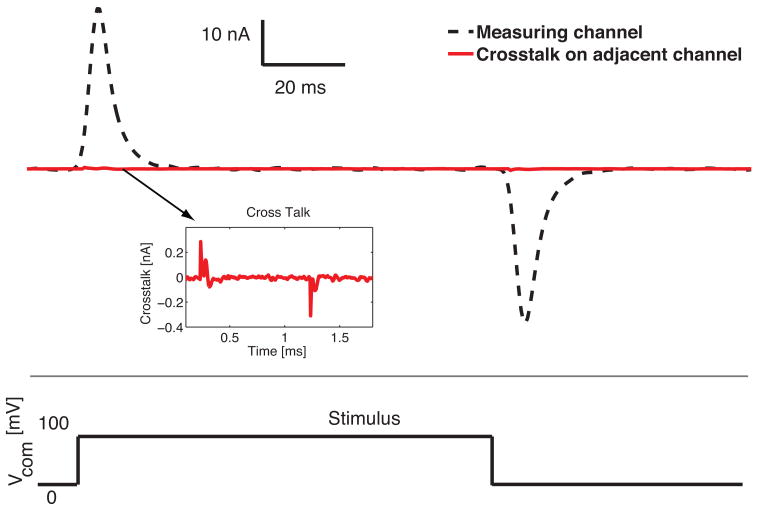

Figure 7 shows measured simultaneous data from both channels of the system. We applied a large voltage step (100 mV) to one channel with a model cell connected to its input terminal. The cross-talk on the adjacent non-measuring channel is 40 dB lower even with 80% series resistance compensation in use.

Figure 7.

Measured crosstalk between channels. A voltage step of 100 mV was applied to one channel, which was driving a model circuit with 80% series-resistance compensation. The current-monitor signal in the adjacent non-measuring channel is at least 40 dB lower.

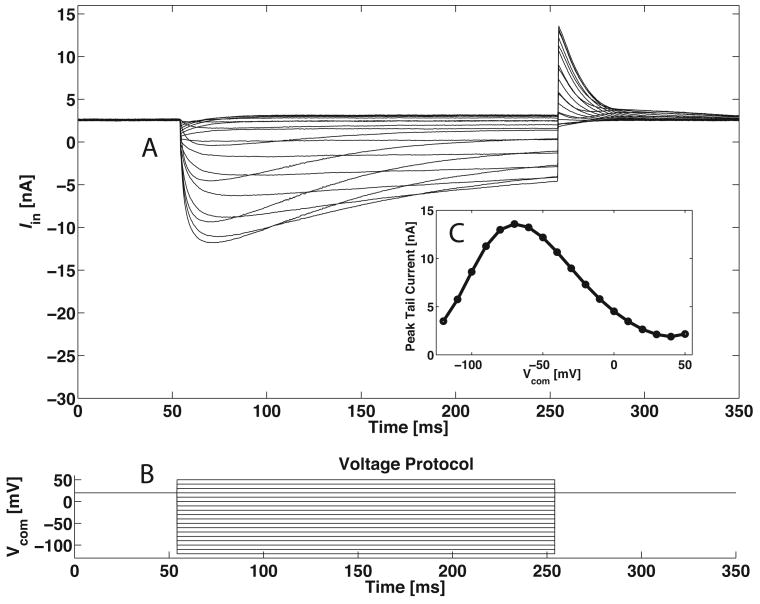

Figure 8 shows a whole-cell recording from an HEK293 cell expressing hERG channels. We compensated the 6.5 pF parasitic capacitance, and 80% of the 4.2 MΩ series resistance present at the input. Rf was set to 5 MΩ. The peak tail current curve in part C shows the standard voltage dependence of inactivation and activation in the channels.

Figure 8.

A, single-sweep responses from an HEK 293 cell expressing hERG channels. Rs was 4.2 MΩ of which 80% was compensated. Cprs of 6.5 pF was fully compensated. Cm was 40 pF. B, the cells were held at 20 mV and stepped to potentials of -130 mV to 50 mV in 10 mV increments for 200 ms. C, the tail currents at +20 mV are plotted vs. Vcom from A. The extracellular solution contained (mM) 117 NaCl, 13 KCl, 10 HEPES, 5 EGTA. The pipette solution contained 160 KCl, 1 EGTA, 10 HEPES. Currents were recoded at 100 kHz and filtered at 10 kHz.

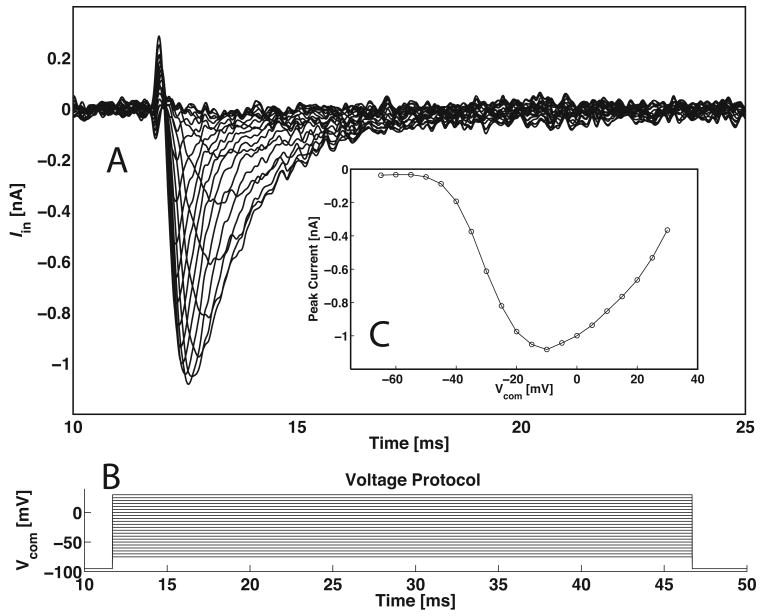

Sodium-channel currents present a particularly demanding test for a whole-cell recording system. The rapid kinetics and negative-resistance characteristic of these currents requires good Rs compensation. Figure 9 A shows single-sweep recordings from an HEK293 cell expressing Nav 1.7 channels. Linear leak and residual capacitance artifacts were subtracted using the -P/6 method. This protocol (using six inverted pulse sequences scaled down by a factor of 6, delivered at negative membrane potentials) increases the net rms noise in the traces about three-fold. Despite the large cell capacitance (Cm = 40 pF) the clamp time constant was 40 μs, giving a faithful current time course. The peak current-voltage curve (Figure 9 C) shows steep activation of the channel currents with no evidence of series-resistance error [11].

Figure 9.

A, single-sweep responses of HEK 293 cells expressing Nav 1.7 sodium channels, after linear leak subtraction using the -P/6 protocol. The leak subtraction increases the net rms noise in the traces about three-fold. RS was 4.5 MΩ of which 80% was compensated. Cprs of 7 pF was fully compensated. Cm was 40 pF. B, to generate activation curves, the cells were held at -100 mV and stepped to potentials of -75 mV to 30 mV in 5 mV increments for 35 ms. C, the peak currents vs. Vcom from A. The current-monitor signal was filtered at 10 kHz and sampled at a 100 kHz rate. The recording was made at room temperature. The extracellular solution contained (in mM) 127 NaCl, 13 KCl, 10 HEPES. The pipette solution contained 10 NaCl, 140 CsF, 10 HEPES, 1 EGTA.

Table 2 summarizes the key features of the PatchChip. The 2-channel system occupies 3 × 3 mm2 of area and consumes 5 mW of power per channel. The low power consumption allows the amplifiers to be placed in close proximity to the cells under test. The input-referred noise is 8 pA rms at 10 kHz bandwidth.

Table 2.

Key features of the two-channel patch-clamp system.

| Technology | 0.5 micron Silicon-on-Sapphire |

|---|---|

| Number of channels | 2 per die |

| Silicon area | 3 × 3 mm per die 1.5 × 3 mm per channel |

| Power consumption | 5 mW per channel at 3.3V |

| Capacitive compensation | 10 pF max |

| Series resistance compensation | 80% up to 10×Rf, or 100% with phase-lag compensation |

| Leak compensation | conductance up to 1/Rf |

| Current noise | 8 pA rms input-referred in a 10kHz bandwidth (Rf =10 MΩ) |

| Variable feedback resistor Rf | 50, 100, 250, 500 kΩ 1, 2.5, 5, 10 MΩ |

| Dynamic range | ± 20 μA |

| Reconstruction filter | 2 poles, 60 kHz cutoff |

| Anti-aliasing filter | 3 poles, 20 kHz cutoff |

| Nonlinearity | < 0.1 % |

| Cross talk between adjacent channels | −40 dB (at 80 % series resistance compensation) |

4. Discussion

We have implemented a two-channel patch-clamp system in silicon-on-sapphire on a 3 × 3 mm chip area. The system reports below −40 dB of cross talk between adjacent channels and the input-referred current noise of the system is 8 pA rms in a 10 kHz bandwidth. The appropriate setting of the feedback resistor, 5-10MΩ for typical whole-cell recordings, means that the resistor's thermal noise makes a contribution; however this contribution is moderate in comparison to the thermal noise from the series resistance of the electrode-and-cell combination. The system is able to compensate series resistances and parasitic capacitances up to 100 MΩ and 10 pF respectively. The power consumption of the device is 5 mW per channel at 3.3 V. This accurate, low-noise system with electrode compensation can replace a commercial rack-mounted patch-clamp system; more importantly it can also be integrated into a massively parallel, high-throughput, patch-clamp system that can significantly advance the state-of-the-art in drug screening and ion-channel research.

Acknowledgments

The authors are grateful to Yangyang Yan and Mark Estacion for their assistance with the cell lines; also to John Keeler of Warner Instruments, and Victor Pantani, Henrik Abildgaard, Hazael Montanaro and Andrew Kunil Choe for their assistance in preparing the hardware test-bed. This project was funded in part by NIH R42NS062408, NSF IDBR DBI-0649349 and ONR N00014-08-1-0065.

Footnotes

Publisher's Disclaimer: This is a PDF file of an unedited manuscript that has been accepted for publication. As a service to our customers we are providing this early version of the manuscript. The manuscript will undergo copyediting, typesetting, and review of the resulting proof before it is published in its final citable form. Please note that during the production process errors may be discovered which could affect the content, and all legal disclaimers that apply to the journal pertain.

References

- 1.Weerakoon P, Culurciello E, Klemic K, Sigworth F. An integrated patch-clamp potentiostat with electrode compensation. IEEE transactions on Biomedical Circuits and Systems. 2009;3:117–125. doi: 10.1109/TBCAS.2008.2005419. [DOI] [PubMed] [Google Scholar]

- 2.Weerakoon P, Sigworth F, Klemic K, Culurciello E. Integrated patch-clamp biosensor for high-density screening of cell conductance. IEEE Electron Device Letters. 2007;44(2):81–82. [Google Scholar]

- 3.Weerakoon P, Klemic K, Sigworth F, Culurciello E. IEEE International Symposium on Circuits and Systems, ISCAS '07. IEEE; New Orleans, LA: 2007. An integrated patch-clamp amplifier for high-density whole-cell recordings; pp. 1205–1209. [Google Scholar]

- 4.Laiwalla F, Klemic K, Sigworth F, Culurciello E. IEEE/NLM Life Science Systems and Application Workshop. IEEE; Bethesda MD: 2006. An integrated silicon-on-sapphire patch-clamp amplifier. [Google Scholar]

- 5.Laiwalla F, Klemic K, Sigworth F, Culurciello E. IEEE International Symposium on Circuits and Systems, ISCAS '06. IEEE; Kos, Greece: 2006. An integrated patch-clamp amplifier in silicon-on-sapphire CMOS; pp. 4054–4057. [Google Scholar]

- 6.Laiwalla F, Klemic K, Sigworth F, Culurciello E. An Integrated Patch-Clamp Amplifier in Silicon-on-Sapphire CMOS. IEEE Transactions on Circuits and Systems, TCAS-I, special issue on Life Science and Applications. 2006;53(11):2364–2370. [Google Scholar]

- 7.Sigworth F. Electronic design of the patch-clamp. In: Sakmann B, Neher E, editors. Single-Channel Recording. 2nd. Ch. 4 Plenum Press; New York: 1995. [Google Scholar]

- 8.Sigworth F. Design of the EPC-9, a computer-controlled patch-clamp amplifier. 1. Hardware. Journal of Neuroscience Methods. 1995;56:195–202. [PubMed] [Google Scholar]

- 9.Culurciello E, Pouliquen P, Andreou A. A digital isolation amplifier in silicon-on-sapphire CMOS. Electronics Letters. 2007;43(8):451–452. [Google Scholar]

- 10.Culurciello E. Silicon-on-Sapphire Circuits and Systems. 1st. McGraw-Hill; 2010. [Google Scholar]

- 11.Estacion M, Dib-Hajj S, Benke P, te Morsche R, Eastman E, Macala L, Drenth J, Waxman S. Nav1.7 gain-of-function mutations as a continuum: A1632E displays physiological changes associated with erythromelalgia and paroxysmal extreme pain disorder mutations and produces symptoms of both disorders. Journal of Neurosceince. 2008;28(43):11079–11088. doi: 10.1523/JNEUROSCI.3443-08.2008. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 12.Weerakoon P, Sigworth F, Kindlmann P, Culurciello E. A 3 nV/sqrt(Hz) rail-to-rail operational amplifier in silicon-on-sapphire with constant transconductance. Analog Integr Circ Sig Process. 2010 doi:10.1007/s10470-010-9484-6. [Google Scholar]