Abstract

A compact nonvolatile programmable switch (NVPS) using 90 nm CMOS technology together with perpendicular magnetic tunnel junction (p-MTJ) devices is fabricated for zero-standby-power field-programmable gate array. Because routing information does not change once it is programmed into an NVPS, high-speed read and write accesses are not required and a write-control transistor can be shared among all the NVPSs, which greatly simplifies structure of the NVPS. In fact, the effective area of the proposed NVPS is reduced by 40% compared to that of a conventional MTJ-based NVPS. The instant on/off behavior without external nonvolatile memory access is also demonstrated using the fabricated test chip.

INTRODUCTION

A field-programmable gate array (FPGA) using a nano-scale CMOS process is quite attractive hardware because of its low volume cost as well as fast turn around time.1 However, standby power dissipation due to leakage current2 has been the largest obstacle for the advancement of the FPGA. The implementation of a nonvolatile FPGA, wherein all the stored data remain in the nonvolatile devices even if the power supply is cut off, is one promising way of completely eliminating wasted standby power.3, 4, 5, 6, 7, 8, 9, 10, 11, 12 Because a magnetic tunnel junction (MTJ) device has attractive features such as 3D-stacking capability, scalability, and virtually unlimited endurance (over 1016 cycles),13, 14 it is a viable candidate for realizing a Nonvolatile FPGA (NVFPGA), and fundamental logic components of the NVFPGA have been proposed.7, 8, 9, 10, 11, 12 On the other hand, it is also important to implement a compact nonvolatile programmable switch (NVPS) that is composed of an NMOS pass switch together with a nonvolatile storage element and used for signal routing in the FPGA. However, a conventional MTJ-based NVPS tends to be large because the nonvolatile storage element requires large write-control transistors for supplying sufficient bi-directional write current through MTJ devices.8, 15

In this paper, a compact NVPS is fabricated using 90 nm CMOS technology together with perpendicular-MTJ (p-MTJ) devices.13 Because routing information does not change frequently once it is programmed into an NVPS, high-speed read and write access is not required, which greatly simplifies the structure of the NVPS. Moreover, because a large-sized transistor for driving sufficient write current is shared among all the NVPS, the effective size of two write-control transistors in each NVPS can be minimized. In fact, the effective area of the proposed NVPS is reduced by 40% in comparison with a conventional MTJ-based NVPS.

NONVOLATILE PROGRAMMABLE SWITCH USING SHARED-CONTROL-TRANSISTOR STRUCTURE

Figure 1a shows a cross-sectional view of the fabricated CoFeB/MgO p-MTJ device having an effective junction size and a tunnel-barrier thickness of and 1.0 nm, respectively. The resistance value (RM) is RP if the p-MTJ device is in a parallel state (P), while it becomes RAP and in an anti-parallel (AP) state. Additionally, the stored data M = 1 corresponds to RM = RP and M = 0 corresponds to RM = RAP, respectively. Figure 1b shows a typical measured R–I curve of the fabricated p-MTJ device. We can see that two distinct resistance values RP = 6 kΩ and RAP= 12 kΩ are obtained by applying write current IAP–P= 50 μA or IP–AP = −80 μA.

Figure 1.

Fabricated p-MTJ device: (a) Cross-sectional view. The effective junction size is and the thickness of the MgO barrier is 1.0 nm. (b) R–I characteristic of the fabricated p-MTJ device.

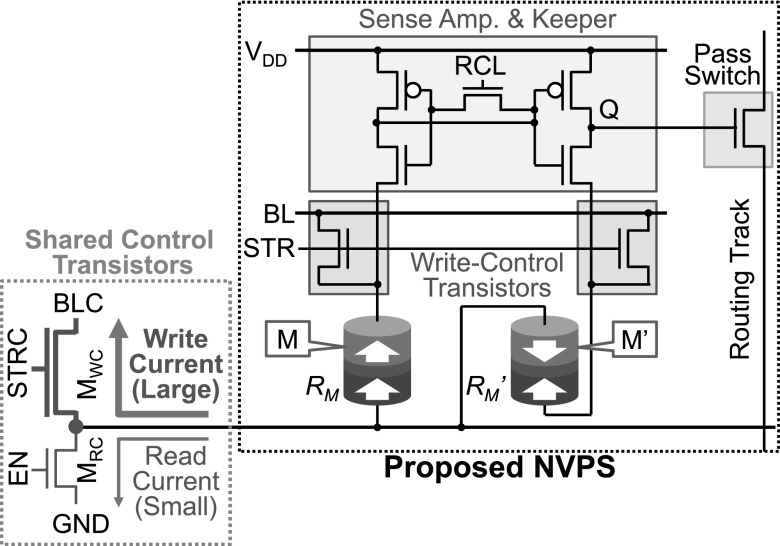

Figure 2 shows the overall structure of the routing block for the NVFPGA, in which NVPSs are used for signal routing from/to the logic block. To reduce the effective area of the routing block, control transistors are shared among all the NVPSs. Figure 3 shows a schematic diagram of the proposed NVPS. The output of nonvolatile storage element (Q) is used for turning on/off the NMOS pass switch. The nonvolatile storage element consists of a sense amplifier using two inverters and two local write control transistors together with two p-MTJ devices, in which routing information is programmed in a complementary fashion. The sense amplifier is used for reading stored state M and keeping it as Q during the power-on state without creating a steady DC current path. Because they do not change once configuration data are programmed into the NVPS, no additional control transistor is required.

Figure 2.

Overall structure of the proposed routing block for the NVFPGA.

Figure 3.

Schematic diagram of the proposed NVPS.

Figure 4 shows the configuration scheme of the proposed NVPS where M = 1 and M′ = 0 are stored into p-MTJ devices. When STR, STRC, and BL are activated high, parallel current paths are created and IM and flow through RM and , respectively. In this case, IM is larger than switching current IAP–P and the state of RM becomes the P state. Then exceeds switching current IP–AP and the state of changes to the AP state. After the configuration, the states are loaded by the sense amplifier. The read-control transistor is implemented with a small feature size compared to that of write-control one, which enables the avoidance of read disturbance, wherein data are accidentally written into an MTJ device while reading. Note that the proposed configuration scheme is performed under a standard CMOS supply voltage, and no special transistor is required. By tuning the gate width of the write-control transistors, we can control appropriate write current for the proposed configuration scheme.

Figure 4.

Configuration scheme of the proposed NVPS.

EVALUATIONS

Figure 5a shows a die photo of the fabricated test chip using 90 nm CMOS technology together with p-MTJ devices. The p-MTJ devices are stacked over the 4th metal layer. The shared-control transistors are located at the right side of the NVPS array. Figure 5b shows the measured waveform of the fabricated test chip. We can confirm that configuration data “0” (turn off NMOS pass switch) and “1” (turn on NMOS pass switch) are stored into the nonvolatile storage element in the NVPS by utilizing the shared-control transistor, and they are recalled after power-on successfully.

Figure 5.

Fabricated test chip using 90 nm CMOS/75 nm MTJ technologies: (a) Die photo. (b) Measured waveform.

Figure 6 summarizes the area comparison.16 The area of NVPS using Ref. 8 is the largest among the three because a bi-directional write current must be applied simultaneously to the series connected p-MTJ devices. By utilizing a two-step MTJ configuration, the area of the NVPS using Ref. 15 becomes smaller than that of the previous one. However, there are wasted control transistors in terms of the NVPS. Moreover, it is somewhat difficult to explore design space between reading and writing properties because the reading and writing functions are merged into the same circuit. In contrast, the proposed NVPS is implemented in the smallest area by removing all the wasted functions and sharing a portion of the read/write-control transistors. Moreover, we can optimize reading properties and writing one of the proposed circuit independently using pseudo three-terminal structure. Note that the effective voltage applied to a p-MTJ device is lower than 0.63 V, which is much lower than both breakdown voltage and back-hopping one.17, 18 While IM (or ) when a p-MTJ device is AP state is decreased as the tunnel magnetoresistance ratio (TMR) is increased, the proposed NVPS can drive sufficient write current even if TMR reaches 200%, which is sufficiently high for reading (the applied voltage to a p-MTJ device is lower than 0.69 V).

Figure 6.

Area comparison.16RP, RAP, IP–AP, and IAP–P used for the circuit design are based on measurement results as shown in Fig. 1b.

CONCLUSIONS

A compact NVPS is presented for an MTJ-based NVFPGA. By removing all the wasted control circuits and utilizing a shared-control transistor structure, the effective area of the NVPS can be minimized. For the next objective, it is very important to discuss how to determine the granularity of shared-control transistor for both an area and time efficient configuration scheme.

ACKNOWLEDGMENTS

This research was granted by the JSPS through FIRST Program. This research was also supported by VDEC in collaboration with Cadence, Inc.

References

- Kuon I. and Rose J., IEEE Trans. VLSI Syst. 19, 71 (2011). 10.1109/TVLSI.2009.2031318 [DOI] [Google Scholar]

- Pop E., Nano Res. 3, 147 (2010). 10.1007/s12274-010-1019-z [DOI] [Google Scholar]

- Greene J., Kaptanoglu S., Feng W., Hecht V., Landry J., Li F., Krouglyanskiy A., Morosan M., and Pevzner V., in Proc. ACM Int. Symp. FPGA (2011), p. 87.

- Liauw Y. Y., Zhang Z., Kim W., Gamal A. E., and Wong S. S., IEEE Int. Conf. Solid-State Circuits Dig. Tech. Pap. 2012, 406.

- Iida M., Koga M., Inoue K., Amagasaki M., Ichida Y., Saji M., Iida J., and Sueyoshi T., IEICE Trans. Electron. E94-C, 548 (2011). 10.1587/transele.E94.C.548 [DOI] [Google Scholar]

- Miyamura M., Tada M., Sakamoto T., Banno N., Okamoto K., Iguchi N., and Hada H., Int. Electron Devices Meet., Tech. Dig. 2012, 247. 10.1109/IEDM.2012.6479020 [DOI] [Google Scholar]

- Zhao W., Belhaire E., Javerliac V., Chappert C., and Dieny B., in Proc. Int. Conf. Inter. Circuit Design and Technologies (2006), p. 1.

- Zhao W., Belhaire E., Chappert C., Jacquet F., and Mazoyer P., Phys. Status Solidi A 205, 1373 (2008). 10.1002/pssa.200778135 [DOI] [Google Scholar]

- Suzuki D., Natsui M., Ikeda S., Hasegawa H., Miura K., Hayakawa J., Endoh T., Ohno H., and Hanyu T., Symp. VLSI Circuits Dig. Tech. Pap. 2009, 80. [Google Scholar]

- Yamamoto S., Shuto Y., and Sugahara S., Jpn. J. Appl. Phys., Part I 51, 11PB02 (2012). 10.7567/JJAP.51.11PB02 [DOI] [Google Scholar]

- Suzuki D., Natsui M., Endoh T., Ohno H., and Hanyu T., J. Appl. Phys. 111, 07E318 (2012). 10.1063/1.3672411 [DOI] [PMC free article] [PubMed] [Google Scholar]

- Suzuki D., Natsui M., Endoh T., Ohno H., and Hanyu T., Jpn. J. Appl. Phys., Part I 51, 04DM02 (2012). 10.7567/JJAP.51.04DM02 [DOI] [Google Scholar]

- Ikeda S., Miura K., Yamamoto H., Mizunuma K., Gan H. D., Endo M., Kanai S., Hayakawa J., Matsukura F., and Ohno H., Nature Mater. 9, 721 (2010). 10.1038/nmat2804 [DOI] [PubMed] [Google Scholar]

- Yoshida C., Ochiai T., Iba Y., Yamazaki Y., Tsunoda K., Takahashi A., and Sugii T., Symp. VLSI Technol. Dig. Tech. Pap. 2012, 59. 10.1109/VLSIT.2012.6242460 [DOI] [Google Scholar]

- Shuto Y., Yamamoto S., and Sugahara S., J. Appl. Phys. 105, 07C933 (2009). 10.1063/1.3076895 [DOI] [Google Scholar]

- Sakimura N., Nebashi R., Tsuji Y., Honjo H., Koike H., Ohsawa T., Fukami S., Hanyu T., Ohno H., and Endoh T., in Proc. IEEE Int. Conf. Circuits and Systems (2012), p. 1971.

- Min T., Sun J. Z., Beach R., Tang D., and Wang P., J. Appl. Phys. 105, 07D126 (2009). 10.1063/1.3063672 [DOI] [Google Scholar]

- Oh S.-C., Park S.-Y., Manchon A., Chshiev M., Han J.-H., Lee H.-W., Lee J.-E., Nam K.-T., Jo Y., Kong Y.-C., Dieny B., and Lee K.-J., Nat. Phys. 5, 898 (2009). 10.1038/nphys1427 [DOI] [Google Scholar]