Abstract

Collective interactions in functional materials can enable novel macroscopic properties like insulator-to-metal transitions. While implementing such materials into field-effect-transistor technology can potentially augment current state-of-the-art devices by providing unique routes to overcome their conventional limits, attempts to harness the insulator-to-metal transition for high-performance transistors have experienced little success. Here, we demonstrate a pathway for harnessing the abrupt resistivity transformation across the insulator-to-metal transition in vanadium dioxide (VO2), to design a hybrid-phase-transition field-effect transistor that exhibits gate controlled steep (‘sub-kT/q') and reversible switching at room temperature. The transistor design, wherein VO2 is implemented in series with the field-effect transistor's source rather than into the channel, exploits negative differential resistance induced across the VO2 to create an internal amplifier that facilitates enhanced performance over a conventional field-effect transistor. Our approach enables low-voltage complementary n-type and p-type transistor operation as demonstrated here, and is applicable to other insulator-to-metal transition materials, offering tantalizing possibilities for energy-efficient logic and memory applications.

The intrinsic properties of conventional semiconductors limits the speed and efficiency of field-effect transistors. Here, the authors take advantage of the insulator-to-metal transition in vanadium dioxide to create a transistor with reversible and steep-slope switching at room temperature.

The intrinsic properties of conventional semiconductors limits the speed and efficiency of field-effect transistors. Here, the authors take advantage of the insulator-to-metal transition in vanadium dioxide to create a transistor with reversible and steep-slope switching at room temperature.

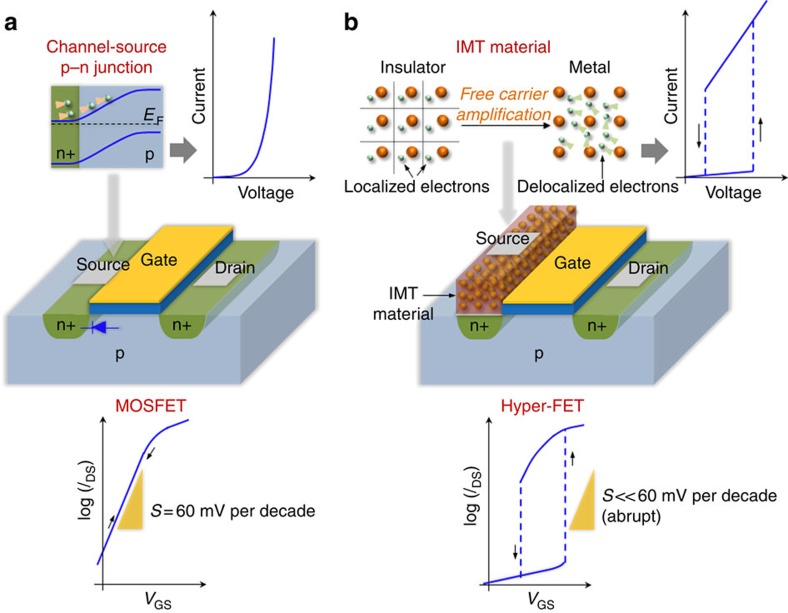

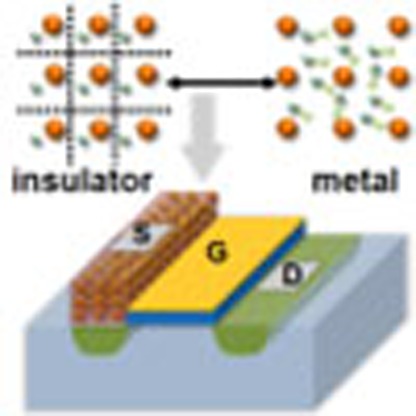

Metal-oxide-semiconductor field-effect transistors (MOSFETs) have been the workhorse of digital computation. In a conventional MOSFET (Fig. 1a), a change in the drain-to-source current (IDS) can be induced by the application of a transverse electric field across the gate dielectric by means of the third gate terminal. This field lowers the potential energy barrier separating the source and the channel, exponentially increasing the number of carriers traversing the channel. At room temperature, a minimum change of 60 mV in the gate bias (VGS) is required to effectuate a decade change in IDS, setting up the so-called ‘60 mV per decade' limit, also known as the ‘Boltzmann limit' (Fig. 1a). Stemming from the statistical distribution of free and independent carriers in conventional semiconductors and determined by the thermal voltage kT/q (k: Boltzmann constant; T: temperature; q: electron charge), this fundamental limit restricts transistor performance, particularly at low-operating voltages1,2,3,4, and has motivated the exploration of FETs that harness collective carrier responses5,6,7,8,9,10,11,12,13. Such collective behaviour—wherein a small external perturbation can trigger an aggregated change in the ground state of the system—can produce internal amplification; and provide a pathway to overcome the Boltzmann limit to enable FET's with sub-kT/q (kT/ηq; η>1) switching slope and superior performance at low voltages. Particularly, in insulator-to-metal transition (IMT) materials14 that exhibit strong correlation, like VO2 (refs 15, 16, 17, 18), the collective response to external perturbation (temperature19,20, pressure21,22 and electrical stimulus23,24,25,26,27,28) can be the ‘melting' of carriers, marking an electronic phase transformation where the electrons localized at atomic sites change to an itinerant state (Fig. 1b). This phase transformation amplifies the free-carrier concentration29; and in the case of VO2, manifests itself as a sharp change in resistivity up to five orders in magnitude30 at ∼340 K. However, attempts to realize IMT-based three-terminal transistor devices with a solid-state gate dielectric to induce the phase transition directly in the channel material have experienced only limited success23,31,32,33. Further, the alternate approach of using an ionic liquid as the gate dielectric, which is the focus of current research34,35,36,37,38,39, is typically slow40,41,42 and susceptible to electrochemical effects43. These constraints have restricted the utilization of this collective phenomenon in FETs for advanced high-performance electronic applications.

Figure 1. Schematic device design of hyper-FET and working principle.

(a) Conventional MOSFET and its transfer characteristics (channel current IDS versus gate bias VGS) for a fixed drain-to-source voltage VDS. The channel-source p–n junction, modulated by the gate terminal, controls the injection of carriers into the channel limiting the switching slope (S) of the MOSFET to 60 mV per decade (Boltzmann limit). (b) Proposed hyper-FET in which an insulator-to-metal transition (IMT) material that shows electrically induced abrupt resistivity switching is electrically integrated in series with the source of a conventional MOSFET. For a given VDS, the gate-terminal voltage VGS modifies the current flowing through the MOSFET and the IMT material in series, triggering an abrupt phase transition. The associated delocalization of localized carriers (free-carrier amplification) across the IMT results in an abrupt decrease in the resistance of the source, enhancing the switching slope characteristics beyond the intrinsic limits of a conventional p–n junction.

Here, we explore a novel transistor architecture that harnesses the abrupt free-carrier amplification across the phase transition in VO2 using a conventional MOSFET. By electrically coupling the VO2 in series with the source of a conventional MOSFET (Fig. 1b), we design a hybrid-phase-transition-FET (hyper-FET) wherein, for a given drain-to-source voltage (VDS), the gate bias VGS modifies the current IDS flowing through the MOSFET channel and the VO2 in series, triggering an abrupt phase transformation in VO2. The proposed hyper-FET not only exhibits steep-slope characteristics but also circumvents the need for a direct field-induced phase transition in VO2 with a solid-state gate dielectric. Further, the abrupt resistivity switching of VO2 in the hyper-FET configuration, which is the origin of the steep-slope characteristics, induces a negative differential resistance (NDR) across VO2 that results in internal voltage amplification which consequently enhances the hyper-FET's performance beyond that of a conventional MOSFET.

Results

Experimental demonstration and operation principle

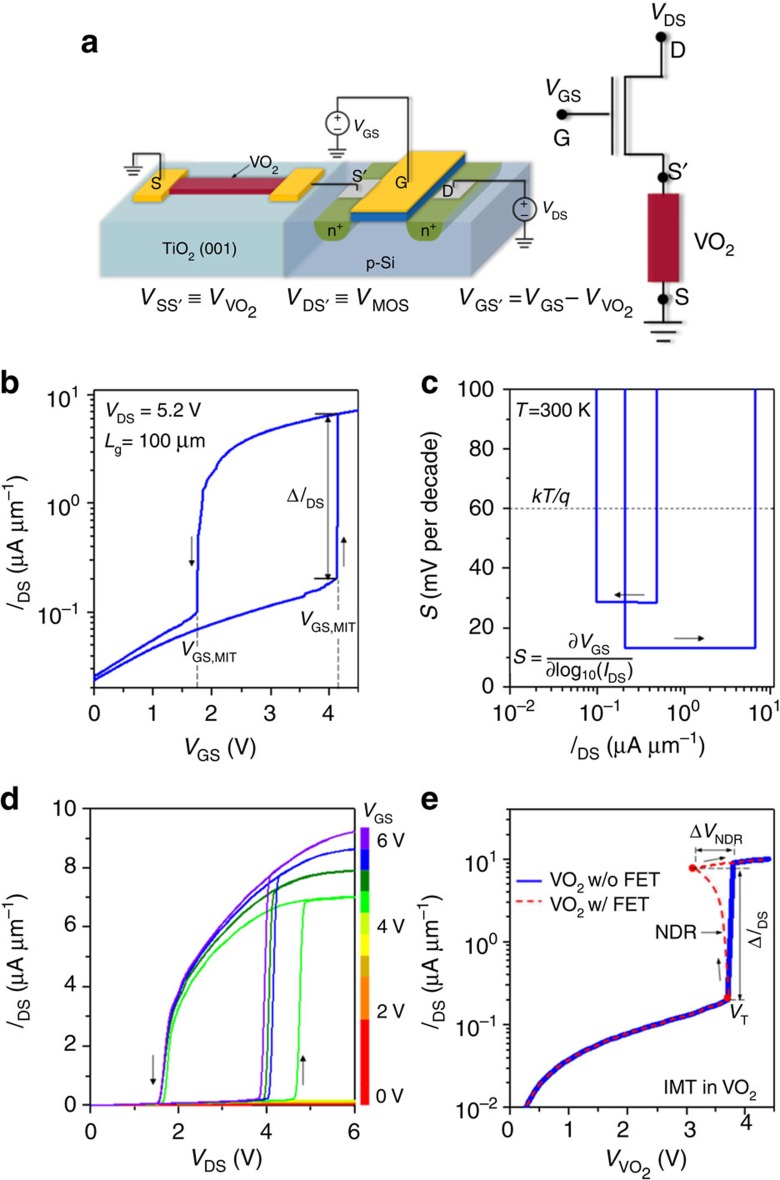

Figure 2a illustrates the schematic of an experimental hyper-FET consisting of a two-terminal VO2 device in series with the channel of a conventional Si n-MOSFET (individual device characteristics are shown in Supplementary Fig. 1 and discussed in Supplementary Note 1). All measurements in this work are performed at room temperature (T=300 K). The modulation in the transfer characteristics (IDS–VGS) of the hyper-FET is shown in Fig. 2b. Initially, at VGS=0 V (MOSFET in OFF-state), VO2 is in the high-resistivity insulating state. In this series combination, VDS is divided between the MOSFET channel and the insulating VO2 in proportion to their respective resistances; and the current IDS through the channel and VO2 is insufficient to induce an IMT. As VGS increases, the MOSFET-channel resistance decreases until IDS reaches a critical current threshold, IIMT. This triggers an abrupt IMT with the VO2 transforming into the low-resistivity metallic state that consequently leads to an abrupt increase in IDS (turn-ON). Similarly, as VGS reduces, the MOSFET-channel resistance increases until IDS drops to a critical threshold value, IMIT, and the VO2 transforms back to the high-resistivity insulating state accompanied by an abrupt reduction in IDS (turn-OFF). The difference between the critical threshold values (IMIT>IIMT; corresponding to VGS,IMT, VGS,MIT, respectively) results in hysteresis (=VGS,IMT−VGS,MIT) (Fig. 2b).

Figure 2. Experimental demonstration of a VO2-based hyper-FET.

(a) Schematic of a hyper-FET consisting of a two-terminal VO2 device ( =4 μm;

=4 μm;  =2 μm) in series with the channel of a conventional Si n-MOSFET (Lg=100 μm; W=100 μm). VVO2 is the voltage across the VO2 device and VGS′ is the effective gate-to-source voltage across the MOSFET. (b) IDS–VGS transfer characteristics of the hyper-FET exhibiting abrupt and reversible modulation of the channel current IDS as a function of the gate-source voltage VGS. The abrupt turn-ON and turn-OFF of the hyper-FET corresponds to the IMT and MIT in VO2, respectively. (c) Switching slope (S) as a function of IDS revealing the steep-slope characteristics (S<60 mV per decade) of the hyper-FET during the forward and reverse gate bias sweep. (d) Output characteristics (IDS–VDS) of the hyper-FET with excellent current saturation. (e) Current versus voltage characteristics of the VO2 device with (red) and without (blue) the MOSFET in series, illustrating the electrically triggered abrupt IMT. The channel resistance of the MOSFET acts as a series resistor, modifying the current–voltage dynamics through a feedback and inducing a negative differential resistance NDR (red) across the phase transition in VO2. The NDR reduces the voltage across the VO2 by ΔVNDR. The current has been normalized to the width of the Si n-MOSFET to show that the abrupt IMT in VO2 triggers the abrupt turn-ON of the hyper-FET shown in b.

=2 μm) in series with the channel of a conventional Si n-MOSFET (Lg=100 μm; W=100 μm). VVO2 is the voltage across the VO2 device and VGS′ is the effective gate-to-source voltage across the MOSFET. (b) IDS–VGS transfer characteristics of the hyper-FET exhibiting abrupt and reversible modulation of the channel current IDS as a function of the gate-source voltage VGS. The abrupt turn-ON and turn-OFF of the hyper-FET corresponds to the IMT and MIT in VO2, respectively. (c) Switching slope (S) as a function of IDS revealing the steep-slope characteristics (S<60 mV per decade) of the hyper-FET during the forward and reverse gate bias sweep. (d) Output characteristics (IDS–VDS) of the hyper-FET with excellent current saturation. (e) Current versus voltage characteristics of the VO2 device with (red) and without (blue) the MOSFET in series, illustrating the electrically triggered abrupt IMT. The channel resistance of the MOSFET acts as a series resistor, modifying the current–voltage dynamics through a feedback and inducing a negative differential resistance NDR (red) across the phase transition in VO2. The NDR reduces the voltage across the VO2 by ΔVNDR. The current has been normalized to the width of the Si n-MOSFET to show that the abrupt IMT in VO2 triggers the abrupt turn-ON of the hyper-FET shown in b.

Analysing the switching slope  , shown in Fig. 2c, it is evident that the abrupt change in current associated with the IMT/MIT in VO2 results in steep-slope (S<60 mV per decade) characteristics, both during the forward and the reverse VGS sweep. We emphasize that the current change ΔIDS is abrupt and the extracted value of S is limited by the voltage resolution (1 mV). The corresponding output characteristics (IDS–VDS) of the hyper-FET (Fig. 2d) show excellent IDS saturation behaviour, which is paramount for small signal amplification. This is in contrast to the traditional IMT-based transistor design where the IMT occurs in the channel material23. Such a transistor is unlikely to demonstrate current saturation since the design envisages the IMT channel to have a metallic character in the transistor's ON-state which fundamentally cannot sustain a drain side depletion region.

, shown in Fig. 2c, it is evident that the abrupt change in current associated with the IMT/MIT in VO2 results in steep-slope (S<60 mV per decade) characteristics, both during the forward and the reverse VGS sweep. We emphasize that the current change ΔIDS is abrupt and the extracted value of S is limited by the voltage resolution (1 mV). The corresponding output characteristics (IDS–VDS) of the hyper-FET (Fig. 2d) show excellent IDS saturation behaviour, which is paramount for small signal amplification. This is in contrast to the traditional IMT-based transistor design where the IMT occurs in the channel material23. Such a transistor is unlikely to demonstrate current saturation since the design envisages the IMT channel to have a metallic character in the transistor's ON-state which fundamentally cannot sustain a drain side depletion region.

Internal amplification in the hyper-FET

To elucidate the internal amplification, we analyze the current–voltage dynamics across VO2 in the hyper-FET configuration (Fig. 2e). In this series combination, the abrupt IMT results in an NDR across the VO2. Such an NDR is induced because when the VO2 resistance decreases abruptly, it results in (a) an increase in IDS (ΔIDS) which flows through the VO2 device and the MOSFET channel in series; (b) a reduction in the voltage across the VO2 device  (−ΔVNDR) (see Supplementary Fig. 2 and Supplementary Note 2 for discussion on the NDR in VO2). The effective gate-to-source voltage across the MOSFET (VGS′; S′: internal node in Fig. 2a) when VO2 is in the insulating state (hyper-FET OFF-state) is VGS′=VGS−

(−ΔVNDR) (see Supplementary Fig. 2 and Supplementary Note 2 for discussion on the NDR in VO2). The effective gate-to-source voltage across the MOSFET (VGS′; S′: internal node in Fig. 2a) when VO2 is in the insulating state (hyper-FET OFF-state) is VGS′=VGS− . It can be observed that the voltage across the insulating VO2 results in an additional voltage drop (=−

. It can be observed that the voltage across the insulating VO2 results in an additional voltage drop (=− ) in the effective gate-to-source voltage VGS′. Across the IMT in VO2 which induces the NDR, this voltage drop (=−

) in the effective gate-to-source voltage VGS′. Across the IMT in VO2 which induces the NDR, this voltage drop (=− ) reduces by ΔVNDR (therefore increasing VGS′ by ΔVNDR; Fig. 2a). Thus, the additional voltage drop (=−

) reduces by ΔVNDR (therefore increasing VGS′ by ΔVNDR; Fig. 2a). Thus, the additional voltage drop (=− ) in VGS′ when VO2 is in the insulating state results in a drastic reduction in the OFF-state current (IDS,OFF) of the hyper-FET in comparison to the stand-alone MOSFET, whereas the reduction in ON-state current (IDS,ON) is much less significant since the voltage drop across the metallic VO2 is small; this results in an overall enhanced current change that is, a higher IDS,ON/IDS,OFF ratio (see Supplementary Fig. 3 and Supplementary Note 3 for additional details and simulations). We model the MOSFET with VO2 combination as an equivalent common-source transistor circuit (Fig. 2a) where:

) in VGS′ when VO2 is in the insulating state results in a drastic reduction in the OFF-state current (IDS,OFF) of the hyper-FET in comparison to the stand-alone MOSFET, whereas the reduction in ON-state current (IDS,ON) is much less significant since the voltage drop across the metallic VO2 is small; this results in an overall enhanced current change that is, a higher IDS,ON/IDS,OFF ratio (see Supplementary Fig. 3 and Supplementary Note 3 for additional details and simulations). We model the MOSFET with VO2 combination as an equivalent common-source transistor circuit (Fig. 2a) where:

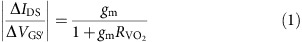

|

Here, gm is the transconductance of the stand-alone MOSFET. Across the IMT, the VO2 exhibits an NDR ( =−ΔVNDR/ΔIDS), and therefore equation (1) evolves to:

=−ΔVNDR/ΔIDS), and therefore equation (1) evolves to:

|

where

Equation (2) indicates that in a particular gate-voltage window, the amplified differential transconductance (βgm; β>1) of the hyper-FET facilitates a larger change in current compared with the stand-alone MOSFET. The VO2, therefore, sets up an internal amplifier (β>1) in the hyper-FET, and the transconductance enhancement (βgm) is directly related to the free-carrier amplification across the phase transition. We note that although the hyper-FET has reduced transconductance before and after the IMT (that is, VO2 in the stable insulating/metallic state), the abrupt free-carrier amplification across the IMT overcompensates this reduction and enables an amplified current change. To evaluate the improved performance of the hyper-FET, particularly for digital-logic applications, we match the OFF-state current IDS,OFF of the hyper-FET and the stand-alone MOSFET and analyze the increase in ON-state current IDS,ON over the operating gate-voltage window, as shown further.

Low-voltage n-type and p-type hyper-FET operation

Next, we focus on the MOSFET component of the hyper-FET. The gate-bias triggers the phase transition in VO2 by enabling the MOSFET to source the corresponding critical currents. Therefore, using a scaled transistor can enable low-voltage hyper-FET operation since the transistor can now source the same currents at low VGS and VDS. This motivates the integration of scaled, high-gm-advanced transistor architectures like FinFETs fabricated on channel materials having mobilities higher than that of silicon to design a low-voltage hyper-FET (Figs 3 and 4).

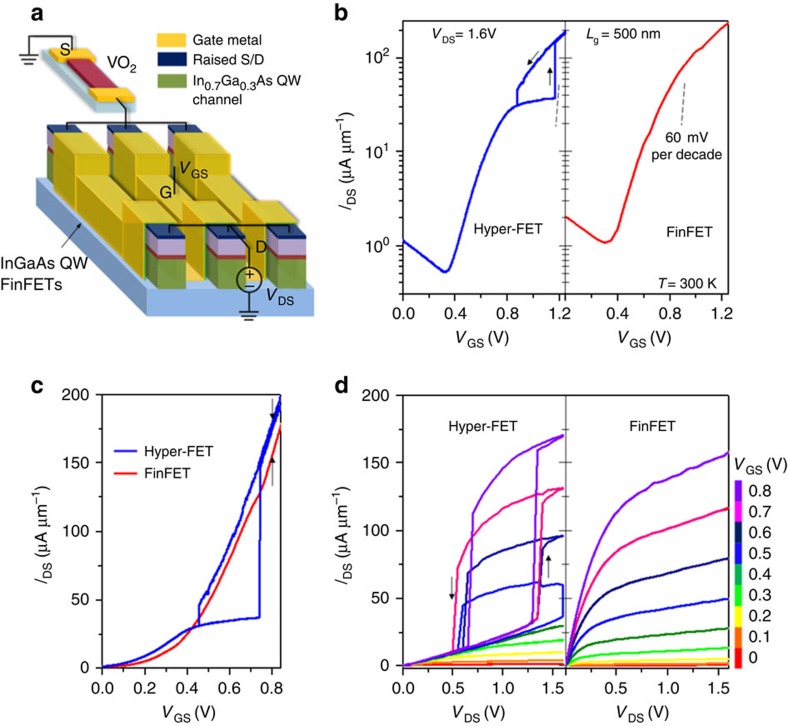

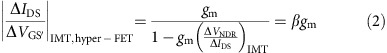

Figure 3. Experimental demonstration a low-voltage hyper-FET using next generation FinFET technology beyond Si.

(a) Schematic of the n-hyper-FET consisting of a series combination of a scaled VO2 ( =200 nm) and a multi-channel (=3 fins) In0.7Ga0.3As quantum-well FinFET (Lg=500 nm). (b) Transfer characteristics (IDS–VGS) of the hyper-FET and the stand-alone FinFET. (c) The positive feedback provided by the VO2 enables the hyper-FET to exhibit a ∼20 % higher ON-state current (IDS,ON) compared with the stand-alone n-FinFET over a gate-voltage window of 0.8 V at matched OFF-state current. (d) Output characteristics (IDS–VDS) of the n-hyper-FET and the conventional FinFET.

=200 nm) and a multi-channel (=3 fins) In0.7Ga0.3As quantum-well FinFET (Lg=500 nm). (b) Transfer characteristics (IDS–VGS) of the hyper-FET and the stand-alone FinFET. (c) The positive feedback provided by the VO2 enables the hyper-FET to exhibit a ∼20 % higher ON-state current (IDS,ON) compared with the stand-alone n-FinFET over a gate-voltage window of 0.8 V at matched OFF-state current. (d) Output characteristics (IDS–VDS) of the n-hyper-FET and the conventional FinFET.

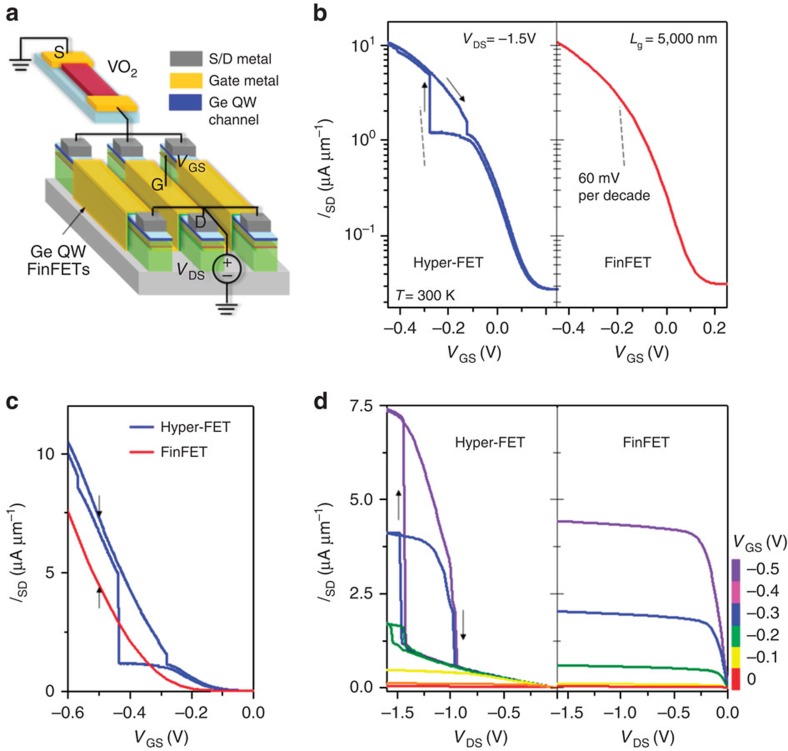

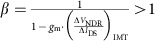

Figure 4. Experimental demonstration of a low-voltage p-type hyper-FET.

(a) Schematic of the p-hyper-FET consisting of a series combination of scaled VO2 ( =200 nm) and multi-channel (=200 fins) p-type Ge quantum-well FinFET (Lg=5,000 nm). (b) Transfer characteristics (ISD–VGS) of the hyper-FET and the FinFET (stand-alone). (c) The p-hyper-FET shows a ∼60 % higher ON-state current (ISD,ON) in comparison to the stand-alone FinFET over a gate-voltage window of −0.5 V at matched OFF-state current. (d) Output characteristics (ISD–VDS) of the p-hyper-FET and the conventional FinFET.

=200 nm) and multi-channel (=200 fins) p-type Ge quantum-well FinFET (Lg=5,000 nm). (b) Transfer characteristics (ISD–VGS) of the hyper-FET and the FinFET (stand-alone). (c) The p-hyper-FET shows a ∼60 % higher ON-state current (ISD,ON) in comparison to the stand-alone FinFET over a gate-voltage window of −0.5 V at matched OFF-state current. (d) Output characteristics (ISD–VDS) of the p-hyper-FET and the conventional FinFET.

Figure 3a illustrates a scaled hyper-FET consisting of a scaled In0.7Ga0.3As quantum-well multi-channel FinFET (Lg=500 nm) (see Supplementary Fig. 4 and Supplementary Note 4 for fabrication method) in series with VO2 ( =200 nm;

=200 nm;  =1 μm). Figure 3b shows the transfer characteristics of the hyper-FET (and the stand-alone FinFET) exhibiting a ‘gate controlled' abrupt turn-ON/turn-OFF associated with the IMT/MIT in VO2, respectively. The direct comparison of the hyper-FET with the stand-alone FinFET reveals an improved IDS,ON/IDS,OFF ratio over a VGS range of 0.8 V, and thus a ∼20% enhancement in IDS,ON at matched IDS,OFF (Fig. 3c). The corresponding output characteristics of the hyper-FET and its constituent FinFET, shown in Fig. 3d, also reflect the IDS enhancement.

=1 μm). Figure 3b shows the transfer characteristics of the hyper-FET (and the stand-alone FinFET) exhibiting a ‘gate controlled' abrupt turn-ON/turn-OFF associated with the IMT/MIT in VO2, respectively. The direct comparison of the hyper-FET with the stand-alone FinFET reveals an improved IDS,ON/IDS,OFF ratio over a VGS range of 0.8 V, and thus a ∼20% enhancement in IDS,ON at matched IDS,OFF (Fig. 3c). The corresponding output characteristics of the hyper-FET and its constituent FinFET, shown in Fig. 3d, also reflect the IDS enhancement.

We also demonstrate a p-type hyper-FET since complementary operation, similar to the complementary metal-oxide-semiconductor (CMOS) logic family, is imperative for low standby-power digital applications. Two-terminal VO2 devices exhibit reversible switching in both positive and negative voltage polarities (Supplementary Fig. 1) which allows for electrical integration with a p-channel FinFET to enable p-type hyper-FET operation. Figure 4a shows the schematic of a p-hyper-FET constructed using a p-channel Ge quantum-well multi-channel FinFET (see Supplementary Fig. 4 and Supplementary Note 4 for fabrication method) in series with VO2 ( =200 nm;

=200 nm;  =1 μm). Figure 4b,d shows the transfer characteristics and the corresponding output characteristics of the p-hyper-FET and its constituent FinFET, respectively. The p-hyper-FET also exhibits an enhanced ISD,ON/ISD,OFF ratio over a VGS range of −0.5 V, and thus a ∼60% enhancement in ISD,ON at matched ISD,OFF (Fig. 4c).

=1 μm). Figure 4b,d shows the transfer characteristics and the corresponding output characteristics of the p-hyper-FET and its constituent FinFET, respectively. The p-hyper-FET also exhibits an enhanced ISD,ON/ISD,OFF ratio over a VGS range of −0.5 V, and thus a ∼60% enhancement in ISD,ON at matched ISD,OFF (Fig. 4c).

Discussion

The hyper-FET is a device concept that harnesses the phase transition in the IMT material, VO2, to enable room temperature, steep-slope, n-type and p-type transistor operation with enhanced performance. These experimental results motivate the realization of a scaled, monolithic hyper-FET design entailing hetero-integration of the IMT material with the conventional FET44,45,46,47,48. Such an integrated device would have to include careful design considerations for minimizing the device ‘foot-print'44, reducing potential self-heating effects as well as ensuring low-contact resistance of both the conventional MOSFET, which can adversely affect its ON-state current (and therefore that of the hyper-FET), and that of the VO2, which may possibly affect the magnitude of abrupt current change across the IMT. Further, scaling and optimizing the VO2 and the MOSFET properties to enable a scaled hyper-FET device with low OFF-state leakage current relevant to low-power circuit applications49, and reduced hysteresis with a complete rail-to-rail swing in a complementary configuration (some of the design considerations are discussed in Supplementary Note 5 and Supplementary Fig. 5) will be key factors in realizing a hyper-FET-based hardware platform that can augment current state-of-the-art technology49.

The hyper-FET, demonstrated here, is a manifestation of a design methodology that consolidates the unique properties of phase transition materials like abrupt and reversible resistivity switching, arising from collective carrier dynamics and usually inaccessible in a conventional semiconductor, with the robust field-induced switching dynamics of a conventional MOSFET. Our approach harnesses the abrupt IMT in VO2 in the much-desired three-terminal transistor configuration, circumventing the need for direct electric field-induced phase transition. Furthermore, the generality of the hyper-FET design also facilitates this transistor architecture to be extended to other insulator–metal transition systems,50,51,52 thus opening the doors to using electronic phase transition materials in digital applications.

Additional information

How to cite this article: Shukla, N. et al. A steep-slope transistor based on abrupt electronic phase transition. Nat. Commun. 6:7812 doi: 10.1038/ncomms8812 (2015).

Supplementary Material

Supplementary Figures 1-5, Supplementary Table, Supplementary Notes 1-5 and Supplementary References

Acknowledgments

This work was primarily supported by the Office of Naval Research through award N00014-11-1-0665 and Intel Corporation through a customized Semiconductor Research Corporation project at the Pennsylvania State University. This work was also supported, in part, by the Center for Low Energy Systems Technology (LEAST), one of six centres of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA.

Footnotes

Author contributions N.S. performed the experiments. N.S. and S.D. analysed the data. A.V.T. fabricated the VO2 devices and the n-InGaAs quantum-well FinFETs. A.Ag. fabricated the p-Ge quantum-well FinFETs. H.P. grew the VO2 films. A.Az. helped with the data analysis. D.G.S., S.K.G., R.E-H. and S.D. supervised the study. N.S., S.K.G., R.E-H. and S.D. wrote the manuscript. All authors discussed the results and commented on the manuscript. S.D. directed the overall project.

References

- Ionescu A. M. & Riel H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329–337 (2011). [DOI] [PubMed] [Google Scholar]

- Zhirnov V. V. & Cavin R. K. Nanoelectronics: negative capacitance to the rescue? Nat. Nanotechnol. 3, 77–78 (2008). [DOI] [PubMed] [Google Scholar]

- Markov I. L. Limits on fundamental limits to computation. Nature 512, 147–154 (2014). [DOI] [PubMed] [Google Scholar]

- Cavin R. K., Lugli P. & Zhirnov V. V. Science and engineering beyond Moore's law. Proc. IEEE 100, 1720–1749 (2012). [Google Scholar]

- Mannhart J. & Haensch W. Put the pedal to the metal. Nature 487, 436–437 (2012). [DOI] [PubMed] [Google Scholar]

- Reich E. S. Metal oxide chips show promise. Nature 495, 17 (2013). [DOI] [PubMed] [Google Scholar]

- Zhou Y. & Ramanathan S. Correlated electron materials and field effect transistors for logic: a review. Crit. Rev. Solid State Mater. Sci. 38, 286–317 (2013). [Google Scholar]

- Inoue I. H. & Rozenberg M. J. Taming the Mott transition for a novel Mott transistor. Adv. Funct. Mater. 18, 2289–2292 (2008). [Google Scholar]

- Newns D. M. et al. Mott transition field effect transistor. Appl. Phys. Lett. 73, 780–782 (1998). [Google Scholar]

- Bernstein K., Cavin R. K., Porod W., Seabaugh A. C. & Welser J. Device and architectures outlook for beyond CMOS switches. Proc. IEEE 98, 2169–2184 (2010). [Google Scholar]

- Inoue I. H. Electrostatic carrier doping to perovskite transition-metal oxides. Semicond. Sci. Technol. 20, S112–S120 (2005). [Google Scholar]

- Ahn C. H., Triscone J.-M. & Mannhart J. Electric field effect in correlated oxide systems. Nature 424, 1015–1018 (2003). [DOI] [PubMed] [Google Scholar]

- Chakhalian J., Millis A. J. & Rondinelli J. Whither the oxide interface. Nat. Mater. 11, 92–94 (2012). [DOI] [PubMed] [Google Scholar]

- Imada M., Fujimori A. & Tokura Y. Metal-insulator transitions. Rev. Mod. Phys. 70, 1039–1263 (1998). [Google Scholar]

- Morin F. J. Oxides which show a metal-to-insulator transition at the Neel temperature. Phys. Rev. Lett. 3, 34–36 (1959). [Google Scholar]

- Berglund C. N. & Guggenheim H. J. Electronic properties of VO2 near the semiconductor-metal transition. Phys. Rev. 185, 1022–1033 (1969). [Google Scholar]

- Wentzcovitch R. M., Schulz W. W. & Allen P. B. VO2: Peierls or Mott-Hubbard? A view from band theory. Phys. Rev. Lett. 72, 3389–3392 (1994). [DOI] [PubMed] [Google Scholar]

- Rice T. M., Launois H. & Pouget J. P. Comment on ‘VO2: Peierls or Mott-Hubbard? A view from band theory'. Phys. Rev. Lett. 73, 3042 (1994). [DOI] [PubMed] [Google Scholar]

- Qazilbash M. M. et al. Mott transition in VO2 revealed by infrared spectroscopy and nano-imaging. Science 318, 1750–1753 (2007). [DOI] [PubMed] [Google Scholar]

- Zhang S., Chou J. Y. & Lauhon L. J. Direct correlation of structural domain formation with the metal insulator transition in a VO2 nanobeam. Nano Lett. 9, 4527–4532 (2009). [DOI] [PubMed] [Google Scholar]

- Cao J. et al. Strain engineering and one-dimensional organization of metal-insulator domains in single-crystal vanadium dioxide beams. Nat. Nanotechnol. 4, 732–737 (2009). [DOI] [PubMed] [Google Scholar]

- Park J. H. et al. Measurement of a solid-state triple point at the metal-insulator transition in VO2. Nature 500, 431–434 (2013). [DOI] [PubMed] [Google Scholar]

- Kim H.-T. et al. Mechanism and observation of Mott transition in VO2 -based two- and three-terminal devices. New J. Phys. 6, 052 (2004). [Google Scholar]

- Kim B.-J. et al. Micrometer X-ray diffraction study of VO2 films: separation between metal–insulator transition and structural phase transition. Phys. Rev. B 77, 235401 (2008). [Google Scholar]

- Cao J. et al. Constant threshold resistivity in the metal–insulator transition of VO2. Phys. Rev. B 82, 241101 (2010). [Google Scholar]

- Zimmers A. et al. Role of thermal heating on the voltage induced insulator–metal transition in VO2. Phys. Rev. Lett. 110, 056601 (2013). [DOI] [PubMed] [Google Scholar]

- Freeman E. et al. Nanoscale structural evolution of electrically driven insulator to metal transition in vanadium dioxide. Appl. Phys. Lett. 103, 263109 (2013). [Google Scholar]

- Stefanovich G., Pergament A. & Stefanovich D. Electrical switching and Mott transition in VO2. J. Phys. Condens. Matter 12, 8837–8845 (2000). [Google Scholar]

- Ruzmetov D., Heiman D., Claflin B., Narayanamurti V. & Ramanathan S. Hall carrier density and magnetoresistance measurements in thin-film vanadium dioxide across the metal-insulator transition. Phys. Rev. B 79, 153107 (2009). [Google Scholar]

- Ladd L. A. & Paul W. Optical and transport properties of high quality crystals of V2O4 near the metallic transition temperature. Solid State Commun. 7, 425–428 (1969). [Google Scholar]

- Ruzmetov D., Gopalakrishnan G., Ko C., Narayanamurti V. & Ramanathan S. Three-terminal field effect devices utilizing thin film vanadium oxide as the channel layer. J. Appl. Phys. 107, 114516 (2010). [Google Scholar]

- Boriskov P. P., Velichko A. A., Pergament A. L., Stefanovich G. B. & Stefanovich D. G. The effect of electric field on metal-insulator phase transition in vanadium dioxide. Tech. Phys. Lett. 28, 406–408 (2002). [Google Scholar]

- Sengupta S. et al. Field-effect modulation of conductance in VO2 nanobeam transistors with HfO2 as the gate dielectric. Appl. Phys. Lett. 99, 062114 (2011). [Google Scholar]

- Nakano M. et al. Collective bulk carrier delocalization driven by electrostatic surface charge accumulation. Nature 487, 459–462 (2012). [DOI] [PubMed] [Google Scholar]

- Liu K. et al. Dense electron system from gate-controlled surface metal-insulator transition. Nano Lett. 12, 6272–6277 (2012). [DOI] [PubMed] [Google Scholar]

- Shi J., Ha S. D., Zhou Y., Schoofs F. & Ramanathan S. A correlated nickelate synaptic transistor. Nat. Commun. 4, 2676 (2013). [DOI] [PubMed] [Google Scholar]

- Shi J., Zhou Y. & Ramanathan S. Colossal resistance switching and band gap modulation in a perovskite nickelate by electron doping. Nat. Commun. 5, 4860 (2014). [DOI] [PubMed] [Google Scholar]

- Hatano T. et al. Gate control of electronic phases in a quarter-filled manganite. Sci. Rep 3, 2904 (2013). [DOI] [PMC free article] [PubMed] [Google Scholar]

- Scherwitzl R. et al. Electric-field control of the metal-insulator transition in ultrathin NdNiO3 films. Adv. Mater. 22, 5517–5520 (2010). [DOI] [PubMed] [Google Scholar]

- Zhou Y. & Ramanathan S. Relaxation dynamics of ionic liquid—VO2 interfaces and influence in electric double-layer transistors. J. Appl. Phys. 111, 084508 (2012). [Google Scholar]

- Misra R., McCarthy M. & Hebard A. F. Electric field gating with ionic liquids. Appl. Phys. Lett. 90, 052905 (2007). [Google Scholar]

- Yi H. T., Gao B., Xie W., Cheong S.-W. & Podzorov V. Tuning the metal-insulator crossover and magnetism in SrRuO3 by ionic gating. Sci. Rep. 4, 6604 (2014). [DOI] [PMC free article] [PubMed] [Google Scholar]

- Jeong J. et al. Suppression of metal-insulator transition in VO2 by electric field-induced oxygen vacancy formation. Science 339, 1402–1405 (2013). [DOI] [PubMed] [Google Scholar]

- Lee M.-J. et al. Two series oxide resistors applicable to high speed and high density nonvolatile memory. Adv. Mater. 19, 3919–3923 (2007). [Google Scholar]

- Chudnovskii F. A., Odynets L. L., Pergament A. L. & Stefanovich G. B. Electroforming and switching in oxides of transition metals: the role of metal–insulator transition in the switching mechanism. J. Solid State Chem. 122, 95–99 (1996). [Google Scholar]

- Sakai J. et al. Pulsed laser-deposited VO2 thin films on Pt layers. J. Appl. Phys. 113, 123503 (2013). [Google Scholar]

- Martens K. et al. The VO2 interface, the metal-insulator transition tunnel junction, and the metal-insulator transition switch On-Off resistance. J. Appl. Phys. 112, 124501 (2012). [Google Scholar]

- Cheng C. et al. Self-assembly and horizontal orientation growth of VO2 nanowires. Sci. Rep. 4, 5456 (2014). [DOI] [PMC free article] [PubMed] [Google Scholar]

- Narasimha S. et al. in IEEE International Electron Devices Meeting, 3.3.1–3.3.4 (San Francisco, 2012).

- Brockman J. S. et al. Subnanosecond incubation times for electric-field-induced metallization of a correlated electron oxide. Nat. Nanotechnol. 9, 453–458 (2014). [DOI] [PubMed] [Google Scholar]

- Pickett M. D. & Williams R. S. Sub-100 fJ and sub-nanosecond thermally driven threshold switching in niobium oxide crosspoint nanodevices. Nanotechnology 23, 215202 (2012). [DOI] [PubMed] [Google Scholar]

- Asamitsu A., Tomioka Y., Kuwahara H. & Tokura Y. Current switching of resistive states in magnetoresistive manganites. Nature 388, 50–52 (1997). [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Supplementary Materials

Supplementary Figures 1-5, Supplementary Table, Supplementary Notes 1-5 and Supplementary References