Abstract

Synaptic devices with bipolar analog resistive switching behavior are the building blocks for memristor-based neuromorphic computing. In this work, a fully complementary metal-oxide semiconductor (CMOS)-compatible, forming-free, and non-filamentary memristive device (Pd/Al2O3/TaOx/Ta) with bipolar analog switching behavior is reported as an artificial synapse for neuromorphic computing. Synaptic functions, including long-term potentiation/depression, paired-pulse facilitation (PPF), and spike-timing-dependent plasticity (STDP), are implemented based on this device; the switching energy is around 50 pJ per spike. Furthermore, for applications in artificial neural networks (ANN), determined target conductance states with little deviation (<1%) can be obtained with random initial states. However, the device shows non-linear conductance change characteristics, and a nearly linear conductance change behavior is obtained by optimizing the training scheme. Based on these results, the device is a promising emulator for biology synapses, which could be of great benefit to memristor-based neuromorphic computing.

Keywords: memristor, artificial synapse, neuromorphic computing

1. Introduction

Over the last decades, rapid advances in digital computing system based on complementary metal-oxide semiconductor (CMOS) integrated circuit technology have substantially changed society. However, due to the limitations of classical von-Neumann computers (the von-Neumann bottleneck) in speed, power efficiency, and parallel processing, there are urgent demands for novel computing structures and systems [1]. The human brain is likely to be the most efficient computing system, because the operating frequency of our brain is in the range of 1–10 Hz, and it consumes only around 1–10 W of power, which means the energy consumption per synaptic event is only approximately 1–100 fJ [2]. Therefore, the novel computing system—neuromorphic computing, inspired by the brain—has attracted scientists’ attention in recent years for its advantages, such as being massively parallel and fault-tolerant. The weight modulation ability of synapses is known as synaptic plasticity, which is believed to be the primary reason for learning and memory in the brain. In order to implement neuromorphic computing, such as artificial neural networks (ANN), an electronic synaptic device is necessary.

Recently, the implementation of artificial synapses with memristors has been proposed. Memristors are two compact terminal devices that change their resistances when subjected to electrical stimulation [3,4,5,6]. Several memristors, ranging from resistive random access memory (RRAM) [7,8,9,10,11], to phase change memory (PCM) [12], to ferroelectric RAM [13,14,15], have been proposed for neuromorphic computing applications as artificial synapses. Several memristors based on new materials [16,17] have been proposed for neuromorphic computing. However, when memristors are employed in neuromorphic computing systems (e.g., artificial neuron networks), binary memristors with only two resistance states (i.e., high resistance state (HRS) and low resistance state (LRS)) have been proven to be effective only in some specific applications [18,19]. In some neuromorphic computing systems designed for complex applications, such as image recognition, the use of only two states as synaptic weights presents disadvantages in performances [20,21]—for example, low accuracy or area-efficiency. On the other hand, in biology neuromorphic systems, synaptic weights are continuously tunable in depression and potentiation; thus, memristors with gradually changing conductance in bipolarity could be more like the biology synapse, and can therefore emulate brain functions better than binary memristors. As artificial synapses, memristors with tunable conductance have attracted growing attention for being promising candidates for weight storage in neuromorphic computing systems, owing to the advantages in accuracy and area-efficiency. Several methods have been discussed to implement analog-resistive switching behavior, including using multiple memristors to construct one synapse [22], utilizing a unipolar analog behavior in some metal oxide-based filamentary memristors [11,23,24], optimizing programming schemes [25,26], adding heat enhancement layers [27], or using non-filamentary memristors [28,29,30]. Compared with the filamentary memristors, non-filamentary memristors can implement multilevel states more easily, but usually have poorer retention [31,32,33] However, realizing bipolar analog conductance change in both SET (transition from HRS to LRS) and RESET (transition from LRS to HRS) processes with satisfying retention time remains an open challenge.

In this paper, a fully CMOS-compatible, forming-free, and non-filamentary memristor device based on Ta/TaOx/Al2O3/Pd, with analog SET and RESET processes, is proposed for neuromorphic computing as an artificial synapse. The direct current (DC) sweeping results demonstrate that the device has bipolar analog resistance switching behavior, and the multilevel conductance states can be obtained with satisfying retention time. Synaptic plasticity, including long-term potentiation/depression (LTP/LTD), paired-pulse facilitation (PPF), and spiking-time-dependent plasticity (STDP), can be mimicked by our devices. For the applications in ANN, determined target conductance states and the linearity of conductance change are carefully examined.

2. Materials and Methods

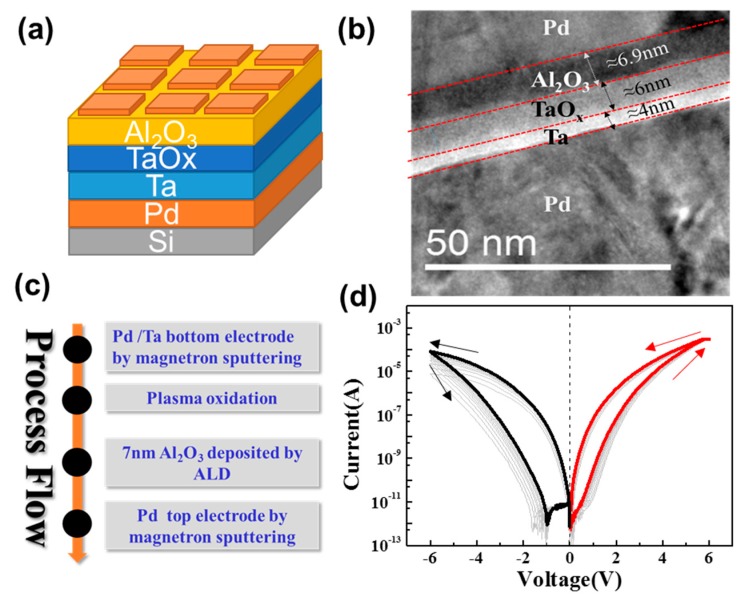

The metal–insulator (double functional layer)–metal structure and the cross-sectional transmission electron microscopy (TEM) image of the Ta/TaOx/Al2O3/Pd device are shown in Figure 1a,b, respectively. The fabrication process of the device is shown in Figure 1c. First, the Si substrate was cleaned with acetone, ethanol, and de-ionized water. 30 nm-thick Pd and 15 nm-thick Ta as the bottom electrode were deposited on the Si substrate by magnetron sputtering. A TaOx layer was formed by rapid thermal annealing (RTA) carried out for 300 s in plasma O2 by plasma-enhanced chemical vapor deposition (PECVD) at 275 °C. Direct oxygen plasma with a power of 100 W was applied on the Ta film. After RTA, 7 nm-thick Al2O3 was deposited by atom layer deposition (ALD). Finally, 40 nm Pd as the top electrode was deposited by magnetron sputtering after the lithography process. For our device, the highest temperature of the process is only 275 °C (below 400 °C), and all the materials (Pd, Ta, Al) were CMOS compatible. As a result, our device was fully CMOS compatible.

Figure 1.

(a) The schematic, (b) a cross sectional transmission electron microscopy (TEM) image of the Ta/TaOx/Al2O3/Pd device, (c) the fabrication processes of the Ta/TaOx/Al2O3/Pd device, and (d) typical I–V curves of the Ta/TaOx/Al2O3/Pd showing bipolar analog switching (SET voltage = 6 V, RESET voltage = −6 V).

The DC electrical characteristics of the device were measured by an Agilent B1500A semiconductor parameter analyzer (Santa Rosa, CA, US). During the electrical measurement, the voltage was applied to the top Pd electrode, while the Ta/Pd bottom electrode was tied to ground.

3. Results and Discussions

The resistive switching characteristics of the device were evaluated under DC programming conditions. The typical current–voltage (I–V) characteristic of the Ta/TaOx/Al2O3/Pd device under DC sweep mode from −6 V to 6 V is shown in Figure 1d. The device is forming-free, and no abrupt change of current in both SET and RESET switching processes is observed, indicating a bipolar analog resistive switching feature. Within 6 V and −6 V stop voltages on SET and RESET processes, a ~103 ratio between HRS and LRS can be obtained (read voltage is 1 V), which is larger than our recent work of similar TaOx/Al2O3 stack device (~102 ratio, Ti/AlOx/TaOx/Pt) [34].

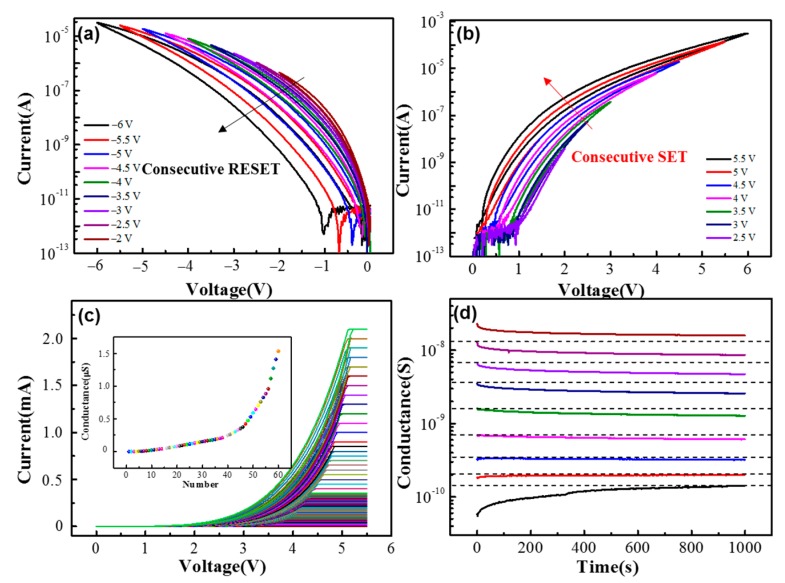

To further demonstrate the analog characteristics, the DC sweep with different working voltages and without compliance currents (SET voltage: 2.5 V, 3 V to 5.5 V; and RESET voltage: −2 V, −2.5 to −6 V) and the DC sweep with different compliance currents during SET process are shown in Figure 2. The initial resistance of the device is ~1011 Ω (read at 1 V). When the positive sweeping voltage is applied to the device, the resistance of the device is retained until the voltage reaches 2.5 V, then the resistance gradually decreases. During the consecutive SET process, as shown in an inset of Figure 2b, the responding currents (read at 1 V) can gradually increase with the increment of the stop voltages, indicating that different conductance states can be obtained in the SET process. Various conductance states can also be obtained by setting different compliance currents during the SET process. With compliance currents from 500 nA to 2.2 mA, the corresponding I–V curves and the 60 different resulting conductance states are shown in Figure 2c and the inset, respectively. The RESET process can be implemented by applying a negative DC sweeping voltage to the device. As shown in Figure 2a, eight consecutive negative DC sweeps with various stop voltages are applied to the device. As the voltages decrease from −2 to −6 V with a −0.5 V step, the device is switched to a higher resistance state after each step. Moreover, the multilevel resistance states can be preserved within satisfying retention time, as shown in Figure 2d. The multilevel resistance states are obtained by consecutive positive voltage sweepings (2 to 6 V with a 0.25 V step). After each sweeping, the device resistance states are monitored by a series of 1 V reading pulses at 0.5 s intervals. As it is shown in Figure 2d, though with slightly decay, nine different states can be clearly distinguished after 1000 s.

Figure 2.

Bipolar analog-resistive switching characteristics of the Ta/TaOx/Al2O3/Pd device under the DC sweeping mode: (a) consecutive DC sweeping with different stop voltages from −2 to −6 V in the RESET process; (b) consecutive DC sweeping with different stop voltages from 2.5 to 5.5 V in the SET process; (c) consecutive DC sweeping with different compliance currents from 500 nA to 2.2 mA in the SET process (inset: 60 different conductance states obtained by modulating different compliance currents); and (d) retention characteristics of nine different resistance states of the Ta/TaOx/Al2O3/Pd device.

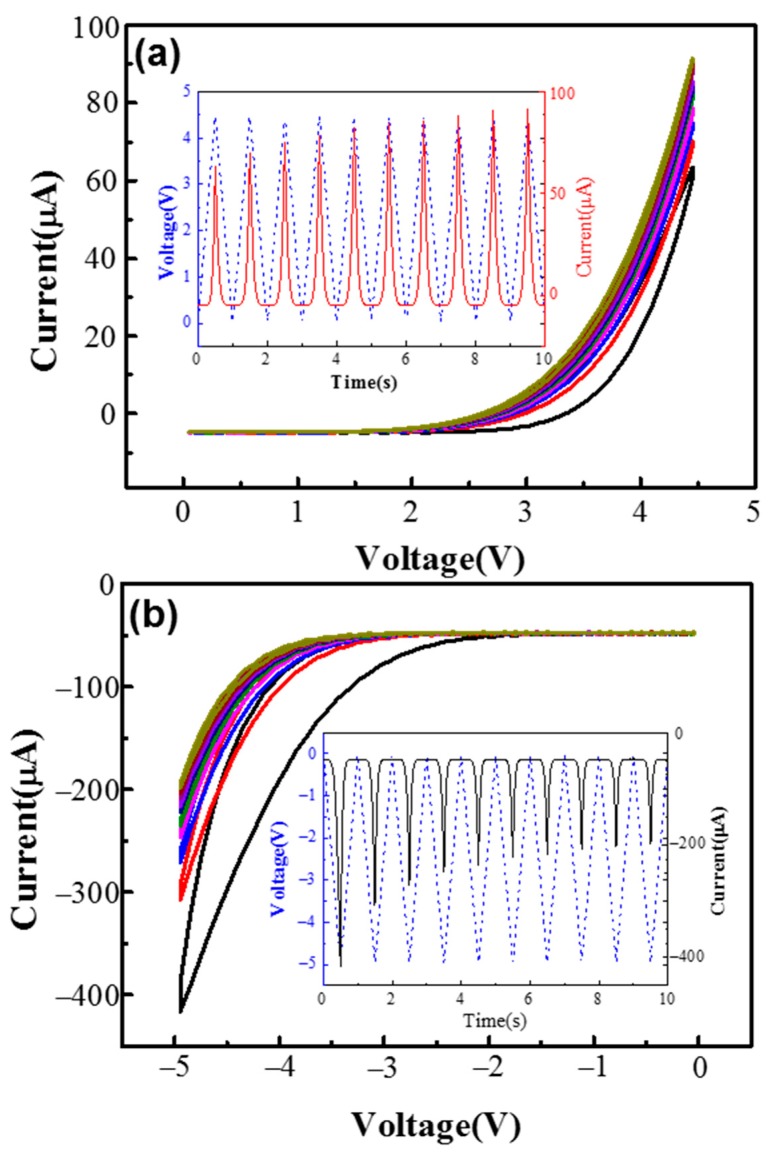

The characteristics of the bipolar analog-resistive switching in pulse mode are investigated via positive (0 to 4.5 V) and negative (0 to −5 V) triangle pulses, as shown in Figure 3a,b, respectively. The curves of current and voltage versus time for the SET and RESET processes are shown in the insets of Figure 3a,b, respectively. These results further confirm the analog resistive switching characteristics under both positive and negative pulses. The results reveal that in both the SET and RESET processes, gradual tuning of the multilevel conductance states can be obtained. Bipolar analog resistive switching characteristics are fully analogous to the biology synapse; thus, the devices have the potential to mimic synaptic functions in neuromorphic computing system.

Figure 3.

(a) Gradual SET under positive triangle pulses (from 0 to 4.5 V) (inset: the I-t and V-t curves of (a), representing the gradual increasing of current with time); (b) gradual RESET under negative triangle pulses (from 0 to −5 V) (inset: the I-t and V-t curves of (b), representing the gradual decreasing of current with time).

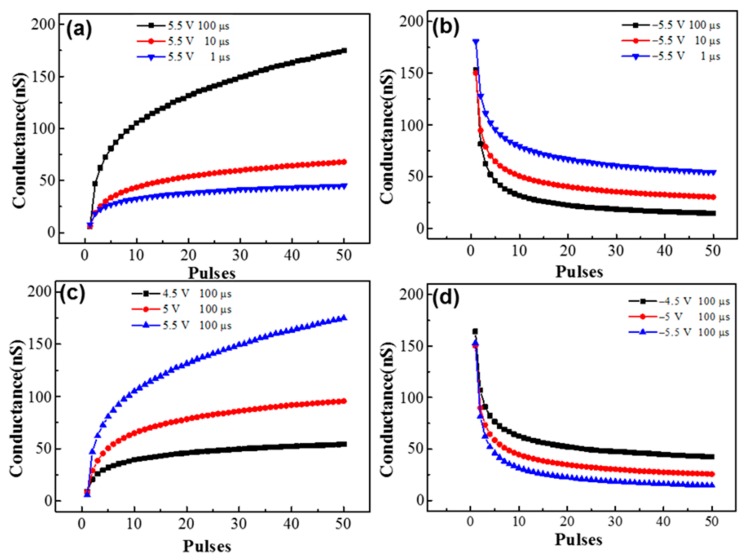

Long-term potentiation/depression (LTP/LTD) is when the synaptic weight can be changed gradually under spiking signals and the changed weight can be maintained from several minutes to years [35]. To evaluate the long-term potentiation/depression of a device, 50 consecutive pulses with different pulse amplitudes and widths are applied to the device, as shown in Figure 4. All the conductance of the device is monitored by 1 V reading voltage. The change of conductance can be modulated by different amplitudes and widths. As shown in Figure 4a,b, the amplitude here was fixed at 5.5 V during potentiation and −5.5 V during depression, with different widths (1 μs, 10 μs, and 100 μs). In addition, Figure 4c,d show the potentiation and depression with a fixed 100 μs width and different amplitudes (potentiation: from 4.5 to 5.5 V; depression: from −4.5 to −5.5 V). With a higher amplitude or larger width, the change of the conductance is increased in both potentiation and depression. For our device, when the pulse amplitude (write voltage) is ~±4.5 V and the pulse width is 1 μs, the write current is around ~10−5 A; thus, the switching energy is 50 pJ per spike. To conclude, the device conductance is continuously increased by positive pulses, which can mimic long-term potentiation. In addition, the device conductance is continuously decreased by negative pulses, which can mimic long-term depression.

Figure 4.

The measured long-term potentiation and long-term depression synaptic function with identical pulses. A total of 50 pulses with 5.5 V pulse amplitude and different pulse widths for (a) potentiation (1 μs, 10 μs, and 100 μs); (b) depression (1 μs, 10 μs, and 100 μs); 50 pulses with 100 μs pulse width and a different pulse amplitude (c) for potentiation (4.5 V, 5 V, and 5.5 V) and (d) for depression (−4.5 V, −5 V, and −5.5 V).

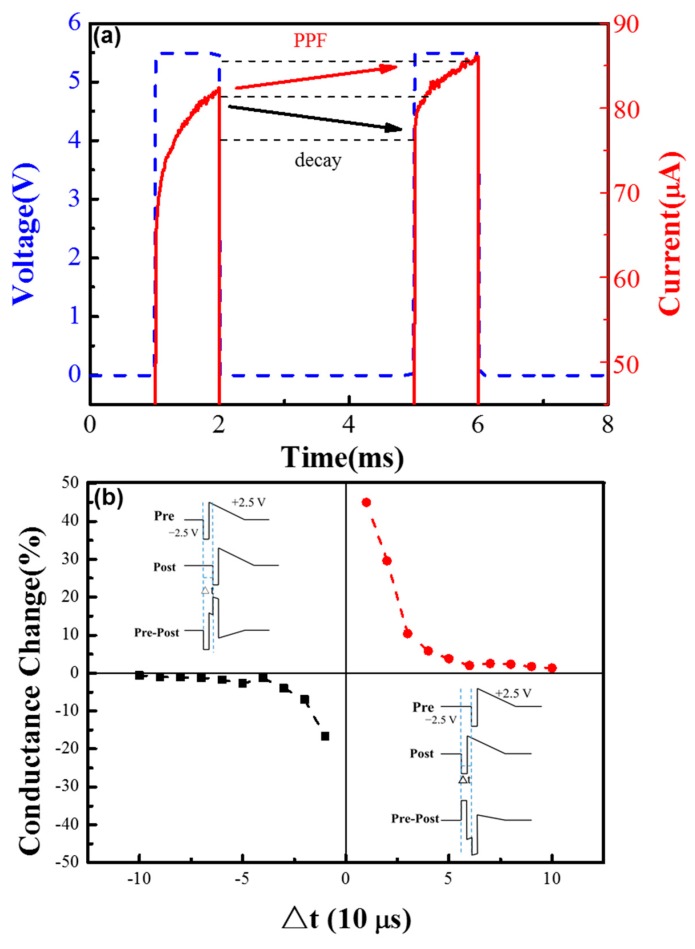

Moreover, the device can emulate other synaptic features, such as paired-pulse facilitation (PPF) and spiking-time-dependent plasticity (STDP), as shown in Figure 5. Most research on artificial synapses focuses on the long-term plasticity, because long-term changes provide a physiological substrate for learning and memory. However, short-term plasticity is also significant, since it supports a variety of computations, such as synaptic filtering, adaptation, and enhancement of transients, decorrelation, burst detection, and sound localization [36]. PPF is an important kind of short-term plasticity. In biological synapses, PPF functions can be described as follows: the second post-synaptic response current becomes larger than the first under two successive spike stimuli, with the interval time of spikes less than recovery time [8]. The experimental demonstration of PPF functions in our device is shown in Figure 5a. When a pair of pulses is applied to the device, the conductance gradually increases during the positive pulses, and the maximum responding current of the second pulse is clearly larger than the first, and a decay phenomenon can be observed during the pulse interval, which is similar to the PPF in the biological system.

Figure 5.

(a) The short-term plasticity: paired-pulse facilitation (PPF) synaptic function of the Ta/TaOx/Al2O3/Pd device; (b) illustration of spike signals and spiking-time-dependent plasticity (STDP) function of the device. The individual pre-synaptic or post-synaptic spike signal is designed as a pair of pulses (−2.5 V, 10 μs pulse and 2.5 V triangle pulse) applied to the top and bottom electrode, respectively.

In biological systems, synaptic weight can be modulated by the temporal relationship of the activity between the pre- and post-synaptic neurons, which is called spiking-time-dependent plasticity (STDP). According to STDP, the change of synaptic weight (ΔW) is a function of the time difference between pre- and post-synaptic activity (Δt). To emulate the STDP function in the device, a pair of pulses acting as the spiking signals with different time intervals is applied to the device. Individual pre-synaptic or post-synaptic spiking signals are designed as a pair of pulses (−2.5 V, 10 μs pulse and a 2.5 V triangle pulse) applied to the top and bottom electrode, respectively, as shown in Figure 5b. It should be noted that an individual positive signal or an individual negative signal is not strong enough to modulate the resistance of the device. As shown in Figure 5b, the effective signal to the device is the pre-synaptic signal minus the post-synaptic signal. When the pre-spike appears before the post-spike (Δt > 0), the conductance (synaptic weight) of the device is enhanced (potentiation), and the change in weight decreases with the increase of Δt. On the contrary, when the pre-spike appears after the post-spike, the conductance of the device depresses and the change of the weight decreases with the increase of Δt. The measurement result shows that the Ta/TaOx/Al2O3/Pd device can emulate the STDP learning rules successfully, which has potential to be used in the spiking neuron network (SNN).

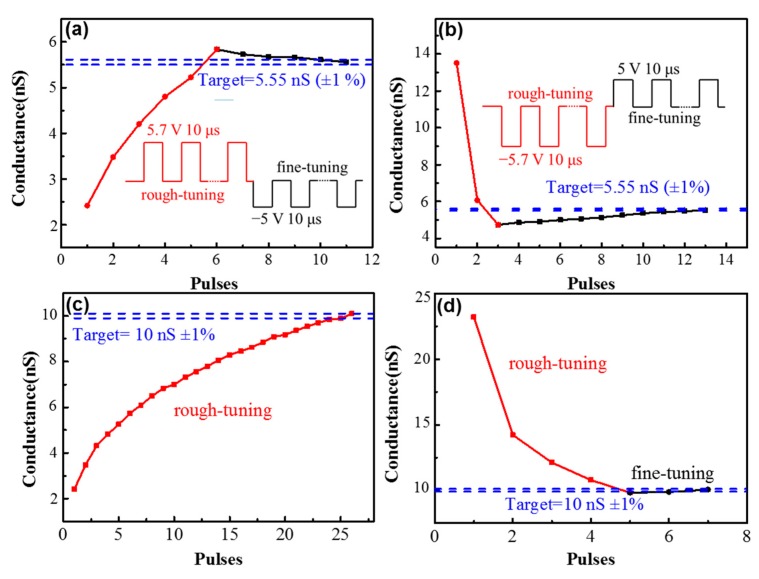

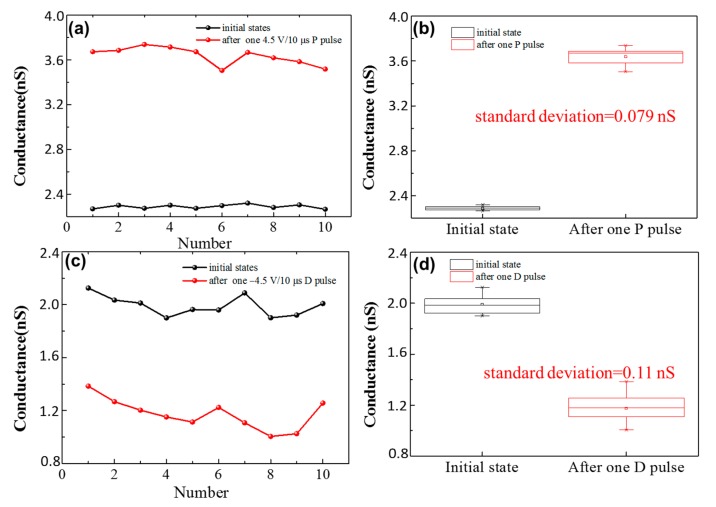

To fully explore bipolar conductance tuning characteristics and demonstrate the potential application of the device in some specific neuromorphic computing systems like ANN, determined target conductance states with different initial states have been tested. As shown in Figure 6a, the initial state is 2.41 nS, after two tuning processes: 5.7 V positive pulses with 10 μs width for rough-tuning, and −5 V negative pulses with 10 μs width for fine-tuning. The target conductance state of 5.5 nS can be obtained with little deviation (<1%). The same target conductance state can also be obtained when the initial conductance state is 13.5 nS, by −5.7 V negative pulses with 10 μs width for rough-tuning and 5 V positive pulses with 10 μs width for fine-tuning, as shown in Figure 6b. As shown in Figure 6c,d, another target conductance state (10 nS), can be obtained with little deviation. It is worth noting that the target conductance states are determined randomly. Based on this result, it can be proven that precision is achieved across a wide dynamic range. Writing error is a standard plot when characterizing resistive switching write noise. The write error of the device has been tested, as shown in Figure 7. A DC sweeping with 100 μA compliance current is used to get nearly the same initial states. Only one programming pulse (4.5 V/10 μs for potentiation and −4.5 V/10 μs for depression) is applied after each DC sweeping. The conductance states (total 10 cycles) are obtained by 1 V reading voltage. As shown in Figure 7b,d the standard deviation is 0.079 nS after one potentiation pulse, and 0.11 nS after one depression pulse, respectively. The dynamic range is around 20 nS under 4.5 V/10 μs training pulses. As a result, the write error is only around 0.6% of the total dynamic range.

Figure 6.

The bipolar conductance tuning to randomly determined target states (5.5 nS ± 1% and 10 nS ± 1%) under pulses with different initial states: (a) the initial state is 2.41 nS, and the target conductance state is obtained by 5.7 V positive pulses for rough-tuning and −5 V negative pulses for fine-tuning; (b) the initial state is 13.5 nS, and the target conductance state is obtained by −5.7 V negative pulses for rough-tuning and 5 V positive pulses for fine-tuning; (c) the initial state is 2.2 nS, and the target state is obtained only by rough-tuning; and (d) the initial state is 23 nS, and the target state is obtained by rough-tuning and fine-tuning methods.

Figure 7.

(a) The conductance states after one 5 V/10 μs P pulse from nearly the same initial states. (b) Conductance distribution from (a), where the standard deviation is 0.079 nS. (c) The conductance states after one −5 V/10 μs P pulse from nearly the same initial states. (d) Conductance distribution from (c), where the standard deviation is 0.11 nS.

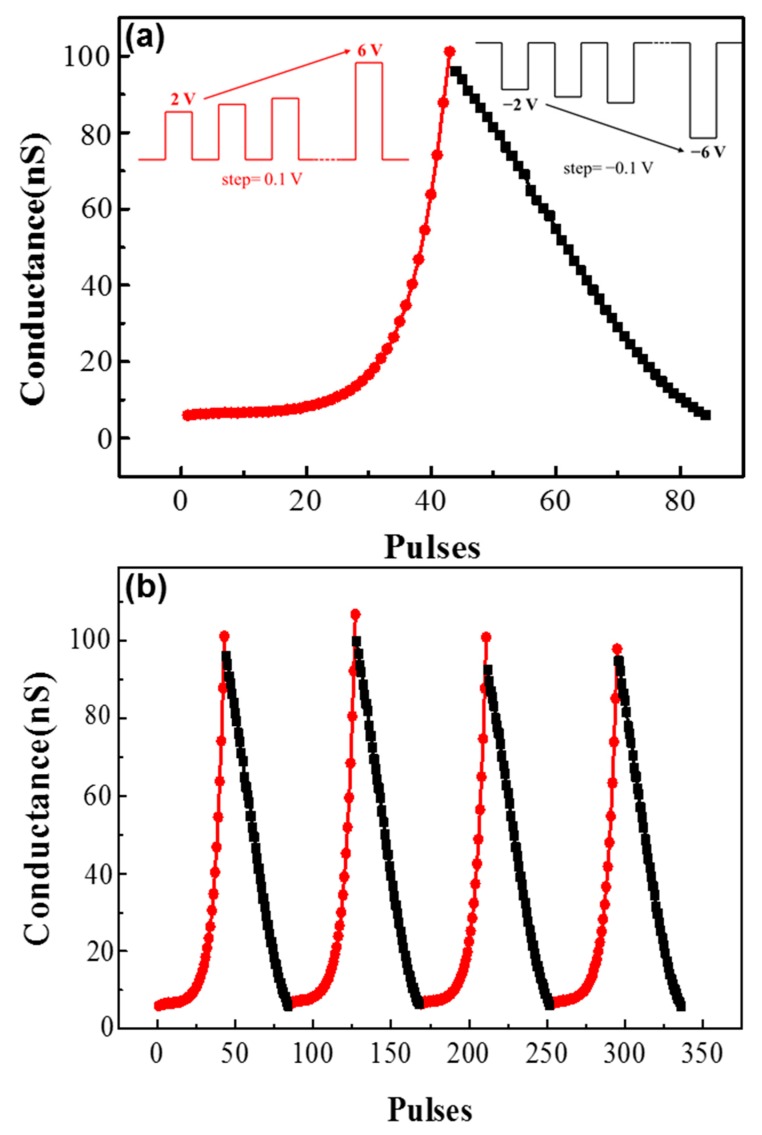

The recognition accuracy of the ANN highly depended on the linearity of the synaptic weight change—i.e., the recognition accuracy is low under high non-linearity [37,38]. However, as shown in Figure 4, the device is highly non-linear. To improve the linearity of the conductance change of the device, a non-identical pulse scheme is adopted, as shown in Figure 8. The training pulses are fixed at width but with increasing amplitudes. The amplitude range of the potentiation process is from 2 to 6 V with 0.1 V steps, and the range of the depression process is from −2 to −6 V with −0.1 V steps. The weight updates are recorded in four training cycles, as shown in Figure 8. The non-linearity factor (NL) has been calculated by NL = average () [39], so the non-linearity factors of the normal training method are 1.09, 1.427, and 1.332 respectively, based on the data in Figure 4a. In addition, the non-linearity factors of the incremental training method are −0.62 for long-term potentiation and 0.13 for long-term depression, based on the data in Figure 8a.

Figure 8.

The measured long-term potentiation/depression synaptic function with non-identical training pulses: (a) the training pulses with increasing amplitudes (potentiation: from 2 to 6 V, 100 μs; depression: from −2 to −6 V, 100 μs); and (b) the weight updates, recorded in four training cycles.

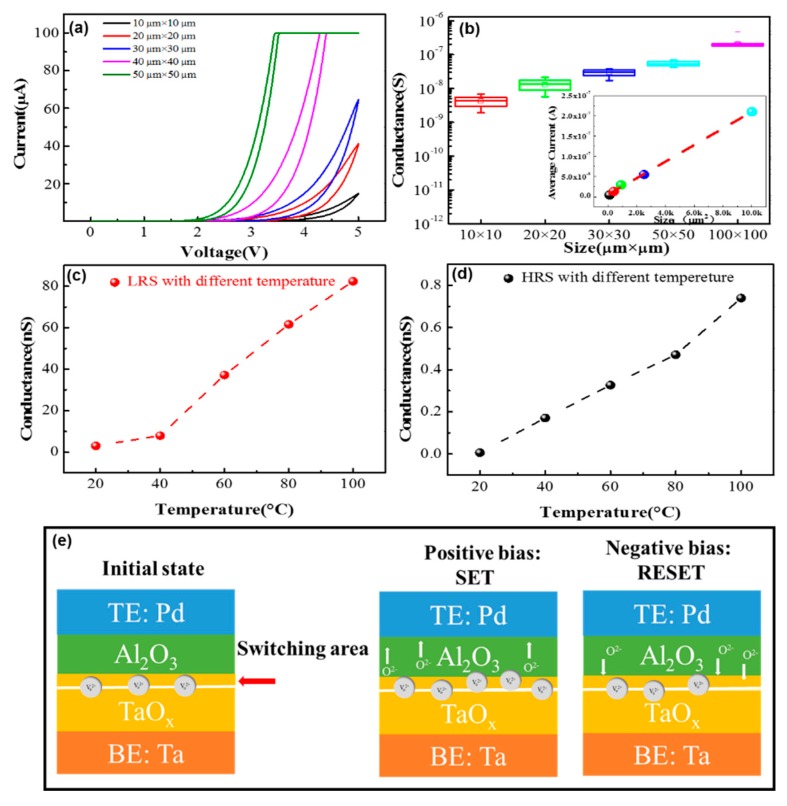

The investigation of the switching mechanism of the device is shown in Figure 9. The conductance of the filamentary memristors mostly depends on the size and morphology of the conductive filament with several nanometers diameter in the device. Thus, the conductance of filamentary memristor does not significantly change with the change of the electrode areas. The I–V curves of the 1st SET process and conductance distribution of 25 different devices at LRS with various electrode areas (from 10 to 100 μm2) are shown in Figure 9a,b, respectively. In Figure 9a, the current level after SET shows a positively proportional relationship with the electrode area. In statistical analysis of 25 devices at LRS in Figure 9b, such a trend can be more clearly seen in the plotting of the conductance with the electrode area. As shown in inset of Figure 9b, the linear fit result confirms that the device conductance scales linearly with the device area. As a result, the switching occurs across the entire electrode area, but not just within a local filament, suggesting a non-filamentary switching mechanism of Ta/TaOx/Al2O3/Pd device. The temperature dependencies of the device conductance at LRS and HRS are studied in Figure 9c,d, respectively. With the increase of temperature, the conductance at both LRS and HRS increases as well, indicating the semiconductor conduction behavior of the device. To explain the switching mechanism of the device, we proposed a simple model [40], shown in Figure 9e. The device can be divided into three parts: a barrier layer (Al2O3), a switching area (interface of Al2O3 and TaOx), and a conductive oxidation layer (TaOx). The switching area is located at the interface of Al2O3 and TaOx. During SET operation, a positive voltage is applied on the top electrode, the oxygen ions in the barrier layer are pulled away from the interface layer, and the materials in the interface are reduced. During RESET operation, a negative voltage is applied on the top electrode, the oxygen ions in the barrier layer are pushed into the interface layer, and the materials in the interface are oxidized. The push-and-pull of the oxygen ions in the surface can change the resistance of the device.

Figure 9.

(a) The I–V curves of the first SET process with different electrode area sizes (from 10 μm × 10 μm to 100 μm × 100 μm). (b) Conductance distribution at LRS with different sized areas (the conductance states are obtained by 1 V reading voltage in 25 different devices) (inset: the linear fit result confirms that the device conductance scales linearly with device areas). (c) Conductance of LRS with different temperatures from 20 to 100 °C; (d) Conductance of HRS with different temperatures from 20 to 100 °C. (e) The schematic of the switching mechanism of the device; the switching area is the interface of TaOx-Al2O3, and the push-and-pull of the oxygen ions in the surface can change the resistance of the interface layer.

To implement neuromorphic computing, the device should be integrated into an array. To operate an array, a half-bias scheme is a common method. However, our device has a low ON/OFF ratio (<100) between the selected voltage and the half-selected voltage, which may cause a sneak path issue during write operation. As a result, it is hard for our device to implement a dense crossbar array without the help of a transistor or selector device. A one transistor one resistor (1T1R) or one selector one resistor (1S1R) structure should be adopted to overcome the sneak path issue during writing operation. The device structure can still be optimized to improve the linearity of the conductance changes and decrease the working voltage. In addition, the detailed non-filamentary switching mechanism in this device needs to be further explored.

4. Conclusions

In this paper, a Ta/TaOx/Al2O3/Pd memristor is fabricated, to be used as artificial synapse. The device shows bipolar analog-resistive switching behavior. Moreover, multilevel conductance states with a satisfying retention time (>1000 s) can be obtained by modulating voltages or compliance currents under DC sweeping mode. Based on the bipolar analog switching, synaptic functions, including long-term potentiation/depression, paired-pulse facilitation, and spiking time dependent plasticity are successfully mimicked. For ANN applications, the determined target conductance, the linearity, and the writing errors are carefully examined. The results suggest that as an artificial synapse, the Ta/TaOx/Al2O3/Pd memristor is a promising candidate for neuromorphic computing.

Author Contributions

Conceptualization: R.W.; data curation: R.W.; formal analysis: X.Z. (Xumeng Zhang); funding acquisition: Q.L.; investigation: R.W. and X.Z. (Xumeng Zhang); project administration: T.S. and Q.L.; resources: X.Z. (Xiaolong Zhao), Z.W. and R.C.; software: W.W. and J.L.; supervision, T.S., S.L., Q.L. and M.L.; visualization: J.W.; writing (original draft): R.W.

Funding

This work is supported by the National High Technology Research Development Program under Grant No. 2017YFB0405603; and the National Natural Science Foundation of China under Grant Nos. 61521064, 61732020, 61751401, and 61522408.

Conflicts of Interest

The authors declare no conflict of interest.

References

- 1.Fusi S., Annunziato M., Badoni D., Salamon A., Amit D.J. Spike-driven synaptic plasticity: Theory, simulation, VLSI implementation. Neural Comput. 2000;12:2227–2258. doi: 10.1162/089976600300014917. [DOI] [PubMed] [Google Scholar]

- 2.Laughlin S.B., van Steveninck R.R.D., Anderson J.C. The metabolic cost of neural information. Nat. Neurosci. 1998;1:36–41. doi: 10.1038/236. [DOI] [PubMed] [Google Scholar]

- 3.Saremi M. Ph.D. Thesis. Arizona State University; Tempe, AZ, USA: 2017. Modeling and Simulation of the Programmable Metallization Cells (PMCs) and Diamond-Based Power Devices. [Google Scholar]

- 4.Strukov D.B., Snider G.S., Stewart D.R., Williams R.S. The missing memristor found. Nature. 2008;453:80–83. doi: 10.1038/nature06932. [DOI] [PubMed] [Google Scholar]

- 5.Saremi M. A physical-based simulation for the dynamic behavior of photodoping mechanism in chalcogenide materials used in the lateral programmable metallization cells. Solid State Ion. 2016;290:1–5. doi: 10.1016/j.ssi.2016.04.002. [DOI] [Google Scholar]

- 6.Saremi M. Carrier mobility extraction method in ChGs in the UV light exposure. Micro Nano Lett. 2016;11:762–764. doi: 10.1049/mnl.2016.0132. [DOI] [Google Scholar]

- 7.Jo S.H., Chang T., Ebong I., Bhadviya B.B., Mazumder P., Lu W. Nanoscale Memristor Device as Synapse in Neuromorphic Systems. Nano Lett. 2010;10:1297–1301. doi: 10.1021/nl904092h. [DOI] [PubMed] [Google Scholar]

- 8.Zhang X.M., Liu S., Zhao X.L., Wu F.C., Wu Q.T., Wang W., Cao R.R., Fang Y.L., Lv H.B., Long S.B. Emulating short-term and long-term plasticity of bio-synapse based on cu/a-Si/Pt memristor. IEEE Electron Device Lett. 2017;38:1208–1211. doi: 10.1109/LED.2017.2722463. [DOI] [Google Scholar]

- 9.Yu S.M., Wu Y., Jeyasingh R., Kuzum D.G., Wong H.S.P. An electronic synapse device based on metal oxide resistive switching memory for neuromorphic computation. IEEE Trans. Electron Devices. 2011;58:2729–2737. doi: 10.1109/TED.2011.2147791. [DOI] [Google Scholar]

- 10.Yu S.M., Gao B., Fang Z., Yu H.Y., Kang J.F., Wong H.S.P. A low energy oxide-based electronic synaptic device for neuromorphic visual systems with tolerance to device variation. Adv. Mater. 2013;25:1774–1779. doi: 10.1002/adma.201203680. [DOI] [PubMed] [Google Scholar]

- 11.Saremi M., Rajabi S., Barnaby H.J., Kozicki M.N. The effects of process variation on the parametric model of the static impedance behavior of programmable metallization cell (PMC) MRS Proc. 2014;1692 doi: 10.1557/opl.2014.521. [DOI] [Google Scholar]

- 12.Suri M., Bichler O., Querlioz D., Cueto O., Perniola L., Sousa V., Vuillaume D., Gamrat C., DeSalvo B. Phase change memory as synapse for ultra-dense neuromorphic systems: Application to complex visual pattern extraction; Proceedings of the 2011 IEEE International Electron Devices Meeting (IEDM); Washington, DC, USA. 5–7 December 2011. [Google Scholar]

- 13.Kaneko Y., Nishitani Y., Ueda M. Ferroelectric artificial synapses for recognition of a multishaded image. IEEE Trans. Electron Devices. 2014;61:2827–2833. doi: 10.1109/TED.2014.2331707. [DOI] [Google Scholar]

- 14.Jerry M., Chen P.Y., Zhang J.C., Sharma P., Ni K., Yu S.M., Datta S. Ferroelectric FET analog synapse for acceleration of deep neural network training; Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM); San Francisco, CA, USA. 2–6 December 2017. [Google Scholar]

- 15.Oh S., Kim T., Kwak M., Song J., Woo J., Jeon S., Yoo I.K., Hwang H. HfZrOx-based ferroelectric synapse device with 32 levels of conductance states for neuromorphic applications. IEEE Electron Device Lett. 2017;38:732–735. doi: 10.1109/LED.2017.2698083. [DOI] [Google Scholar]

- 16.Suri M., Querlioz D., Bichler O., Palma G., Vianello E., Vuillaume D., Gamrat C., DeSalvo B. Bio-inspired stochastic computing using binary CBRAM synapses. IEEE Trans. Electron Devices. 2013;60:2402–2409. doi: 10.1109/TED.2013.2263000. [DOI] [Google Scholar]

- 17.Yan X., Zhang L., Chen H., Li X., Wang J., Liu Q., Lu C., Chen J., Wu H., Zhou P. Graphene oxide quantum dots based memristors with progressive conduction tuning for artificial synaptic learning. Adv. Funct. Mater. 2018;28:1803728. doi: 10.1002/adfm.201803728. [DOI] [Google Scholar]

- 18.Shi Y., Liang X., Yuan B., Chen V., Li H., Hui F., Yu Z., Yuan F., Pop E., Wong H.S.P., et al. Electronic synapses made of layered two-dimensional materials. Nat. Electron. 2018;1:458. doi: 10.1038/s41928-018-0118-9. [DOI] [Google Scholar]

- 19.Yu S.M., Gao B., Fang Z., Yu H.Y., Kang J.F., Wong H.S.P. Stochastic learning in oxide binary synaptic device for neuromorphic computing. Front. Neurosci. 2013;7 doi: 10.3389/fnins.2013.00186. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 20.Garbin D., Vianello E., Bichler O., Rafhay Q., Gamrat C., Ghibaudo G., DeSalvo B., Perniola L. HfO2-based OxRAM devices as synapses for convolutional neural networks. IEEE Trans. Electron Devices. 2015;62:2494–2501. doi: 10.1109/TED.2015.2440102. [DOI] [Google Scholar]

- 21.Bill J., Legenstein R. A compound memristive synapse model for statistical learning through STDP in spiking neural networks. Front. Neurosci. 2014;8:412. doi: 10.3389/fnins.2014.00412. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 22.Piccolboni G., Molas G., Portal J.M., Coquand R., Bocquet M., Garbin D., Vianello E., Carabasse C., Delaye V., Pellissier C., et al. Investigation of the potentialities of Vertical Resistive RAM (VRRAM) for neuromorphic applications; Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM); Washington, DC, USA. 7–9 December 2015. [Google Scholar]

- 23.Yu S.M., Gao B., Fang Z., Yu H.Y., Kang J.F., Wong H.S.P. A neuromorphic visual system using RRAM synaptic devices with sub-pJ energy and tolerance to variability: Experimental characterization and large-scale modeling; Proceedings of the 2012 IEEE International Electron Devices Meeting (IEDM); San Francisco, CA, USA. 10–13 December 2012. [Google Scholar]

- 24.Yan X., Zhao J., Liu S., Zhou Z., Liu Q., Chen J., Liu X.Y. Memristor with Ag-cluster-doped TiO2 films as artificial synapse for neuroinspired computing. Adv. Funct. Mater. 2018;28 doi: 10.1002/adfm.201705320. [DOI] [Google Scholar]

- 25.Wang I.T., Chang C.C., Chiu L.W., Chou T.Y., Hou T.H. 3D Ta/TaOx/TiO2/Ti synaptic array and linearity tuning of weight update for hardware neural network applications. Nanotechnology. 2016;27 doi: 10.1088/0957-4484/27/36/365204. [DOI] [PubMed] [Google Scholar]

- 26.Jeong Y., Kim S., Lu W.D. Utilizing multiple state variables to improve the dynamic range of analog switching in a memristor. Appl. Phys. Lett. 2015;107 doi: 10.1063/1.4934818. [DOI] [Google Scholar]

- 27.Wu W., Wu H.Q., Gao B., Deng N., Yu S.M., Qian H. Improving analog switching in HfOx-based resistive memory with a thermal enhanced layer. IEEE Electron Device Lett. 2017;38:1019–1022. doi: 10.1109/LED.2017.2719161. [DOI] [Google Scholar]

- 28.Shi T., Wu J.F., Liu Y., Yang R., Guo X. Behavioral plasticity emulated with lithium lanthanum titanate-based memristive devices: Habituation. Adv. Electron. Mater. 2017;3:10–1002. doi: 10.1002/aelm.201700046. [DOI] [Google Scholar]

- 29.Geoffrey W., Burr R.M.S., Abu S., Sangbum K., Seyoung K., Severin S., Kumar V., Masatoshi I., Pritish N., Alessandro F., et al. Neuromorphic computing using non-volatile memory. Adv. Phys. X. 2017;2:89–124. doi: 10.1080/23746149.2016.1259585. [DOI] [Google Scholar]

- 30.Yang R., Terabe K., Yao Y., Tsuruoka T., Hasegawa T., Gimzewski J.K., Aono M. Synaptic plasticity and memory functions achieved in a WO3−x-based nanoionics device by using the principle of atomic switch operation. Nanotechnology. 2013;24:384003. doi: 10.1088/0957-4484/24/38/384003. [DOI] [PubMed] [Google Scholar]

- 31.Pan R.B., Li J., Zhuge F., Zhu L.Q., Liang L.Y., Zhang H.L., Gao J.H., Cao H.T., Fu B., Li K. Synaptic devices based on purely electronic memristors. Appl. Phys. Lett. 2016;108 doi: 10.1063/1.4939436. [DOI] [Google Scholar]

- 32.Wang Y.F., Lin Y.C., Wang I.T., Lin T.P., Hou T.H. Characterization and modeling of nonfilamentary Ta/TaOx/TiO2/Ti analog synaptic device. Sci. Rep. 2015;5 doi: 10.1038/srep10150. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 33.Shi T., Yang R., Guo X. Coexistence of analog and digital resistive switching in BiFeO3-based memristive devices. Solid State Ion. 2016;296:114–119. doi: 10.1016/j.ssi.2016.09.001. [DOI] [Google Scholar]

- 34.Sun Y., Xu H., Wang C., Song B., Liu H., Liu Q., Liu S., Li Q. A Ti/AlOx/TaOx/Pt analog synapse for memristive neural network. IEEE Electron Device Lett. 2018;39:1298–1301. doi: 10.1109/LED.2018.2860053. [DOI] [Google Scholar]

- 35.Lynch M.A. Long-term potentiation and memory. Physiol. Rev. 2004;84:87–136. doi: 10.1152/physrev.00014.2003. [DOI] [PubMed] [Google Scholar]

- 36.Abbott L.F., Regehr W.G. Synaptic computation. Nature. 2004;431:796–803. doi: 10.1038/nature03010. [DOI] [PubMed] [Google Scholar]

- 37.Jang J.W., Park S., Burr G.W., Hwang H., Jeong Y.H. Optimization of conductance change in Pr1−xCaxMnO3-Based synaptic devices for neuromorphic systems. IEEE Electron Device Lett. 2015;36:457–459. doi: 10.1109/LED.2015.2418342. [DOI] [Google Scholar]

- 38.Woo J., Yu S. Resistive memory-based analog synapse: The pursuit for linear and symmetric weight update. IEEE Nanotechnol. Mag. 2018;12:36–44. doi: 10.1109/MNANO.2018.2844902. [DOI] [Google Scholar]

- 39.Bae J.-H., Lim S., Park B.-G., Lee J.-H. High-density and near-linear synaptic device based on a reconfigurable gated Schottky diode. IEEE Electron Device Lett. 2017;38:1153–1156. doi: 10.1109/LED.2017.2713460. [DOI] [Google Scholar]

- 40.Luo Q., Zhang X., Hu Y., Gong T., Xu X., Yuan P., Ma H., Dong D., Lv H., Long S. Self-rectifying and forming-free resistive-switching device for embedded memory application. IEEE Electron Device Lett. 2018;39:664–667. doi: 10.1109/LED.2018.2821162. [DOI] [Google Scholar]