Abstract

The change of electrical performance of amorphous SiZnSnO thin film transistors (a-SZTO TFTs) has been investigated depending on various metal capping layers on the channel layer by causing different contact property. It was confirmed that the change of electrical characteristics was sensitively dependent on the change of the capping layer materials on the same channel layer between the source/drain electrodes. This sensitive change in the electrical characteristics is mainly due to different work function of metal capping layer on the channel layer. The work function of each capping layer material has been analyzed and derived by using Kelvin probe force microscopy and compared with the energy bandgap of the SZTO layer. When the work function of the capping layer is larger than that of the channel layer, electrons are depleted from the channel layer to the capping layer. On the contrary, in the case of using a material having a work function smaller than that of the channel layer, the electrical characteristics were improved because electrons were injected into the channel layer. Based on depletion and injection mechanism caused by different contact barrier between metal capping layer and channel layer, NOT, NAND, and NOR logic circuits have been implemented simply by changing metal capping layer on the channel layer.

Introduction

Amorphous oxide semiconductors (AOSs) have been applied to the next-generation electric and electronic industrial fields in recent decades. The AOS can be used as an active channel layer of thin film transistors (TFTs), which can be applied directly to organic light-emitting diodes and/or active-matrix liquid crystal display, which is a recent issue1–4. This is because AOS is composed of metal-oxide (M-O) network and the conduction band is composed of spherical ns orbitals, which shows high carrier mobility despite being amorphous. In addition, the AOS has a wide bandgap of 3 eV or more, which is transparent, and has a merit that can be applied widely from an insulator to a conductive materials5,6. AOS is known to control the density of state (DOS) in the energy bandgap by controlling the oxygen vacancy (Vo) or the hydrogen content in the thin film7,8. To control this, an oxygen vacancy suppressor substance is added or an additional treatment process is used. Lee et al. recently reported the change of energy bandgap when Si was added on the ZTO (SZTO) system by DOS and X-ray photoelectron spectroscopy (XPS)9,10. Based on the reports, SZTO showed a systematic reduction of DOS and an increase in energy bandgap as Si content increased. This steady AOS study has contributed greatly to improving the quality of the thin film. When Vo is suppressed, the stability under various stresses, such as negative bias temperature illumination stress is improved but the conduction characteristics are reduced, which is complementary to each other11,12. Therefore, studies for improving electrical characteristics while securing stability have been actively conducted. Recently, many groups including Kim et al., Zan et al., and Choi et al. proposed a capping structure13–15 to secure the electrical characteristics and to improve the stability by depositing a conductive material between source/drain electrode. The capping layer structure improves the electrical properties and the stability of TFTs which could be explained by several mechanisms. According to the report of Kim et al., the electrical characteristics were improved by the movement of electrons during the contact between the capping layer and the active channel layer13. Choi et al. reported using TCAD simulation the stability is improved with flowing the current flow in ω-shape by low-resistivity capping layer15. In this capping structure, studies on electrical properties and stability have been progressed steadily through a simple process, but studies on various active channel layer materials and capping layer materials are still lacking.

Here, we report the change of the electrical characteristics of SZTO active channel layer among AOS candidates by varying capping layer materials from the traditional metallic materials to the oxide-based electrode materials as well as transparent conductive oxide (TCO). The electron injection or depletion phenomenon by adopting different capping layer were analyzed by using different energy band gap and work function difference. We have also implemented the NOT, NAND, and NOR logic circuits by controlling electrical characteristics simply the use of different capping layer.

Results and Discussion

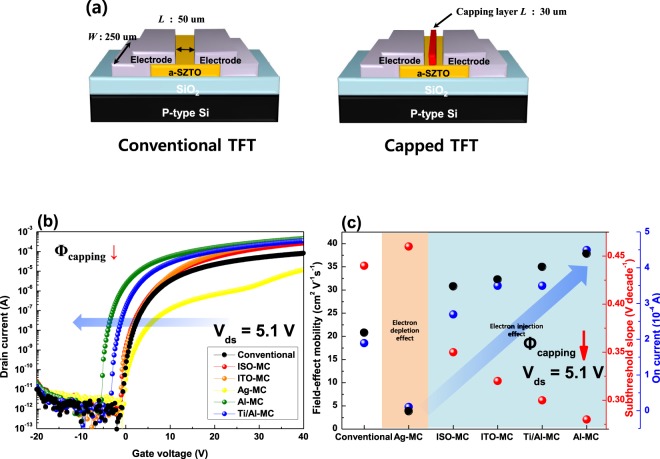

Figure 1(b,c) show transfer characteristic and electrical properties of SZTO-TFT with different capping layers. Other electrical characteristics, such as threshold voltage (Vth), on-current (Ion), and on/off-current ratio (Ion/off), are summarized in Table 1. The Vth of the TFTs were calculated, which was the gate voltage at Ids of 1 nA current level. Also, the field-effect mobility (µfe) was calculated by using the following Equation9:

| 1 |

where gm is the trans-conductance, COX is the oxide capacitance of the gate dielectric, Vds is the drain to source voltage and W and L are channel width and length. In this manuscript we use Vds, W and L to 5.1 V, 250 μm and 50 μm, respectively. In the case of the capping layer, the same channel L value was set to extract the µfe same as in our previous study15. In ref. 15, we analyzed the current path of the capping layer and further experiment has been conducted for the channel L. However, the electrical characteristics were not improved when a short L-TFT, such as the channel length except the portion occupied by the capping layer above the channel layer, was fabricated. In addition, the current path was formed in the ω-shape, which is not due to a phenomenon, such as a short-channel effect. Therefore, we extracted µfe of the capped-TFT by fixing an L value of 50 μm, for the comparison of the same conventional-TFT. The capped-TFTs have the same source/drain electrode and exhibit a change in electrical properties as the only capping layer material on top of the SZTO layer changes. We have confirmed that the change of the electrical performance could be explained by two different types depending on the capping layer based on the conventional device. First, when Ag is used as the capping layer, μfe, on-current (Ion), and subthreshold slope (SS) are deteriorated more than those of the conventional-TFT. The deterioration of these properties is mainly due to the electron-depletion phenomenon in which electrons in the SZTO layer move to the capping layer13. Because of this phenomenon, degradation of electrical properties, such as μfe of 3.85 cm2V−1s−1, Ion of 1.2 × 10−5 A, and SS of 0.46 V decade−1 has been observed. On the contrary, the electrical characteristics tend to be improved systematically depending on the capping layer, such as ISO, ITO, Ti/Al, and Al. This effect is mainly due to the electron-injection phenomena where electrons move from the capping layer materials to the conduction band of the SZTO layer. It has been clearly observed that the electrical characteristics of the TFTs have been systematically improved of μfe (20.79 to 37.84 cm2V−1s−1), Ion (1.9 × 10−4 to 4.5 × 10−4 A), and SS (0.44 to 0.28 V decade−1) by adopting capping layer as the electron-injection phenomenon occurs. In the case of Vth, it was confirmed that threshold voltages move from 0.65 to −4.69 V in the negative direction because of the electron injection into the SZTO layer. As a result, it was confirmed that different capping layers strongly change the electrical characteristics of the TFT, which can be analyzed by the work function difference between the channel layer and the capping layer material. We have conducted the energy band diagram analysis depending on various conductive capping layer to investigate the effect of contact potential appearing in the SZTO layer and capping layer resulting in the change of electrical performance seriously in TFTs.

Figure 1.

(a) Schematic view of conventional-TFT and capped-TFT. (b) Transfer characteristic and (c) electrical performance of TFTs with different capping layer.

Table 1.

The electrical properties and work function of a-SZTO TFTs for different capping layer materials.

| Capping layer | Vth (V) | Ion (A) | I on/off | µFE (cm2V−1s−1) | SS (Vdecade−1) | Φ (eV) |

|---|---|---|---|---|---|---|

| Conventional | 0.65 | 1.9 × 10−4 | 1.6 × 109 | 20.79 | 0.44 | 4.53 |

| Ag capped | 1.82 | 1.2 × 10−5 | 2.0 × 107 | 3.85 | 0.46 | 4.64 |

| ISO capped | −0.02 | 2.7 × 10−4 | 6.7 × 108 | 30.79 | 0.35 | 4.49 |

| ITO capped | −0.18 | 3.5 × 10−4 | 2.3 × 109 | 32.27 | 0.32 | 4.51 |

| Ti/Al capped | −2.35 | 3.5 × 10−4 | 2.9 × 109 | 35.00 | 0.30 | 3.92 |

| Al capped | −4.69 | 4.5 × 10−4 | 3.0 × 109 | 37.84 | 0.28 | 3.79 |

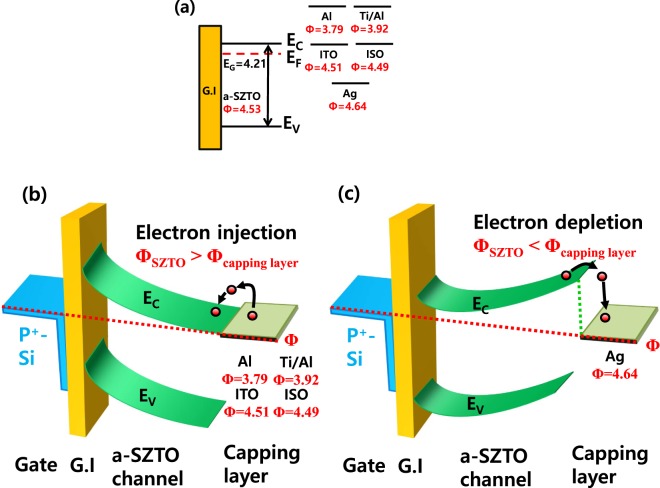

Figure 2 shows the energy band diagram for the SZTO-TFT depending on various capping layers with different energy band gap in thermal equilibrium state. In our previous research, we analyzed different Si content can change the energy band of ZTO system systematically by using ultraviolet photoelectron spectroscopy (UPS), high resolution electron energy loss spectroscopy (HR-EELS), and Kelvin probe force microscopy (KPFM) methods16. In ref. 16, for the ZTO system with a Si content of 0.5 wt.%, the bandgap was 4.21 eV and the work function (Φ) was 4.53 eV. We also measured the Φ of the capping layer materials using the KPFM method. The contact potential difference during the measurement was calibrated based on Pt/Ir (Tip Φ = 4.91 eV)17,18. According to KPFM results, the materials used in the capping layer showed Φ values of Al of 3.79, Ti/Al of 3.92, ISO of 4.49, ITO of 4.51, and Ag of 4.64 eV. In addition, the standard deviation of all capping materials was about 0.012 eV. We have extracted the energy band diagram for the two types of the electron-injection and electron-depletion as shown in Fig. 2 (b,c), respectively. When ITO, ISO, Ti/Al, and Al materials are used as the capping layer, electron-injection occurs because the Φ of the capping layer material is smaller than the Φ of the channel layer (ΦSZTO > Φcapping layer)13. Therefore, it could be expected that as the Φ of the capping layer material becomes smaller, the movement of electrons from the capping layer to the SZTO layer becomes smooth and the electrical characteristics are improved. In the case of metal-based capping layers among the materials exhibiting electron-injection phenomena, the resistivity does not show a large difference (≈10−6 Ω∙cm). Nevertheless, it appears that the improvement of the electrical performance is due to the electron-injection phenomenon. However, in the case of oxide-based capping layers such as ITO and ISO, the ISO capped-TFT electron-injection phenomenon occurs easily than ITO Because the work function of ISO is smaller than that of ITO, but the resistivity is higher than that of ITO. Therefore, it should be considered that ITO capped-TFT shows better electrical performance than ISO capped-TFT due to the difference of the resistivity even though small work function. For Ag capped-TFT case, however, when the Φ of the capping layer is larger than the Φ of the SZTO layer (ΦSZTO < Φcapping layer), electrons of the capping layer become difficult to inject into the SZTO layer because the barrier exists and rather the electrons of the SZTO layer move to the capping layer, so that the SZTO layer loses electrons and provides a lower electrical performance than the conventional-TFT. By adopting two types of electron-injection and electron-depletion capped TFTs, we have implemented two types of NOT logic circuit (or inverters).

Figure 2.

Energy band diagram of SZTO-TFTs with different capping layer in thermal equilibrium. (a) non-contact, (b) electron-injection model (when ΦSZTO > Φcapping layer), and (c) electron-depletion model (when ΦSZTO < Φcapping layer).

Figure 3 shows the voltage transfer characteristic (VTC) depending on the VDD from 1 to 5 V of the fabricated NOT logic circuits. We fabricated the model of NOT logic circuit as a depletion-load type, and the capped-TFT with Al capping layer as the lower Vth value than other capped-TFT was commonly used as a depletion mode (D-mode), and the enhancement mode (E-mode) has been designed by using the capped-TFT using an ITO capping layer or Ti/Al capping layer. In general, the operation of depletion-load type NOT logic circuit can be roughly divided into three regions. In region I, when input voltage (VIN) is lower than the driving voltage of the E-mode TFT, VDD is output to output voltage (VOUT). In region II, when VIN is greater than or equal to the driving voltage of the E-mode TFT, the circuit has full-swing characteristics and the VOUT drops to near 0 V. In the subsequent region III, the E-mode TFT exhibits an operating characteristic in which the VOUT is maintained at 0 V as the TFT is fully opened19. The D-mode TFT always maintains the on-state when the circuit is driven as follows20. This is because the gate electrode and the source electrode connected each other in the case of the D-mode TFT. It can be seen that both of the fabricated NOT logic circuits exhibit full-swing characteristics. In addition, voltage gain (|δVOUT/δVIN|) is extracted through VTC and summarized in Table 2. It was confirmed that the voltage gain of the NOT logic circuit using the Ti/Al capped-TFT as the E-mode TFT shows a value higher than that of the ITO capped-TFT with respect to the VDD change. The maximum voltage gain can be seen when Ti/Al capped-TFT and ITO capped-TFT are 12.83 and 6.51, respectively, when VDD is 5 V. The difference in voltage gain strongly depends on the SS value of the E-mode TFT. It was observed that the depletion-load type NOT logic circuit is sensitive to the SS value rather than the μfe of the E-mode TFT21. Therefore, we can analyze that Ti/Al capped-TFT with better SS value can show higher voltage gain value in this case. We have fabricated more complex NAND and NOR logic circuits using Ti/Al capped-TFT, which exhibits high performances in NOT logic circuit.

Figure 3.

The voltage transfer characteristic (VTC) curves and voltage gain of the NOT logic circuit using different E-mode TFT, obtained for various supply voltage (VDD) from 1 to 5 V.

Table 2.

The maximum voltage gain values of the NOT logic circuit for VDD from 1 to 5V.

| VDD E-mode TFT | 1 V | 2 V | 3 V | 4 V | 5 V |

|---|---|---|---|---|---|

| Ti/Al capped-TFT | 0.48 | 1.71 | 4.14 | 8.79 | 12.83 |

| ITO capped-TFT | 0.28 | 0.87 | 1.93 | 3.60 | 6.51 |

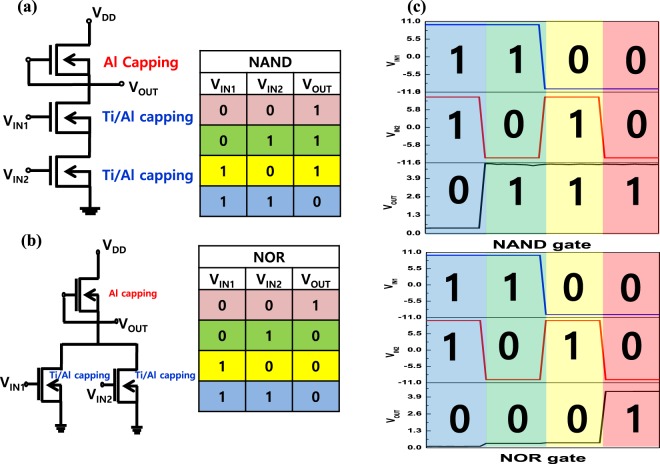

Figure 4 shows the circuit diagram, truth table, and output characteristics of NAND and NOR fabricated. We connected the previously configured NOT logic simply by wire bonding using an additional Ti/Al capped-TFT as the E-mode-TFT2. In the case of the NAND logic circuit, the two E-mode-TFTs are connected in series and the NOR logic circuit can be connected in parallel22. In the case of wire bonding, we may report on simple output characteristics in this manuscript, although it may affect the logic circuit characteristics by connecting each device using additional wiring. However, these problems will not be serious because they can be simply processed by forming independent gates. In addition, after VDD was fixed at 5 V, we applied a voltage of −10 V and 10 V, which could show sufficient operating characteristics for each of VIN1 and VIN2. The VOUT was output close to the VDD setting value of 5 V (digital signal of “1 (high)”), and it was observed that the VOUT drop to 0 V (digital signal of “0 (low)”) when the E-mode TFTs were operated. As a result, when we configure the NAND and NOR logic circuits simply using different capping layer, it was confirmed that the same operation as the truth table is normally observed.

Figure 4.

NAND (a) and (b) NOR (b) logic circuits, showing circuit diagram and logic table. (c) VOUT cycling of NAND and NOR circuits, for prescribed VIN sequence.

Conclusion

In summary, we have investigated the changes in electrical properties for TFTs with different capping layer materials. It has been observed that the change of electrical characteristics is sensitively due to the difference in work function of the capping layer as compared with the conventional-TFT. Based on the work function of the channel layer, electron-injection and electron-depletion have been found, depending on the work function of the capping layer materials. As the work function of the capping layer becomes smaller, the electrical performance of TFT has been improved easily by electron-injection phenomena. In addition, when the best electrical characteristics were shown, TFTs using Al as a capping layer showed μfe of 37.84 cm2V−1s−1, Ion of 4.5 × 10−4 A, and SS of 0.28 Vdecade−1. Since the electrical characteristics could be changed sensitively depending on the change of the capping layer, we could easily fabricate the logic circuit. NOT logic circuit showed high voltage gain of 12.83 at VDD = 5 V when using Ti/Al capped-TFT as E-mode. In the case of NAND and NOR logic circuits, it is confirmed that the output characteristics according to the inputs are driven in the same manner as the truth table. These results can be directly applied to next-generation thin film logic circuits and electronic devices.

Methods

Device fabrication

All TFTs choose the substrate that heavily doped p+-type silicon wafer (resistivity 0.001–0.002 Ω/cm), which has 200 nm thick SiO2depositedby thermal oxidation process. The substrate was cleaned in acetone, methanol, and deionized water using conventional ultrasonic cleaning method. The powder mixture of 99.99% pure ZnO, SnO2, and SiO2 was used as a SZTO (SiO2: ZnO: SnO2 = 0.5: 65: 35 wt.%) target. We fixed the thickness of the channel layer to 24 nm to analyze the effect of the capping layer. The SZTO channel layer was deposited using RF-sputtering process. The deposition condition was RF power density of 60 W, working pressure of 3 mTorr, and the oxygen and argon ratio of 40: 1 at room temperature. The SZTO-TFTs with inverted staggered bottom gate and top source/drain electrode structure were fabricated by conventional photo-lithography and wet-etching. After channel patterned, SZTO thin films were annealed at 500 oC in air ambient for 2 hrs. Thereafter, the source/drain electrodes were commonly fabricated using the Ti/Al material by lift-off process and e-beam/thermal evaporation. The capping layer was fabricated by changing the material using the same method as the source/drain process. The materials used in the capping layer are Ag, ISO, ITO, Ti/Al, and Al, respectively. The conventional TFT W/L ratio of the channel was 250 μm/50 μm and capping layer L was 30 μm, as shown in Fig. 1(a).

Characterization

The work function of each capping layer materials were measured by using Kelvin probe force microscopy (KPFM) The electrical characteristics were measured using a semiconductor parameter analyzer (EL 423, ELECS Co.) at room temperature in a dark box.NAND and NOR logic circuit performance was characterized by using a triple output DC power supply (E3631A, Keysight Co.) to supply the input voltage VIN, with VOUT recorded by the semiconductor parameter analyser.

Acknowledgements

This work was supported by the Korea Institute of Energy Technology Evaluation and Planning (KETEP) and the Ministry of Trade, Industry & Energy (MOTIE) of the Republic of Korea (No. 20172010104940). The Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (NRF-2017R1D1A3B06033837).

Author Contributions

S.Y.L. and S.K. designed and executed the study and analysed the data; B.H.L. and A.S. performed the experiments and data analysed using K.P.F.M.; B.H.L. analysed the data and wrote the main manuscript text. All authors reviewed the manuscript.

Competing Interests

The authors declare no competing interests.

Footnotes

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

References

- 1.Hosono. H. Ionic amorphous oxide semiconductors: Materials design, carrier transport, and device application. J. Non-Cryst. Solids. 2006;352:851–858. doi: 10.1016/j.jnoncrysol.2006.01.073. [DOI] [Google Scholar]

- 2.Nomura K, et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature (London) 2004;432:488. doi: 10.1038/nature03090. [DOI] [PubMed] [Google Scholar]

- 3.Fernandes C, et al. A Sustainable Approach to Flexible Electronics with Zinc-Tin Oxide Thin-Film Transistors. Adv. Electron. Mater. 2018;4:1800032. doi: 10.1002/aelm.201800032. [DOI] [Google Scholar]

- 4.Kim W-G, et al. High-pressure Gas Activation for Amorphous Indium-Gallium-Zinc-Oxide Thin-Film Transistors at 100 oC. Sci. Rep. 2016;6:23039. doi: 10.1038/srep23039. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 5.Ma P, et al. Low voltage operation of IGZO thin film transistors enabled by ultrathin Al2O3 gate dielectric. Appl. Phys. Lett. 2018;112:023501. doi: 10.1063/1.5003662. [DOI] [Google Scholar]

- 6.Wang Y, et al. Experimental and theoretical analysis of H and Ti co-doped ZnO transparent conductive films. Ceramics International. 2017;43:5396–5402. doi: 10.1016/j.ceramint.2016.12.112. [DOI] [Google Scholar]

- 7.Choi JY, et al. Effect of hafnium addition on Zn-Sn-O thin film transistors fabricated by solution process. Appl. Phys. Lett. 2012;100:022109. doi: 10.1063/1.3669700. [DOI] [Google Scholar]

- 8.Bang J, et al. Hydrogen anion and subgap states in amorphous In-Ga-Zn-O thin films for TFT applications. Appl. Phys. Lett. 2017;110:232105. doi: 10.1063/1.4985627. [DOI] [Google Scholar]

- 9.Lee BH, et al. Direct investigation on energy bandgap of Si added ZnSnO system for stability enhancement by X-ray photoelectron spectroscopy. J. Alloy. Compd. 2017;715:9–15. doi: 10.1016/j.jallcom.2017.04.294. [DOI] [Google Scholar]

- 10.Kang I, et al. Role of Si as carrier suppressor in amorphous Zn-Sn-O. Curr. Appl. Phys. 2012;12:S12–S16. doi: 10.1016/j.cap.2012.05.044. [DOI] [Google Scholar]

- 11.Liu P-T, et al. Nitrogenated amorphous InGaZnO thin film transistor. Appl. Phys. Lett. 2011;98:052102. doi: 10.1063/1.3551537. [DOI] [Google Scholar]

- 12.Sallis. S, et al. Deep subgap feature in amorphous indium gallium zinc oxide: Evidence against reduced indium. Phys. Status Solidi A. 2015;212:1471–1475. doi: 10.1002/pssa.201431806. [DOI] [Google Scholar]

- 13.Kim KT, et al. In-Situ Metallic Oxide Capping for High Mobility Solution-Processed Metal-Oxide TFTs. IEEE Electron Device Lett. 2014;35:850–852. doi: 10.1109/LED.2014.2329955. [DOI] [Google Scholar]

- 14.Zan H-W, et al. Achieving high Field-Effect Mobility in Amorphous Indium-Gallium-Zinc Oxide by Capping a Strong Reduction Layer. Adv. Mater. 2012;24:3509–3514. doi: 10.1002/adma.201200683. [DOI] [PubMed] [Google Scholar]

- 15.Choi JY, et al. Role of metal capping layer on highly enhanced electrical performance of In-free Si-Zn-Sn-O thin film transistor. Thin Solid Films. 2015;594:293–298. doi: 10.1016/j.tsf.2015.04.048. [DOI] [Google Scholar]

- 16.Choi JY, et al. Engineering of band gap states of amorphous SiZnSnO semiconductor as a function of Si doping concentration. Sci. Rep. 2016;6:36504. doi: 10.1038/srep36504. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 17.Sommerhalter C, et al. High-sensitivity quantitative Kelvin probe microscopy by noncontact ultra-high-vacuum atomic force microscopy. Appl. Phys. Lett. 1999;75:2. doi: 10.1063/1.124357. [DOI] [Google Scholar]

- 18.Glatzel T, et al. Amplitude or frequency modulation-detection in Kelvin probe force microscopy. Appl. Surf. Sci. 2003;210:84–89. doi: 10.1016/S0169-4332(02)01484-8. [DOI] [Google Scholar]

- 19.Han S, Lee SY. High performance of full swing logic inverter using all n-types amorphous ZnSnO and SiZnSnO thin film transistors. Appl. Phys. Lett. 2015;106:212104. doi: 10.1063/1.4921791. [DOI] [Google Scholar]

- 20.Huang X, et al. Large-swing a-IGZO inverter with a depletion load induced by laser annealing. IEEE Electron Device Lett. 2014;35:1034–1036. doi: 10.1109/LED.2014.2345412. [DOI] [Google Scholar]

- 21.Han S, Lee. SY. Full swing depletion-load inverter with amorphous SiZnSnO thin film transistors. Phys. Stat. Sol. (a) 2016;214:1–5. [Google Scholar]

- 22.Chen H, Cao Y, Zhang J, Zhou C. Large-scale complementary macroelectronics using hybrid integration of carbon nanotubes and IGZO thin-film transistors. Nature Communications. 2014;5:4097. doi: 10.1038/ncomms5097. [DOI] [PubMed] [Google Scholar]