Abstract

Organic printed electronics are suitable for the development of wearable, lightweight, distributed applications in combination with cost‐effective production processes. Nonetheless, some necessary features for several envisioned disruptive mass‐produced products are still lacking: among these radio‐frequency (RF) communication capability, which requires high operational speed combined with low supply voltage in electronic devices processed on cheap plastic foils. Here, it is demonstrated that high‐frequency, low‐voltage, polymer field‐effect transistors can be fabricated on plastic with the sole use of a combination of scalable printing and digital laser‐based techniques. These devices reach an operational frequency in excess of 1 MHz at the challengingly low bias voltage of 2 V, and exceed 14 MHz operation at 7 V. In addition, when integrated into a rectifying circuit, they can provide a DC voltage at an input frequency of 13.56 MHz, opening the way for the implementation of RF devices and tags with cost‐effective production processes.

Keywords: flexible organic transistors, laser sintering, printed electronics, radio frequency, rectifiers

1. Introduction

Printed and solution‐processed polymer field‐effect transistors (FETs) are considered among key enablers of flexible, wearable, and portable electronics, and they hold the promise of low‐cost access to many novel mass applications. This promise stemmed from the prospect of utilizing printing tools derived from well‐established graphical arts technologies to deposit a variety of functional materials, which exhibit a suitable combination of mechanical and electronic properties.1, 2, 3, 4, 5 Such vision has begun to show concrete potential through a variety of proof‐of‐concept demonstrations, among which are programmable logic circuitry for flexible displays,6 transferrable electronics for pharmaceutics,7 healthcare sensors for brainwave detection8 or pulse oximetry,9 fully printed washable electronics on fabrics,10 and imperceptible logic circuitry on ultrathin substrates for intelligent electronic skin.11

Nonetheless, several among the most desirable applications, such as radio‐frequency (RF) tags and smart labels, driving circuitry for large‐area high‐resolution flexible displays, and real‐time sensor arrays, along with wireless sensors and sensors networks, require high‐speed and low‐voltage operation of the basic components of the circuits, in particular the transistor.12, 13 Given the limited carrier mobility and the coarse resolution of printing tools, printed organic electronics has struggled to deliver the challenging performances required to enable wireless capabilities.14, 15, 16, 17, 18, 19 Alternative flexible electronics technologies with higher carrier mobilities are being developed to achieve high‐frequency circuits, such as metal‐oxide semiconductors, carbon nanotubes, and 2D materials, reaching in some cases very high “transition frequency” f t, 20 the highest operational frequency of a transistor, in the order of the GHz or tens of GHz.21, 22 However such high performances are either achieved by resorting to conventional micro and nanofabrication techniques (i.e., e‐beam lithography, chemical vapor deposition, sputtering, and thermal evaporation), or pose scaling and processing issues (placing of high‐quality monolayers of 2D materials,23 alignment of carbon nanotubes,24, 25, 26, 27 and process temperatures compatible with cheap plastic substrates for high‐quality metal‐oxide layers28, 29).

It is therefore highly desirable to further develop printed and flexible organic electronics in order to achieve high‐frequency operation. While the possibility to obtain GHz organic transistors has only recently become argument of discussion,30 progresses are being made in the range of near‐field wireless communication. Several research groups in fact have proven the feasibility of operating organic transistors at frequencies in excess of 10 MHz,31, 32, 33, 34, 35, 36 but only a few works have achieved such frequencies by adopting printing techniques,37 which are more easily upscalable and compatible with large‐area processing. The maximum frequency drastically decreases for organic transistors on flexible substrates.15, 17, 18

Moreover, since f t is proportional to the bias voltage, the requirement of low‐voltage operation, at least below 10 V as necessary for portable, self‐powered wireless electronics, further complicates the achievement of high operational frequency. Examples of f t beyond the MHz threshold have been shown through the adoption of conventional thermally grown silicon dioxide dielectrics (20 MHz at a bias voltage of 10 V19), alumina deposited via atomic layer deposition (19 MHz at 10 V33), or hybrid metal‐oxide/self‐assembled ultrathin dielectrics (3.7 MHz at a bias of 3 V38 and 1.5 MHz at 4 V39). There are instead scarce examples of fast devices where low‐voltage is achieved through solution‐processing. In this respect, ionic gating schemes through electrolyte dielectrics,40, 41 which allow to achieve 1 V, or even lower, operational voltages, are not suitable because of their slow switching speed, in the tens of kHz range for the best reported cases,42, 43 because of the slow movement of ions. Polymer dielectrics, in particular if based on low‐k materials, are a suitable choice to attain ideal high‐frequency operation of FETs, but the achievement of the high capacitance necessary for low‐voltage operation is challenging. Demonstrations of MHz operation in FETs integrating low‐k polymers are rare,16 and high f t values at a voltage below 10 V of transistors of this kind on flexible substrate are yet to be shown.

In this work, we demonstrate that fully solution‐processed, low‐voltage polymer FETs, operating at MHz range, can be realized on flexible substrates with a combination of printing and direct‐writing techniques. In particular, f t in excess of 1 MHz can be reached at an extremely low bias voltage of 2 V, a voltage comparable to electrolyte‐gated devices. 14 MHz operation can be attained already at 7 V, therefore enabling near‐field wireless communication, which we exemplify here with a voltage rectifier, one of the most relevant building blocks for 13.56 MHz RF tags. The combination of these performances, obtained through scalable processes on cheap flexible substrates, represents a step forward in the realization of mass‐produced, distributed electronics with RF communication functionalities.

2. Results

To realize low‐voltage, high‐frequency polymer FETs we adopted a combination of femtosecond‐laser sintering of high‐resolution metal electrodes on plastic, a fast coating of uniaxially aligned polymer semiconductor, and a solution‐processed high capacitance dielectric stack. We have previously adopted femtosecond‐laser sintering for the realization of high‐resolution electrodes and high‐frequency polymer transistors on glass.37 The same technique was also previously demonstrated to be compatible with plastic substrates for the fabrication of electrodes,44, 45 semi‐transparent grids,46 and transistors,47, 48, 49 while it has not yet been adopted yet for high‐frequency, printed electronics on plastic. Here we show that femtosecond‐laser sintering, thanks to highly controlled deposition of energy, allows the conversion of silver inks on plastic and the high spatial resolution patterning of electrodes suitable for high‐performance fully solution‐processed polymer transistors. Our simple two‐step fabrication process is sketched in Figure 1 a: we first deposit via spin‐coating a uniform thin film of an ink of silver nanoparticles, then a near‐infrared femtosecond‐pulsed laser beam (λ = 1030 nm, 67 MHz repetition rate) induces the local sintering of the nanoparticles, directly writing conductive patterns. Finally, the unprocessed areas are washed out with an organic solvent. In future implementations aiming at reducing the amount of waste materials, spin‐coating may be replaced with a suitable printing technique (e.g., bar‐coating or inkjet) and the washed material can be recollected and recycled.

Figure 1.

a) Laser sintering processing steps for the fabrication of conductive electrodes on plastic; b) optical micrograph of a single device comprising active area and contact pads (magnification: layout of the source and drain electrodes); c) picture of the final realized devices on plastic PEN substrate.

This approach allows to reach a maximum resolution of 1.5 µm for the patterning of conductive features at a scanning speed of 1 mm s−1 (current limit of our setup), with an impinging laser beam intensity of 1.9 mW µm−2. With this method, we patterned silver source and drain electrodes with a width L ov of 1.7 µm on polyethylene naphthalate (PEN) to be used in FETs with a bottom‐contact, top‐gate architecture (Figure 1b). We realized an interdigitated structure in which the central finger is used as the source electrode, while the two external fingers are used as the drain. A photograph of the realized devices on a flexible PEN substrate is shown in Figure 1c.

To proceed with the fabrication of organic field‐effect transistors (OFETs), we followed the process illustrated in Figure 2 a. We first modified the sintered Ag electrodes with a self‐assembled monolayer of dimethylamino(benzenethiol) (DABT), which has been shown to improve electrons injection in organic semiconductors.50 Then, we adopted the widely studied semiconducting good electron transporting co‐polymer poly[N,Nʹ‐bis(2‐octyldodecyl)‐naphthalene‐1,4,5,8‐bis(dicarboximide)‐2,6‐diyl]‐alt‐5,5ʹ‐(2,2ʹ‐bithiophene) (P(NDI2OD‐T2)) and deposited a thin layer of such material via bar‐coating, which is a simple and fast method to induce the directional alignment of the polymer chains along the coating direction,51 yielding a film with optimized charge mobility over large area.14 We then deposited via spin‐coating a 150 nm thick multilayered polymer dielectric stack, composed of an ultrathin crossed‐linked low‐k polymer and a top high‐k polymer, achieving an areal capacitance C diel of 39 nF cm−2. We finally inkjet‐printed poly(3,4‐ethylenedioxythiophene) polystyrene sulfonate (PEDOT:PSS) gate electrodes on top of the dielectric. We fabricated FETs (Figure 2b) with a varying channel length L, ranging from 1 to 17.5 µm, with constant channel width W of 800 µm.

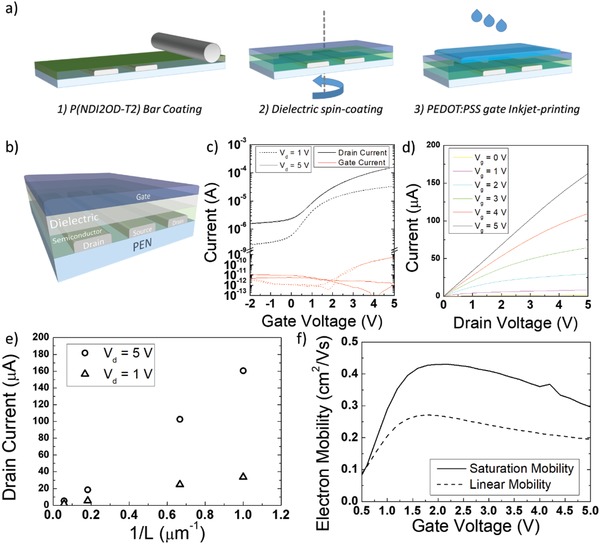

Figure 2.

a) Process flow for the fabrication of polymer FETs on plastic with solution‐based techniques; b) 3D view of the final device stack; c) transfer curve and d) output curve for a realized FET with L = 1 µm; e) drain current at V g = 5 V for the FETs and for the realized channel lengths; and f) calculated apparent charge mobility for the device with L = 1 µm.

The transfer curve for an FET with the shortest channel length of 1 µm (Figure 2c) highlights the correct operation and turn‐on of the device at a gate voltage as low as 5 V, both in the linear (V d = 1 V) and in the saturation (V d = 5 V) regime, with no appreciable hysteresis. In addition, we highlight the extremely low gate leakage current that is more than four orders of magnitude lower than the device ON current in both operation regimes. Similarly, analogous electrical performance and low gate leakage current are achieved in the devices with longer channel length (Figure S1a–c, Supporting Information). The drain current scales correctly with the channel length (Figure 2e and Figure S2a–c, Supporting Information), while the output curve, although not achieving clear saturation differently from the longer channel devices (Figure S3a–c, Supporting Information) and likely owing to the onset of short‐channel effects,52 both confirms the correct operation of our downscaled device and suggests that a good charge injection performance is achieved in our architecture (Figure 2d).

We calculated the apparent electron mobility (µ app) for our devices as a function of gate voltage from the derivative of the transfer curves according to the gradual channel approximation model. In the device with L = 1 µm (Figure 2f), µ app peaks at a low V g of 1.8 V (2.2 V) in the linear (saturation) regime, and then slightly rolls off with V g, an effect related to the influence of charge injection limitations. For our case, we simply report in Table 1 the calculated value for the mobility in the saturation regime at maximum V g, being one of the relevant bias points for the FET and for the rectifier circuit presented later in the text. At this bias point, µ app ranges in the interval from 0.15 to 0.3 cm2 V−1 s−1 when L is shortened from 17.5 to 1 µm. Such an increasing trend as the channel length is reduced is an effect stemming from the increase of the lateral electric field across the channel region, which affects charge injection and/or charge transport in organic FETs.53, 54, 55 In Table 1, alongside with the calculated mobility, we report the “measurement reliability factor” r as suggested in Choi et al.,56 which in our cases is always above 100%, highlighting the presence of a very mild “kink effect.”

Table 1.

Measured effective charge mobility and corresponding reliability factor for the realized FETs for the different channel lengths

| Channel length [µm] | Apparent mobility at V g = 5 V [cm2 V−1 s−1] | Reliability factor r [%] |

|---|---|---|

| 1 | 0.30 | 107 |

| 1.5 | 0.29 | 109 |

| 5.5 | 0.16 | 128 |

| 17.5 | 0.14 | 134 |

We extracted the contact resistance of the shortest channel device (L = 1 µm) with the differential method,57 which yielded a width‐normalized contact resistance R C W = 1015 Ωcm at V g = 5 V in the linear regime. The latter is a very small value in the context of printed polymer FETs, has rarely been achieved with the sole use of solution‐based approaches and with low‐voltage operation,58, 59 and has a paramount role in the achievement of good electrical behavior of our downscaled FETs. In particular, R C W is below the value of the width‐normalized channel resistance R ch W = V d W/I d −R c W = 1369 Ωcm at the highest gate bias of V g = 5 V (and V d = 1 V). Despite R C W values below 1000 Ωcm have been demonstrated for organic transistors,60, 61, 62, 63, 64, 65, 66 these examples either adopted evaporation of dopants/electrodes, or device biasing in excess of 10 V, or the use of electrolyte‐gating schemes, which are not desirable for high‐frequency, low‐voltage, all‐solution‐processed devices.

We show in Figure S4a,b (Supporting Information) the superimposed transfer curves of five different devices each for L = 1 µm and L = 1.5 µm cases, and in Figure S5 (Supporting Information) we plot the superimposed trends of the extracted mobility versus gate voltage for the devices with the shortest channel (L = 1 µm), highlighting that our results are reproducible even at these challengingly short, micrometer‐sized channel lengths. In Table S1 (Supporting Information) we also report the mean and standard deviation of some selected figures of merit (i.e., the mobility at maximum bias and the parameters µ 0, γ, and V T as defined in Natali et al.57) for the set of five devices with L = 1 µm. Once again, the reproducibility of our devices is highlighted especially in terms of intrinsic mobility µ 0 and in terms of the threshold voltage V T, for which the standard deviation is, respectively, 1.4% and 5% of the mean value.

We also measured the transfer curve of a device (L = 1 µm) after 7 months from fabrication and storage in nitrogen atmosphere, highlighting how only a small loss in performance is detected (Figure S6a, Supporting Information). We then kept such transistor in the ON state for 150 min by applying V g = V d = 5 V and measured its transfer curves every 30 min (Figure S6b, Supporting Information), detecting a good stability of the device upon operational stress.

In order to evidence the benefit of downscaled features on the frequency response of the fabricated FETs, we characterized the AC performance of our devices in terms of transition frequency f t, which depends on the electrical parameters of the transistor according to20

| (1) |

where g m is the device transconductance and C gs, C gd are the gate/source and gate/drain capacitances, respectively. Additional details on the measurement method can be found in ref. 37. In Figure 3 a we show the measured C gs and C gd versus bias voltage in the saturation regime (V gs = V ds) and compared them to the theoretically expected values for our layout, according to67

| (2) |

| (3) |

where W ov = 500 µm is the total width of the overlap between gate and bottom electrodes, which exceeds the actual channel width W (see the scheme reported in Figure S7, Supporting Information), while the correction factors αf,gs and αf,gd are introduced to account for the fringing capacitance between the source/drain electrodes and the wide top gate. We calculated such factors using a formula proposed by Elmasry,68 yielding αf,gs = 12.4% and αf,gd = 21.1%, which is in perfect agreement with our measured data. In the case of C gd, the measured values are correctly constant at ≈0.8 pF up to a bias voltage of 5 V, while C gs exhibits a slightly increasing trend with the bias voltage, which we attribute to parasitic accumulation of additional charge outside the channel active area. This effect has already been explained for structures of this kind,69 and originates from the fact that the semiconductor layer is not patterned, covering the whole substrate. At bias voltages >5 V, the higher electric fields are producing a further increase in capacitance and a relatively small deviation from the predicted values.

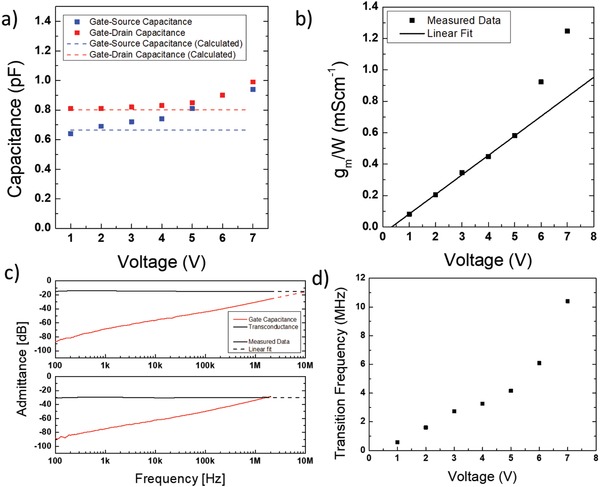

Figure 3.

a) Measured and calculated data for the gate–source and gate–drain capacitances of an FET with L = 1 µm versus gate–source bias voltage; b) measured transconductance of the same device versus V gs (the linear fit is a guide to the eye); c) combined measurement of the transconductance and gate capacitance of the same FET for f t extraction (top panel: 7 V bias, bottom panel: 2 V bias); d) extracted transition frequency for the same FET versus gate–source bias voltage.

The measured g m per unit width versus bias voltage is shown in Figure 3b. We correctly identify a linear increase of g m from V gs = 1 V to V gs = 5 V, where the transconductance varies from 0.081 to 0.58 mS cm−1. The latter value is very close to the theoretical one extracted from the slope of the transfer curves, which yields For bias voltages in excess of 5 V, g m exhibits a superlinear increase with V gs, an effect that we attribute to the high lateral electric field insisting across the channel region. The measurements for g m, C gs, and C gd can be combined to identify f t as in Figure 3c, where we show such measurement for a device with L = 1 µm and a bias voltage of 7 V (top panel) and 2 V (bottom panel). The measurement is limited at a frequency of 2 MHz due to setup constraints. Remarkably, we can measure an f t = 1.6 MHz for a bias voltage of only 2 V. In Figure 3d we show the trend of the measured f t for the same device versus bias voltage, highlighting how this figure of merit essentially follows the behavior of g m. In the case of a bias voltage of 7 V, we can extrapolate a high transition frequency of 10.4 MHz.

To assess the relevance of the performance achieved by our devices and also to favor the identification of effective strategies to improve even further f t, we have calculated the maximum achievable transition frequency with respect to the variation of our FET parameters, using the modeling recently proposed by Klauk.30 With an R C W of a value equal to the one we measured, neither a further reduction of L nor an increase of µ 0 would yield a very significant increase in f t (Figure S8a, Supporting Information). At such fixed contact resistance, an increase in f t would only be obtainable with the reduction of L ov. However, even in the extreme and unrealistic case of L ov = 0, f t would be limited to a value below 100 MHz at best (Figure S8b, Supporting Information). These calculations underline that we have already obtained, with the physical parameters characterizing our devices, an AC performance that is close to the highest possible. The reduction of the contact resistance thus constitutes the main route for accessing higher f t in the future, as it is the key point in order to achieve a regime where the modification of the other parameters is effective (Figure S8c, Supporting Information).

We have also measured the reproducibility of our devices in terms of transition frequency after 7 months from fabrication. In Figure S9 (Supporting Information) we show the measured curves for four devices with L = 1 µm at a bias voltage of 5 V, which highlight good reproducibility for f t with a mean value of 6.65 MHz and a standard deviation of 2.12 MHz. Overall, our best f t in the measurement set yielded a value of 14.4 MHz at a bias voltage of 7 V (Figure S10, Supporting Information).

We have also compared our achieved performance to the previous literature for organic high‐frequency transistors on plastic, for which the transition frequency was explicitly measured and reported. Since f t is directly proportional to the applied bias voltage, in our comparison we decouple such effect by defining the voltage‐normalized transition frequency f t /V bias, where V bias is the maximum voltage applied to the transistor electrodes during f t measurement. In this way the voltage‐normalized transition frequency encompasses the achieved performance exclusively in terms of effective charge transport properties and geometrical resolution. We report in Table 2 the calculated f t /V bias of our FETs in comparison with other representative examples of high‐frequency (f t > 1 MHz) organic devices on flexible substrate.

Table 2.

Achieved voltage‐normalized transition frequency f t/V bias for relevant works on organic, high‐frequency FETs on flexible substrate

| f t [MHz] | V bias [V] | f t /V bias [MHz V−1] | Fabrication techniques | Ref. |

|---|---|---|---|---|

| 14.4 | 7 | 2.06 | Laser sintering, bar‐coating, spin‐coating, inkjet | This work |

| 1.6 | 2 | 0.80 | Laser sintering, bar‐coating, spin‐coating, inkjet | This work |

| 1.6 | 8 | 0.20 | Inkjet, spin‐coating | 16 |

| 4.9 | 30 | 0.16 | Laser ablation, spin‐coating, inkjet | 18 |

| 1.92 | 15 | 0.13 | Gravure, inkjet | 15 |

| 3.3 | 30 | 0.11 | NILa), evaporation, inkjet, gravure | 17 |

NIL: Nanoimprint lithography.

Our FETs achieve the best performance in terms of f t/V bias in the field of organic transistors on plastic, with a tenfold improvement compared to previous demonstrations.

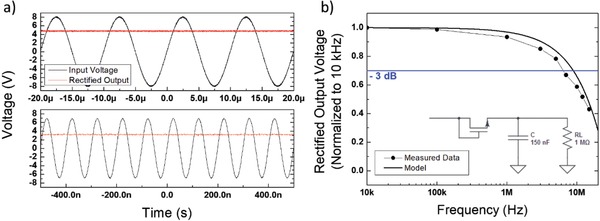

While f t is the relevant figure of merit for the assessment of the FET maximum operational speed for integration in analog circuitry (e.g., amplifiers), we additionally assessed the performance of our FETs upon large‐signal operation, which is relevant for the implementation of RF applications such as wireless data communication. To this goal, we realized a simple rectifying circuit (Figure 4 b, inset) and operated it up to 15 MHz, above the frequencies of interest for near‐field communication (NFC). In Figure 4a we show the rectified output (red line) on an oscilloscope corresponding to an oscillating input signal with an amplitude of 8 V (black line). We measure a −3 dB frequency of 8.7 MHz, with respect to the amplitude recorded at 100 kHz (Figure S11, Supporting Information). For a reduced signal amplitude of 5 V, the −3 dB frequency is as high as 6.4 MHz already (Figure 4b), and 1 V can still be read in DC at 15 MHz (Figure S12, Supporting Information) proving the applicability of our approach for the implementation of RF tags.

Figure 4.

a) Input and output voltage waveforms for a rectifier based on a realized FET with L = 1 µm at an input voltage frequency of 100 kHz (top panel) and of 10 MHz (bottom panel). b) Measured and simulated output voltage of the same rectifier versus frequency at an input voltage amplitude of 5 V (inset: rectifier circuit).

We also verified the stability of the output of our rectifier upon constant operation for 150 min at an input voltage amplitude of 5 V and at an input frequency of 15 MHz (Figure S13, Supporting Information). The device was measured after 7 months from fabrication. Our rectifier shows stable performance over 2.5 h of continuous operation even at the high operational frequency of 15 MHz.

To better understand the measured performance of our rectifier we developed a simple model, based on the charge balance of the smoothing capacitor (see Figure 4b, inset), for the behavior of the output voltage versus input voltage frequency (see the Supporting Information). We are able to predict with good approximation the frequency behavior of the output voltage (Figure 4b, solid line), correctly identifying the frequency cutoff. Moreover, the model allows us to identify the main factors determining the output/input voltage ratio without affecting the rectifier cutoff frequency: in order to achieve a high ratio, it is critical to limit the OFF current in the transistor and to adopt a channel width large enough to feed the load resistance. The cutoff frequency is instead determined by the same parameters as the f t (i.e., L, µ, and V bias) and can be set independently.

3. Conclusions

We have demonstrated the realization of high‐frequency, low‐voltage polymer FETs on flexible substrates using only printing techniques and digital laser patterning. The proposed FETs feature a transition frequency in excess of 1 MHz at a bias voltage as low as 2 V, and can operate at a frequency in excess of 10 MHz at a bias voltage of 7 V, which is, to the best of our knowledge, the highest for the case of printed polymers integrating direct‐written electrodes, on flexible substrates. Such performance allows the reported devices to operate at supply voltages comparable to electrolyte gated organic transistors, while they can be modulated at two to three orders of magnitude higher frequencies. Moreover, such operational bias voltage enables the implementation of stand‐alone electronic devices, being fully compatible with thin film batteries or energy harvesters, such as plastic photovoltaic modules.70 In addition, these devices achieve the best figure to date, by an order of magnitude, in terms of voltage‐normalized transition frequency (2.06 MHz V−1). Finally, we have integrated these devices into a rectifying circuit that can provide voltage rectification up to 15 MHz, thus being compatible with NFC wireless communication at 13.56 MHz. The demonstration of such performance and its achievement with the sole use of solution‐based processing, printing techniques, and laser patterning identify a feasible route toward low‐cost, mass‐scale production of organic devices for RF applications.

4. Experimental Section

General: The Ag‐nanoparticles ink (NPS‐JL) was purchased from Harima Chemicals, 4‐(dimethylamino)benzenethiol (DABT) was purchased from TCI Chemicals, P(NDI2OD‐T2) was purchased from Polyera (M n = 35.3 kDa; PDI = 1.8 (GPC); elemental analysis: C: 75.21, H: 8.73, N: 2.87 (theoretical: C: 75.26, H: 8.96, N: 2.83)), and PEDOT:PSS (Clevios PJ700) was purchased from Heraeus. The substrates consisted of 125 µm thick polyethylene naphthalate foils (Teonex Q65FA) purchased from DuPont TeijinFilms.

Femtosecond Laser Sintering Setup: The laser setup consisted of a commercial laser source (LightConversion PHAROS, based on Yb:KGW as active medium), which generated ≈80 fs long laser pulses with a repetition rate of 67 MHz, λ = 1030 nm, and maximum output power of 2 W. Before reaching the sample, the beam was conditioned through an optical path that includes a software‐controlled attenuator and a focalizing objective (Mitutoyo) lens whose magnifying power could be selected between 20X, 50X, and 100X. The sample was positioned on a software‐controlled moving stage (Aerotech ABL1000) capable of a maximum resolution of 0.5 nm and a maximum speed of 300 mm s−1.

Contacts Fabrication: The PEN substrates were used as‐is on the pristine side (without adhesion‐promoting treatment) and a 4 nm thick AlOx layer was deposited via thermal evaporation of Al and exposure to atmosphere. The Ag‐nanoparticles ink was spun at 7000 rpm for 5 min, yielding a 70 nm thick layer. The laser‐sintering step was then performed using 1.9 mW µm−2 beam power, 50X optics, and 0.1 mm s−1 scanning speed. After laser processing, the samples were thoroughly washed with o‐Xylene and isopropanol and finally dried with a nitrogen flux.

Organic FET Fabrication: The samples with the desired laser‐sintered patterns for the FET bottom electrodes were Ar‐plasma etched with a power of 100 W for 4 min. A solution of 17 µL of DABT in 12 mL of isopropanol was prepared, and the samples were immersed in it for 15 min and then rinsed with abundant isopropanol. A solution of P(NDI2OD‐T2) in toluene (5 g L−1) was then deposited via bar‐coating on the samples as described in ref. 14 using a bar designed to yield an 8 µm thick wet layer. The samples were then annealed in a nitrogen atmosphere for 20 min at 120 °C. The dielectric was a double layer stack71 composed of a very thin layer of a low‐k polymer, in contact with the semiconductor, and a top high‐k polymer, for a total thickness of about 200 nm and an areal capacitance of 39 nF cm−2. Finally, PEDOT:PSS was inkjet‐printed with a Fujifilm Dimatix DMP‐2831 to pattern the gate electrodes and the samples were annealed for 8 h in nitrogen atmosphere before measurement.

Rectifier Fabrication: The rectifier circuit was realized by connecting one of the realized transistors, biased in a transdiode configuration, to a discrete capacitor of 0.15 µF and to an oscilloscope with an input resistance of 1 MΩ using external point‐contact probes.

Electrical Characterization: The devices were measured in nitrogen atmosphere. Static characterization was performed via a Keysight B1500A Semiconductor Parameter Analyzer. Frequency performance was measured using a custom setup that includes a Keysight ENA E5061B Vector Network Analyzer and an Agilent B2912A Sourcemeter. The apparent mobility µ app was extracted from the transfer characteristic according to for the saturation regime and according to for the linear regime.

Conflict of Interest

The authors declare no conflict of interest.

Supporting information

Supplementary

Acknowledgements

The authors are thankful to L. Criante and his team for the support with the femtosecond laser machining setup. This work was financially supported by the European Research Council (ERC) under the European Union's Horizon 2020 research and innovation programme “HEROIC”, grant agreement 638059.

Perinot A., Caironi M., Adv. Sci. 2019, 6, 1801566 10.1002/advs.201801566

References

- 1. Guo X., Xu Y., Ogier S., Ng T. N., Caironi M., Perinot A., Li L., Zhao J., Tang W., Sporea R. A., Nejim A., Carrabina J., Cain P., Yan F., IEEE Trans. Electron Devices 2017, 64, 1906. [Google Scholar]

- 2. Mattana G., Loi A., Woytasik M., Barbaro M., Noël V., Piro B., Adv. Mater. Technol. 2017, 2, 1700063. [Google Scholar]

- 3. Chang J. S., Facchetti A. F., Reuss R., IEEE J. Emerg. Sel. Topics Circuits Syst. 2017, 7, 7. [Google Scholar]

- 4. Shunpu L., Daping C., Flexible Printed Electron. 2017, 2, 013002. [Google Scholar]

- 5. Fukuda K., Someya T., Adv. Mater. 2017, 29, 1602736. [DOI] [PubMed] [Google Scholar]

- 6. Sou A., Jung S., Gili E., Pecunia V., Joimel J., Fichet G., Sirringhaus H., Org. Electron. 2014, 15, 3111. [Google Scholar]

- 7. Bonacchini G. E., Bossio C., Greco F., Mattoli V., Kim Y. H., Lanzani G., Caironi M., Adv. Mater. 2018, 30, 1706091. [DOI] [PubMed] [Google Scholar]

- 8. Yoshimoto S., Araki T., Uemura T., Nezu T., Kondo M., Sasai K., Iwase M., Satake H., Yoshida A., Kikuchi M., Sekitani T., presented at 2016 38th Annual Int. Conf. of the IEEE Engineering in Medicine and Biology Society (EMBC), Orlando, FL, USA, August 2016. [DOI] [PubMed]

- 9. Lochner C. M., Khan Y., Pierre A., Arias A. C., Nat. Commun. 2014, 5, 5745. [DOI] [PubMed] [Google Scholar]

- 10. Carey T., Cacovich S., Divitini G., Ren J., Mansouri A., Kim J. M., Wang C., Ducati C., Sordan R., Torrisi F., Nat. Commun. 2017, 8, 1202. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 11. Takeda Y., Hayasaka K., Shiwaku R., Yokosawa K., Shiba T., Mamada M., Kumaki D., Fukuda K., Tokito S., Sci. Rep. 2016, 6, 25714. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 12. Subramanian V., Frechet J. M. J., Chang P. C., Huang D. C., Lee J. B., Molesa S. E., Murphy A. R., Redinger D. R., Volkman S. K., Proc. IEEE 2005, 93, 1330. [Google Scholar]

- 13. Semple J., Georgiadou D. G., Wyatt‐Moon G., Gelinck G., Anthopoulos T. D., Semicond. Sci. Technol. 2017, 32, 123002. [Google Scholar]

- 14. Bucella S. G., Luzio A., Gann E., Thomsen L., McNeill C. R., Pace G., Perinot A., Chen Z., Facchetti A., Caironi M., Nat. Commun. 2015, 6, 8394. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 15. Kitsomboonloha R., Kang H., Grau G., Scheideler W., Subramanian V., Adv. Electron. Mater. 2015, 1, 1500155. [Google Scholar]

- 16. Noh Y.‐Y., Zhao N., Caironi M., Sirringhaus H., Nat. Nanotechnol. 2007, 2, 784. [DOI] [PubMed] [Google Scholar]

- 17. Higgins S. G., Muir B. V. O., Dell'Erba G., Perinot A., Caironi M., Campbell A. J., Appl. Phys. Lett. 2016, 108, 023302. [Google Scholar]

- 18. Bucella S. G., Perinot A., Caironi M., IEEE Trans. Electron Devices 2017, 64, 1960. [Google Scholar]

- 19. Yamamura A., Watanabe S., Uno M., Mitani M., Mitsui C., Tsurumi J., Isahaya N., Kanaoka Y., Okamoto T., Takeya J., Sci. Adv. 2018, 4, eaao5758. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 20. Caironi M., Noh Y. Y., Sirringhaus H., Semicond. Sci. Technol. 2011, 26, 034006. [Google Scholar]

- 21. Chimot N., Derycke V., Goffman M. F., Bourgoin J. P., Happy H., Dambrine G., Appl. Phys. Lett. 2007, 91, 153111. [Google Scholar]

- 22. Cheng R., Jiang S., Chen Y., Liu Y., Weiss N., Cheng H.‐C., Wu H., Huang Y., Duan X., Nat. Commun. 2014, 5, 5143. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 23. Carey B. J., Ou J. Z., Clark R. M., Berean K. J., Zavabeti A., Chesman A. S. R., Russo S. P., Lau D. W. M., Xu Z.‐Q., Bao Q., Kavehei O., Gibson B. C., Dickey M. D., Kaner R. B., Daeneke T., Kalantar‐Zadeh K., Nat. Commun. 2017, 8, 14482. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 24. Park S., Vosguerichian M., Bao Z., Nanoscale 2013, 5, 1727. [DOI] [PubMed] [Google Scholar]

- 25. Rouhi N., Jain D., Burke P. J., ACS Nano 2011, 5, 8471. [DOI] [PubMed] [Google Scholar]

- 26. Zhang J., Cui J., Wang X., Wang W., Mei X., Yi P., Yang X., He X., Phys. Status Solidi A 2018, 215, 1700719. [Google Scholar]

- 27. Derenskyi V., Gomulya W., Talsma W., Salazar‐Rios J. M., Fritsch M., Nirmalraj P., Riel H., Allard S., Scherf U., Loi M. A., Adv. Mater. 2017, 29, 1606757. [DOI] [PubMed] [Google Scholar]

- 28. Thomas S. R., Pattanasattayavong P., Anthopoulos T. D., Chem. Soc. Rev. 2013, 42, 6910. [DOI] [PubMed] [Google Scholar]

- 29. Petti L., Münzenrieder N., Vogt C., Faber H., Büthe L., Cantarella G., Bottacchi F., Anthopoulos T. D., Tröster G., Appl. Phys. Rev. 2016, 3, 021303. [Google Scholar]

- 30. Klauk H., Adv. Electron. Mater. 2018, 4, 1700474. [Google Scholar]

- 31. Kitamura M., Arakawa Y., Jpn. J. Appl. Phys. 2011, 50, 01BC01. [Google Scholar]

- 32. Uno M., Uemura T., Kanaoka Y., Chen Z., Facchetti A., Takeya J., Org. Electron. 2013, 14, 1656. [Google Scholar]

- 33. Nakayama K., Uno M., Uemura T., Namba N., Kanaoka Y., Kato T., Katayama M., Mitsui C., Okamoto T., Takeya J., Adv. Mater. Interfaces 2014, 1, 1300124. [Google Scholar]

- 34. Uno M., Cha B.‐S., Kanaoka Y., Takeya J., Org. Electron. 2015, 20, 119. [Google Scholar]

- 35. Uemura T., Matsumoto T., Miyake K., Uno M., Ohnishi S., Kato T., Katayama M., Shinamura S., Hamada M., Kang M.‐J., Takimiya K., Mitsui C., Okamoto T., Takeya J., Adv. Mater. 2014, 26, 2983. [DOI] [PubMed] [Google Scholar]

- 36. Kheradmand‐Boroujeni B., Klinger M. P., Fischer A., Kleemann H., Leo K., Ellinger F., Sci. Rep. 2018, 8, 7643. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 37. Perinot A., Kshirsagar P., Malvindi M. A., Pompa P. P., Fiammengo R., Caironi M., Sci. Rep. 2016, 6, 38941. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 38. Zaki T., Rodel R., Letzkus F., Richter H., Zschieschang U., Klauk H., Burghartz J. N., IEEE Electron Device Lett. 2013, 34, 520. [Google Scholar]

- 39. Senanayak S. P., Sangwan V. K., McMorrow J. J., Everaerts K., Chen Z. H., Facchetti A., Hersam M. C., Marks T. J., Narayan K. S., Adv. Electron. Mater. 2015, 1, 1500226. [Google Scholar]

- 40. Zeglio E., Inganas O., Adv. Mater. 2018, 30, 1800941. [DOI] [PubMed] [Google Scholar]

- 41. Nketia‐Yawson B., Kang S.‐J., Tabi G. D., Perinot A., Caironi M., Facchetti A., Noh Y.‐Y., Adv. Mater. 2017, 29, 1605685. [DOI] [PubMed] [Google Scholar]

- 42. Wang B., Huang W., Chi L., Al‐Hashimi M., Marks T. J., Facchetti A., Chem. Rev. 2018, 118, 5690. [DOI] [PubMed] [Google Scholar]

- 43. Kim S. H., Hong K., Xie W., Lee K. H., Zhang S., Lodge T. P., Frisbie C. D., Adv. Mater. 2013, 25, 1822. [DOI] [PubMed] [Google Scholar]

- 44. Son Y., Yeo J., Ha C. W., Hong S., Ko S. H., Yang D.‐Y., Int. J. Nanomanuf. 2013, 9, 468. [Google Scholar]

- 45. Lee H., Kwon J., Shin W. S., Kim H. R., Shin J., Cho H., Han S., Yeo J., Hong S., Micromachines 2017, 8, 153. [Google Scholar]

- 46. Hong S., Yeo J., Kim G., Kim D., Lee H., Kwon J., Lee H., Lee P., Ko S H., ACS Nano 2013, 7, 5024. [DOI] [PubMed] [Google Scholar]

- 47. Ko S. H., Pan H., Grigoropoulos C. P., Luscombe C. K., Fréchet J. M. J., Poulikakos D., Nanotechnology 2007, 18, 345202. [Google Scholar]

- 48. Yeo J., Hong S., Lee D., Hotz N., Lee M.‐T., Grigoropoulos C. P., Ko S. H., PLoS One 2012, 7, e42315. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 49. Son Y., Yeo J., Moon H., Lim T. W., Hong S., Nam K. H., Yoo S., Grigoropoulos C. P., Yang D. Y., Ko S. H., Adv. Mater. 2011, 23, 3176. [DOI] [PubMed] [Google Scholar]

- 50. Kitamura M., Kuzumoto Y., Aomori S., Kamura M., Na J. H., Arakawa Y., Appl. Phys. Lett. 2009, 94, 083310. [Google Scholar]

- 51. Khim D., Luzio A., Bonacchini G. E., Pace G., Lee M. J., Noh Y. Y., Caironi M., Adv. Mater. 2018, 30, 1705463. [DOI] [PubMed] [Google Scholar]

- 52. Taur Y., Ning T. H., Fundamentals of Modern VLSI Devices, Cambridge University Press, New York, NY, USA 2009. [Google Scholar]

- 53. Luzio A., Criante L., D'Innocenzo V., Caironi M., Sci. Rep. 2013, 3, 3425. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 54. Sirringhaus H., Adv. Mater. 2014, 26, 1319. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 55. Fazzi D., Caironi M., Phys. Chem. Chem. Phys. 2015, 17, 8573. [DOI] [PubMed] [Google Scholar]

- 56. Choi H. H., Cho K., Frisbie C. D., Sirringhaus H., Podzorov V., Nat. Mater. 2017, 17, 2. [DOI] [PubMed] [Google Scholar]

- 57. Natali D., Fumagalli L., Sampietro M., J. Appl. Phys. 2007, 101, 014501. [Google Scholar]

- 58. Natali D., Caironi M., Adv. Mater. 2012, 24, 1357. [DOI] [PubMed] [Google Scholar]

- 59. Liu C., Xu Y., Noh Y.‐Y., Mater. Today 2015, 18, 79. [Google Scholar]

- 60. Minari T., Liu C., presented at 2013 IEEE Int. Interconnect Technology Conf. – IITC, Tokyo, Japan, June 2013. [Google Scholar]

- 61. Wang Q., Jiang S., Qian J., Song L., Zhang L., Zhang Y., Zhang Y., Wang Y., Wang X., Shi Y., Zheng Y., Li Y., Sci. Rep. 2017, 7, 7830. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 62. He D., Qiao J., Zhang L., Wang J., Lan T., Qian J., Li Y., Shi Y., Chai Y., Lan W., Ono L. K., Qi Y., Xu J.‐B., Ji W., Wang X., Sci. Adv. 2017, 3, e1701186. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 63. Uemura T., Rolin C., Ke T.‐H., Fesenko P., Genoe J., Heremans P., Takeya J., Adv. Mater. 2016, 28, 151. [DOI] [PubMed] [Google Scholar]

- 64. Darmawan P., Minari T., Xu Y., Li S.‐L., Song H., Chan M., Tsukagoshi K., Adv. Funct. Mater. 2012, 22, 4577. [Google Scholar]

- 65. Stadlober B., Haas U., Gold H., Haase A., Jakopic G., Leising G., Koch N., Rentenberger S., Zojer E., Adv. Funct. Mater. 2007, 17, 2687. [Google Scholar]

- 66. Braga D., Ha M., Xie W., Frisbie C. D., Appl. Phys. Lett. 2010, 97, 193311. [Google Scholar]

- 67. Ytterdal T., Cheng Y., Fjeldly T. A., Device Modeling for Analog and RF CMOS Circuit Design, John Wiley & Sons, Hoboken, New Jersey, USA: 2003. [Google Scholar]

- 68. Elmasry M. I., IEEE Electron Device Lett. 1982, 3, 6. [Google Scholar]

- 69. Valletta A., Rapisarda M., Calvi S., Fortunato G., Jacob S., Fischer V., Benwadih M., Bablet J., Chartier I., Coppard R., Mariucci L., IEEE Trans. Electron Devices 2014, 61, 4120. [Google Scholar]

- 70. Berny S., Blouin N., Distler A., Egelhaaf H. J., Krompiec M., Lohr A., Lozman O. R., Morse G. E., Nanson L., Pron A., Sauermann T., Seidler N., Tierney S., Tiwana P., Wagner M., Wilson H., Adv. Sci. 2016, 3, 1500342. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 71. Tang W., Li J., Zhao J., Zhang W., Yan F., Guo X., IEEE Electron Device Lett. 2015, 36, 950. [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Supplementary Materials

Supplementary