Abstract

The contact resistance in organic thin-film transistors (TFTs) is the limiting factor in the development of high-frequency organic TFTs. In devices fabricated in the inverted (bottom-gate) device architecture, staggered (top-contact) organic TFTs have usually shown or are predicted to show lower contact resistance than coplanar (bottom-contact) organic TFTs. However, through comparison of organic TFTs with different gate-dielectric thicknesses based on the small-molecule organic semiconductor 2,9-diphenyl-dinaphtho[2,3-b:2’,3’-f]thieno[3,2-b]thiophene, we show the potential for bottom-contact TFTs to have lower contact resistance than top-contact TFTs, provided the gate dielectric is sufficiently thin and an interface layer such as pentafluorobenzenethiol is used to treat the surface of the source and drain contacts. We demonstrate bottom-contact TFTs fabricated on flexible plastic substrates with record-low contact resistance (29 Ωcm), record subthreshold swing (62 mV/decade), and signal-propagation delays in 11-stage unipolar ring oscillators as short as 138 ns per stage, all at operating voltages of about 3 V.

The widespread adoption of organic thin-film transistors (TFTs) in low-voltage high-frequency device applications is impeded by the contact resistance in the TFTs. Here, the authors report record-low contact resistance in bottom-gate, bottom-contact organic TFTs with an ultrathin gate dielectric.

Introduction

To enable the adoption of organic thin-film transistors (TFT) in high-frequency device applications, the contact resistance must be reduced well below the smallest values reported to date1–3. The reason is that the contact resistance is a key limiting factor determining the transit frequency of organic TFTs4,5., and when the TFT dimensions are in the range required for megahertz operation at low voltages, the contact resistance is more limiting to the transit frequency than the intrinsic carrier mobility2. For example, achieving a transit frequency of 10 MHz in a TFT with a channel length of 1 µm and a total gate-to-contact overlap of 10 µm operating with voltages of 3 V requires the contact resistance to be smaller than 40 Ωcm, regardless of whether the intrinsic channel mobility is 10, 100, or 1000 cm2 V−1 s−1.2. In organic TFTs, the contact resistance is greatly affected not only by the choice of materials, but also by the choice of TFT architecture. In the case of the inverted (bottom-gate) architectures, the staggered (top-contact; TC) configuration has typically provided smaller contact resistance than the coplanar (bottom-contact; BC) configuration, even for devices comprising the same materials and layer thicknesses6,7. To date, the smallest contact resistances reported for TC and BC organic TFTs are 46.9 Ωcm1 and 80 Ωcm8, respectively. These and other experimental observations are in line with most device simulations that predict that TC organic TFTs would generally outperform BC organic TFTs due to lower contact resistance7,9. The smaller contact resistance of TC organic TFTs is ascribed primarily to the overlap between the contacts and a portion of the gate-induced carrier channel directly under the contacts, leading to more efficient charge injection10–12. Additionally, the electrical conductivity in the contact regions may be enhanced by metal clusters penetrating into the semiconductor layer upon deposition of the contact metal13, by contact doping14, and by the relatively large area for charge injection between the contact metal and the gate-induced carrier channel (current crowding)10,15.

In BC organic TFTs, the contact resistance is typically higher, since the gate field-assisted charge injection is weakened9. In addition, BC organic TFTs often exhibit a discontinuous coverage and poor thin-film morphology of the organic semiconductor layer along and across the edges of the contacts. Such a poor semiconductor morphology occurs, because the surface energy of the contact material usually differs profoundly from that of the gate dielectric6. Various approaches have been implemented to improve the wetting behavior of organic semiconductors on metal contacts, such as ozone exposure8, oxygen-plasma treatment16, and chemisorbed molecular monolayers17. Chemisorbed molecular monolayers show particular promise for the modification of both the gate dielectric and the contacts, because such modifications are area-selective, reproducible and when chosen carefully do not adversely affect subsequent processing steps18–22. For metal contacts, thiol monolayers can improve the morphology of the organic semiconductor layer above the contacts and across the contact edges and can lower the injection barrier by tuning the work function of the metal contacts by a few hundred milli-electronvolts23–27. The most utilized and effective molecule to date for improving the charge injection in p-channel organic TFTs is pentafluorobenzenethiol (PFBT)26,28. The increase in the work function is caused by the large interface dipole created by the high density of fluorine atoms in the PFBT monolayer29. The successful use of PFBT to improve the performance of p-channel BC organic TFTs has motivated investigations into other molecules capable of forming monolayers, particularly those with a large number of fluorine atoms to induce a work function shift beyond that obtained with PFBT24. Despite these efforts to improve the contact-semiconductor interface of BC organic TFTs, their contact resistance is still largely inferior to that of the best TC organic TFTs1.

However, recent drift-diffusion-based simulations performed by Zojer et al. predict that BC organic TFTs may exhibit lower contact resistances than otherwise equivalent TC organic TFTs11,30, provided the energy barrier between the source contact and the organic semiconductor is sufficiently low and the gate dielectric is sufficiently thin. Given the importance of the contact resistance for the dynamic TFT performance1,2, this is a potentially critical finding, but an experimental study to confirm the impact of the gate-dielectric thickness on the contact resistance has to our knowledge not yet been performed, although investigations into the effects of the gate-dielectric thickness on other organic-TFT-performance parameters are abundant31–34.

Here, we fabricated BC and TC organic TFTs with different thicknesses of aluminum oxide passivated with an alkylphosphonic acid self-assembled monolayer (SAM) as the gate dielectric. We used gold for the source and drain contacts, PFBT to treat the contacts of the BC TFTs, and the vacuum-deposited small-molecule semiconductor 2,9-diphenyl-dinaphtho-[2,3-b:2’,3’-f]thieno[3,2-b]thiophene (DPh-DNTT)35–37. DPh-DNTT has previously shown low contact resistance in TC TFTs38. We measured the contact resistance using the transmission line method (TLM) and found that when the gate-dielectric thickness is sufficiently small, the contact resistance is indeed smaller in the BC TFTs than in the TC TFTs, supporting the prediction by Zojer et al.30. Further, we fabricated TFTs and circuits on flexible plastic substrates, utilizing an aluminum oxide/SAM hybrid gate dielectric with a thickness of 5.3 nm. For the TC TFTs, we measured a contact resistance of 56 Ωcm, very similar to the contact resistance reported by Yamamura et al. for this device architecture on a glass substrate1. For the BC TFTs, we obtained an even smaller contact resistance of 29 Ωcm, the smallest contact resistance reported to date for organic TFTs using a non-electrolyte gate dielectric39. Furthermore, the signal-propagation delay, measured in flexible 11-stage unipolar ring oscillators at a supply voltage of 3.7 V, is 178 ns per stage for the TC TFTs and 138 ns per stage for the BC TFTs, confirming the benefit of a small contact resistance for the dynamic transistor performance. These are the shortest signal-propagation delays reported to date for organic ring oscillators at a supply voltage of less than 50 V, and they represent a significant step towards the use of organic TFTs in flexible low-power electronics applications.

Results

Organic TFTs with different gate-dielectric thicknesses

To maintain the highest possible degree of comparability between the performance of the BC and TC TFTs, multiple measures were taken to render the devices in the two architectures as equivalent as possible. This is necessary to be able to base the comparison of contact resistance on controlled assumptions. As a first measure to maintain comparability, we fabricated the TFTs in close proximity to each other on a common substrate, utilizing the same gate-oxide layer and the same semiconductor layer (Fig. 1). With this measure in place, we only directly compare those contact resistances that are extracted from TFTs fabricated on the common substrate, i.e., from TFTs sharing the same gate-dielectric thicknesses. Secondly, we settled on a common nominal thickness of the vacuum-deposited DPh-DNTT (Fig. 1a) layer of 20 nm for all TFTs in this study. This is the optimum semiconductor-layer thickness that we have previously identified for TC organic TFTs based on DPh-DNTT37. Note that the semiconductor-layer thickness is relevant for the contact resistance in two ways. In TC organic TFTs, a larger thickness is expected to increase the contact resistance due to the poor vertical carrier transport and the increase in trap-state density with increasing thickness of small-molecular-semiconductor layers1,12,40–42. The intrinsic carrier mobility in the charge accumulation region, in turn, partially determines the bulk resistivity component of the contact resistance in the context of current crowding12. The importance of this effect will depend on the particular semiconductor and the TFT architecture, since a high intrinsic mobility in the accumulation region can mitigate the larger space-charge limitations on injection in the staggered configuration12,43. As a third measure, we omitted the use of contact doping for the TC TFTs, because it would compromise the comparability to the BC organic TFTs. Contact doping has shown the potential to reduce space-charge limitations of the contact resistance in TC TFTs, possibly by reducing the width of the Schottky barrier at the contact-semiconductor interface and by filling trap states in the semiconductor region directly under the contacts and in parts of the channel region adjacent to the contacts, with charges generated by the dopant20,44,45. Finally, PFBT (Fig. 1a) was used to modify the gold bottom contacts, which primarily serves to maintain similar semiconductor morphology across the contact-to-channel interface26,46. The use of PFBT has an additional benefit in terms of the charge-injection barrier at the contact-semiconductor interface of the BC TFTs24.

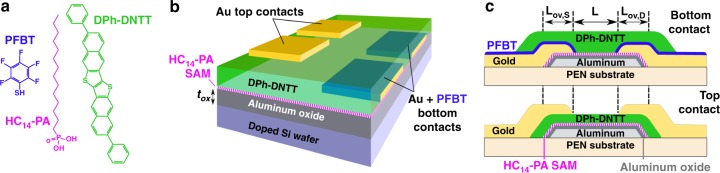

Fig. 1.

Organic thin-film transistors fabricated for this study. a Chemical structures of pentafluorobenzenethiol (PFBT) used to treat the surface of the gold bottom contacts, of n-tetradecylphosphonic acid used for the gate-dielectric self-assembled monolayer (SAM), and of the organic semiconductor 2,9-diphenyl-dinaphtho-[2,3-b:2’,3’-f]thieno[3,2-b]thiophene (DPh-DNTT). b Schematic cross-section of bottom-contact and top-contact organic TFTs fabricated on silicon substrates to study the relation between the gate-oxide thickness and the contact resistance. c Schematic cross-section of bottom-contact and top-contact organic TFTs fabricated on PEN substrates to evaluate the contact resistance and the dynamic performance of TFTs and circuits on flexible plastic substrates

Unfortunately, the PFBT treatment is not applicable to TC TFTs due to the buried contact-semiconductor interface, but it is nonetheless an acceptable measure for the BC TFTs in this comparative study for three reasons. First, due to the high surface energy of the gold contacts, the bottom contacts must be modified in some way to enable a fair comparison of contact resistance between these architectures at all. Second, the very large contact areas in the TFTs on the silicon substrates ensures that the largest contributor to the contact resistance in the TC TFTs is the bulk resistance under the contacts and not the interface resistance10. Finally, an Ohmic contact resistance is required to justify the use of TLM to evaluate the contact resistance47. To that end, gold contacts were used for the TC TFTs, since the work function of gold (5.0 eV) is close to the HOMO energy level of DPh-DNTT (5.3 eV)48, and because penetration of gold clusters into small-molecule semiconductor films has been shown to reduce the dipole barrier that can otherwise form at the contact-semiconductor interface49. In the BC TFTs, Ohmic contact resistance can be realized by treating the gold contacts with an interface layer, which can increase the work function. This is accomplished with PFBT, since the large dipole moment pointing towards the –SH bonding group increases the effective work function of the gold to around 5.4 eV24,50.

Semiconductor thin-film morphology

Atomic force microscopy (AFM) and scanning electron microscopy (SEM) analyses of the vacuum-deposited DPh-DNTT films show that the semiconductor morphology is very similar on all substrates, regardless of the type of substrate (silicon or PEN), the method by which the gate oxide was formed (atomic-layer deposition or plasma oxidation), and the gate-oxide thickness. The DPh-DNTT films show the characteristic terrace-like structure (Fig. 2a–c) that has been observed for this and other small-molecule semiconductors37,38 and is indicative of in-plane π–π stacking. This is additionally confirmed by grazing incidence X-ray diffraction (GIXRD) measurements of the DPh-DNTT films deposited onto the dielectric surface (see Fig. 2d)48. In the particular case of the BC TFTs, SEM, and GIXRD reveal that the treatment of the gold contacts with PFBT promotes the extension of the terrace-like DPh-DNTT film morphology in the channel region along and across the source and drain contact edges (Fig. 2c). Conversely, the GIXRD spectrum from DPh-DNTT deposited onto bare gold shows only the (110) peak, indicating poor in-plane π–π stacking on the gold surface.

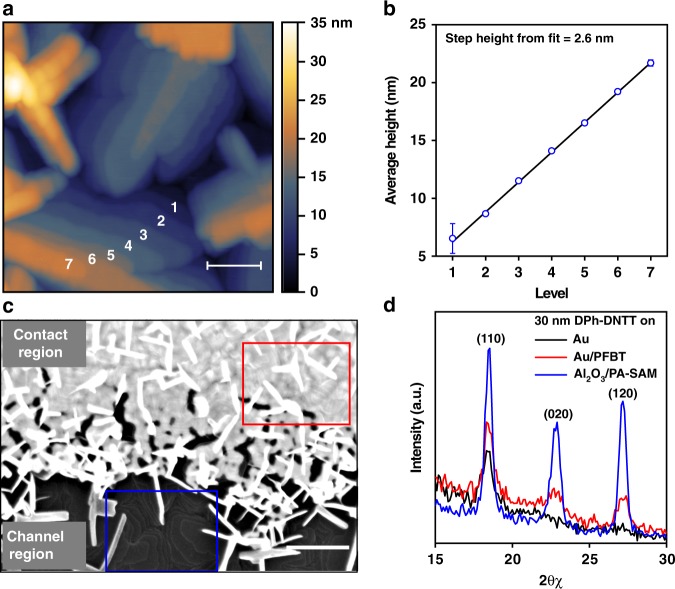

Fig. 2.

Morphological characterization of vacuum-deposited DPh-DNTT films. a AFM topography image of a DPh-DNTT layer formed on the Al2O3/SAM gate dielectric. Individual terrace levels are indicated with numbers 1–7. The scale bar corresponds to 100 nm. b Analysis of the height differences between the terraces. The step height of 2.6 nm corresponds closely to the length of a DPh-DNTT molecule, indicating that the molecules in each layer are oriented approximately upright with respect to the gate-dielectric surface. The data points and the error bars were obtained by local averaging of the terrace height over a large number of locations on each terrace in the AFM height image. c SEM image of the contact edge of a DPh-DNTT bottom-contact TFT with PFBT-treated gold contacts. The terrace morphology of the DPh-DNTT film is distinguishable on the contact surface near the contact edge (red box) and in the channel region (blue box). The scale bar corresponds to 200 nm. d Grazing incidence X-ray diffraction measurements on 30-nm-thick DPh-DNTT films on surfaces consisting of Au (black), PFBT-treated Au (red), and atomic-layer-deposited Al2O3 passivated with n-tetradecylphosphonic acid (PA-SAM, blue). The (110), (020), and (120) peaks are clearly distinguished in both of the latter two cases, signifying in-plane π–π stacking48, while on bare Au only the (110) peak is present

Gate-dielectric thickness and contact resistance

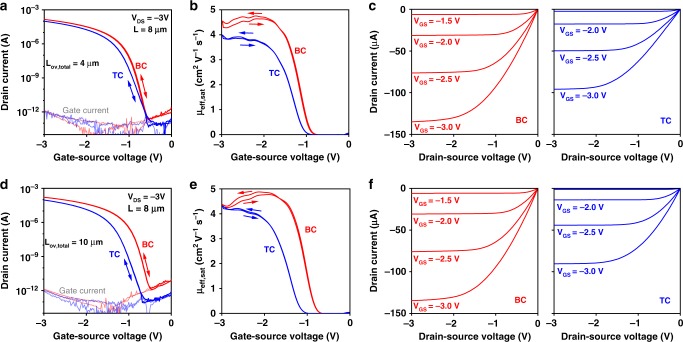

Representative measured transfer characteristics of the BC and TC TFTs fabricated on silicon substrates are shown in Fig. 3a, b. Regardless of gate-dielectric thickness and the TFT architecture, all TFTs have a threshold voltage close to zero, a subthreshold swing smaller than 200 mV/decade, and an on/off current ratio of about 106. To quantify the contact resistance of the TFTs, we employed the widely used transmission line method (TLM)47. The TLM assumes that the total device resistance (R) is the sum of a channel-length-independent and Ohmic contact resistance (RC) comprising both the source and drain contact resistances and a channel resistance proportional to the channel length (L)47. The channel-width-normalized resistance (RW) is determined at a drain-source voltage (VDS) as close to zero as possible (here: VDS = −0.1 V) for a set of TFTs with channel lengths ranging from 6 to 50 µm. Based on the above-mentioned assumptions, the TLM deduces, for each desired gate-overdrive voltage (VGS−Vth), a channel-width-normalized contact resistance (RCW) from the linear dependence on L of RW. In our TLM results, the linear fits of RW versus L for all gate-oxide thicknesses and gate-overdrive voltages are of good quality, with adjusted R² values > 0.9 (Supplementary Figure 1). Regardless of the device architecture and the gate-oxide thickness (tox), RCW is always smaller than 1 kΩcm at sufficiently large VGS−Vth, indicative of a small injection barrier.

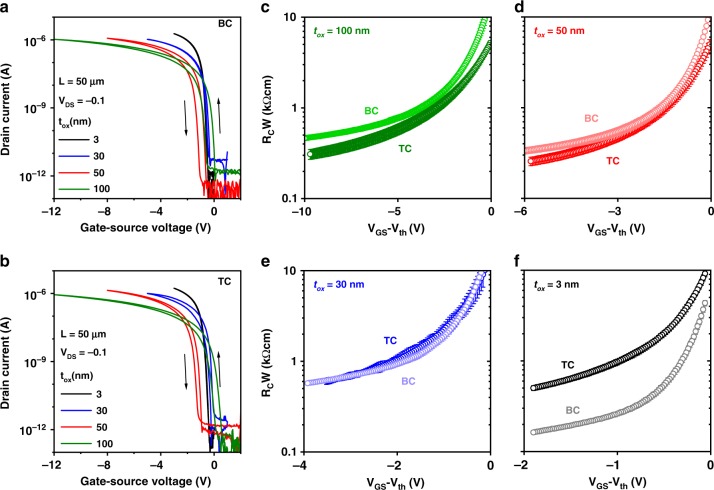

Fig. 3.

Bottom-contact and top-contact DPh-DNTT TFTs with different gate-dielectric thicknesses. The TFTs have gate-oxide thicknesses (tox) of 3, 30, 50, and 100 nm, a channel length of 50 µm, and a channel width of 200 µm. a, b Transfer characteristics measured in the linear regime of operation (VDS = −0.1 V). c–f Channel-width-normalized contact resistance (RCW) of TFTs with channel lengths ranging from 6 to 50 µm extracted in the linear regime of operation (VDS = −0.1 V) and plotted as a function of the gate-overdrive voltage (VGS−Vth), showing the influence of the gate-dielectric thickness on the contact resistance. For the smallest gate-oxide thickness of 3 nm, the contact resistance of the bottom-contact (BC) TFTs is smaller than that of the top-contact (TC) TFTs

The contact resistances obtained for the two device architectures and the four gate-oxide thicknesses are plotted in Fig. 3c–f as a function of the gate-overdrive voltage. As can bee seen, the difference between the contact resistances of the bottom-contact and top-contact TFTs depends on the gate-oxide thickness. It is intriguing to compare these results to a prediction obtained by two-dimensional drift-diffusion simulations, according to which the difference between the contact resistances of BC and TC TFTs will scale with the gate-dielectric thickness30. Indeed, when the gate-oxide thickness is large (≥50 nm), the contact resistance of our TC TFTs is smaller than that of our BC TFTs over the entire range of VGS−Vth. At a medium gate-oxide thickness (30 nm), the contact resistances are approximately equal. When the gate-oxide thickness is sufficiently small (3 nm), the contact resistance in the BC TFTs is significantly smaller than in the TC TFTs over the entire range of gate-overdrive voltages. This confirms that there is an opportunity for BC TFTs to outperform TC TFTs in terms of contact resistance, provided the gate dielectric is sufficiently thin and the injection barrier at the contact-semiconductor interface is small.

In addition to the observation that the difference between the contact resistances of the BC and TC TFTs depends on the gate-oxide thickness, there are also noticeable differences in the shapes of the curves showing the contact resistance as a function of the gate-overdrive voltage (Fig. 3c–f): At small VGS−Vth, the slope of the RCW vs. VGS−Vth curve is always steeper for the BC than for the TC TFTs, whereas at large VGS−Vth, the slope is nearly the same when tox = 100, 50, or 30 nm (note the logarithmic scaling of RCW in Fig. 3c–f). For tox = 3 nm, the slope is always smaller for the BC TFTs and is also the smallest overall. We postulate that these features are related to the dependence of the contact resistance on two factors whose relative contributions depend on the TFT architecture: the geometry-specific electric-field distribution at the contact interface and the bulk resistance of the semiconductor layer between the contacts and the channel. As mentioned previously, the bulk resistance contributes significantly more strongly to the contact resistance in TC than in BC TFTs12,51. In TC TFTs, the bulk resistance is primarily modulated by the thickness of the semiconductor layer, i.e., a greater semiconductor-layer thickness results in a larger access resistance. This would likely result in a larger gate-oxide thickness below which BC TFTs have lower contact resistance than otherwise comparable TC TFTs. For BC TFTs, on the other hand, the contact resistance is primarily determined by the hole-injection barrier at the contact-semiconductor interface and the presence of space charges in the semiconductor43. Therefore, the contact resistance depends strongly on the electric field and less so on the semiconductor-layer thickness30,52,53. In addition, the contact resistance in BC TFTs has been shown to be dependent on the carrier mobility of the semiconductor. If the mobility is small and the charge injection efficient, space charges may build up that will inhibit carrier flow away from the region directly adjacent to the source contact, especially at small gate-source voltages40,43. Hence, for the BC TFTs with tox = 3 nm, the contact resistance and its dependence on the gate-overdrive voltage are reduced overall.

Low-voltage bottom-contact and top-contact TFTs on flexible PEN substrates

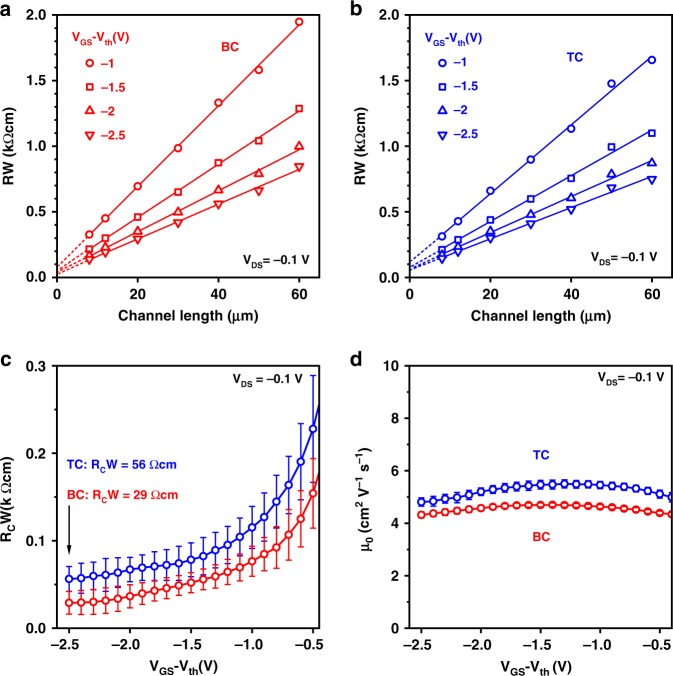

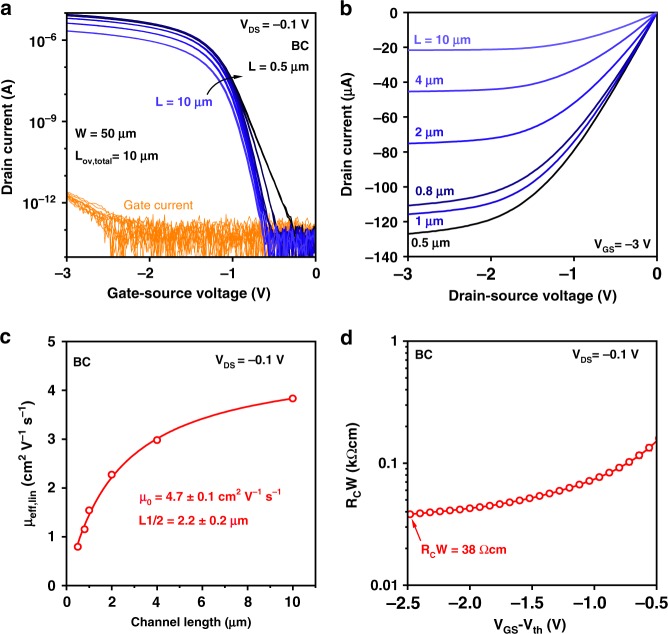

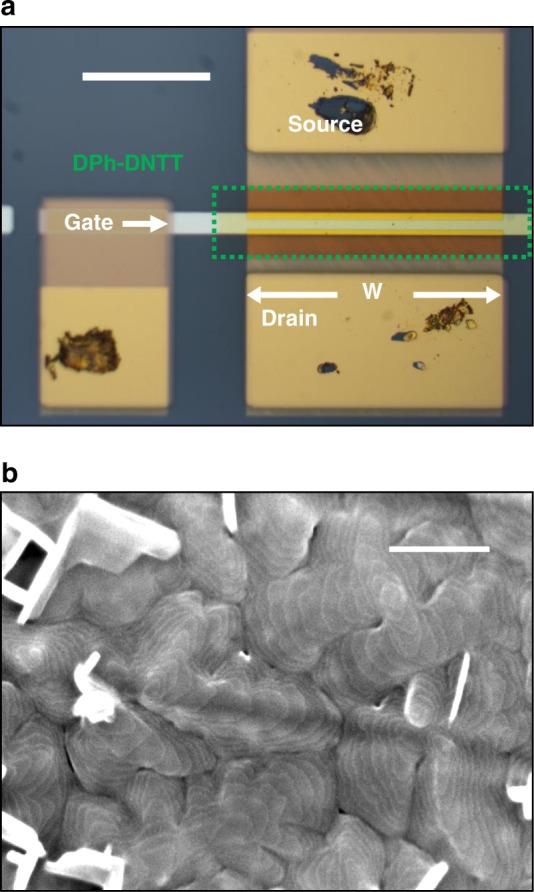

We next show that the small contact resistance of bottom-contact DPh-DNTT TFTs with very thin gate dielectrics is evident also in TFTs fabricated on flexible plastic substrates (schematic shown in Fig. 1c). A photograph of a BC TFT fabricated on a PEN substrate is shown in Fig. 4a. An SEM image of the channel region of a DPh-DNTT TFT on a PEN substrate (Fig. 4b) indicates that the thin-film morphology of the DPh-DNTT films on the PEN substrates on which the plasma-grown aluminum oxide is used for the gate dielectric is similar to the thin-film morphology on the silicon substrates with the atomic-layer-deposited aluminum oxide. This is to be expected, since both oxide surfaces were treated in an identical manner with an n-tetradecylphosphonic acid SAM. For the extraction of the contact resistance we performed TLM analysis on TFTs with channel lengths ranging from 8 to 60 µm, a total gate-to-contact overlap (sum of the gate-to-source and gate-to-drain overlaps, Lov,total) of 10 µm, and a channel width of 200 µm. The results of the TLM measurements are shown in Fig. 5 and summarized in Table 1. The quality of the linear fits to the data in the RW vs. L graphs is again excellent, with adjusted R² ≥ 0.99. At a gate-overdrive voltage of −2.5 V, the TC TFTs have a channel-width-normalized contact resistance of 56 Ωcm, very similar to the record-low contact resistance reported by Yamamura et al. for TFTs fabricated in the same device architecture1. Despite the lower intrinsic channel mobility (Fig. 5d), the BC TFTs have an even smaller contact resistance of 29 Ωcm, which is to our knowledge the smallest contact resistance reported to date for organic transistors fabricated in the coplanar device architecture. For comparison, Stadlober et al. reported a contact resistance of 80 Ωcm for bottom-gate, bottom-contact pentacene TFTs in which the surface of the gold source and drain contacts had been exposed to ultraviolet radiation and ozone in order to induce a favorable pentacene morphology on the contacts8. Braga et al. reported the smallest contact resistance yet reported for organic TFTs of any architecture in electrolyte-gated top-gate staggered poly(3-hexylthiophene) TFTs in which strong doping of the semiconductor from the electrolyte resulted in a very small contact resistance of 1 Ωcm39.

Fig. 4.

DPh-DNTT TFTs fabricated on flexible PEN substrates. a Optical microscopy image of a bottom-contact TFT with a channel length of 8 µm, a total gate-to-contact overlap (sum of the gate-to-source and gate-to-drain overlaps) of 10 µm, and a channel width of 200 µm on a flexible PEN substrate. The scale bar corresponds to 100 µm. b SEM image of the DPh-DNTT film in the channel region of a bottom-contact TFT on the same substrate. The terrace-like morphology of the organic semiconductor film is clearly distinguished and similar to that formed on the silicon substrates with atomic-layer-deposited aluminum oxide. The scale bar corresponds to 200 nm

Fig. 5.

TLM analysis of bottom-contact and top-contact DPh-DNTT TFTs fabricated on flexible PEN substrates. The TFTs have a gate-dielectric thickness of 5.3 nm, channel lengths ranging from 8 to 60 µm, and a channel width of 200 µm. a, b Linear fits to the total width-normalized resistance (RW) at selected gate-overdrive voltages (VGS−Vth). c Width-normalized contact resistance (RCW) plotted as a function of the gate-overdrive voltage. The error bars correspond to the standard error from the linear regression at each gate-overdrive voltage. d Intrinsic channel mobility (µ0) plotted as a function of the gate-overdrive voltage

Table 1.

Summary of the results of the TLM measurements performed on top-contact and bottom-contact DPh-DNTT TFTs fabricated on flexible PEN substrates

| Device architecture | RCW (Ωcm) at VGS−Vth = −2.5 V | LT (µm) at VGS−Vth = −2.5 V | µ0 (cm2 V−1 s−1) | L1/2 (µm) |

|---|---|---|---|---|

| TC | 56 ± 14 | 2.4 ± 0.6 | 5.7 ± 0.1 | 4.3 ± 0.2 |

| BC | 29 ± 13 | 1.1 ± 0.5 | 4.9 ± 0.1 | 2.6 ± 0.2 |

The intrinsic channel mobility (µ0) and the channel length at which the effective carrier mobility is half the intrinsic channel mobility (L1/2) were extracted from the fits in Supplementary Figure 2c

In addition to the contact resistance, the TLM analysis also yields the transfer length (LT). In staggered TFTs, LT is the contact length over which 63% of the charge-carrier exchange occurs between the contact and the semiconductor12,54. For our TC TFTs, the transfer length is 2.4 µm, which is significantly smaller than the gate-to-source and gate-to-drain overlaps (Lov,S and Lov,D), signifying that the injection is not limited by the contact area55. Despite the fact that the physical meaning of the transfer length in BC TFTs has so far not been elucidated, we still report it in Table 1 for comparison. The effective carrier mobility (µeff) extracted from the transfer curves in the linear regime of operation (VDS = −0.1 V) is less affected by the contact resistance in TFTs with long channel lengths (Supplementary Figure 2c). The intrinsic channel mobility (µ0) and the channel length at which the effective carrier mobility is half the intrinsic channel mobility (L1/2) were extracted using Equation 1 from ref. 37.

The transfer and output characteristics of DPh-DNTT TFTs with a channel length of 8 µm and total gate-to-contact overlaps (Lov,total = Lov,S + Lov,D) of 4 and 10 µm are shown in Fig. 6. All TFTs have threshold voltages of about −1 V and on/off current ratios, here defined as the ratio between the drain current at VGS = −3V and the lowest drain current measured in the transfer curve, between 108 and 109. The smaller contact resistance of the BC TFTs results in a larger effective carrier mobility compared to the TC TFTs (see Fig. 6 and Table 2).

Fig. 6.

Static electrical characteristics of bottom-contact and top-contact DPh-DNTT TFTs on flexible PEN substrates. The TFTs have a gate-dielectric thickness of 5.3 nm, a channel length of 8 µm, a channel width of 200 µm, and a total gate-to-contact overlap of 4 µm (a–c) or 10 µm (d–f). a, d Transfer characteristics measured in the saturation regime (VDS = −3 V). b, e Effective carrier mobility extracted from the transfer characteristics in the saturation regime (VDS = -3 V). c, f Output characteristics of the same TFTs

Table 2.

Summary of the static performance of top-contact and bottom-contact DPh-DNTT TFTs shown in Fig. 6, having a channel length of 8 µm and a channel width of 200 µm

| Device architecture | Lov,total (µm) | µeff,sat (cm² V−1 s−1) | SS (mV/dec) | On/off ratio |

|---|---|---|---|---|

| TC | 4 | 3.9 | 94 | 109 |

| TC | 10 | 4.2 | 92 | 109 |

| BC | 4 | 4.6 | 62–64 | 109 |

| BC | 10 | 4.4 | 68 | 108 |

VDS −3 V for all measurements

All TFTs have subthreshold swings (SS) smaller than 100 mV/decade, but those of the BC TFTs are notably smaller (62–68 mV/decade) than those of the TC TFTs (92–94 mV/decade). For the BC TFT with the smallest subthreshold swing, we have extracted the exact subthreshold swing using two different methods: once by fitting an exponential function to the data over a range of 200 mV in the subthreshold regime and once by point-wise derivation of the measured transfer curves (Supplementary Figure 3). Depending on the method and the applied drain-source voltage, the subthreshold swing is between 62 and 64 mV/decade. To our knowledge, this is the smallest subthreshold swing reported to date for organic TFTs, regardless of device architecture, gate dielectric, and semiconductor56–59. The observation that the BC TFTs have a notably smaller subthreshold swing than the TC TFTs suggests that the subthreshold swing is affected not only by the charge-trap density at the interface between the gate dielectric and the semiconductor layer (which is nominally identical in the two device architectures), but also by the charge-trap density in the semiconductor volume that separates the top contacts from the gate-induced carrier channel which the carriers have to traverse in the TC TFTs.

Flexible low-voltage bottom-contact TFTs with small channel lengths

Often when the channel length is reduced, short-channel effects, such as drain-induced barrier lowering and increased off-state drain current, can become more prominent55. To investigate whether our flexible BC TFTs show any of these effects, we have fabricated short-channel bottom-contact DPh-DNTT TFTs on PEN substrates. These TFTs have a channel length ranging from 0.5 µm to 10 µm, a channel width of 50 µm, and a total gate-to-contact overlap of 10 µm. Regardless of the channel length, all TFTs have an on/off current ratio of at least 108 (Fig. 7a), and the output curves do not show any noticeable non-linearity at small drain-source voltages that would indicate Schottky contacts (Fig. 7b)60. All TFTs with a channel length of at least 0.8 µm show effective carrier mobilities above 1 cm2 V−1 s−1 (Fig. 7c). The TLM analysis again shows a low contact resistance of 38 Ωcm at a gate-overdrive voltage of −2.5 V (Fig. 7d, Supplementary Figure 4).

Fig. 7.

Short-channel bottom-contact DPh-DNTT TFTs on flexible PEN substrates. The TFTs have a gate-dielectric thickness of 5.3 nm, channel lengths ranging from 0.5 to 10 µm, a channel width of 50 µm, and a total gate-to-contact overlap of 10 µm. a Transfer characteristics measured in the linear regime of operation (VDS = −0.1 V). b Output characteristics of the same TFTs measured at a gate-source voltage of −3 V. c Effective carrier mobility (µeff) plotted as a function of the channel length. The error bars correspond to the standard error from the linear regression at each gate-overdrive voltage. d Channel-width-normalized contact resistance (RCW) plotted as a function of the gate-overdrive voltage (VGS−Vth)

Dynamic performance of flexible bottom-contact and top-contact TFTs

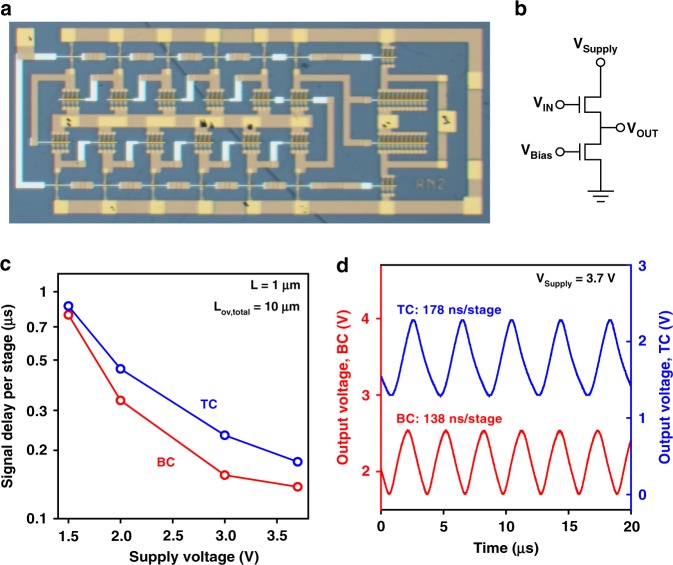

Finally, to demonstrate the benefit of a small contact resistance for the dynamic TFT performance, 11-stage unipolar ring oscillators were fabricated on the same PEN substrates as the TFTs discussed above (Fig. 8). All TFTs in the ring oscillators have a channel length of 1 µm and a total gate-to-contact overlap of 10 µm. For this channel length and gate-to-contact overlap, the effective carrier mobilities are 1.3 cm2 V−1 s−1 for the TC TFTs and 1.7 cm2 V−1 s−1 for the BC TFTs (Supplementary Figure 5). The ring oscillators utilize the biased-load inverter design61. The signal-propagation delay (τ) is calculated from the oscillation frequency (fosc) and the number of stages (n) by τ = 1/(2nfosc)62. At a supply voltage of 3.7 V, the measured signal-propagation delay is 178 ns per stage for the ring oscillator based on the TC TFTs and 138 ns per stage for the ring oscillator based on the BC TFTs, confirming the effect of the contact resistance on the frequency behavior of the TFTs. These signal delays are to our knowledge the shortest delays reported to date for organic ring oscillators on flexible substrates63 and the shortest delays for organic ring oscillators on any substrate at a supply voltage of less than 50 V64.

Fig. 8.

Dynamic performance of unipolar ring oscillators on flexible PEN substrates. a Photograph of an 11-stage unipolar ring oscillator based on bottom-contact DPh-DNTT TFTs with a channel length of 1 µm and a total gate-to-contact overlap of 10 µm. b Circuit diagram of the biased-load inverters implemented for the ring oscillators. c Signal-propagation delay per stage measured on ring oscillators based on top-contact(TC) and bottom-contact(BC) TFTs plotted as a function of the supply voltage. d Output signals measured at a supply voltage of 3.7 V, showing stage delays of 178 ns for the ring oscillator based on TC TFTs and 138 ns for the ring oscillator based on BC TFTs. Depending on the supply voltage, the bias voltage is between −1 and −2.5 V

Discussion

Through an analysis of the contact resistance in TFTs with different gate-dielectric thicknesses, we have found strong experimental indications that it is possible to fabricate bottom-gate, bottom-contact organic TFTs that show lower contact resistance than comparable top-contact TFTs. As predicted by Zojer et al.30, we have found that for sufficiently small gate-dielectric thickness, bottom-contact TFTs have lower contact resistance than top-contact TFTs, so long as sufficient measures are taken to control the semiconductor thin-film morphology across the contact-channel interface and to minimize the barrier height at the contact-semiconductor interface. This was accomplished here by employing a thin hybrid gate dielectric composed of aluminum oxide passivated with an alkylphosphonic acid SAM in combination with PFBT-modified gold source and drain contacts in the bottom-contact TFTs. The potential of this approach to improve the static and dynamic performance of organic TFTs is most significantly exemplified here by bottom-contact DPh-DNTT TFTs with a gate-dielectric thickness of 5.3 nm fabricated on flexible PEN substrates which show a channel-width-normalized contact resistance as small as 29 Ωcm. In addition to a low contact resistance, bottom-contact TFTs can show improvements in other performance metrics, including subthreshold swings as small as 62–64 mV/decade and on/off current ratios as high as 109. Furthermore, the lower contact resistance of the bottom-contact TFTs enables higher frequencies in flexible organic-TFT circuits operating at low voltages, as shown here by the signal-propagation delay of 138 ns per stage at a supply voltage of 3.7 V, obtained in 11-stage unipolar ring oscillators based on bottom-contact DPh-DNTT TFTs fabricated on flexible PEN substrates. It is possible that even lower contact resistance is achievable with other combinations of interface layers, gate dielectrics and semiconductors in the bottom-gate, bottom-contact architecture. Further reductions in contact resistance, ideally in combination with smaller lateral TFT dimensions, are then expected to yield even higher dynamic TFT performance2.

Methods

TFTs with different gate-oxide thicknesses on Si substrates

The TFTs that were used to study the relation between the gate-dielectric thickness and the contact resistance were fabricated on heavily doped silicon wafers (525 µm thickness). To reduce the effects of substrate-to-substrate variations, bottom-contact (BC) and top-contact (TC) TFTs with a common gate-dielectric thickness were fabricated on the same substrate in close proximity to each other (separated by about 100–200 µm). The silicon substrate serves as a global gate electrode for all TFTs on the substrate (Fig. 1a). As the first component of the gate dielectric, aluminum oxide (Al2O3) was deposited by atomic-layer deposition (ALD, Savannah 100, Cambridge NanoTech Inc.; substrate temperature 250 °C, 10 cycles/nm) with a thickness of 3, 30, 50, or 100 nm. The silicon wafers were then cut into strips (0.5 × 3 cm). The Al2O3 surface was activated by oxygen plasma (Oxford Instruments; oxygen flow rate 30 sccm, partial pressure 10 mTorr, plasma power 200 W, duration 30 s) and then passivated with a self-assembled monolayer (SAM) by immersing the substrate into a 1-mM solution of n-tetradecylphosphonic acid (PCI Synthesis, Newburyport, MA, U.S.A.) in 2-propanol (VLSI grade) for one to two hours33. Afterwards, the substrates were rinsed in 2-propanol and dried on a hotplate (150 °C, 1 min). The capacitance of these dielectrics was calculated assuming relative dielectric constants (ϵr) of 9 for Al2O3 and 2.5 for the phosphonic acid SAM33. Next, gold bottom source and drain contacts were deposited by thermal evaporation in vacuum onto the surface of the Al2O3/SAM gate dielectric and modified with a monolayer of pentafluorobenzenethiol (PFBT, Santa Cruz Biotechnology, Heidelberg, Germany) by immersing the substrates into a 10-mM solution of PFBT in 2-propanol for 30 min. The substrates were then rinsed with 2-propanol. A 20-nm-thick layer of DPh-DNTT (Nippon Kayaku, kindly provided by Koichi Ikeda) was then deposited by sublimation in vacuum (base pressure 10–6 mbar, substrate temperature 90 °C, deposition rate 0.3 Å s−1) onto all four substrates simultaneously (in order to minimize substrate-to-substrate variations). Prior to electrical measurements, the unpatterned DPh-DNTT layer was scratched away around each set of source and drain contacts using a probe needle. Electrical measurements were then performed on the BC TFTs, followed by depositing the gold top source and drain contacts onto the organic semiconductor layer in close proximity to the bottom contacts and performing the electrical measurements on the TC TFTs. All contacts have an area of 200 × 200 µm and were patterned using a silicon stencil mask (IMS Chips, Stuttgart, Germany) with channel lengths ranging from 4 to 50 µm38.

TFTs and ring oscillators on flexible PEN substrates

We fabricated bottom-contact and top-contact DPh-DNTT TFTs and 11-stage unipolar ring oscillators on 125-µm-thick flexible polyethylene naphthalate substrates (Teonex® Q65 PEN; provided by William A. MacDonald, DuPont Teijin Films, Wilton, U.K.) using a set of four silicon stencil masks (IMS Chips, Stuttgart, Germany) to define interconnects, gate electrodes, source and drain contacts, and the organic semiconductor layer (Fig. 1b)62,65. Prior to fabrication, the PEN substrates were baked at a temperature of 100 °C for 1 h and cleaned with 2-propanol. In the first fabrication step, 30-nm-thick gold interconnects and probe pads were deposited through the first stencil mask. For the gate electrodes, a 30-nm-thick layer of aluminum was deposited through the second stencil mask. In the case of the TFTs discussed above that were used to evaluate the relation between the gate-dielectric thickness and the contact resistance, the gate oxide was deposited by atomic-layer deposition. ALD has the advantage that the oxide thickness can be easily scaled over a wide range. However, one issue with ALD is that the oxide is not easily deposited selectively, so that subtractive patterning is usually required to create access to the gate electrodes underneath the oxide. For the TFTs discussed above, this issue was avoided by contacting the gate electrode (i.e., the doped silicon substrate) from the backside of the substrate. For devices and circuits on plastic substrates this is not an option. Therefore, for the TFTs and ring oscillators on PEN, we used plasma oxidation (Oxford Instruments, 30 sccm oxygen, 10 mTorr, 200 W, 30 s) to form a thin aluminum oxide (AlOx) layer selectively on the patterned aluminum gate electrodes. The completed gate dielectric is a stack of the 3.6-nm-thick layer of AlOx and an n-tetradecylphosphonic acid SAM, resulting in a total dielectric thickness of 5.3 nm and a unit-area capacitance of 0.7 µF cm−2.37. For all subsequent layers, the fabrication procedure was the same as described above for the TFTs on silicon substrates, with the exception that the semiconductor layer is patterned with a stencil mask. In the ring oscillators, the drive TFTs have channel widths of 80 µm and the bias TFTs have channel widths of 20 µm. In the two buffer inverters prior to the output node the drive TFT has a channel width of 220 µm and the bias TFT has a channel width of 60 µm.

Semiconductor thin-film morphology characterization

The thin-film morphology of the DPh-DNTT layer was characterized using tapping-mode atomic force microscopy (AFM, Bruker Dimension Icon), scanning electron microscopy (SEM, Zeiss Merlin), and grazing incidence X-ray diffraction (GIXRD, Rigaku SmartLab). The X-ray diffractometer is equipped with a 9 kW copper source. The grazing incidence angle was set to 0.15°. The detector moved horizontally at 2θ = 0.15° and 2θχ from 15° to 30° in steps of 0.1°. The X-ray beam size was set to 5 × 0.1 mm. The diffraction peaks were assigned using the PDXL software with the standard Gaussian distribution method. SEM and AFM were performed on completely processed TFTs, while GIXRD required samples either without any metal or with the gold layer covering the entire substrate, due to the large spot size required for the measurement. Three silicon substrates were thus prepared for the GIXRD measurements, with 30-nm thick DPh-DNTT deposited onto 30-nm thick Au, 30-nm thick Au treated with PFBT, and atomic-layer-deposited Al2O3 passivated with an n-tetradecylphosphonic acid SAM.

Electrical measurements

All electrical measurements, including the bias-stress measurements summarized in Supplementary Figure 6, were performed in ambient air at room temperature (292 K). The capacitance of the gate dielectrics, the current-voltage characteristics of the TFTs, and the signal-propagation delays of the ring oscillators were measured using an Agilent 4156 C Semiconductor Parameter Analyzer, a Tektronix TDS1000 oscilloscope, a Femto DPLCA-200 low-noise transimpedance amplifier, and gold-plated tungsten probe tips (EPP GmbH) with a tip radius of 50 µm for contacting the probe pads.

Supplementary information

Acknowledgements

The authors acknowledge Kazuo Takimiya (RIKEN Center for Emergent Matter Science, Wako, Saitama, Japan) as well as Koichi Ikeda, Yuichi Sadamitsu and Satoru Inoue (Nippon Kayaku, Tokyo, Japan) for providing the organic semiconductor DPh-DNTT and Marion Hagel at the Max Planck Institute for Solid State Research for expert technical assistance. This work was partially funded by the German Research Foundation (DFG) under the grants KL 2223/6–1 and KL 2223/6–2 (SPP FFlexCom), KL 2223/7–1, and INST 35/1429–1 (SFB 1249). K.Z. acknowledges the funding provided by the Austrian Science Fund through the FWF Elise Richter fellowship (V317-N20).

Author contributions

J.W.B. and H.K. devised the experimental details of the study. J.W.B. fabricated all devices and samples and performed electrical and morphological measurements. J.W.B., H.K. and K.Z. wrote the article. B.P. and P.K.L.C. performed grazing incidence X-ray characterization. F.L. and J.N.B. manufactured the silicon stencil masks used to fabricate the TFTs and circuits. S.L. and H.K. supervised the project. All the authors discussed the results and contributed to the development of the final manuscript.

Data availability

The data that support the findings of this study are available from the corresponding author on reasonable request.

Competing interests

The authors declare no competing interests.

Footnotes

Journal peer review information: Nature Communications thanks Cedric Rolin and the other anonymous reviewers for their contribution to the peer review of this work.

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Contributor Information

James W. Borchert, Email: J.Borchert@fkf.mpg.de

Hagen Klauk, Email: H.Klauk@fkf.mpg.de.

Supplementary information

Supplementary Information accompanies this paper at 10.1038/s41467-019-09119-8.

References

- 1.Yamamura A, et al. Wafer-scale, layer-controlled organic single crystals for high-speed circuit operation. Sci. Adv. 2018;4:eaao5758. doi: 10.1126/sciadv.aao5758. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 2.Klauk H. Will we see gigahertz organic transistors? Adv. Electron. Mater. 2018;4:1700474. doi: 10.1002/aelm.201700474. [DOI] [Google Scholar]

- 3.Paterson AF, et al. Recent progress in high-mobility organic transistors: a reality check. Adv. Mater. 2018;30:1801079. doi: 10.1002/adma.201801079. [DOI] [PubMed] [Google Scholar]

- 4.Wagner V, Wöbkenberg P, Hoppe A, Seekamp J. Megahertz operation of organic field-effect transistors based on poly(3-hexylthiopene) Appl. Phys. Lett. 2006;89:243515. doi: 10.1063/1.2405414. [DOI] [Google Scholar]

- 5.Noh YY, Zhao N, Caironi M, Sirringhaus H. Downscaling of self-aligned, all-printed polymer thin-film transistors. Nat. Nanotechnol. 2007;2:784–789. doi: 10.1038/nnano.2007.365. [DOI] [PubMed] [Google Scholar]

- 6.Gundlach DJ, et al. An experimental study of contact effects in organic thin film transistors. J. Appl. Phys. 2006;100:024509. doi: 10.1063/1.2215132. [DOI] [Google Scholar]

- 7.Kim CH, Bonnassieux Y, Horowitz G. Fundamental benefits of the staggered geometry for organic field-effect transistors. IEEE Electron Device Lett. 2011;32:1302–1304. doi: 10.1109/LED.2011.2160249. [DOI] [Google Scholar]

- 8.Stadlober B, et al. Orders-of-magnitude reduction of the contact resistance in short-channel hot embossed organic thin film transistors by oxidative treatment of Au-electrodes. Adv. Funct. Mater. 2007;17:2687–2692. doi: 10.1002/adfm.200700294. [DOI] [Google Scholar]

- 9.Shim CH, Maruoka F, Hattori R. Structural analysis on organic thin-film transistor with device simulation. IEEE Trans. Electron Devices. 2010;57:195–200. doi: 10.1109/TED.2009.2035540. [DOI] [Google Scholar]

- 10.Richards TJ, Sirringhaus H. Analysis of the contact resistance in staggered, top-gate organic field-effect transistors. J. Appl. Phys. 2007;102:094510. doi: 10.1063/1.2804288. [DOI] [Google Scholar]

- 11.Gruber M, et al. Impact of materials versus geometric parameters on the contact resistance in organic thin-film transistors. Adv. Funct. Mater. 2013;23:2941–2952. doi: 10.1002/adfm.201203250. [DOI] [Google Scholar]

- 12.Fischer A, et al. Nonlinear contact effects in staggered thin-film transistors. Phys. Rev. Appl. 2017;8:054012. doi: 10.1103/PhysRevApplied.8.054012. [DOI] [Google Scholar]

- 13.Braga D, Horowitz G. High-Performance organic field-effect transistors. Adv. Mater. 2009;21:1473–1486. doi: 10.1002/adma.200802733. [DOI] [Google Scholar]

- 14.Schroeder R, Majewski LA, Grell M. Improving organic transistor performance with Schottky contacts. Appl. Phys. Lett. 2004;84:1004–1006. doi: 10.1063/1.1645993. [DOI] [Google Scholar]

- 15.Natali D, Caironi M. Charge injection in solution-processed organic field-effect transistors: physics, models and characterization methods. Adv. Mater. 2012;24:1357–1387. doi: 10.1002/adma.201104206. [DOI] [PubMed] [Google Scholar]

- 16.Kim, W. K., Hong, K. & Lee, J. L. Enhancement of hole injection in pentacene organic thin-film transistor of O2 plasma-treated Au electrodes. Appl. Phys. Lett.89, 87–90 (2006).

- 17.Gundlach DJ, Jia L, Jackson TN. Pentacene TFT with improved linear region characteristics using chemically modified source and drain electrodes. IEEE Electron Device Lett. 2001;22:571–573. doi: 10.1109/55.974580. [DOI] [Google Scholar]

- 18.Lin YY, Gundlach DJ, Nelson SF, Jackson TN. Stacked pentacene layer organic thin-film transistors with improved characteristics. IEEE Electron Device Lett. 1997;18:606–608. doi: 10.1109/55.644085. [DOI] [Google Scholar]

- 19.Acton O, et al. Simultaneous modification of bottom-contact electrode and dielectric surfaces for organic thin-film transistors through single-component spin-cast monolayers. Adv. Funct. Mater. 2011;21:1476–1488. doi: 10.1002/adfm.201002035. [DOI] [Google Scholar]

- 20.Liu C, Xu Y, Noh YY. Contact engineering in organic field-effect transistors. Mater. Today. 2015;18:79–96. doi: 10.1016/j.mattod.2014.08.037. [DOI] [Google Scholar]

- 21.Kim CH, et al. Decoupling the effects of self-assembled monolayers on gold, silver, and copper organic transistor contacts. Adv. Mater. Interfaces. 2015;2:1400384. doi: 10.1002/admi.201400384. [DOI] [Google Scholar]

- 22.Casalini S, Bortolotti CA, Leonardi F, Biscarini F. Self-assembled monolayers in organic electronics. Chem. Soc. Rev. 2017;46:40–71. doi: 10.1039/C6CS00509H. [DOI] [PubMed] [Google Scholar]

- 23.Liu D, Miao Q. Recent progress in interface engineering of organic thin film transistors with self-assembled monolayers. Mater. Chem. Front. 2017;2:11–21. doi: 10.1039/C7QM00279C. [DOI] [Google Scholar]

- 24.Mei Y, et al. Interface engineering to enhance charge injection and transport in solution-deposited organic transistors. Org. Electron. 2017;50:100–105. doi: 10.1016/j.orgel.2017.07.032. [DOI] [Google Scholar]

- 25.Singh KA, et al. Effect of self-assembled monolayers on charge injection and transport in poly (3-hexylthiophene) -based field-effect transistors at different channel length scales. ACS Appl. Mater. Interfaces. 2011;3:2973–2978. doi: 10.1021/am200449x. [DOI] [PubMed] [Google Scholar]

- 26.Niazi MR, et al. Contact-induced nucleation in high-performance bottom-contact organic thin film transistors manufactured by large-area compatible solution processing. Adv. Funct. Mater. 2016;26:2371–2378. doi: 10.1002/adfm.201502428. [DOI] [Google Scholar]

- 27.Risteska A, Steudel S, Nakamura M, Knipp D. Structural ordering versus energy band alignment: Effects of self-assembled monolayers on the metal/semiconductor interfaces of small molecule organic thin-film transistors. Org. Electron. 2014;15:3723–3728. doi: 10.1016/j.orgel.2014.10.023. [DOI] [Google Scholar]

- 28.Gundlach DJ, et al. Contact-induced crystallinity for high-performance soluble acene-based transistors and circuits. Nat. Mater. 2008;7:216–221. doi: 10.1038/nmat2122. [DOI] [PubMed] [Google Scholar]

- 29.De Boer B, Hadipour A, Mandoc MM, Van Woudenbergh T, Blom PWM. Tuning of metal work functions with self-assembled monolayers. Adv. Mater. 2005;17:621–625. doi: 10.1002/adma.200401216. [DOI] [Google Scholar]

- 30.Zojer K, Zojer E, Fernandez AF, Gruber M. Impact of the capacitance of the dielectric on the contact resistance of organic thin-film transistors. Phys. Rev. Appl. 2015;4:044002. doi: 10.1103/PhysRevApplied.4.044002. [DOI] [Google Scholar]

- 31.Tsukagoshi K, et al. Suppression of short channel effect in organic thin film transistors. Appl. Phys. Lett. 2007;91:113508. doi: 10.1063/1.2785118. [DOI] [Google Scholar]

- 32.Ortiz RP, Facchetti A, Marks TJ. High- k organic, inorganic, and hybrid dielectrics for low-voltage organic field-effect transistors. Chem. Rev. 2010;110:205–239. doi: 10.1021/cr9001275. [DOI] [PubMed] [Google Scholar]

- 33.Aghamohammadi M, et al. Threshold-voltage shifts in organic transistors due to self-assembled monolayers at the dielectric: evidence for electronic coupling and dipolar effects. ACS Appl. Mater. Interfaces. 2015;7:22775–22785. doi: 10.1021/acsami.5b02747. [DOI] [PubMed] [Google Scholar]

- 34.Liu C, Xu Y, Li Y, Scheideler W, Minari T. Critical impact of gate dielectric interfaces on the contact resistance of high-performance organic field-effect transistors. J. Phys. Chem. C. 2013;117:12337–12345. doi: 10.1021/jp4023844. [DOI] [Google Scholar]

- 35.Niimi K, Kang MJ, Miyazaki E, Osaka I, Takimiya K. General synthesis of dinaphtho[2,3- b:2’,3’- f]thieno[3,2- b]thiophene (DNTT) derivatives. Org. Lett. 2011;13:3430–3433. doi: 10.1021/ol2010837. [DOI] [PubMed] [Google Scholar]

- 36.Yokota T, et al. Flexible low-voltage organic transistors with high thermal stability at 250 °c. Adv. Mater. 2013;25:3639–3644. doi: 10.1002/adma.201300941. [DOI] [PubMed] [Google Scholar]

- 37.Kraft U, et al. Flexible low-voltage organic complementary circuits: finding the optimum combination of semiconductors and monolayer gate dielectrics. Adv. Mater. 2015;27:207–214. doi: 10.1002/adma.201403481. [DOI] [PubMed] [Google Scholar]

- 38.Kraft U, et al. Detailed analysis and contact properties of low-voltage organic thin-film transistors based on dinaphtho[2,3-b:2′,3′-f]thieno[3,2-b]thiophene (DNTT) and its didecyl and diphenyl derivatives. Org. Electron. 2016;35:33–40. doi: 10.1016/j.orgel.2016.04.038. [DOI] [Google Scholar]

- 39.Braga D, Ha M, Xie W, Frisbie CD. Ultralow contact resistance in electrolyte-gated organic thin film transistors. Appl. Phys. Lett. 2010;97:193311. doi: 10.1063/1.3518075. [DOI] [Google Scholar]

- 40.Pesavento PV, Puntambekar KP, Frisbie CD, McKeen JC, Ruden PP. Film and contact resistance in pentacene thin-film transistors: Dependence on film thickness, electrode geometry, and correlation with hole mobility. J. Appl. Phys. 2006;99:094504. doi: 10.1063/1.2197033. [DOI] [Google Scholar]

- 41.Matsumoto T, Ou-Yang W, Miyake K, Uemura T, Takeya J. Study of contact resistance of high-mobility organic transistors through comparisons. Org. Electron. 2013;14:2590–2595. doi: 10.1016/j.orgel.2013.06.032. [DOI] [Google Scholar]

- 42.Xu Y, et al. Understanding thickness-dependent charge transport in pentacene transistors by low-frequency noise. IEEE Electron Device Lett. 2013;34:1298–1300. doi: 10.1109/LED.2013.2277613. [DOI] [Google Scholar]

- 43.Merces L, de Oliveira RF, Gomes HL, Bof Bufon CC. The role of the electrode configuration on the electrical properties of small-molecule semiconductor thin-films. Org. Electron. 2017;49:107–113. doi: 10.1016/j.orgel.2017.06.041. [DOI] [Google Scholar]

- 44.Minari T, et al. Highly enhanced charge injection in thienoacene-based organic field-effect transistors with chemically doped contact. Appl. Phys. Lett. 2012;100:93303. doi: 10.1063/1.3690949. [DOI] [Google Scholar]

- 45.Ante F, et al. Contact doping and ultrathin gate dielectrics for nanoscale organic thin-film transistors. Small. 2011;7:1186–1191. doi: 10.1002/smll.201002254. [DOI] [PubMed] [Google Scholar]

- 46.Heimel G, Salzmann I, Duhm S, Koch N. Design of organic semiconductors from molecular electrostatics. Chem. Mater. 2011;23:359–377. doi: 10.1021/cm1021257. [DOI] [Google Scholar]

- 47.Luan S, Neudeck GW. An experimental study of the source/drain parasitic resistance effects in amorphous silicon thin film transistors. J. Appl. Phys. 1992;72:766–772. doi: 10.1063/1.351809. [DOI] [Google Scholar]

- 48.Kang MJ, Miyazaki E, Osaka I, Takimiya K, Nakao A. Diphenyl derivatives of dinaphtho[2,3- b:2′,3′-f]thieno[3,2- b]thiophene: Organic semiconductors for thermally stable thin-film transistors. ACS Appl. Mater. Interfaces. 2013;5:2331–2336. doi: 10.1021/am3026163. [DOI] [PubMed] [Google Scholar]

- 49.Horowitz G. Organic thin film transistors: from theory to real devices. J. Mater. Res. 2004;19:1946–1962. doi: 10.1557/JMR.2004.0266. [DOI] [Google Scholar]

- 50.Choi S, et al. A study on reducing contact resistance in solution-processed organic field-effect transistors. ACS Appl. Mater. Interfaces. 2016;8:24744–24752. doi: 10.1021/acsami.6b07029. [DOI] [PubMed] [Google Scholar]

- 51.Li J, Ou-Yang W, Weis M. Electric-field enhanced thermionic emission model for carrier injection mechanism of organic field-effect transistors: understanding of contact resistance. J. Phys. D Appl. Phys. 2017;50:035101. doi: 10.1088/1361-6463/aa4e95. [DOI] [Google Scholar]

- 52.Kim CH, Bonnassieux Y, Horowitz G, Member S. Charge distribution and contact resistance model for coplanar organic field-effect transistors. IEEE Trans. Electron Devices. 2013;60:280–287. doi: 10.1109/TED.2012.2226887. [DOI] [Google Scholar]

- 53.Brondijk JJ, Torricelli F, Smits ECP, Blom PWM, De Leeuw DM. Gate-bias assisted charge injection in organic field-effect transistors. Org. Electron. 2012;13:1526–1531. doi: 10.1016/j.orgel.2012.04.029. [DOI] [Google Scholar]

- 54.Berger HH. Contact resistance and contact resistivity. J. Electrochem. Soc. 1972;119:507–514. doi: 10.1149/1.2404240. [DOI] [Google Scholar]

- 55.Ante F, et al. Contact resistance and megahertz operation of aggressively scaled organic transistors. Small. 2012;8:73–79. doi: 10.1002/smll.201101677. [DOI] [PubMed] [Google Scholar]

- 56.Zschieschang U, et al. Flexible low-voltage organic thin-film transistors and circuits based on C 10 -DNTT. J. Mater. Chem. 2012;22:4273–4277. doi: 10.1039/C1JM14917B. [DOI] [Google Scholar]

- 57.Blülle B, Häusermann R, Batlogg B. Approaching the trap-free limit in organic single-crystal field-effect transistors. Phys. Rev. Appl. 2014;1:034006. doi: 10.1103/PhysRevApplied.1.034006. [DOI] [Google Scholar]

- 58.Xu W, Wang F, Rhee SW. Quasi-ordering in spontaneously associated surface dipoles: an intrinsic interfacial factor for high-kpolymer insulated organic field-effect transistors. J. Mater. Chem. 2012;22:1482–1488. doi: 10.1039/C1JM14398K. [DOI] [Google Scholar]

- 59.Zhao J, Tang W, Li Q, Liu W, Guo X. Fully Solution processed bottom-gate organic field-effect transistor with steep subthreshold swing approaching the theoretical limit. IEEE Electron Device Lett. 2017;38:1465–1468. doi: 10.1109/LED.2017.2742952. [DOI] [Google Scholar]

- 60.Chiang CS, et al. Top-gate staggered amorphous silicon thin-film transistors: series resistance and nitride thickness effects. Jpn. J. Appl. Phys. 1998;37:5914–5920. doi: 10.1143/JJAP.37.5914. [DOI] [Google Scholar]

- 61.Elsobky M, et al. A digital library for a flexible low-voltage organic thin-film transistor technology. Org. Electron. 2017;50:491–498. doi: 10.1016/j.orgel.2017.08.028. [DOI] [Google Scholar]

- 62.Zschieschang U, et al. Megahertz operation of flexible low-voltage organic thin-film transistors. Org. Electron. 2013;14:1516–1520. doi: 10.1016/j.orgel.2013.03.021. [DOI] [Google Scholar]

- 63.Heremans, P. et al. Thin-film transistors and circuits on plastic foil. IEEE Int. Electron Devices Meet. 10.1109/IEDM.2009.5424346 (2009).

- 64.Ogier SD, et al. Uniform, high performance, solution processed organic thin-film transistors integrated in 1 MHz frequency ring oscillators. Org. Electron. 2018;54:40–47. doi: 10.1016/j.orgel.2017.12.005. [DOI] [Google Scholar]

- 65.Zaki T, et al. Digital-to-analog converter using organic P-type thin-film transistors on glass. IEEE J. Solid-State Circuits. 2012;47:292–300. doi: 10.1109/JSSC.2011.2170639. [DOI] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Supplementary Materials

Data Availability Statement

The data that support the findings of this study are available from the corresponding author on reasonable request.