Abstract

The negative-capacitance field-effect transistor(NC-FET) has attracted tremendous research efforts. However, the lack of a clear physical picture and design rule for this device has led to numerous invalid fabrications. In this work, we address this issue based on an unexpectedly concise and insightful analytical formulation of the minimum hysteresis-free subthreshold swing (SS), together with several important conclusions. Firstly, well-designed MOSFETs that have low trap density, low doping in the channel, and excellent electrostatic integrity, receive very limited benefit from NC in terms of achieving subthermionic SS. Secondly, quantum-capacitance is the limiting factor for NC-FETs to achieve hysteresis-free subthermionic SS, and FETs that can operate in the quantum-capacitance limit are desired platforms for NC-FET construction. Finally, a practical role of NC in FETs is to save the subthreshold and overdrive voltage losses. Our analysis and findings are intended to steer the NC-FET research in the right direction.

Subject terms: Electronic devices, Electronic devices, Electronic and spintronic devices

Negative Capacitance field-effect-transistor has long been touted as a steep-slope logic switch. Here, the authors present a lucid formulation that reveals the intrinsic limitation of NC-FETs in achieving steep-slope switching characteristics and highlights their more practical role in saving the voltage losses in modern FETs.

Introduction

Although the global semiconductor industry has reached a staggering ~$500 billion, to further continue such a flourishing growth, low-voltage or steep-slope logic transistor is crucial for simultaneous reduction of power consumption along with dimensional scalability of the metal oxide semiconductor field-effect transistors (MOSFETs)1,2. However, lowering of the supply voltage, has failed to keep pace with the feature-size scaling because the thermionic emission based transport mechanism of MOSFETs limits the steepness of their transfer characteristics in the subthreshold regime, i.e., SS, to be ≥ 60 mV per decade at room temperature3, thereby constraining the energy/power efficiency. To overcome this limitation, many steep-slope (SS < 60 mV per decade) device concepts have been proposed, such as tunnel FETs4,5, impact ionization MOSFETs6, NC-FETs7 etc., (Supplementary Note 1). Among these devices, NC-FETs have been attracting most interest in recent years7–28, thanks to their simple structure that involves minimal penalty in added (w.r.t. MOSFETs) manufacturing complexity. The NC layer can be implemented with single-domain (best case) ferroelectric (FE) materials, which are featured by their “double-well” energy landscape versus polarization29 (see Supplementary Note 2 and Supplementary Fig. 2a). The anomalous polarization response of FE material systems in the metastable state to external electric field, results in an effective NC (see Supplementary Fig. 2b). It has been suggested7 that connecting an FE layer in series with a normal dielectric (DE) capacitor with a proper capacitance matching between FE and DE can stabilize (see Supplementary Fig. 2c) the metastable NC state of the FE layer, which has been experimentally verified recently19,20. It was also predicted that NC-FETs may be plagued by hysteresis, if the capacitance matching process is inappropriately performed, which should be avoided in logic applications. Driven by the enthusiasm toward this novel “steep-slope” device, experimentalists have been indiscriminately trying to incorporate FE materials in the gate of various “X-FETs”, where X can be SOI, Fin, nanowire (NW), 2D (such as MoS2, WSe2 etc.), or 1D (such as carbon nanotube (CNT), graphene nanoribbon (GNR) etc.), generating numerous “NC-FETs” in the past several years8–15. However, none of them exhibit SSs that are noticeably smaller than 60 mV per decade and simultaneously free of hysteresis during both AC and DC operations (see Supplementary Table 1). Such a deviation from expectation stems from a lack of clear understanding of NC-FETs for many device experimentalists. In this sense, comprehending what NC-FETs really are, how to design NC-FETs, and what can be expected from NC-FETs, can play a decisive role in identifying a genuinely low-voltage switch that can revolutionize next-generation electronics including computing, sensing, and communication.

Previous attempts at understanding the workings of NC-FETs either assumed the total FET gate capacitance to be a constant7,18, i.e., the bias-dependent channel capacitance was ignored, or were focused on performing intensive numerical simulations21–25 or complex analytical modeling26,27 of a specific NC-FET such as NC-FinFET and NC-2DFET etc., in which the generic device physics, design rule and major challenges of NC-FETs get obscured. In this work, we analytically formulate the slope of the transfer characteristics of a generic NC-FET structure, from which a physics-rich but concise picture is innovatively extracted for “visualizing” the intriguing device physics and design space of NC-FETs. This picture can not only serve as a convenient design platform for NC-FET experimentalists, but also allow us to find a novel functionality of NC in modern MOSFET applications.

More specifically, using fundamental FET and NC theory, we uncover the intriguing interplay between hysteresis and subthermionic (or < 60 mV per decade) SS in NC-FETs in a very simple and generic manner, and arrive at several important conclusions that are contrary to many contemporary understandings on NC-FETs. Our analysis reveals that well-designed scaled MOSFETs that have low trap density and low doping in the channel, and excellent electrostatic integrity by employing state-of-the-art FET structures, such as SOI-FET, FinFET, NW-FET, CNT-FET, and 2D material based FETs etc., which have negligible parasitic capacitance compared to the gate capacitance, receive very limited benefit from NC in terms of achieving small SS (< 60 mV per decade). Secondly, we derive an unexpectedly concise and insightful formula for the minimum SS for hysteresis-free operation, which allows us to uncover that the quantum capacitance is the limiting factor for NC-FETs to achieve hysteresis-free subthermionic SS, and thus, only FETs that can operate in the quantum-capacitance limit are desired platforms for NC-FET construction. Thirdly, our analysis unveils a hitherto concealed knowledge that compared to the target of achieving subthermionic SS, a more practical role of NC in FETs could be to save the subthreshold voltage loss caused by short-channel effects, and the overdrive voltage loss caused by the large quantum capacitance, provided the polarization response of ferroelectric materials can be enhanced to allow the NC to function effectively at high frequencies (GHz range).

Results

Capacitor network in a generic NC-FET

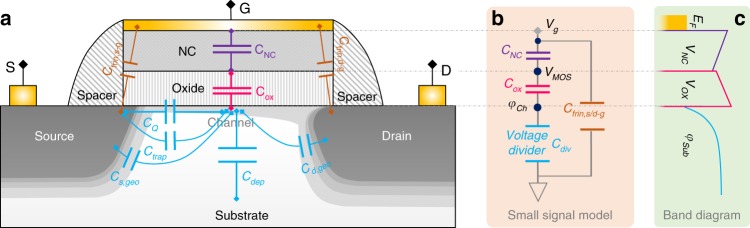

The switching of FETs is realized by electrostatic (or capacitive) modulation of the potential of the channel through which current is conducted. Figure 1a depicts all relevant capacitors in a generic NC-FET structure. The discussion throughout this work is based on n-type device, if not specified otherwise. CNC and COX are the capacitances of the NC layer and gate oxide, respectively. CQ, Ctrap, Cdep, and Cs/d,geo represent quantum, interface trap induced, depletion, and source/drain geometrical capacitances, respectively, and can be grouped as gate voltage divider capacitance Cdiv,

| 1 |

CQ in FETs describes the change of electron charge density (Qe) in response to channel potential (φCh) modulation, and can be expressed as

| 2 |

where q is the elementary charge, i is the index of conduction modes, DOSi is the density-of-states of the ith mode, Ec,i is the energy level of the ith mode, and Ef is the Fermi level. CQ approaches zero below threshold, while approaches q2·ΣiDOSi above threshold. Ctrap is the trap state filling induced capacitance (~dQtrap/dφCh). Cdep is the geometrical capacitance of the depletion layer. Cs/d,geo stem from the capacitive coupling from source and drain. This capacitance also captures the effect of fringing field from source/drain toward gate through the path inside the device in the short-channel condition28. As indicated in the small-signal diagram in Fig. 1b, Cdiv prevents the channel potential φCh from being efficiently modulated by the gate voltage, and thus its unnecessary components (Ctrap, Cdep, and Cs/d,geo) are normally minimized in modern MOSFET design. Note that the source/drain-to-gate fringing capacitance (including overlap capacitance) Cfrin,s/d-g is directly connected between power rails (gate to source/drain), and hence is irrelevant to central-channel potential modulation (that determines device performance) in any FETs with long-channel or with excellent electrostatic integrity. Therefore, any steep slope of fabricated NC-FETs12 in long-channel condition should not be mis-attributed to Cfrin,s/d-g. In the operation of NC-FETs, the negative CNC induces a negative voltage drop (VNC) across the NC layer, as illustrated in the conduction band diagram in Fig. 1c, to compensate for the positive voltage (VMOS) on the underlying FET, thereby potentially reducing the total gate voltage (Vg = VNC + VMOS).

Fig. 1. Capacitors in a generic NC-FET structure and its small-signal model.

a Capacitors potentially involved in determining the channel potential of a generic NC-FET. CQ, Cdep, Cs/d,geo, and Ctrap are the quantum-, depletion-, s/d geometrical, and trap induced, capacitors, respectively. CNC and COX represent the capacitance of the NC and oxide layers, respectively. b Simplified small-signal model for NC-FETs. Note that in the small-signal model, the change in the values of the capacitances near the vicinity of a given DC bias point is negligible. Cdiv is the voltage divider capacitance that includes CQ, Cdep, Cs/d,geo, and Ctrap. The effect of fringing capacitance, Cfrin,s/d-g, is screened by power rails, and hence is irrelevant to channel potential control. c The conduction band diagram of NC-FETs under a positive gate bias. Note that due to negative CNC, VNC is negative.

Formulating Id–Vg swing of a generic NC-FET

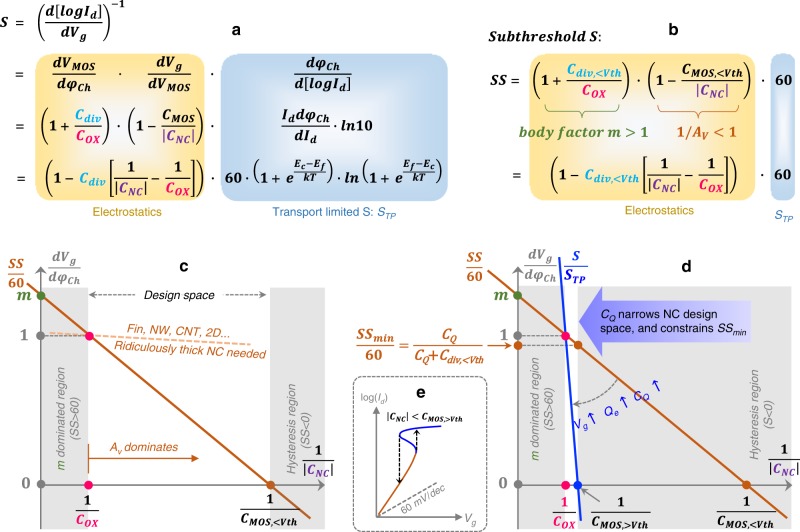

To quantify the operation mechanism of NC-FET, the slope or swing (S) of the entire Id–Vg curve of a generic NC-FET is formulated in the form of decoupled contributions from electrostatics and transport mechanism (Fig. 2a, with detailed derivations in Supplementary Note 3). CMOS is the total gate capacitance of the FET under the NC layer (Fig. 1b),

| 3 |

Fig. 2. Impact of electrostatics and quantum capacitance on NC-FET design space.

a Formulating Id-Vg slope or swing (S) by decoupling the electrostatics and transport contributions. STP is the transport limited S. b S is reduced to subthreshold S (SS) in the subthreshold regime. STP is reduced to 60 mV per decade. Body factor m (>1) and voltage gain AV (>1) compete with each other in determining SS. c Visualizing the SS formula and its physics. In the shaded region on the LHS, m dominates, thus SS > 60 mV per decade. In the shaded region on the RHS, SS < 0, represents the appearance of hysteresis. The design space here is between the two shaded regions where AV dominates and 0 < SS < 60. The dashed line illustrates the ultra-small negative slope of SS/60 line (which implies that SS/60 can be noticeably below 1 only for 1/|CNC| ≫ 1/Cox) for Fin-, nanowire (NW)-, carbon nanotube (CNT)- and 2D- FETs, indicating very small |CNC|, or equivalently very thick NC layer in these devices is required to obtain NC benefit. d A picture that captures all essential quasi-static device physics of NC-FETs. Note that in the near and above-threshold region, the SS/60 line transforms to the S/STP line, which rotates clockwise due to the rapidly increasing quantum-capacitance CQ with gate bias till a nearly vertical position is reached when the device is fully turned on. Since S in the entire range of Id–Vg curve should be guaranteed to be positive, in order to prevent hysteresis in both sub- and super- threshold regimes, the lower bound of 1/|CNC| is extended to 1/CMOS,>Vth, leading to a narrow NC design space and a minimum hysteresis-free SS ( = CQ/(CQ + Cdiv,<Vth)) at 1/|CNC| = 1/CMOS,>Vth. e Id-Vg curve of an example NC-FET in which 1/|CNC| is designed to be within the shaded region on the RHS of (d). Although SS (brown colored portion) is small, negative S (i.e., hysteresis) appears in the near- or above-threshold region (blue colored portion).

STP represents the thermionic transport mechanism limited S. The expression of STP in Fig. 2a only takes into account the lowest conduction mode for conciseness, which does not affect the conclusions drawn in this paper. All numerical simulations carried out in this work rigorously include all conduction modes.

The battle field for any steep-slope device to pursue small SS is the subthreshold regime where Ef is well below Ec. In this regime, STP is reduced to 60 mV per decade at room temperature (according to the expression of STP in Fig. 2a)- often referred to as “Boltzmann tyranny”. Moreover, CQ is negligibly small (according to Eq. (2)), and hence Cdiv is reduced to Cdiv,<Vth = Ctrap + Cdep + Cs,geo + Cd,geo, CMOS is reduced to CMOS,<Vth = Cdiv,<Vth·COX/(Cdiv,<Vth + COX). S is reduced to SS, as expressed in Fig. 2b. m is called the body factor that captures the gate efficiency of the FET under the NC layer, and AV is the voltage gain introduced by the NC layer,

| 4 |

which is expected to be larger than 1. In other words, m and AV compete with each other in determining SS.

NC does not help good FETs

The detailed physics of the equation in Fig. 2b can be “visualized” in Fig. 2c. As shown, when |CNC| is larger than COX, m wins the competition, and SS > 60 mV per decade (shaded region on the left). When |CNC| is smaller than COX, AV dominates SS, and enables sub-60 SS. However, |CNC| should not be smaller than CMOS,<Vth, otherwise AV and SS become smaller than zero (Eq. (4) and Fig. 2b, and the shaded region on the right in Fig. 2c), and the total gate capacitance Cg = |CNC|·CMOS,<Vth/(|CNC| − CMOS,<Vth) (note CNC = −|CNC|) is negative, indicating that the metastable state of the NC layer (see Supplementary Fig. 2) is not well stabilized by the FET structure underneath. In the charge-voltage or current-voltage characteristics, the metastable negative Cg or negative SS portion is reflected as hysteresis7, resembling that in a ferroelectric memory device30. As indicated in Fig. 2b, Cdiv,<Vth represents the slope of SS/60 line. As long as Cdiv,<Vth is not too large compared to COX, the design space of 1/|CNC| (normally spanned by designing the NC layer thickness, TNC) for sub-60 SS, i.e., between 1/CMOS,<Vth (=1/COX + 1/Cdiv,<Vth) and 1/COX, is reasonably spacious. Meanwhile, Cdiv,<Vth should not be too small either, otherwise |CNC| is required to be equally small to achieve steep slope (from Fig. 2b), as illustrated by the dashed line in Fig. 2c. Considering the generally large absolute value of the dielectric constant of ferroelectric materials (|ɛNC|)7,11,30, small |CNC| translates to very thick NC layer, which is impractical for state-of-the-art very-large-scale-integration (VLSI) technology. Modern MOSFETs have evolved into the ultrathin-body (UTB) era, in the form of semiconductor-on-insulator (SOI)31, Fin-FET32, NW-FET33, CNT-FET33, and 2D-FET34 et al., accompanied with the requirement of high-quality material/interface and low channel doping (to suppress impurity scattering and performance variation), all of which are the constituents of a “good” FET for optimal gate efficiency and current drive. Unfortunately, these designs result in small Cs/d,geo, Cdep, and Ctrap, resulting in very small Cdiv,<Vth and hence small CMOS,<Vth (Eq. (3)) (also verified with numerical simulation in Supplementary Note 4). In other words, NC does not help these “good” MOSFET platforms achieve steep slope.

Although required Cdiv,<Vth (as discussed above) is not feasible in state-of-the-art MOSFET platforms, it can be introduced in unconventional ways. For example, in traditional bulk MOSFET technology, Cdiv,<Vth can be realized in the form of high doping induced Cdep; In SOI structure, the buried oxide (BOX) can be designed to be comparable with gate oxide in terms of capacitance value, thereby serving as an effective Cdep; In poorly designed ultra-short-channel devices and/or devices with poor interface, Cs/d,geo and/or Ctrap can, although in undesired ways, supply an appreciable Cdiv,<Vth.

Quantum capacitance may “kill” NC-FETs

Although, as discussed above, the tuning of Cdiv,<Vth is non-trivial, the greatest challenge of NC-FETs arises from the rapidly increasing channel electron density (or CQ in Eq. (2)) with gate bias near and above threshold (Supplementary Note 5), significantly increasing Cdiv, which is the slope of S/STP versus 1/|CNC| (see the equation in Fig. 2a). Increased Cdiv is equivalent to clockwise rotating the S/STP line w.r.t. the SS/60 line, as illustrated in Fig. 2d. In order to guarantee hysteresis-free I-V characteristics, or positive S, not only in the subthreshold regime, but also near- and above-threshold regimes, the lower bound of the forbidden hysteresis region (shaded region on the RHS of Fig. 2d) of 1/|CNC| gets extended from 1/CMOS,<Vth ( = 1/Cdiv,<Vth + 1/COX) to 1/CMOS,>Vth = (1/Cdiv,>Vth + 1/COX ≈ 1/CQ + 1/COX), which is very close to 1/COX, since CQ in near- and above-threshold regimes generally becomes much larger than COX in typical Si or Ge MOSFETs. In other words, the design space of NC is significantly narrowed by CQ. If |CNC| is designed to be smaller than CMOS,>Vth, although SS can be noticeably lower than 60 mV per decade, a hysteresis appears at the near- or above-threshold regime, as schematically illustrated in Fig. 2e, ending up with a memory device rather than a logic device. In the design of a FET structured FE memory30, in which hysteresis is a desired property, the oxide layer is normally made very thin, or completely removed if the employed FE material is a good insulator. Interestingly, the reason for these devices always exhibiting hysteresis becomes very clear from Fig. 2d. With finite oxide layer thickness, if 1/|CNC| is designed to be within the “m dominated region” (shaded region on the LHS of Fig. 2d), S in the entire range of Id–Vg curve is guaranteed to be positive, i.e., Id–Vg curve is free of hysteresis. On the other hand, in the absence of an oxide layer (i.e., 1/COX ≈ 0), the “m dominated region” disappears, leaving negligible 1/|CNC| design space (between 0 and 1/CMOS,>Vth ≈1/CQ) in which hysteresis is absent. Hence, in the feasible 1/|CNC| range, S is always smaller than 0, which guarantees hysteresis. Figure 2d also gives the minimum SS without suffering from hysteresis to be

| 5 |

at |CNC| = CMOS,>Vth (see derivation in Supplementary Note 6).

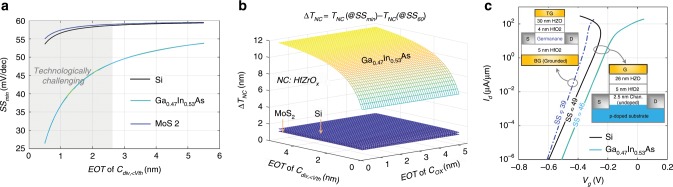

Designing NC-FET in the quantum-capacitance limit

Inspired by Eq. (5), lowering CQ, desirably into the quantum-capacitance limit (CQ < COX), seems to be an effective direction in enlarging the NC design space and reducing SSmin. According to the dependence of CQ on DOS (Eq. (2)), low-DOS material systems could help. In order to illustrate this, SSmin is evaluated for Si (as reference), Ga0.47In0.53As, and monolayer MoS2, as shown in Fig. 3a, versus Cdiv,<Vth, which is normalized w.r.t the equivalent oxide thickness (EOT) for the convenience of comparison. If not specified otherwise, Hf0.5Zr0.5O2 (parameters are provided in Supplementary Fig. 2) is used as the NC material in the calculation throughout this work. As shown, the low-DOS Ga0.47In0.53As can provide much smaller SSmin, w.r.t. Si and MoS2. However, it is technologically rather difficult to implement large Cdiv,<Vth with EOT less than 3 nm (i.e., close to COX in state-of-the-art MOSFETs), thus hysteresis-free sub-60 SS and sub-50 SS can hardly be achieved in Si/MoS2 and Ga0.47In0.53As-based NC-FETs, respectively.

Fig. 3. Impact of density-of-states on SSmin and NC design space.

a SSmin at room temperature and b NC thickness design space (∆TNC) for Si, Ga0.47In0.53As, and monolayer MoS2. The effective DOS (conduction band) of Si and Ga0.47In0.53As are ~2.8 × 1019 cm−3 and ~2.1 × 1017 cm−3, respectively. The DOS of single-layer MoS2 is ~2.4 × 1014 eV−1·cm−2. The low-DOS Ga0.47In0.53As exhibits significant advantages. Cdiv,<Vth and COX are normalized w.r.t the equivalent oxide thickness (EOT). c With the same device structure/size, Ga0.47In0.53As device can (in principle) achieve smaller SS, w.r.t. Si device, without hysteresis. SS of monolayer Germanane device can reach 39 mV per decade due to its low-DOS. The DOS of single-layer Germanane is ~2.9 × 1013 eV−1·cm−2.

Figure 3b shows the NC thickness design space (ΔTNC, essentially the width of the design space in Fig. 2d) in terms of normalized Cdiv,<Vth and COX. ΔTNC of Si and MoS2 based NC-FETs almost vanish due to their large DOS, which is consistent with their near-60 SSmin shown in Fig. 3a. The low-DOS of Ga0.47In0.53As can help derive a feasible ΔTNC of ~12 nm due to its low CQ. Further reduction of the DOS of GaInAs system by increasing the In content is possible, but will result in lowered bandgap that degrades ON-OFF current ratio. To further confirm the effect of DOS and hence CQ, numerical simulations are carried out to obtain the Id–Vg curves of Si and Ga0.47In0.53As based NC-FETs, as shown in Fig. 3c. Cdiv,<Vth in bulk Si and Ga0.47In0.53As devices are intentionally implemented as Cdep with an engineered doping profile as illustrated in the inset figure on the RHS. With exactly the same device structure/size, Ga0.47In0.53As device shows a hysteresis-free SS of ~46 mV per decade, while Si device shows a SS of ~49 mV per decade suffering from hysteresis, which is consistent with the predicted hysteresis-free SSmin in Fig. 3a. The thinness of 2D material is intrinsically beneficial in terms of achieving low DOS. However, the most widely studied 2D semiconductor, MoS2, although is promising for short-channel MOSFETs34, suffers due to its large electron effective mass (~0.6m0) that results in high DOS. In contrast, Germanane (also a single-layer 2D semiconductor) possesses a much smaller electron effective mass (~0.07m0) and a finite bandgap of ~1.5 eV35, thus can be an ideal channel material for NC-FET design. Figure 3c also shows simulated Id–Vg curve of a Germanane NC-FET. The atomic scale thickness of Germanane, as well as the lack of effective doping techniques prevent Germanane based NC-FETs from exploiting Cdep. Instead, a HfO2 based BOX layer is employed to act as an effective Cdep, as illustrated in the inset on the LHS of Fig. 3c. By optimizing the oxide and NC thicknesses, SS of Germanane based NC-FETs can be as low as 39 mV per decade.

The role of NC non-linearity

It is worthwhile to mention that the P–E characteristics in the NC region of a FE material is not strictly linear, as shown in Supplementary Fig. 2b, i.e., |CNC| is not a constant with bias or charge density. Using the analysis developed above, it is found that this secondary effect can slightly enlarge the NC design space, and may help a bit in deriving smaller SSmin (Supplementary Note 7).

IMG: Borrow parasitic charge for polarization in NC

An internal metal gate (IMG) has been proposed to be inserted between the NC layer and the underlying MOSFET. It has been found that the IMG induced fringing capacitance (that helps induce further polarization in the NC layer) can help improve SS21. The physical mechanism of this effect is well captured by the developed analysis in this work (Supplementary Note 8). Note that although IMG is beneficial to the performance of NC-FETs from a capacitance point of view, it will introduce floating gate effect and domain formation that may destabilize NC18.

A practical role of NC for FETs: Voltage-loss saver

As discussed above, although hysteresis-free sub-60 mV per decade SS, can be achieved in NC-FETs in principle, judicious device structural design for a proper Cdiv,<Vth, rigorous matching between NC and the total gate capacitance (CMOS), which involves a strongly bias-dependent CQ, and non-trivial fabrication efforts are required to demonstrate a prototype NC-FET. Moreover, there is a critical thickness for ferroelectric materials (~5 nm for BiFeO3)36, below which the ferroelectricity begins to degrade, and hence |ɛNC| decreases, leading to reduced |CNC|. Such a thickness dependence of ferroelectricity introduces additional difficulty to precisely match CMOS,>Vth in the narrow design space, as illustrated in Fig. 2d. Therefore, all fabricated “NC-FETs” in which FE layers are simply inserted in the gate of Fin-FETs, NW-FETs, Tunnel-FETs, or 2D-FETs, which are not suitable for NC-FET construction, are unlikely to be genuine NC-FETs. Moreover, almost all of the observed steep SSs in those fabricated “NC-FETs”9–12 appear at low drain current level (close to the OFF current and/or current noise floor) only, which not only obscures their prospects, but also, again, casts doubt on their claims of being NC-FETs, since those observations are not consistent with or supported by the fundamental physics-based predictions of the subthreshold behavior of NC-FETs in this work and other relevant work in the literature. In fact, more and more studies37–40 have indicated that the steep SSs observed in many of those fabricated “NC-FETs” can be attributed to the transient effects (not captured in this work because of the ideal steady-state model employed, aimed at uncovering the essential physics and evaluating the upper-limit of NC-FET performance) during the measurement and/or ferroelectric polarization dynamics, instead of the negative capacitance effect through capacitance matching, which provide further support to the analysis and the insightful conclusions of this work, albeit from a different perspective. Here, based on the SS physics of NC-FETs developed above, we also provide our insight/suggestion to those who are trying to interpret the observed steep SSs in various reported “NC-FETs” from transient effect point of view. Essentially, to achieve subthermionic SS, the polarization dynamics should allow FE layer in the subthreshold regime to be greatly depolarized and allow the weak residual polarization to be self-sustained (i.e., D ≈ QMOS,<Vth ≈ 0 or P ≈ −ɛ0E), instead of relying on the charge compensation (i.e., ɛ0E ≈ 0 or P ≈ D ≈ QMOS,<Vth) from the FET underneath, since in modern FETs, Cdiv,<Vth and CMOS,<Vth are negligibly small. More details are provided in Supplementary Note 9. It is worth noting that such transient effects induced steep SSs, impose strict constraints on bias sweeping rate/direction, and operating frequency38,40, and therefore are of limited practical use in logic transistor applications, and hence, irrelevant to the discussion in this work. It is also worthwhile to mention that the polarization response of ferroelectric materials must be enhanced41,42 to allow the NC to function effectively at high frequencies (GHz range).

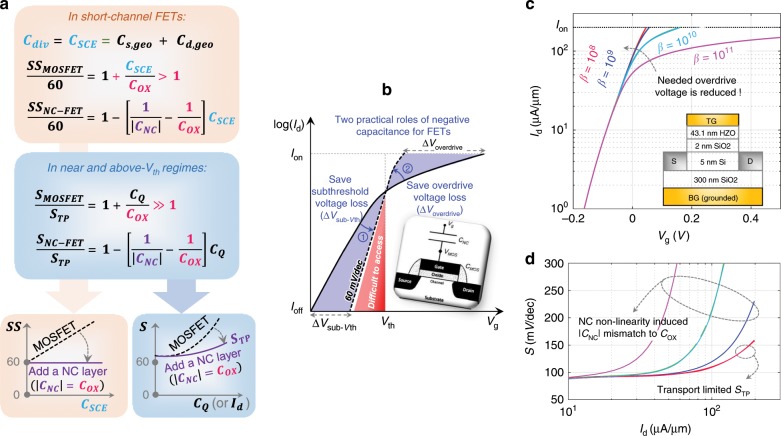

In fact, in terms of saving switching energy, NC-FET does not have to be designed as a steep-slope device. As indicated in Fig. 2d, the S/STP line rotates with bias about a constant (bias and NC material independent) point (1/COX, 1), which provides an important implication for a new role NC can play. To make it clearer, SS formula for short-channel MOSFETs and NC-FETs, and S formula in the near and above-threshold regimes for MOSFETs and NC-FETs of any scale, are reorganized in Fig. 4a. In the short-channel MOSFETs, Cdiv is mainly attributed to short-channel effect (SCE), specifically, Cdiv = CSCE = Cs,geo + Cd,geo. CSCE prevents gate voltage in subthreshold regime to drop entirely in the channel, i.e., it causes a subthreshold gate voltage loss on the gate oxide, which is reflected by a poor SS, SSMOSFET = 60(1 + CSCE/COX) > 60 (see detailed derivations in Supplementary Note 3). On the other hand, in near and above-threshold regimes of MOSFETs, large CQ, or electron charge screening effect, forces Vg–Vth, which is usually referred to as the overdrive voltage, to drop on the gate oxide, instead of in the channel, leading to a poor gate efficiency, or equivalently a large S, SMOSFET = STP·(1 + CQ/COX) ≫ STP (see detailed derivations in Supplementary Note 3). In this sense, overdrive voltage is a type of voltage loss. Interestingly, by adding a NC layer on MOSFETs, and simply matching |CNC| to the constant COX, CSCE, and CQ can be absorbed. In other words, SS in short-channel devices can be restored to 60 mV per decade, and S in the near and above-threshold regimes can be restored to transport mechanism limited STP, as illustrated in the schematics in Fig. 4a, b. The significance of the latter is that it provides an alternative solution to reduce the supply voltage and hence the switching energy, i.e., by saving overdrive voltage, which also occupies a big portion of the entire supply voltage, instead of struggling to save subthreshold voltage. This idea is supported by the numerical simulation results shown in Fig. 4c, d. Note that small NC non-linearity (proportional to the β coefficient that is discussed in detail in Supplementary Note 7) is desired to reduce S in near- and above-threshold regimes. Compared to matching |CNC| to the variable CMOS for sub-60 mV per decade SS, which is rather difficult to achieve and inevitably introduces variation issues, matching |CNC| to the constant COX is obviously much more practical in terms of saving switching energy. In several reported NC-FET experiments10,11,43,44, a common observation is that the use of the FE layer helps improve SS (instead of achieving steep slope, i.e., < 60 mV per decade), and enhance the ON-current, which very likely stems from the voltage loss saving role of NC uncovered in this paper.

Fig. 4. Role for NC in MOSFETs as a voltage-loss saver.

a With a simple |CNC| = COX matching, SS can be restored to 60 mV per decade in short-channel MOSFETs, and S in near- and above- threshold regimes can be reduced to the transport limit (STP). Here Ctrap and Cdep are neglected, since they have been greatly suppressed in state-of-the-art MOSFETs. Thereby, b NC layer can help suppress the short-channel effect induced subthreshold voltage loss (∆Vsub-Vth), and inversion charge screening induced overdrive voltage loss (∆Voverdrive). It is difficult for NC to help obtain hysteresis-free steep-slope turn-on characteristics. c Simulated Id–Vg and d S versus Id curve of a Si SOI NC-FET in which |CNC| is matched to COX. Lower NC non-linearity (quantified by the factor of β) is desired, in terms of restoring S back to STP.

Discussion

In summary, in a very simple and generic manner, our analysis not only unambiguously clarifies the intriguing physics that limits the capability of NC-FETs in achieving steep slope, thereby invalidating all the claimed “NC-FETs” in the literature, but also helps uncover the voltage loss saving capability of NC in modern X-FETs (where X = SOI/Fin/NW/2D/1D), provided the intrinsic limitation41,42 of ferroelectric polarization switching speed can be overcome, along with reliability issues arising from high electric-field in the DE and large interface trap density between the FE and DE. Our insightful analysis and findings provide invaluable guidance in terms of designing NC-FETs that could not only prevent further generation of scientifically misleading claims, but also prevent wasting millions of dollars of research and development expenditures and perhaps help identify a practical low-operation-voltage device that genuinely exploits NC.

Supplementary information

Acknowledgements

The research outlined in this article from the Nanoelectronics Research Lab at UCSB was supported by the ARO (grant W911NF1810366), JST CREST program (grant SB180064), and Intel Corporation.

Author contributions

W.C. and K.B. wrote the manuscript.

Competing interests

The authors declare no competing interests.

Footnotes

Peer review information Nature Communications thanks Chun-Hu Cheng and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. Peer reviewer reports are available.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary information is available for this paper at 10.1038/s41467-019-13797-9.

References

- 1.Lundstrom, M. S. The MOSFET revisited: device physics and modeling at the nanoscale. in IEEE Int. SOI Conf. Proceedings. 17–19 (2006).

- 2.Sakurai T. Perspectives of low-power VLSI’s. IEICE Trans. Electron. 2004;E87-C:429–436. [Google Scholar]

- 3.Sze, S. M. Physics of Semiconductor Devices. 3rd edn. p. 315 (Wiley Interscience, 2006).

- 4.Baba T. Proposal for surface tunnel transistors. Jpn. J. Appl. Phys. 1992;31:455–457. doi: 10.1143/JJAP.31.L455. [DOI] [Google Scholar]

- 5.Sarkar D, et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature. 2015;526:91–95. doi: 10.1038/nature15387. [DOI] [PubMed] [Google Scholar]

- 6.Gopalakrishnan K, Griffin P, Plummer J. Impact ionization MOS (I-MOS)-Part I: Device and circuit simulations. IEEE Tran. Elec. Dev. 2005;52:69–76. doi: 10.1109/TED.2004.841344. [DOI] [Google Scholar]

- 7.Salahuddin S, Datta S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 2008;8:405–410. doi: 10.1021/nl071804g. [DOI] [PubMed] [Google Scholar]

- 8.Rusu, A., Salvatore, G. A., Jimenez, D., & Ionescu, A. M. Metal-ferroelectric-meta-oxide-semiconductor field effect transistor with sub-60 mV/decade subthreshold swing and internal voltage amplification. IEEE Int. Elec. Dev. Meeting. 16.3.1–16.3.4 (2010).

- 9.Cheng CH, Chin A. Low-voltage steep turn-on pMOSFET using ferroelectric high-κ gate dielectric. IEEE Electron Device Lett. 2014;35:274–276. doi: 10.1109/LED.2013.2291560. [DOI] [Google Scholar]

- 10.Krivokapic, Z. et al. 14 nm ferroelectric FinFET technology with steep subthreshold slope for ultra low power applications. IEEE Int. Elec. Dev. Meeting. 357–360 (2017).

- 11.Saeidi A, et al. Negative capacitance as performance booster for tunnel FETs and MOSFETs: an experimental study. IEEE Electron Device Lett. 2017;38:1485–1488. doi: 10.1109/LED.2017.2734943. [DOI] [Google Scholar]

- 12.Si M, et al. Steep-slope hysteresis-free negative capacitance MoS2 transistors. Nat. Nano. 2018;13:24–28. doi: 10.1038/s41565-017-0010-1. [DOI] [PubMed] [Google Scholar]

- 13.Wang X, et al. Van der Waals negative capacitance transistors. Nat. Comm. 2019;10:1–8. doi: 10.1038/s41467-018-07882-8. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 14.McGuire F, et al. Sustained sub-60 mV/decade switching via the negative capacitance effect in MoS2 transistors. Nano Lett. 2017;17:4801–4806. doi: 10.1021/acs.nanolett.7b01584. [DOI] [PubMed] [Google Scholar]

- 15.Si M, et al. Steep-slope WSe2 negative capacitance field-effect transistor. Nano Lett. 2018;18:3682–3687. doi: 10.1021/acs.nanolett.8b00816. [DOI] [PubMed] [Google Scholar]

- 16.Böscke TS, Müller J, Bräuhaus D, Schröder U, Böttger U. Ferroelectricity in hafnium oxide thin films. Appl. Phys. Lett. 2011;99:102903. doi: 10.1063/1.3634052. [DOI] [Google Scholar]

- 17.Mueller S, et al. Incipient ferroelectricity in Al-doped HfO2 thin films. Adv. Funct. Mater. 2012;22:2412–2417. doi: 10.1002/adfm.201103119. [DOI] [Google Scholar]

- 18.Hoffmann M, Pesic M, Slesazeck S, Schroeder U, Mikolajick T. On the stabilization of ferroelectric negative capacitance in nanoscale devices. Nanoscale. 2018;10:10891–10899. doi: 10.1039/C8NR02752H. [DOI] [PubMed] [Google Scholar]

- 19.Hoffmann M, et al. Unveiling the double-well energy landscape in a ferroelectric layer. Nature. 2019;565:464–467. doi: 10.1038/s41586-018-0854-z. [DOI] [PubMed] [Google Scholar]

- 20.Yadav A, et al. Spatially resolved steady-state negative capacitance. Nature. 2019;565:468–471. doi: 10.1038/s41586-018-0855-y. [DOI] [PubMed] [Google Scholar]

- 21.Ota, H. et al. Fully coupled 3-D device simulation of negative capacitance FinFETs for sub 10 nm integration. IEEE Int. Elec. Dev. Meeting. 318–321 (2016).

- 22.You W, Su P. Design space exploration considering back-gate biasing effects for 2D negative-capacitance field-effect transistors. IEEE Trans. Electron Devices. 2017;64:3476–3481. doi: 10.1109/TED.2017.2714687. [DOI] [Google Scholar]

- 23.Khan, A. et al. Ferroelectric negative capacitance MOSFET: Capacitance tuning & antiferroelectric operation. IEEE Int. Elec. Dev. Meeting. 255–258 (2011).

- 24.Kobayashi M, et al. On device design for steep-slope negative-capacitance field-effect-transistor operating at sub-0.2V supply voltage with ferroelectric HfO2 thin film. AIP Adv. 2016;6:025113. doi: 10.1063/1.4942427. [DOI] [Google Scholar]

- 25.Rollo, T. et al. A simulation-based study of NC-FETs design: off-state versus on-state perspective. IEEE Int. Elec. Dev. Meeting. 213–216 (2018).

- 26.Pahwa G, et al. Analysis and compact modeling of negative capacitance transistor with high ON-current and negative output differential resistance-Part II: Model validation. IEEE Trans. Electron Devices. 2016;63:4986–4992. doi: 10.1109/TED.2016.2614436. [DOI] [Google Scholar]

- 27.Duarte, J. et al. Compact models of negative-capacitance FinFETs: lumped and distributed charge models. IEEE Int. Elec. Dev. Meeting. 754–757 (2016).

- 28.Pahwa G, et al. Numerical investigation of short-channel effects in negative capacitance MFIS and MFMIS transistors: subthreshold behavior. IEEE Trans. Electron Devices. 2018;65:5130–5136. doi: 10.1109/TED.2018.2870519. [DOI] [Google Scholar]

- 29.Tolédano, J. C. & Tolédano, P. The Landau Theory of Phase Transitions. (World Scientific, Singapore, 1987).

- 30.Miller SL, McWhorter PJ. Physics of the ferroelectric nonvolatile memory field effect transistor. J. Appl. Phys. 1992;72:5999–6010. doi: 10.1063/1.351910. [DOI] [Google Scholar]

- 31.Mistry, K. et al. A 2.0V, 0.35µm partially depleted SOI-CMOS Technology. IEEE Int. Elec. Dev. Meeting. 583–586 (1997).

- 32.Auth, C. et al. A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. IEEE VLSI Tech. Dig. 131–132 https://ieeexplore.ieee.org/document/6242496 (2012).

- 33.Appenzeller J, et al. Toward nanowire electronics. IEEE Trans. Electron Devices. 2008;55:2827–2845. doi: 10.1109/TED.2008.2008011. [DOI] [Google Scholar]

- 34.Cao W, et al. 2D semiconductor FETs- Projections and design for sub-10 nm VLSI. IEEE Trans. Electron Devices. 2015;62:3459–3469. doi: 10.1109/TED.2015.2443039. [DOI] [Google Scholar]

- 35.Ghosh R, et al. Germanane: a low effective mass and bandgap 2-D channel material for future FETs. IEEE Trans. Electron Devices. 2014;61:2309–2315. doi: 10.1109/TED.2014.2344914. [DOI] [Google Scholar]

- 36.Steffes J, et al. Thickness scaling of ferroelectricity in BiFeO3 by tomographic atomic force microscopy. PNAS. 2019;116:2413–2418. doi: 10.1073/pnas.1806074116. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 37.Saha A, Datta S, Gupta S. “Negative capacitance” in resistor-ferroelectric and ferroelectric-dielectric networks: Apparent or intrinsic? J. Appl. Phys. 2018;123:105102–1. doi: 10.1063/1.5016152. [DOI] [Google Scholar]

- 38.Wang, H. et al. New insights into the physical origin of negative capacitance and hysteresis in NCFETs. IEEE Int. Elec. Dev. Meeting. 31.1.1–31.1.4 (2018).

- 39.Li, X. & Toriumi, A. Direct relationship between sub-60 mV/dec subthreshold swing and internal potential instability in MOSFET externally connected to ferroelectric capacitor. IEEE Int. Elec. Dev. Meeting. 31.3.1–31.3.4 (2018).

- 40.Jin, C., Jang, K., Saraya, T., Hiramoto, T. & Kobayashi, M. Experimental study on the role of polarization switching in subthreshold characteristics of HfO2-based ferroelectric and anti-ferroelectric FET. IEEE Int. Elec. Dev. Meeting. 31.5.1–31.5.4 (2018).

- 41.Kobayashi, M., Ueyama, N., Jang, K. & Hiramoto, T. Experimental study on polarization-limited operation speed of negative capacitance FET with ferroelectric HfO2. IEEE Int. Elec. Dev. Meeting. 314–317 (2016).

- 42.Yuan Z, et al. Switching-speed limitations of ferroelectric negative-capacitance FETs. IEEE Trans. Electron Devices. 2016;63:4046–4052. doi: 10.1109/TED.2016.2602209. [DOI] [Google Scholar]

- 43.Kwon D, et al. Improved subthreshold swing and short channel effect in FDSOI n-channel negative capacitance field effect transistors. IEEE Electron Device Lett. 2018;39:300–303. doi: 10.1109/LED.2017.2787063. [DOI] [Google Scholar]

- 44.Zhang Z, et al. FinFET with improved subthreshold swing and drain current using 3-nm ferroelectric Hf0.5Zr0.5O2. IEEE Electron Device Lett. 2019;40:367–370. doi: 10.1109/LED.2019.2891364. [DOI] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.