Abstract

Since its invention in the 1960s, one of the most significant evolutions of metal-oxide-semiconductor field effect transistors (MOS-FETs) would be the three dimensionalized version that makes the semiconducting channel vertically wrapped by conformal gate electrodes, also recognized as FinFET. During the past decades, the width of fin (W) in FinFETs has shrunk from about 150 nm to a few nanometers. However, W seems to have been levelling off in recent years, owing to the limitation of lithography precision. Here, we show that by adapting a template-growth method, different types of mono-layered two-dimensional crystals are isolated in a vertical manner. Based on this, FinFETs with one atomic layer fin are obtained, with on/off ratios reaching . Our findings push the FinFET to the sub 1 nm fin-width limit, and may shed light on the next generation nanoelectronics for higher integration and lower power consumption.

Subject terms: Two-dimensional materials, Electronic devices

FinFETs are an evolution of metal-oxide-semiconductor field effect transistors (MOSFETs) featuring a semiconducting channel vertically wrapped by conformal gate electrodes. Here, the authors use a two-dimensional semiconductor to push the FinFET width to sub-nm whilst achieving a 107 ON/OFF ratio.

Introduction

Field effect transistors, which usually have the architecture of a conduction channel gated through an insulating layer, are known to be the core of modern semiconductor technologies1. As depicted by the famed Moore’s law, the number of transistors per unit area in an integrated circuit is expected to be exponentially increasing in a yearly time scale, which requires a continuous reduction of transistor size2. Nevertheless, when the channel width becomes at the order of sub-10 nm, performances of the conventional planar-structured FETs are often poisoned by the quantum confinement effects3. One way to mitigate this issue is to take advantage of the vertical dimension and fabricate fin-like conduction channel wrapped by oxides and gate electrodes, thus giving rise to a FinFET configuration with smaller device footprint, higher gate efficiency, and lower power consumption4.

To date, most of the FinFETs are fabricated by a top-down method, with the conducting fin etched from bulk plane5. However, this is forcibly limited by the precision of state-of-the-art lithography tools, while the narrowest line width of which can reach 6 nm6. Yet satisfaction cannot be met with the iterative progresses of semiconducting industry, as the further improvement of optical lithography technique is extremely difficult7.

Recently, efforts have been devoted to novel structure of FETs using low-dimensional materials as a platform. For example, two dimensional (2D) MoS planar FET with a single carbon nanotube (CNT) gate was demonstrated, pushing gate lengths of FETs to a sub-1 nm scale8. Similarly, CNT can serve as an ultra narrow conducting channel with graphene source and drain9. Few-layered semiconducting MoS10–14, as well as CNT films15–18, were also utilized to replace the conventional Si channel for developing novel FinFETs. 2D semiconductors are reported to be less pronged to short channel effects, but they however usually take similar space on chips as compared to those conventional Si-based technologies, making them far from satisfactory in terms of scaling19–21. The verticallization of monolayer (ML) 2D van der Waals (vdW) materials thus becomes a goal that has been long pursued, as it is not only a prototype that reaches the single atom limit of the Fin width in a FinFET structure, but also can keep the fin height as compared to the etched Si-fins and nanotubes (see Fig. 1a). So far, challenges still remain in terms of experimental realization of vertically free-standing 2D nano flakes.

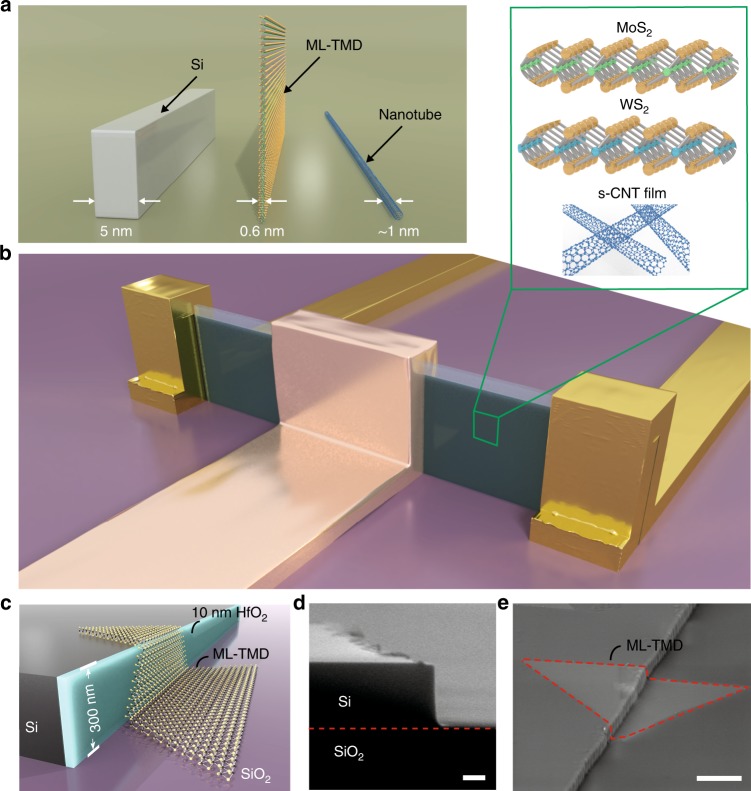

Fig. 1. The ML-FinFET with 0.6 nm.

a Demonstration of the ML-TMD fin as compared to etched Si-fin and nanotubes in their typical dimensions. b Schematic picture of the ML-FinFET presented in this work. Inset in b shows the several options for depositing the fin materials in this structure. c Schematic of a monolayer MoS crystal growing over a 300 nm height Si step, with the side wall coated by HfO. d Scanning electron micrograph (SEM) image of the as-fabricated 300 nm Si step. e SEM morphology of a typical monolayered MoS crystal growing over the 300 nm height step, while the dash red lines highlight the outline of the crystal. Scale bars in d, e are 100 nm and 1 µm, respectively.

In this work, we show that by designing a universal template-growth method, different types of ML 2D crystals are isolated in a vertical manner. Based on this bottom-up fabrication route, the vertical free-standing 2D MLs are further conformally coated with insulating dielectric and metallic gate electrodes, forming a 0.6 nm ML-FinFET structure (illustrated in Fig. 1b). A series of ML vdW materials and gate materials are demonstrated to show similar performances, with on/off ratios reaching around 10. Although, at this stage, these ML-FinFETs still struggle for relatively low-carrier mobilities, the realization of physical limit of in the FinFET structure opens up possibilities for future nanoelectronic applications.

Results

Template growth of 2D crystals on a 300-nm height Si step

In order to obtain vertically clamped 2D vdW materials with a considerable height as shown in Fig. 1b, we here devised a template growth method to allow deposition over a few-hundred nm step of materials such as transitional metal dichalcogenide (TMD), as shown in Fig. 1c. First, 300 nm step edge (Fig. 1d; Supplementary Fig. 1) was etched from a planar Si on insulator wafer (an optimization of the fabrication process to obtain a steep vertical step was performed, see Methods and Supplementary Figs. 2–4). Note that, as indicated in Fig. 1c, there is a 10 nm HfO coating on the side wall of the step edge, achieved via atomic layer deposition (ALD) and anisotropic dry etching (we call it a plane-removing process, see Supplementary Fig. 5). Tests were also carried out without the HfO coating on the side wall, which failed to yield the desired fin structure (more discussion can be found in Supplementary Fig. 6). This is to help to protect and support the TMD flakes in the consequential fabrication processes. A dedicated wet spray chemical vapor deposition (CVD) process was optimized (see Supplementary Figs. 7–11) to conformally grow ML 2D vdW crystals over the as prepared 300 nm step edges, which serve as vertical templates, as depicted in the schematic picture in Fig. 1e. It is found that this template growth can be a rather universal route to grow TMDs, such as MoS and WS on those sharp-edge templates, as well as to deposit other thin layer such as CNT-films (see Supplementary Figs. 12 and 13). More experimental details proving the ML-nature of those grown TMD flakes can be found in the Supplementary Figs. 14 and 15.

Before moving to the next steps of nano fabrications of FinFET, we tested the conventional in-plane FET made of the as-grown TMD crystals on SiO. Characteristic n-type field effect curves are seen in most of the in-plane MoS FET samples (more details in Supplementary Fig. 16). According to the aspect ratio in the MoS devices, such as illustrated in Fig. 2k, l, room temperature electron mobility was estimated to be at the order of 10 cm V s. WS planar FETs and s-CNT film FETs show similar performances, as shown in Supplementary Figs. 17 and 18. The relatively low mobilities of the planar FETs (Supplementary Figs. 16 and 17) made following this route may be caused by the existence of extra defective scattering centers, owing to the nature of the wet-spray growth. Further improvements are required in the future works. Nevertheless, this growth method provides a unique opportunity for the fabrication of ML-FinFET, as will be discussed in the following text.

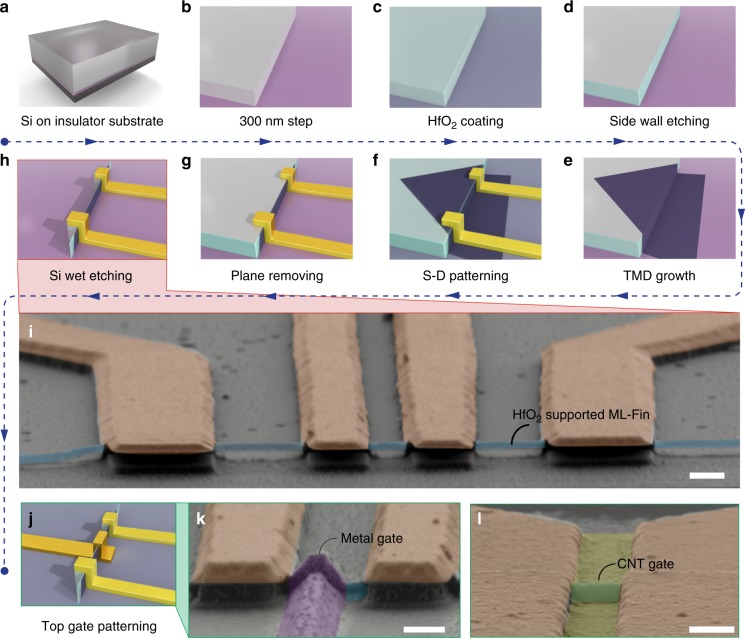

Fig. 2. Fabrication of ML-FinFETs.

a–h Schematic images of the detailed process for fabricating the ML-FinFETs, with the name of each step labeled below. i Zoomed-in false-colored SEM image of a typical vertically clamped ML MoS, corresponding to the h. j Gate electrodes deposited on the HfO-coated structure in h, finishing the whole process of ML-FinFET fabrication. k, l False-colored SEM images of the ML-FinFET with metal and CNT-film gates, respectively. Scale bars in i, k, l are 500, 500 and 200 nm, respectively.

The fabrication processes of ML-FinFETs

To describe in detail the feasibility of FinFET with ML fin, we demonstrate each fabrication step in a work flow, as shown in Fig. 2a–h. The preparation of 300 nm sharp edge with the side wall covered by 10 nm HfO are illustrated in Fig. 2a–d. Such 300 nm step edges were fabricated in an array, as shown in Supplementary Fig. 1b, in order to achieve batch fabrication. After the wet-spray of precursor and CVD growth, a certain coverage of ML TMDs can be obtained (Fig. 2e) for source–drain (S–D) electrodes deposition after a HfO coating (Fig. 2f). To obtain better contacts of electrodes, we have tested systematically the evaporation angle and thickness, as shown in Supplementary Figs. 19 and 20.

One of the most critical processes is the removal of planar part (defined as the plane-removing process) of the as-grown ML TMDs, which conformally cover the step edge. This is to retain only the 2D materials on the 300 nm side wall with an under layer of previously coated HfO, as shown in Fig. 2d, g and Supplementary Figs. 5 and 21. In the next step, a wet etch (Fig. 2h) was carried out to remove the 300 nm Si step, making the HfO/TMD/HfO sandwich structure vertically clamped by the S–D electrodes. A false-colored SEM image of the sketch shown in Fig. 2h is given in Fig. 2i, with the vertical blue belt (i.e., the HfO supported ML-fin of vertical TMD nanobelt, more details can be seen in Supplementary Figs. 21 and 22) clearly seen. Next, shown in Fig. 2j, a gate metallization procedure was done after an ALD coating of HfO gate dielectric on the basis of structure shown in Fig. 2h, i. Here, gate electrodes can be made by either metal deposition (see also Supplementary Fig. 23) or CNT-film deposition (see also Supplementary Fig. 24), as illustrated by the false-colored SEM images in Fig. 2k, l. It is noted that the ML-Fin can in principle consist of ML MoS, WS, and other thin films including CNT films, as indicated by the insets in Fig. 1b. Indeed, by replacing MoS with WS or CNT films, we found that the work flow in Fig. 2a–i a universal bottom-up route for fabricating FinFETs with sub 1 nm as its conduction channel.

Discussion

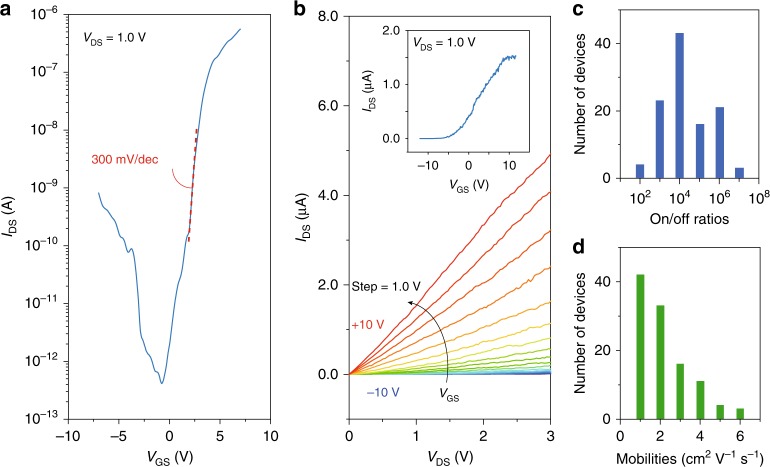

In the following text, we discuss the electrical transport of those prepared TMD ML-FinFETs. As shown in Fig. 3a, a typical field effect curve (measured from Sample-108) is shown with the best sub-threshold swing (SS) obtained to be 300 mV per decade. Meanwhile, characteristics of a typical ML-FinFET (measured from Sample-52) are shown in Fig. 3b. Rather linear curves can be seen, with its corresponding field effect curve plotted in the inset. Semiconducting CNT-film FinFET and WS ML-FinFETs are also fabricated using the same methods and tested to show similar electrical properties (Supplementary Figs. 24 and 26). Among the tested devices, on/off ratios of those ML-FinFETs are extracted to be in the range of 10–10, with the statistical distribution illustrated in Fig. 3c. Meanwhile, mobilities of those tested ML-FinFETs devices are extracted to be in the range of 1–6 cm V s, as shown in the statistics in Fig. 3d. Optimizing the material growth conditions to improve the intrinsic mobility of the material is our next plan.

Fig. 3. Electrical performances of the MoS ML-FinFETs.

a Field effect curves at 1.0 V source-drain voltage of MoS ML-FinFET. b curves at different gate voltages for the MoS ML-FinFET, the inset figure shows the field effect curve of the same device. c, d Statistics of on/off ratios and mobilities of MoS ML-FinFETs in this work.

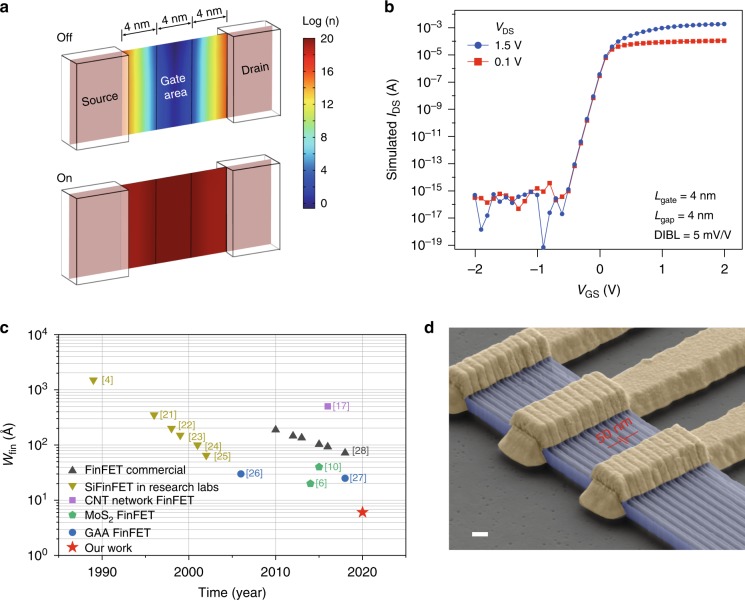

At this stage, electrical performances such as SS and mobility of the ML-FinFET can be further improved to meet the criteria for future application. Nevertheless, modelings of a ML-FinFET with 4nm gate length and 0.65 nm were carried out to address the performance of such ideal cases, using the finite element software COMSOL Multiphysics model (Methods). As shown in Fig. 4a, the model device was built with three parts, i.e., channel, source, and drain regions, where the gate area was separated with 2 nm dielectric layer of HfO. The simulated distribution of carrier density of OFF ( = −1 V) and ON ( = 1 V) states at = 0.1 V are shown in Fig. 4a, which correspond to the red dots at = −1 V and 1 V in Fig. 4b. A typical short channel parameter screening length is computed to be 0.26 nm (Methods). Meanwhile, the on/off ratio and drain-induced-barrier-lowering were estimated to be around and 5 mV/V, respectively. Figure 4a, b together with these short-channel-effect (SCE) parameters exhibit that, with simulations, a 4 nm gate length FinFET has performances overcoming the SCE with powerful gate controllability. Besides 4 nm gate length ML-FinFET, COMSOL simulations have been done to estimate the performance of variable gate length and dielectric layer thickness (Supplementary Figs. 27–29). Our simulations thus prove that the ML-FinFET can be of much improved performances. As shown in Fig. 4c we plot the iterative progresses of FinFETs as a function of time line. It is seen that, strikingly, the has been levelling off since 2 decades4,6,10,11,18,22–28. Our present work brings this nanostructure to a limit of 0.6 nm ML, an order of magnitude thinner than the of state-of-the-art FinFETs. Furthermore, we have also fabricated the TMD fin-array ML-FinFET as shown in Fig. 4d with different fin spacing (Supplementary Fig. 30), the minimum pitch between two fins reaches 50 nm in our experimental conditions (more data in Supplementary Fig. 31). The ML-Fin arrays can in principle be building blocks for future integrated circuits.

Fig. 4. Prospects of the ML-FinFETs.

a The simulated carrier statics of 4 nm gate length FinFET at off and on states, the color bar represents the carrier density in a log scale. b The simulated field effect curves of 4 nm gate length FinFET at = 0.1 and 1.5 V, respectively. c A time scale evolution of . Our current work, marked by the red solid star, brings the to the one atomic layer limit, which in principle cannot be shrunk any further. d False-colored SEM image of an ML-Fin array, with 50 nm pitch and 300 nm fin height. Scale bar in (d) is 300 nm.

In conclusion, we have developed a universal bottom-up method, with which ML-FinFET with a 0.6 nm fin width can be obtained. We tested different types of single layered two-dimensional crystals as the fins of the ML-FinFETs, and observed SS with 300 mV/dec and on/off ratios reaching 10 in them. Based on our COMSOL simulation results, potentially, ML-FinFET has a great advantage over the Si and Si/Ge GAA devices in overcoming the short channel effect. Computational modelings also suggest that using the ideal conditions, the performance of the TMD ML-FinFET can be further improved. It is known that has been levelling off at a few nanometers since almost 2 decades, owing to the limitation of lithography precision. Our present work pushes the of FinFET to the one atomic physical limit, which is one order of magnitude smaller than the state-of-art devices. It is believed to shed light on the development of next generation nanoelectronics for lower power consumption and higher integration.

Methods

Wet spray CVD technique

Preparation of precursor: 20.6 mg NaMoO (99, Aladdin) or 88.2 mg NaWO (98, Adamas) dissolved into 10 mL DI water to make precursor solution, respectively. Substrate rinsed by O plasma (CIF Tech Co., Ltd. CPC-C-40 kHz) to improve the hydrophilicity. The substrate first coated 0.01 M NaMoO/0.03 M NaWO solution was then placed into the center of the furnace. Crucible with 80 mg S powder (99.5, Sigma Aldrich) 10 cm upstream the heating center. Before heating, the tube was flushed with 300 sccm Ar for 10 min to keep an inert environment. Then the furnace was heated to 850 C in 45 min and was kept at this temperature for 40 min with 280 sccm Ar to realize a molten liquid precursor state. Finally, the reaction was finished within 2 min by introducing the sulfur powder into the heating zone for the growth of MoS. For the growth of WS, 270 sccm Ar and 30 sccm H mixture gases were introduced to convey the sulfur vapor and other growth conditions were same as that of MoS. After growth, the furnace was naturally cooled down to room temperature.

Semiconducting CNT and metallic CNT deposition

Semiconducting CNTs: the high-purity (99.9) semiconducting CNTs was mixed with toluene by a volume ratio of 1:15 and then ultrasonically treated for 10 min. Before the deposition process, a SOI substrate was preheated at 130 C for 20 min. Then, a ML of hexamethyldissilazane (MCC Primer) was spin-coated onto the substrate to improve the surface wettability. Subsequently, the substrate was immersed in the semiconducting CNT solution at 60 C for 3 h and then settled statically for 6 h at room temperature. Finally, the substrate was successively soaked in the toluene, acetone and isopropyl alcohol for 5 min, and heated at 150 C for 30 min. Metallic CNTs: the TUBALLTM SWCNTs used as gate electrodes were purchased from OCSiAl Inc. The dispersant 9-(1-octylonoyl)-9H-carbazole-2,7-diyl (PCz) were prepared by Suzuki polycondensation. The deposition process is the same with the semiconducting one.

Nano fabrications

SOI wafer with 300 nm device thickness is used as the substrate in our experiment. The SOI wafer is first patterned into different size arrays using photolithography (ABM/6/350/NUV/DCCD/M) process and ICP-RIE (Plasma Pro 100 Estrelas). After that, 10 nm HfO is deposited at 150 C using ALD (Savannah S100). RIE (RIE-10NR) is used to etch the planar part materials. The electrodes are fabricated with standard EBL process and evaporated with electron beam evaporation (ei-501z).

Electrical measurement setups

The fabricated devices were characterized using an optical microscope (Nikon LV100ND), SEM (FEI XL30 SFEG using an accelerating voltage of 10 kV) and AFM (Bruker Dimension Icon AFM). The electrical performance of the FinFETs was measured using a semiconductor analyzer (Agilent B1500A) and a probe station (Cascade Microtech Inc. 150-PK-PROMOTION) under ambient conditions.

Finite element simulation

The finite element simulation basing on the commercial software COMSOL Multiphysics29 was performed, where semiconductor module basing on Maxwells equation, Boltzmann transport theory together with Neumann boundary conditions were emplied30–32. Three-dimensional model of FinFET (Fig. 4a) was built with gate around the gate area by three sides, including the top and two side walls. The gap between gate and source/drain region was set to be 4 nm. Here, the source and drain regions were heavily doped ( = cm) to make them conducting, and the channel region (gated and gapped regions) was slightly N-doped with ( = cm (6.5 cm)) for model simulation converging. COMSOL simulation was performed at 300 K, and the material properties used in COMSOL simulation were shown in Supplementary Table 1. was set to be 0.65 nm as the thickness of ML MoS, and the gate length were simulated at 200, 100, 50, and 4 nm, respectively. The Shockley–Read–Hall was used to simulate the trapping assisted recombination33. Dielectric layer HfO thickness is set to be 2 and 20 nm. The source and drain contacting are set to be ohmic. Screening length was calculated34 using

| 1 |

where the represents the relative dielectric constant, and is the thickness.

Supplementary information

Acknowledgements

This work is supported by the National Key R&D Program of China (2019YFA0307800, 2017YFA0206302, and 2016YFB0401104) and the National Natural Science Foundation of China (NSFC) with Grants 11974357, U1932151, and 51627801. D.-M. Sun acknowledges the Strategic Priority Research Program of Chinese Academy of Sciences (Grant No. XDB30000000), Key Research Program of Frontier Sciences CAS Grant No. ZDBS-LY-JSC027, and supports from NSFC with Grants 51272256, 61422406, and 61574143. S. Liu acknowledges supports from NSFC (21705036 and 21975067) and Natural Science Foundation of Hunan Province, China (2018JJ3035). S. Qiu acknowledges the Guangdong Project of R&D Plan in Key Areas, 2019B010934001. Z. Han acknowledges the support from the Program of State Key Laboratory of Quantum Optics and Quantum Optics Devices (No. KF201816).

Author contributions

Z.H., D.S., and T.A. conceived the experiment and supervised the overall project. M.C., X.S., and Q.Z. fabricated the devices, and M.C. carried out electrical transport measurements. H.L. and S.L. performed the growth of 2D crystals. M.C., Z.H., and D.S. analyzed the data. H.W. contributed to the 3D schematic pictures. Y.S. carried out ALD depositions. S.W. and H.D. carried out TEM characterizations; B.D. and J.Z. conducted the computational simulations and discussions. S.Q. provided CNT samples. The paper was written by Z.H. with discussion and inputs from all authors.

Data availability

The data that support the findings of this study are available at Zenodo (2020), 10.5281/zenodo.3672715.

Competing interests

The authors declare no competing interests.

Footnotes

Peer review information Nature Communications thanks the anonymous reviewer(s) for their contribution to the peer review of this work.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

These authors contribute equally: Mao-Lin Chen, Xingdan Sun, Hang Liu.

Contributor Information

Baojuan Dong, Email: dongbaojuan.1989@gmail.com.

Song Liu, Email: liusong@hnu.edu.cn.

Dong-Ming Sun, Email: dmsun@imr.ac.cn.

Zheng Han, Email: vitto.han@gmail.com.

Supplementary information

Supplementary information is available for this paper at 10.1038/s41467-020-15096-0.

References

- 1.Edgar, L. J. Method and apparatus for controlling electric currents, US Patent 1,745,175 (1930).

- 2.Moore GE, et al. Cramming More Components onto Integrated Circuits. New York, NY, USA: McGraw-Hill; 1965. [Google Scholar]

- 3.Takagahara T, Takeda K. Theory of the quantum confinement effect on excitons in quantum dots of indirect-gap materials. Phys. Rev. B. 1992;46:15578–15581. doi: 10.1103/PhysRevB.46.15578. [DOI] [PubMed] [Google Scholar]

- 4.Hisamoto, D., Kaga, T., Kawamoto, Y. & Takeda, E. A fully depleted lean-channel transistor (delta)—a novel vertical ultra thin SOI MOSFET. In: Proc. International Technical Digest on Electron Devices Meeting, 833–836 (1989).

- 5.Jan, C. H. et al. A 22 nm SoC platform technology featuring 3-D tri-gate and high-k/metal gate, optimized for ultra low power, high performance and high density SoC applications. In: Proc. 2012 International Electron Devices Meeting, 3.1.1–3.1.4 (2012).

- 6.Choi Y, King T, Hu C. Spacer FinFET: nanoscale double-gate CMOS technology for the terabit era. Solid State Electron. 2002;46:1595–1601. doi: 10.1016/S0038-1101(02)00111-9. [DOI] [Google Scholar]

- 7.Ito T, Okazaki S. Pushing the limits of lithography. Nature. 2000;406:1027–1031. doi: 10.1038/35023233. [DOI] [PubMed] [Google Scholar]

- 8.Desai SB, et al. MoS transistors with 1-nanometer gate lengths. Science. 2016;354:99–102. doi: 10.1126/science.aah4698. [DOI] [PubMed] [Google Scholar]

- 9.Qiu C, et al. Scaling carbon nanotube complementary transistors to 5-nm gate lengths. Science. 2017;355:271–276. doi: 10.1126/science.aaj1628. [DOI] [PubMed] [Google Scholar]

- 10.Chen, M. et al. TMD FinFET with 4 nm thin body and back gate control for future low power technology. In: Proc. 2015 IEEE International Electron Devices Meeting (IEDM), 32.2.1–32.2.4 (2015).

- 11.Chen, M.-C. et al. Hybrid Si/TMD 2D electronic double channels fabricated using solid CVD few-layer-mos stacking for V matching and CMOS-compatible 3DFETs. In: Proc. 2014 IEEE International Electron Devices Meeting, 33–5 (IEEE, 2014).

- 12.Lee Y, et al. Ge GAA FETs and TMD FinFETs for the applications beyond SiA review. IEEE J. Electron Devices Soc. 2016;4:286–293. doi: 10.1109/JEDS.2016.2590580. [DOI] [Google Scholar]

- 13.Zhang, M., Chien, P.-Y. & Woo, J. C. Comparative simulation study on MoS FET and FinFET. In: Proc. TENCON 2015-2015 IEEE Region 10 Conference, 1–2 (IEEE, 2015).

- 14.Lan Y-W, et al. Scalable fabrication of a complementary logic inverter based on MoS fin-shaped field effect transistors. Nanoscale Horiz. 2019;4:683–688. doi: 10.1039/C8NH00419F. [DOI] [Google Scholar]

- 15.Shi J, Guo CX, Chan-Park MB, Li CM. All-printed carbon nanotube finFETs on plastic substrates for high-performance flexible electronics. Adv. Mater. 2012;24:358–361. doi: 10.1002/adma.201103674. [DOI] [PubMed] [Google Scholar]

- 16.Li J, et al. Vertically aligned carbon nanotube field-effect transistors. Carbon. 2012;50:4628–4632. doi: 10.1016/j.carbon.2012.05.049. [DOI] [Google Scholar]

- 17.Zhang P, et al. Performance projections for ballistic carbon nanotube FinFET at circuit level. Nano Res. 2016;9:1785–1794. doi: 10.1007/s12274-016-1071-4. [DOI] [Google Scholar]

- 18.Lee D, et al. Three-dimensional fin-structured semiconducting carbon nanotube network transistor. ACS Nano. 2016;10:10894–10900. doi: 10.1021/acsnano.6b05429. [DOI] [PubMed] [Google Scholar]

- 19.Mak KF, Lee C, Hone J, Shan J, Heinz TF. Atomically thin MoS: a new direct-gap semiconductor. Phys. Rev. Lett. 2010;105:136805. doi: 10.1103/PhysRevLett.105.136805. [DOI] [PubMed] [Google Scholar]

- 20.Radisavljevic B, Radenovic A, Brivio J, Giacometti V, Kis A. Single-layer MoS transistors. Nat. Nanotechnol. 2011;6:147. doi: 10.1038/nnano.2010.279. [DOI] [PubMed] [Google Scholar]

- 21.Zhang Y, et al. Controlled growth of high-quality monolayer WS layers on sapphire and imaging its grain boundary. ACS Nano. 2013;7:8963–8971. doi: 10.1021/nn403454e. [DOI] [PubMed] [Google Scholar]

- 22.Leobandung, E. & Chou, S. Y. Reduction of short channel effects in SOI MOSFETs with 35 nm channel width and 70 nm channel length. In: Proc. 1996 54th Annual Device Research Conference Digest, 110–111 (1996).

- 23.Hisamoto, D. et al. A folded-channel MOSFET for deep-sub-tenth micron era. International Electron Devices Meeting. Technical Digest (Cat. No.98CH36217) 38, 1032–1034 (1998).

- 24.Huang, X. et al. Sub 50-nm FinFET: PMOS. In: Proc. International Electron Devices Meeting 1999. Technical Digest (Cat. No.99CH36318), 67–70 (1999).

- 25.Choi, Y.-K. et al. Sub-20 nm CMOS FinFET technologies. In: Proc. International Electron Devices Meeting. Technical Digest (Cat. No.01CH37224), 19.1.1–19.1.4 (2001).

- 26.Lee, H. et al. Sub-5 nm all-around gate FinFET for ultimate scaling. In: Proc. 2006 Symposium on VLSI Technology, 2006. Digest of Technical Papers. 58–59 (2006).

- 27.Lu, W. et al. First Transistor Demonstration of Thermal Atomic Layer Etching: InGaAs FinFETs with sub-5 nm Fin-width Featuring in situ ALE-ALD. 895–898 (2018).

- 28.Seo, K.-I. et al. A 10 nm platform technology for low power and high performance application featuring FINFET devices with multi workfunction gate stack on bulk and SOI. In: Proc. 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, 1–2 (IEEE, 2014).

- 29.Miyaguchi, K. et al. Modeling FinFET metal gate stack resistance for 14 nm node and beyond. In: Proc. 2015 International Conference on IC Design Technology (ICICDT), 1–4 (2015).

- 30.Maxwell, J. C. A dynamical theory of the electromagnetic field. Philos. Trans. R. Soc.155, 459–512 (1865).

- 31.Lerner, R. G. & Trigg, G. L. Encyclopedia of Physics (VCH, 1991).

- 32.Cheng AH-D, Cheng DT. Heritage and early history of the boundary element method. Eng. Anal. Bound. Elem. 2005;29:268–302. doi: 10.1016/j.enganabound.2004.12.001. [DOI] [Google Scholar]

- 33.Shockley W, Read WT. Statistics of the recombinations of holes and electrons. Phys. Rev. 1952;87:835–842. doi: 10.1103/PhysRev.87.835. [DOI] [Google Scholar]

- 34.Pierre CJ. FinFETs and Other Multi-Gate Transistors. New York: Springer; 2008. [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Supplementary Materials

Data Availability Statement

The data that support the findings of this study are available at Zenodo (2020), 10.5281/zenodo.3672715.