Abstract

We report the performance improvement of low-temperature coplanar indium–gallium–zinc–oxide (IGZO) thin-film transistors (TFTs) with a maximum process temperature of 230 °C. We treated F plasma on the surface of an SiO2 buffer layer before depositing the IGZO semiconductor by reactive sputtering. The field-effect mobility increases from 3.8 to 9.0 cm2 V−1·s−1, and the threshold voltage shift (ΔVth) under positive-bias temperature stress decreases from 3.2 to 0.2 V by F-plasma exposure. High-resolution transmission electron microscopy and atom probe tomography analysis reveal that indium fluoride (In-F) nanoparticles are formed at the IGZO/buffer layer interface. This increases the density of the IGZO and improves the TFT performance as well as its bias stability. The results can be applied to the manufacturing of low-temperature coplanar oxide TFTs for oxide electronics, including information displays.

Keywords: low-temperature coplanar IGZO TFT, bias stability, In-F nanoparticles

1. Introduction

Indium–gallium–zinc–oxide (IGZO) thin-film transistors (TFTs) are widely used as a TFT backplane for active-matrix liquid-crystal displays (AMLCDs) and active-matrix organic light-emitting diode (AMOLED) displays due to their higher mobility and smaller subthreshold swing compared to amorphous silicon (a-Si) TFTs [1,2,3,4]. To realize the future of displays with flexible and transparent functions, transparent polyimide (PI) and poly(ethersulfone) (PES) could be used, and a low-temperature process (~230 °C) is required. The advantage of oxide TFTs is that they require a low-temperature process, but a relatively high-temperature process at about 350 °C is being used for the mass production of displays. This is mainly due to the improvement of the mobility and bias stability of oxide TFTs [5,6]. It is noted that the quality of SiO2 depends on its substrate process temperature; the density and leakage through SiO2 and electrical breakdown voltage could be improved by increasing the deposition temperature of SiO2. The buffer SiO2 of coplanar structures and the gate dielectric SiO2 of back-channel-etch (BCE) structures are usually deposited at 300 to 400 °C by plasma-enhanced chemical vapor deposition (PECVD) for display applications [7,8]. The coplanar structure of IGZO TFTs has the advantage of negligible overlap capacitance between the gate and source/drain electrodes, and thus, the RC (resistance–capacitance product) delay can be remarkably reduced for display applications [5,6,7] [9,10,11]. In addition, the coplanar oxide TFT is a strong candidate for low-temperature devices because it could not use high-temperature SiO2 as a gate insulator (GI) because of the damage this would cause to IGZO during GI deposition [12]. In order words, coplanar oxide TFTs with only a high-temperature buffer layer have good performance to be used in AMOLED televisions [13,14], and the coplanar oxide TFTs with a low-temperature buffer layer could be widely used as low-temperature TFTs, if the TFTs improve their performance. Note that low-temperature coplanar IGZO TFTs suffer from lower mobility and higher threshold voltage shift (ΔVth) under positive-bias temperature stress (PBTS), and improving PBTS stability is important for the development of stable IGZO TFTs for AMOLED displays, given that driving TFTs in the OLED pixel are positively biased, and even a small change in the Vth can deteriorate image quality [15,16].

In this work, we studied the effect of F-plasma treatment on low-temperature SiO2 to improve the performance and bias stability, PBTS, of the low-temperature coplanar IGZO TFT. The physical damage by ion bombardment on the SiO2 buffer layer during the sputter deposition of IGZO might be one of the main reasons for the generation of trap sites in low-temperature SiO2 [17]. To reduce the trap sites generated during the sputtering process, we performed F-plasma treatment on the SiO2 buffer because F is known to passivate traps in SiO2 as well as in IGZO [18,19,20,21,22]. Methods such as dynamic secondary-ion mass spectroscopy (D-SIMS), high-resolution transmission electron microscopy (HR-TEM) and APT (atom probe tomography) were used to investigate the relationships between the process temperature of the buffer layer, the performance of the TFTs and the effect of plasma treatment on the buffer layer.

2. Materials and Methods

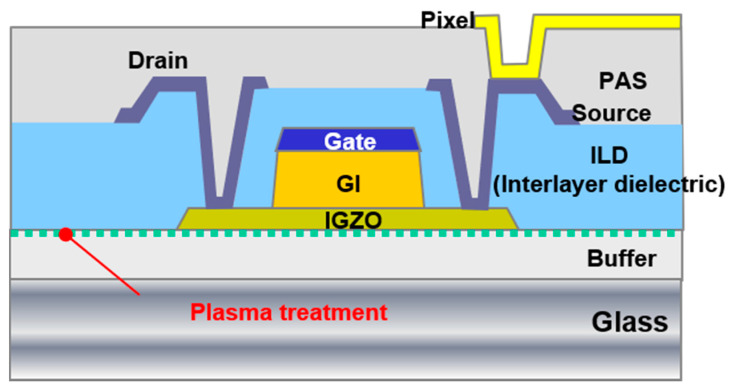

The cross-sectional view of the coplanar IGZO TFT studied in this work is shown in Figure 1. First, a 200-nm-thick SiO2 was deposited as buffer layer at 230 or 350 °C by PECVD (Applied Materials, Santa Clara, CA, USA). The F-plasma treatment (500 W, 100 mTorr, 60 s) was carried out in a reactive ion etching (RIE) chamber before depositing the IGZO. Device I is the control sample with a high-temperature buffer layer processed at 350 °C. Device II is another control sample with a low-temperature SiO2 buffer layer processed at 230 °C. Device III is for checking the effect of F-plasma treatment on the buffer layer processed at 230 °C. A 30-nm IGZO (In: Ga: Zn = 1: 1: 1 at%) active layer (JX NIPPON MINING & METALS KOREA Co., Ltd, Pyeongtaek, Korea) was deposited by direct current sputtering at room temperature. Then, a 200-nm-thick SiO2 layer was deposited by PECVD at 230 °C as the gate insulator (GI). The subsequent thermal annealing was performed at 230 °C for 1 h in air and followed by the sequential deposition of a 300-nm-thick Mo layer as the gate metal. The Mo and GI layers were patterned continuously by photolithography. He-plasma treatment was applied to make n+ ohmic contacts with source/drain electrodes as previously reported [21,23]. A 400-nm-thick SiO2 was deposited by PECVD at 230 °C to form the interlayer dielectric (ILD). Contact holes were formed by dry etching, after which a 300-nm-thick Mo layer was sputtered and then patterned by wet etching to form the source/drain electrode. A 200-nm-thick SiO2 layer was deposited at 230 °C as a passivation layer by PECVD and then patterned. Finally, an indium tin oxide (ITO) was deposited and wet etched to form the pixel electrodes.

Figure 1.

Cross-sectional view of the coplanar indium–gallium–zinc–oxide (IGZO) thin-film transistor (TFT) studied in this work.

3. Results and Discussions

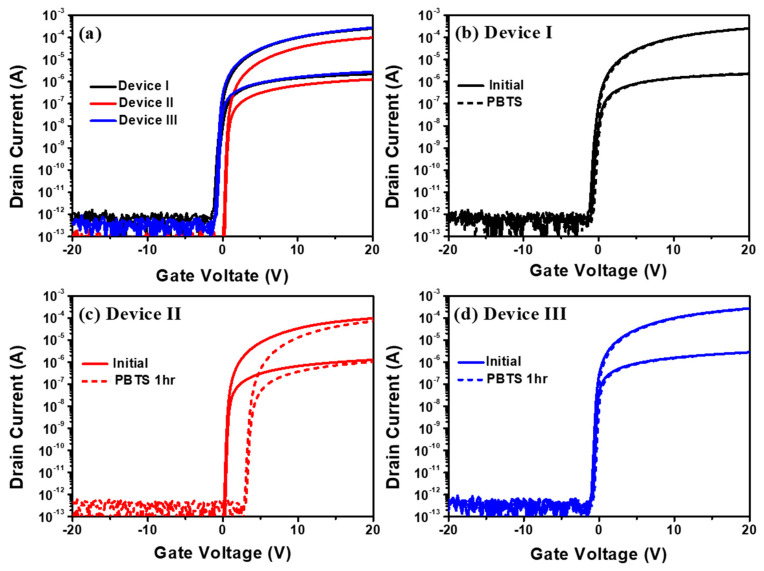

Figure 2a shows the transfer characteristics of the devices before stress. Figure 2b–d shows the transfer characteristics of devices I, II and III before and after 1 h of PBTS, applying a constant gate voltage (VGS) of +30 V at 60 °C for 1 h in a dark box. The channel width and length of the devices are 100 and 10 μm, respectively. Table 1 lists the device parameters, such as threshold voltage (Vth), field-effect mobility (µFE), subthreshold swing (SS) and Vth shift (ΔVth) under PBTS for the three devices. Vth is the VGS giving the drain current (ID) = W/L × 10 nA at the drain voltage (VDS) = 10 V. µFE is obtained at VGS–Vth = 10 V and VDS = 10 V. The SS is taken from the minimum value of ΔVGS/Δlog(IDS) with VDS = 10 V. Devices I and II are fabricated with the same process conditions, except for the process temperature of the buffer layer. However, the mobility increases by 2.4 times and the Vth shift decreases from 3 to 0.2 V by using a high-temperature buffer layer. For device III, the initial Vth, SS, µFE and ΔVth are found to be −0.2 V, 139 mV/dec, 9 cm2 V−1·s−1 and 0.2 V, respectively. The results show that the performance of device III is similar to that of device I, and that plasma treatment plays a critical role to improve performance.

Figure 2.

(a) Transfer curves of the TFTs I, II and III (W/L = 100/10 μm) before bias stress. The transfer curves were measured before and after 1 h of PBTS (dash line) at VDS = 0.1 and 10 V for (b) device I, (c) device II and (d) device III, respectively.

Table 1.

Summary of the device parameters and bias stability for the three TFTs. The threshold voltage shift (ΔVth) was measured after 1 h PBTS.

| Vth (V) | µFE (cm2/V·s) | SS (mV/dec) | ΔVth (V) | |

|---|---|---|---|---|

| Device I | 0.0 | 9.2 | 181 | 0.2 |

| Device II | 1.1 | 3.8 | 109 | 3.2 |

| Device III | −0.2 | 9.0 | 139 | 0.2 |

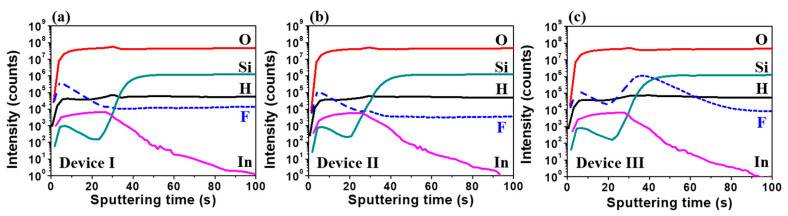

Figure 3a–c shows the D-SIMS profiles of H, O, F, Si and In for devices I, II and III, respectively. The significant increase of F intensity was found for device III. This result shows that F is incorporated into the IGZO/SiO2 interlayer. The presence of F in the top region of the active layer of the TFT appears to be due to the contamination from the chamber wall because NF3 plasma is used to etch the deposited layers to clean the PECVD chambers.

Figure 3.

The dynamic secondary-ion mass spectroscopy (D-SIMS) profiles of H, O, F, Si and In for devices (a) I, (b) II and (c) III, respectively.

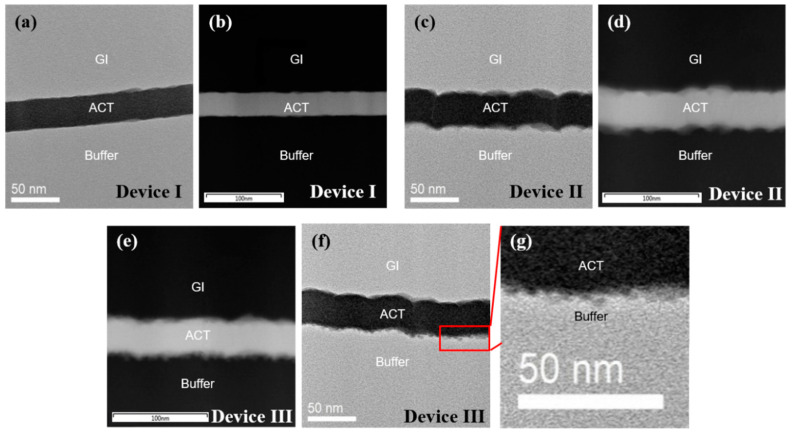

Figure 4 shows the cross-sectional HR-TEM images and annular dark-field (ADF) images in a scanning TEM (STEM) of the GI (SiO2)/IGZO/buffer (SiO2) interfaces. Figure 4a shows that device I has smooth surface roughness at the top and bottom regions of the active layer. This relates to a buffer layer fabricated through a high-temperature process. On the other hand, device II has poor roughness (~8 nm RMS roughness) at the bottom of the active layer, caused by the low-temperature buffer layer. Therefore, the top IGZO surface has poor surface morphology (Figure 4c). The results show the roughness of the GI/IGZO is affected by the deposition temperature of the buffer layer. Device III also has poor roughness (Figure 4f), but nanoparticles are found at the IGZO/Buffer (SiO2) interface. To identify nanoparticles, the annular dark-field (ADF) images in a scanning TEM (STEM) of the devices were analyzed and the interface of device III was enlarged. Figure 4b,d,e shows ADF images for each device. ADF imaging is a method of mapping samples in a STEM. These images are formed by collecting scattered electrons with an annular dark-field detector [24]. Note that the sizes of scale bar in Figure 4d,e are larger than in Figure 4b for the identification of the nanoparticles. The nanoparticles, of around 1 nm in diameter, are identified by Figure 4e and the enlarged view of Figure 4g. The SiO2 roughness affects the performance of the devices. In addition, the nanoparticles produced by plasma treatment seem to improve the mobility and Vth shift by PBTS.

Figure 4.

High-resolution TEM (HR-TEM) images of the gate insulator (GI) (SiO2)/active (IGZO)/buffer (SiO2) interfaces for devices (a) I, (c) II and (f) III, respectively. Annular dark-field (ADF) images in a scanning TEM (STEM) for devices (b) I, (d) II and (e) III, respectively. (g) Enlarged interface of device III.

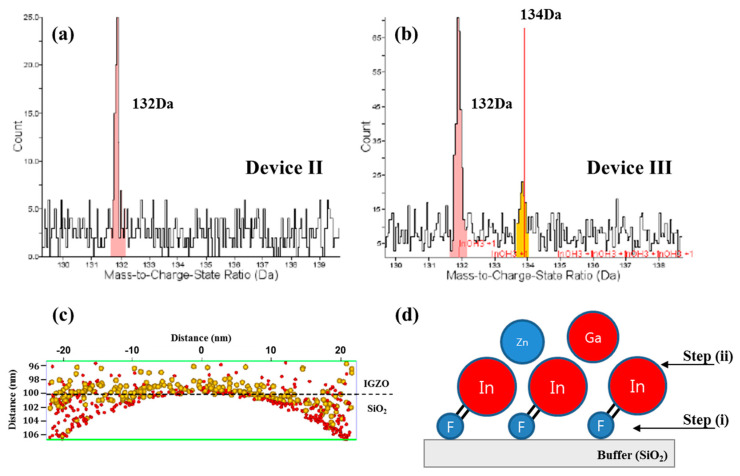

We measured the mass spectra and atomic map by atom probe tomography, APT (CAMECA, LEAP5000). APT supports the material analysis, offering extensive capabilities for both 3D imaging and chemical composition measurements at the atomic scale (around 0.1–0.3 nm resolution in depth and 0.3–0.5 nm laterally) [25]. The IGZO (100 nm)/SiO2 (200 nm) layers, deposited with the same process conditions used for fabricating devices II and III, were used for APT measurement. Note that the 100-nm IGZO layer was used to prevent contamination during APT measurement. Figure 5a,b shows the mass spectra for the IGZO/buffer (SiO2) interfaces of devices II and III. A 132 Da (Dalton) peak is found for the samples, which may be related with Si3O3 because of the atomic mass (Si: 28 Da, O: 16 Da). The peak of 134 Da is observed, which is estimated to be InF (In: 115 Da, F: 19 Da). As shown in the atomic map (Figure 5c), the InF nanoparticles of about 1 nm in diameter are formed on the top of Si3O3. Figure 5d shows the generation model of InF nanoparticles with the F atoms introduced by plasma treatment on the buffer layer. The InF nanoparticles could be generated during the IGZO sputtering process because In has the highest electron affinity and the largest reactivity with F. For example, the electron affinity of In is 37.043 kJ/mol, Ga is 29.061 kJ/mol and Zn is −58 kJ/mol. It is reported that F-plasma treatment on IGZO improves the TFT performance by passivating electron traps in IGZO. We found in this work that F-plasma treatment on the buffer layer formed InF nanoparticles at the IGZO/SiO2 interfaces. The nanoparticles increase the density of the active layer in spite of having poor roughness. The increased density of the IGZO can improve the mobility and Vth shift by PBTS (Figure 2). As a result, device III has excellent TFT performance even at the low-temperature buffer-layer deposition.

Figure 5.

Mass spectra at the IGZO/buffer (SiO2) interface for (a) device II and (b) device III. (c) Atomic map for device III (132 Da: red, 134 Da: yellow) analyzed with APT (atom probe tomography). (d) InF nanoparticle generation model. The InF formation can be seen in (d); step (i) is F bonding on SiO2 and step (ii) is the formation of InF nanoparticles during the IGZO sputtering process.

4. Conclusions

We report the significant improvement of a low-temperature coplanar IGZO device by plasma exposure on an SiO2 buffer layer. The low-temperature IGZO TFT (device III) has similar performance and Vth shift for PBTS to those of IGZO TFT with the buffer layer fabricated at 350 °C, by introducing F plasma on the buffer layer (230 °C). By TEM and APT analyses, it is found that In-F nanoparticles of about 1 nm in diameter are formed at the IGZO/buffer interface. Therefore, F-plasma treatment on an SiO2 buffer layer can be a suitable method to make low-temperature coplanar IGZO TFTs.

Author Contributions

Conceptualization, H.-y.J. and J.J.; methodology, S.-h.N., K.-s.P. and S.-y.Y.; formal analysis, H.-y.J.; writing—original draft preparation, H.-y.J. and C.P.; writing—review and editing, H.-y.J.; supervision, J.J. All authors have read and agreed to the published version of the manuscript.

Funding

This work was supported by the Technology Innovation Program (or Industrial Strategic Technology Development Program (20010082, Development of low temperature patterning and heat treatment technology for light and thermal stability in soluble oxide TFT manufacturing)) funded by the Ministry of Trade, Industry & Energy (MI, Korea).

Conflicts of Interest

The authors declare no conflicts of interest.

References

- 1.Nomura K., Ohta H., Takagi A., Kamiya T., Hirano M., Hosono H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature. 2004;432:488–492. doi: 10.1038/nature03090. [DOI] [PubMed] [Google Scholar]

- 2.Yabuta H., Sano M., Abe K., Aiba T., Den T., Kumomi H., Nomura K., Kamiya T., Hosono H. High-mobility thin-film transistor with amorphous InGaZnO4 channel fabricated by room temperature rf-magnetron sputtering. Appl. Phys. Lett. 2006;89:112123. doi: 10.1063/1.2353811. [DOI] [Google Scholar]

- 3.Kamiya T., Nomura K., Hosono H. Present status of amorphous In–Ga–Zn–O thin-film transistors. Sci. Technol. Adv. Mater. 2010;11:044305. doi: 10.1088/1468-6996/11/4/044305. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 4.Mativenga M., Choi M.H., Choi J.W., Jang J. Transparent Flexible Circuits Based on Amorphous-Indium–Gallium–Zinc–Oxide Thin-Film Transistors. IEEE Electron Device Lett. 2011;32:170–172. doi: 10.1109/LED.2010.2093504. [DOI] [Google Scholar]

- 5.Wu C.W., Yoo S.Y., Ning C., Yang W., Shang G.L., Wang K., Liu C.H., Liu X., Yuan G.C., Chen J., et al. Improvement of Stability on a-IGZO LCD. SID Symp. Dig. Tech. Pap. 2013;44:97–99. doi: 10.1002/j.2168-0159.2013.tb06150.x. [DOI] [Google Scholar]

- 6.Oh S., Baeck J.H., Lee D., Park T., Shin H.S., Bae J.U., Park K.S., Kang I.B. Improvement of PBTS Stability in Self-Aligned Coplanar a-IGZO TFTs. SID Symp. Dig. Tech. Pap. 2015;46:1143–1146. doi: 10.1002/sdtp.10032. [DOI] [Google Scholar]

- 7.Nag M., Roose F.D., Myny K., Steudel S., Genoe J., Groeseneken G., Heremans P. Characteristics improvement of top-gate self-aligned amorphous indium gallium zinc oxide thin-film transistors using a dual-gate control. J. Soc. Inf. Disp. 2017;25:349–355. doi: 10.1002/jsid.558. [DOI] [Google Scholar]

- 8.Rahaman A., Chen Y., Hasan M.M., Jang J. A High Performance Operational Amplifier Using Coplanar Dual Gate a-IGZO TFTs. IEEE J. Electron Devices Soc. 2019;7:655–661. doi: 10.1109/JEDS.2019.2923208. [DOI] [Google Scholar]

- 9.Kang D.H., Kang I., Ryu S.H., Jang J. Self-Aligned Coplanar a-IGZO TFTs and Application to High Circuits. IEEE Electron Device Lett. 2011;32:1385–1387. doi: 10.1109/LED.2011.2161568. [DOI] [Google Scholar]

- 10.Wu C.H., Hsieh H.H., Chien C.W., Wu C.C. Self-Aligned Top-Gate Coplanar In-Ga-Zn-O Thin-Film Transistors. J. Disp. Technol. 2009;5:515–519. doi: 10.1109/JDT.2009.2026189. [DOI] [Google Scholar]

- 11.Geng D., Kang D.H., Seok M.J., Mativenga M., Jang J. High-Speed and Low-Voltage-Driven Shift Register with Self-Aligned Coplanar a-IGZO TFTs. IEEE Electron Device Lett. 2012;33:1012–1014. doi: 10.1109/LED.2012.2194133. [DOI] [Google Scholar]

- 12.Choi S., Han M. Effect of Deposition Temperature of SiOx Passivation Layer on the Electrical Performance of a-IGZO TFTs. IEEE Electron Device Lett. 2012;33:396–398. doi: 10.1109/LED.2011.2181320. [DOI] [Google Scholar]

- 13.Ha C., Lee H.J., Kwon J.W., Seok S.Y., Ryoo C.I., Yun K.Y., Kim B.C., Shin W.S., Cha S.Y. High Reliable a-IGZO TFTs with Self-Aligned Coplanar Structure for Large-Sized Ultrahigh-Definition OLED TV. SID Symp. Dig. Tech. Pap. 2015;46:1020–1022. doi: 10.1002/sdtp.10346. [DOI] [Google Scholar]

- 14.Shin H.J., Takasugi S., Park K.M., Choi S.H., Jeong Y.S., Song B.C., Kim H.S., Oh C.H., Ahn B.C. Novel OLED Display Technologies for Large-Size UHD OLED TVs. SID Symp. Dig. Tech. Pap. 2015;46:53–56. doi: 10.1002/sdtp.10225. [DOI] [Google Scholar]

- 15.Yoon J.S., Hong S.J., Kim J.H., Kim D.H., Ryosuke T., Nam W.J., Song B.C., Kim J.M., Kim P.Y., Park K.H., et al. 55-inch OLED TV using Optimal Driving Method for Large-Size Panel based on InGaZnO TFTs. SID Symp. Dig. Tech. Pap. 2014;58:849–852. doi: 10.1002/j.2168-0159.2014.tb00224.x. [DOI] [Google Scholar]

- 16.Arai T. The Advantages of the Self-Aligned Top Gate Oxide TFT Technology for AM-OLED Displays. SID Symp. Dig. Tech. Pap. 2015;46:1016–1019. doi: 10.1002/sdtp.10342. [DOI] [Google Scholar]

- 17.Ryu M.K., Park S.H.K., Hwang C.S., Yoon S.M. Comparative studies on electrical bias temperature instabilities of In–Ga–Zn–O thin film transistors with different device configurations. Solid-State Electron. 2013;89:171–176. doi: 10.1016/j.sse.2013.08.008. [DOI] [Google Scholar]

- 18.Jiang J., Toda T., Hung M.P., Wang D., Furuta M. Highly stable fluorine-passivated In-Ga-Zn-O thin-film transistors under positive gate bias and temperature stress. Appl. Phys. Express. 2014;7:114103. doi: 10.7567/APEX.7.114103. [DOI] [Google Scholar]

- 19.Jiang J., Tatsuya T., Tatsuoka G., Wang D., Furuta M. Improvement of Electrical Properties and Bias Stability of InGaZnO Thin-Film Transistors by Fluorinated Silicon Nitride Passivation. {ECS} Trans. 2014;64:59–64. doi: 10.1149/06410.0059ecst. [DOI] [Google Scholar]

- 20.Yamazaki H., Ishikawa Y., Fujii M., Ueoka Y., Fujiwara M., Takahashi E., Andoh Y., Maejima N., Matsui H., Matsui F., et al. The Influence of Fluorinated Silicon Nitride Gate Insulator on Positive Bias Stability toward Highly Reliable Amorphous InGaZnO Thin-Film Transistors. {ECS} J. Solid State Sci. Technol. 2013;3:20–23. doi: 10.1149/2.014402jss. [DOI] [Google Scholar]

- 21.Um J.G., Jang J. Heavily doped n-type a-IGZO by F plasma treatment and its thermal stability up to 600 °C. Appl. Phys. Lett. 2018;112:162104. doi: 10.1063/1.5007191. [DOI] [Google Scholar]

- 22.Lee S., Shin J., Jang J. Top Interface Engineering of Flexible Oxide Thin-Film Transistors by Splitting Active Layer. Adv. Funct. Mater. 2017;27:1604921. doi: 10.1002/adfm.201604921. [DOI] [Google Scholar]

- 23.Jeong H.Y., Lee B.Y., Lee Y.J., Lee J.I., Yang M.S., Kang I.B., Mativenga M., Jang J. Coplanar amorphous-indium-gallium-zinc-oxide thin film transistor with He plasma treated heavily doped layer. Appl. Phys. Lett. 2014;104:022115. doi: 10.1063/1.4862320. [DOI] [Google Scholar]

- 24.Otten M.T. High-Angle annular dark-field imaging on a tem/stem system. J. Electron Microsc. Tech. 1991;17:221–230. doi: 10.1002/jemt.1060170209. [DOI] [PubMed] [Google Scholar]

- 25.Herbig M., Choi P., Raabe D. Combining structural and chemical information at the nanometer scale by correlative transmission electron microscopy and atom probe tomography. Ultramicroscopy. 2015;153:32–39. doi: 10.1016/j.ultramic.2015.02.003. [DOI] [PubMed] [Google Scholar]