Abstract

Recently, three-terminal synaptic devices have attracted considerable attention owing to their nondestructive weight-update behavior, which is attributed to the completely separated terminals for reading and writing. However, the structural limitations of these devices, such as a low array density and complex line design, are predicted to result in low processing speeds and high energy consumption of the entire system. Here, we propose a vertical three-terminal synapse featuring a remote weight update via ion gel, which is also extendable to a crossbar array structure. This synaptic device exhibits excellent synaptic characteristics, which are achieved via precise control of ion penetration onto the vertical channel through the weight-control terminal. Especially, the applicability of the developed vertical organic synapse array to neuromorphic computing is demonstrated using a simple crossbar synapse array. The proposed synaptic device technology is expected to be an important steppingstone to the development of high-performance and high-density neural networks.

Subject terms: Engineering, Engineering, Materials science, Materials science, Nanoscience and technology

Though three-terminal organic synapses are attractive for artificial neural networks due their weight controllable property, their structural limitations hinder performance. Here, the authors report a crossbar synapse array featuring vertical organic synapses with remote weight update capability.

Introduction

With the rise of the “big data” era, in which there has been an explosion of unstructured data, such as images, text, sound, and video, handling such types of data through using conventional von Neumann computing with separate processing and memory units has become difficult1–5. Neuromorphic computing‒which mimics the ability of the human brain to perform energy-efficient parallel processing of information using a complex neural network (NN)‒has attracted considerable attention as one of the pathways to meet such technical demands6–10. The brain processes and memorizes information simultaneously, which makes it free from the bottleneck problem. As such NNs in the brain consist of numerous synapses, the development of high-density and low-power synapse-like devices is essential to the successful implementation of neuromorphic computing1,2,4,11–14. As pioneering research, extensive studies on an artificial synapse based on a two-terminal resistive memory device have been conducted in recent years4,7,11,13,15–17. These two-terminal synapses are fabricated in a crossbar array structure, whose simplicity and short channel ensure a high integration density and low power consumption. However, nondestructive weight update in the two-terminal synapse is difficult to be accomplished because of its structural nature, i.e., a single shared terminal for reading and writing7,15–21. Very recently, Wang et al. effectively alleviated this issue by applying a significantly low readout voltage pulse, but further researches are still required for resolving this issue fundamentally17. In the meantime, three-terminal synaptic devices have attracted considerable interest owing to their nondestructive-weight-update behavior, which is attributed to the completely separated terminals for reading (drain) and writing (gate)1,6,9,22–27. In recent studies, three-terminal artificial synapses implemented with various inorganic and organic materials showed a desirable weight-controllability property via various charge-storage principles using interfacial traps28–30, atomic vacancies14, ion intercalation22,26,28,31, and floating gates32–35. For example, electric-double-layer transistors and floating-gate transistors have been demonstrated to be able to successfully emulate a biological synapse12,32,33,36. However, three-terminal synapses have a lower array density and a structural limitation on line-design compared to the two-terminal crossbar array structure in a complicated circuit configuration; these drawbacks result in a lower processing speed and higher energy consumption of the entire system.

Herein we propose a vertical synapse featuring a remote weight update via ion gel, which is also extendable to a crossbar array structure. For the device configuration, a sub-100-nm-thick poly(3-hexylthiophene) (P3HT) channel is positioned at every cross-point of the pre- and postsynaptic terminals, and the ion-gel weight-control (WC) layer is deposited on them. Mobile ions in the ion gel readily penetrate the free volume in the P3HT channel, which results in a nonvolatile change in the channel conductance. Important synaptic properties, such as short-term plasticity (STP), excitatory and inhibitory postsynaptic currents (EPSC and IPSC, respectively), and long-term potentiation/depression (LTP/D) are evaluated via current–voltage measurements. In particular, the dimensional condition of vertical channel for achieving the optimal LTP/D characteristics are investigated via control of the channel length and area of the line cross-point. Finally, the applicability of the developed organic synapse array to the hardware NNs (HW-NNs) is evaluated in two ways: small-scale real-time learning and large-scale theoretical simulation.

Results

Fabrication of ion-gel-gated vertical crossbar synapse array and its synaptic properties

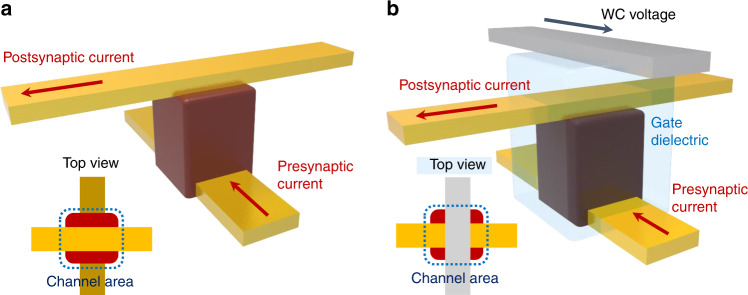

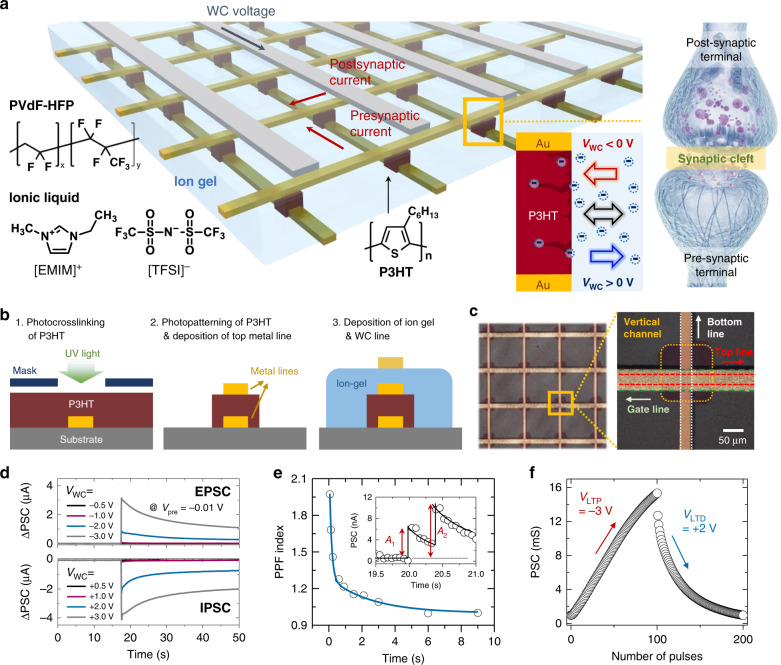

Figure 1a, b show a proof-of-concept illustration of vertical crossbar synapses with two-terminal and three-terminal device geometries, respectively. The three-terminal vertical synapses, enabled by remote gate controllability of ion-gel, are integrated into a large area crossbar array to construct an artificial neural network (ANN) as shown in Fig. 2a. The device array consisted of the bottom and top electrode lines, which corresponded to the pre- and postsynaptic terminals, respectively. The semiconducting polymer layer, sandwiched at every cross-point between the top and bottom electrode lines, served as the synaptic channel. The ion-gel layer and top gate lines were utilized to achieve the nonvolatile-weight-change property of a biological synapse as a WC terminal stack. By virtue of the free volume in the semiconducting polymer layer, mobile negative ions in the ion-gel could readily penetrate the channel under the application of a negative WC voltage (VWC)37,38. The penetration of negative ions (TFSI− ions) was proven using scanning electron microscope-energy dispersive X-ray spectroscopy (SEM-EDS) analysis (see details in Supplementary Fig. 1 and Supplementary Note 1). In contrast, ions moved out from the channel layer under the application of a positive VWC. The penetrating negative ions accumulated hole carriers in the channel layer, which led to an increase in the channel conductance. The conductance change in our ion-gel-gated device caused by the ion movement was similar to the operation of a biological synapse39–41. In the proposed ion-gel-gated artificial synapse, p-type P3HT was used as the vertical channel, whereas an ion-gel consisting of ionic liquid and poly(vinylidene fluoride-co-hexafluoropropylene) (PVdF-HFP) was used as the gate dielectric layer (see the chemical structures in Fig. 2a). Figure 2b shows a cross-sectional schematic of the fabrication procedure of the proposed ion-gel-gated vertical synapse. To fabricate the organic synapse array, a P3HT solution blended with a crosslinking agent was spin-coated onto the substrate with prepatterned bottom metal lines42,43. The channel was then defined by UV exposure and a subsequent solvent washing process. The top metal line was thermally deposited to form the vertical channel. Finally, the ion-gel gate dielectric layer was spin-coated, and the WC electrode lines were thermally deposited. Figure 2c shows an optical-microscopy image of the vertical transistor-type organic synapse array.

Fig. 1. Schematic illustration of synaptic devices.

a Two-terminal synapse. b Three-terminal synapse with crossbar array structure.

Fig. 2. Fabrication of ion-gel-gated vertical crossbar synapse array and its synaptic properties.

a Schematic diagram of ion-gel-gated vertical crossbar synapse array mimicking biological NN. The inset shows the chemical structures of P3HT, PVdF-HFP, and ionic liquid ([TFSI]- anion and [EMIM]+ cation). b Cross-sectional schematic of fabrication procedure of ion-gel-gated vertical P3HT synapse. c Optical microscopy image of crossbar synapse array. d EPSC and IPSC responses induced by negative and positive VWCs with magnitudes varying from ± 0.5 to ± 3 V. e Plot of PPF index as a function of Δt for proposed ion-gel-gated P3HT crossbar synaptic device. The inset shows the PSC generated by a pair of VWC stimuli. f LTP/D characteristics of synaptic device under application of 100 consecutive potentiation pulses (VWC = −3 V) followed by 100 consecutive depression pulses (VWC = +2 V).

The channel conductance of a transistor-type synaptic device is correlated to the synaptic weight in a biological synapse17,24. Thus, we applied a VWC pulse to the WC terminal and monitored the postsynaptic current (PSC) between the bottom (source) and top (drain) lines. A typical PSC–VWC characteristic curve of the ion-gel-gated vertical synaptic device is shown in Supplementary Fig. 2. The device showed a high on/off ratio of over 105 within a small VWC operation range of ±4 V. A clear hysteresis loop was observed in the clockwise direction because of the slow movement of the penetrating ions within the P3HT channel37,38. Then, the synaptic properties, including the EPSC/IPSC, paired-pulse facilitation (PPF), and LTP/D, of the ion-gel-gated vertical synapse were analyzed. Under varied VWC with its amplitude from ±0.5 to ±3 V and width of 50 ms, the PSC measured at a constant presynaptic voltage (Vpre) of −0.01 V showed clear EPSC and IPSC responses (Fig. 2d). The PSC immediately increased (decreased) upon the application of negative (positive) VWC, and it was retained even after 50 s; however, it did not return to the initial value, because of the residual ions in the P3HT layer.

Next, the STP of our synaptic device was investigated. Figure 2e shows the PPF characteristics of the device measured under a small VWC of −1 V. In this voltage, ion penetration into the P3HT channel was limited, and thus, the device showed clear STP behavior. As shown in the inset of Fig. 2e, two successive pulses applied at a shorter interval evoked highly amplified EPSC responses. The PPF index can be defined as the ratio of the first PSC peak to the second PSC peak (A2/A1)39,41. This PPF index decreased exponentially as the interval between the first and second pulses (Δt) increased. The relationship between the PPF index and the interval can be expressed as PPF = 1 + C1 exp(−Δt/τ1) + C2 exp(−Δt/τ2), where τ1 and τ2 denote the relaxation times of rapid and slow phases, respectively, and C1 and C2 are constants representing the initial facilitation magnitude of rapid and slow pulses, respectively. Our ion-gel-gated vertical synapse showed τ1 of 87 ms and τ2 of 1762 ms, which coincided with the corresponding values of a biological synapse39–41. Our synaptic device also showed reliable long-term plasticity behavior wherein the changed current did not completely return to the initial value, because of the residual ions in the P3HT channel. To analyze the LTP/D characteristics of the proposed device, 100 consecutive potentiation pulses (VWC = −3 V, 50 ms) followed by 100 consecutive depression pulses (VWC = +2 V, 50 ms) were applied to the WC terminal. As shown in Fig. 2f, the PSC after 100 negative pulses increased up to 15.3 mS, after which it decreased continuously with the application of positive pulses. Overall, the device successfully mimicked various electrical behaviors that occur in biological synapses, including short-term and long-term properties.

Optimization of vertical synaptic device geometry

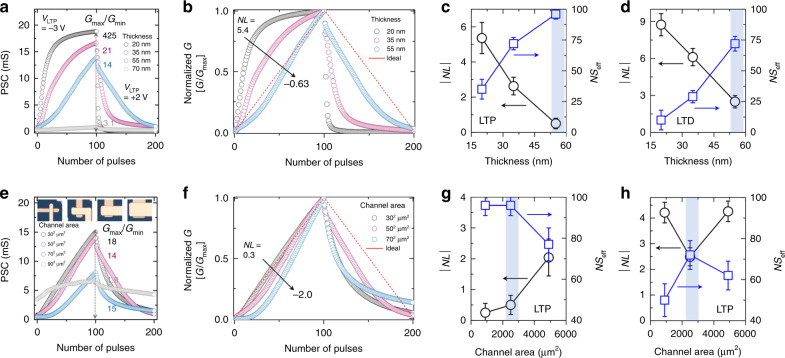

The LTP/D characteristics of a synaptic device are considered as its most critical property in neuromorphic computing because key factors of the LTP/D curves, such as the dynamic range (Gmax/Gmin), nonlinearity (NL), and effective number of states (NSeff), have a significant impact on the accuracy of the learning/recognition tasks performed by an ANN44,45. Therefore, we optimized the LTP/D characteristics of the proposed device by adjusting the ion-penetration behavior through tuning of the channel thickness and area of the ion-gel-gated vertical synapse. Figure 3a and Supplementary Fig. 3 show the LTP/D characteristics of vertical synaptic devices with P3HT channels of various thicknesses under the application of a set of VWC pulses consisting of 100 potentiation pulses (VWC = −3 V) and 100 depression pulses (VWC = + 2 V). Here, the pulse frequency and pulse width were fixed at 2 Hz and 50 ms, respectively (see Supplementary Figs. 4 and 5, and Supplementary Notes 2 and 3 for the additional information about various pulse frequencies and pulse widths). The thickness of the P3HT channel was controlled in the range of 20–95 nm by varying the concentration of the P3HT solution, whereas the channel area was fixed at 50 × 50 μm2. The maximum conductance value (Gmax) was the highest (18.9 mS) in the device with the thinnest channel (20 nm), and it decreased to 2.3 μS with an increase in the thickness of the P3HT channel to 95 nm. Because the channel thickness is considered as the channel length in a vertically stacked device, in this study, the channel length of the synaptic device increased with increasing thickness of the P3HT channel; this resulted in a decrease in the overall channel conductance. The dynamic range (Gmax/Gmin) values of the synaptic devices having 20-, 35-, and 55-nm-thick P3HT channels were higher than 10, which is the minimum value required for a successful pattern recognition task45. To extract the values of NL and NSeff, which represent the precision of the weight-update behavior, we first normalized the LTP/D characteristic curves of the devices with different channel lengths by dividing each conductance value by the maximum value (G/Gmax), as shown in Fig. 3b. Then, we calculated the NL value by fitting the measured curve to the normalized one (see detailed equations in the methods section, Supplementary Figure 6, and Supplementary Note 4). The synaptic device with the thinnest channel (20 nm) showed a positive NL value (+5.4). In this device, the ions were able to penetrate the entire channel upon the application of VWC pulses, which enhanced the overall channel controllability. In contrast, the NL values of the devices with the thicker channels decreased in the negative direction and reached −0.6 for the device with the 55-nm-thick P3HT channel. This is because the channel region far away from the ion gel was relatively impermeable to the mobile ions in the thick-channel device, which degraded the controllability of channel conductance under the same number of VWC pulses. Note that a similar behavior of the NL value was seen in the LTD region. The synaptic device with the 20-nm-thick channel exhibited a sharp decrease in the NL value as high as −8.7, and the 55-nm-thick P3HT exhibited a relatively linear decreasing characteristic (NLLTD = − 2.3). Figure 3c, d show the absolute NL and NSeff values plotted as functions of the P3HT thickness for the LTP and LTD characteristics, respectively. Here, states having ΔG above the noise range (0.5% of Gmax − Gmin) were defined as the effective states. The |NL| value (denoted by black circles) was lowest (0.6/2.3 for LTP/D regions) for the device with the 55-nm-thick P3HT channel. This device also showed the highest NSeff of 96/72 for the LTP/D regions.

Fig. 3. Optimization of vertical synaptic device geometry.

a LTP/D characteristics of thickness-controlled vertical crossbar synaptic devices under application of 100/100 potentiation/depression pulses (VWC pulses with amplitudes of −3 V/+2 V). Devices had P3HT channels with thicknesses of 20, 35, 50, and 70 nm. b, Normalized LTP/D curves of thickness-controlled synaptic devices. c Plots of |NL| and NSeff as functions of thickness of P3HT channel in LTP region and (d) LTD region. e LTP/D characteristics of synaptic devices with various areas of line cross-point. Channel area (Ach) was controlled to 30 × 30, 50 × 50, 70 × 70, and 90 × 90 μm2 as shown in the inset. f Normalized LTP/D curves of area-controlled synaptic devices. Plots of |NL | and NSeff as functions of area of line cross-point in g LTP and h LTD region. The average |NL|and NSeff are obtained from five devices prepared independently, and the error bars represents the standard deviation of the data.

Next, the effect of the channel area on the LTP/D characteristics was investigated by varying the width of metal lines (Fig. 3e, f). The channel areas were controlled to 30 × 30, 50 × 50, 70 × 70, and 90 × 90 μm2, where the thickness of the P3HT channel (that is, channel length) was fixed at 55 nm. Among these devices, the one with the largest channel area (90 × 90 μm2) showed the highest conductance value in the absence of any external voltage stimulus (VWC = 0 V), which indicates that the device had the lowest channel resistance (Supplementary Fig. 7). However, this device with the 90 × 90 μm2 channel showed a poor Gmax/Gmin of 1.9, which was attributed to the obstruction of ion penetration by the large metal coverage (Supplementary Fig. 8). The Gmax/Gmin value increased from 1.9 to 18 as the channel area decreased from 90 × 90 μm2 to 30 × 30 μm2, because of the enhanced channel controllability. The highest Gmax and Gmax/Gmin values were obtained for the device with the 30 × 30 μm2 channel. The absolute value of NL and the NSeff value for the LTP/D regions were plotted as a function of the channel area, as shown in Fig. 3g, h. The device with a channel area of 50 × 50 μm2 exhibited desirable synaptic properties in both the LTP and LTD regions (i.e., low |NL| values and the highest NSeff). The device with the channel area of 30 × 30 μm2 also showed a low |NL| of 0.35 and high NSeff of 96. However, this device had a high |NL| value of 4.2 and a low NSeff of 50 in the LTD region. Overall, the LTP/D characteristics of the ion-gel-gated vertical synapse were strongly affected by the ion penetration into the organic channel. From these results, the device with the channel area of 50 × 50 μm2 and channel thickness of 55 nm was confirmed to exhibit desirable LTP/D characteristics such as large Gmax/Gmin, low |NL|, and sufficient NSeff.

Operational stability of vertical synaptic device

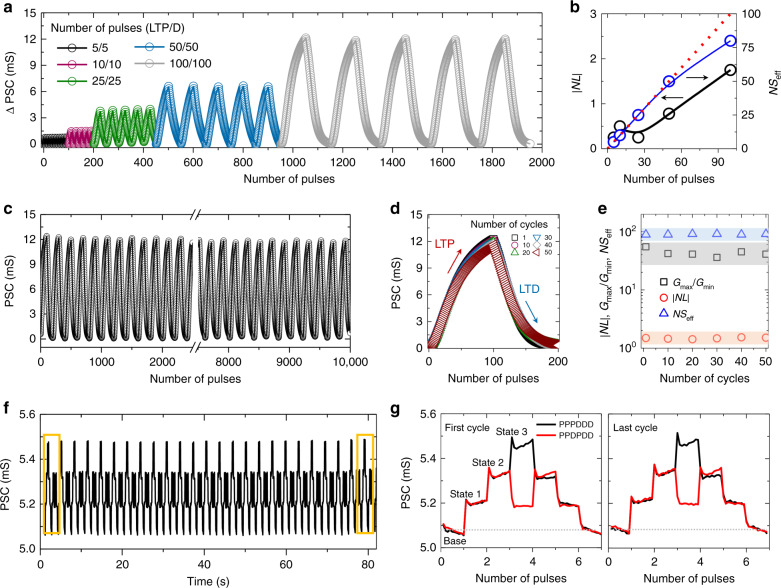

In addition to the high LTP/D performance of a synaptic device, its operation must also be stable to enable its practical application to an ANN44,45. To investigate the repeatability and stability of the LTP/D characteristics in each cycle, various pulse sets with different numbers of pulses were applied to the WC terminal. The potentiation and depression pulses were set to −3 V and +2 V, respectively (see the LTD optimization procedure in Supplementary Fig. 9 and Supplementary Note 5). Figure 4a shows the PSC response of the synaptic device over five cycles under the application of different numbers of pulses, ranging from 5 to 100 (a total of 2000 pulses). The LTP/D characteristic curves extracted under the application of various pulse sets were highly stable and repeatable over the five cycles. To investigate the synaptic characteristics more quantitatively, we calculated the |NL| and NSeff values. As shown in Fig. 4b, our synaptic device showed a linear weight-update behavior of |NL| < 2 for all pulse sets. We then extended the number of measurement cycles to 50 (a total of 10000 update pulses) and investigated the PSC response (Fig. 4c and Supplementary Fig. 10). During the test, our device showed reliable LTP/D behavior without any sign of degradation (Fig. 4d). Furthermore, key parameters such as NL, NSeff, and Gmax/Gmin remained constant during the lengthy cycle test (Fig. 4e). The cycle-to-cycle variations of |NL|, NSeff, and Gmax/Gmin were calculated to be 1.4%, 6.4%, and 1.1%, respectively. Additionally, we investigated the LTP/D characteristics by elongating the cycle test to 200 k pulses for observing the degradation of the device performance (Supplementary Fig. 11 and Supplementary Note 6). Then, reliability of the PSC was also investigated under irregular-pulse conditions. Figure 4f shows a plot of the real-time change in the PSC of the device under the application of two different VWC pulse sets. The regular set consisted of successive potentiation (P) and depression (D) pulses (PPPDDD), whereas the random set consisted of randomly arranged P and D pulses (PPDPDD). For a detailed evaluation of the PSC change, the PSC plots in the first and last cycles of the regular set (black line) and random set (red line) were overlapped, as shown in the middle and right panels of Fig. 4g. The variation in the PSC state between the regular- and random-pulse conditions was lower than 1% at the base state for every pulse cycle. This value is quite comparable with other research results reported thus far (see the comparison in Supplementary Table 1 and Supplementary Note 7). Overall, the optimized vertical synaptic device showed stable weight-update behavior under various VWC conditions. Additionally, we investigated the writing energy of the device for single potentiation/depression pulse by measuring the current between WC terminal and postsynaptic terminal (see details in Supplementary Fig. 12 and Supplementary Note 8). The device exhibited energy consumption of 11.9/1.6 nJ for the potentiation/depression pulse, which was further reduced to 0.25/0.17 nJ under a pulse width of 700 ns.

Fig. 4. Operational stability of vertical synaptic device.

a LTP/D characteristics of vertical crossbar synapse array under application of various potentiation/depression pulse sets. b Plots of |NL| and NSeff as functions of pulse number for single cycle. c LTP/D characteristics of vertical synaptic device over 50 cycles. Number of potentiation/depression pulses for single cycle was set to 100/100. d Cycle-to-cycle variations of LTP/D curve for 50 cycles. e Plots of Gmax/Gmin, |NL|, and NSeff for 50 LTP/D cycles. f State stability under application of random combinations of potentiation/depression pulses with amplitudes of −3 V/+2 V. g Overlapping of PSC plots in the first and last cycles of regular (PPPDDD) and irregular (PPDPDD) pulse sets.

Logic application of vertical synaptic device and training/recognition processes

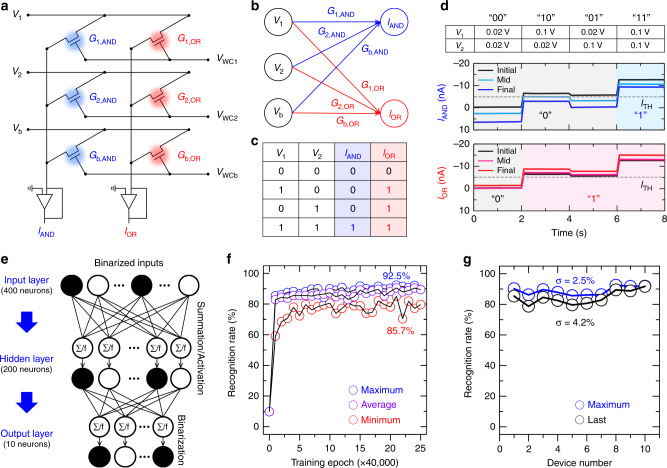

Finally, to confirm the applicability of the developed device to HW-NNs, we prepared a small-scale synapse array with a size of 2 × 3 and trained Boolean logic operations such as binary AND and OR onto the neural network based on the synapse array. Various logic gate operations can be implemented on this neural network platform via the training of the gate functions, as in the case of reconfigurable circuits1,43,46. Figure 5a shows circuit diagrams of AND and OR gates composed with our synaptic devices. V1 and V2 denote two logic inputs, and Vb denotes a bias voltage. The G means a conductance value of the synaptic device. The VWC1, VWC2, and VWCb denote weight-control voltages. IAND and IOR are the output currents corresponding to the AND and OR logic operations, respectively. This circuit matches a single-layer neural network consisting of three input neurons, two output neurons, and six synapses connecting them, as shown in Fig. 5b. The learning process of this neural network is as follows. When the input voltages are applied to the input neurons, the output current vector (I) is calculated as the inner product between the conductance matrix of the synaptic array (G) and the input voltage vector (V), i.e., I = GV. We then compare the obtained output currents with a threshold value (here, ITH = −5 nA), consequently distinguishing whether the output is “0” or “1”. If the output current is less than −5 nA, its state is considered as “0”; else, its state is considered as “1”. As the final step of the learning, all conductance values in the synaptic array are updated by VWC toward reducing difference between the output value and the corresponding value of the truth table in Fig. 5c. Through this learning process, we updated all conductance values of the synaptic array in real-time and then investigated output currents when the two logic inputs were “00”, “10”, “01”, or “11”, respectively (Fig. 5d). Two voltage values of 0.02 V and 0.2 V were used for binary logic input states of “0” and “1”, respectively. Before training (black line), the initial output currents were close to the ITH so that were difficult to determine the output state. Particularly, when the inputs were “10” or “01”, there were little differences between the output current values and the threshold value in both operations of AND and OR. However, as the learning proceeded and after completing the learning, the differences between those values became more explicit. This result successfully demonstrated that our synapse array can be functionalized as the AND and OR logic gates via the learning process.

Fig. 5. Logic application of vertical synaptic device and training/recognition processes.

a Schematic illustration of AND and OR logic gates implemented using proposed synaptic array with size of 2 × 3. b Simplified diagram of NN for AND and OR logic gates. c Truth table of AND and OR logic gates. d Real-time training and classification of AND and OR gates using implemented synaptic array. e Schematic illustration of two-layer perceptron-based ANN with size of 400 × 200 × 10. f Recognition rate as a function of number of training epochs for 10 synaptic devices; the maximum, average, and minimum recognition rates are indicated in blue, purple, and red, respectively. g Maximum (blue) and final (black) recognition rates of 10 synaptic devices.

To further investigate the feasibility of the synapse array toward HW-NNs, we theoretically constructed a large-scale NN with a size of 400 × 200 × 10 with the measured LTP/D characteristics of 10 synaptic devices (Fig. 5e)44. We then performed the training/recognition tasks for Modified National Institute of Standards and Technology (MNIST) digit patterns and plotted the recognition rate of each device at every 40,000 training number (1 epoch) in Fig. 5f. The corresponding parameters of each synaptic device used in the simulation are listed in Supplementary Table 2. Among the 10 devices, the maximum accuracy was recorded to be as high as 92.5% when the NL value for LTP/D and the dynamic range were −1.25/−5.72 and 10.72, respectively. The minimum accuracy was 85.7% when the NL value for LTP/D and the dynamic range were −0.42/−6.77 and 49.33, respectively. Further improvement in the accuracy was achieved later by pulse engineering (Supplementary Fig. 13 and Supplementary Note 9). We then investigated the device-to-device variation in the recognition rate for the 10 synaptic devices (Fig. 5g). The standard deviation of maximum recognition rates was as low as 2.5%, and the standard deviation after the 25 epoch learning was 4.2%. Through this theoretical learning and recognition task, we confirmed the applicability of the proposed synapse array for more complex HW-NNs.

Discussion

In this study, we successfully implemented a crossbar synapse array based on a vertical organic transistor with an ion-gel WC layer. This three-terminal synapse array was achieved by adopting the vertical gate-all-around field effect transistor (GAA-FET) concept and securing acceptable gate controllability with the assistance of an ion-gel dielectric. Mobile ions in the ion gel penetrated the free volume in the P3HT vertical organic channel located at every cross-point between the top and bottom electrode lines, which resulted in a nonvolatile change in the channel conductance. By virtue of ion movement, the proposed device exhibited diverse synaptic characteristics, such as STP, EPSC/IPSC, and LTP/D. In particular, optimization of the channel length and area of the line cross-point yielded excellent LTP/D characteristics, such as a large dynamic range (>10), low nonlinearity (<1), sufficient effective number of conductance states (>64), and low cycle variation (<1%). Furthermore, we demonstrated the feasibility of using the proposed vertical organic synapse array for implementing a complex NN through real-time training and classification tasks in a simple 2 × 3 NN. A very high recognition rate of 92.5% for MNIST digit patterns was achieved in a simulated two-layer ANN with a size of 400 × 200 × 10. To implement a hardware ANN with the vertical organic synapses as a follow-up research, the excellent endurance of the synapses is critically required. In this regard, identifying and understanding the failure mechanism for weight update will help in assessing and improving the endurance. Besides, the researches optimizing encapsulation layers, ion-gel dielectrics, and organic semiconductors in the synapses need to be done for the excellent endurance. Notably, this GAA-FET concept has already been considered for 3-nm technology nodes (for a lateral type) and next technology node (for a vertical type) by many global semiconductor companies. Thus, this research is meaningful as a proof-of-concept of a cross-point FET-type synapse array that can be used to implement NNs based on Si CMOS technology. We expect the proposed vertical crossbar synapse array to play a pioneering role in the development of high-performance and high-density NNs in the future.

Methods

Materials

Processing solvents such as acetone, chloroform, and 2-propanol were purchased from Sigma-Aldrich. Regioregular P3HT (Mn: 54,000–75,000, lot number: MKCK1947), PVdF-HFP (Mn: 110,000), and 1-ethyl-3-methylimidazolium bis(trifluoromethylsulfonyl)imide (EMIM:TFSI) ionic liquid were also purchased from Sigma-Aldrich. The azide crosslinker bis(6-((4-azido-2,3,5,6-tetrafluorobenzoyl)oxy) hexyl)decanedioate was synthesized as previously reported42. P3HT solution was prepared by dissolving P3HT in concentrations of 3, 5, 7, 9, 11, and 13 mg mL−1 in chloroform for obtaining P3HT organic channels of various thicknesses. After being stirred on a hot plate for 5 h at 50 °C, the P3HT solution was blended with the azide crosslinker (5 mg mL−1 in chloroform) in a 4:1 ratio. Ion-gel solution was prepared by mixing the EMIM:TFSI ionic liquid, PVdF-HFP, and acetone solvent in a 4:1:7 ratio. The ion-gel solution was stirred at 50 °C for 5 h before use.

Fabrication of vertical synapse

The bottom metal lines (Cr/Au with 1 nm/17 nm thickness) were thermally deposited on a cleaned SiO2/Si++ (thermally grown 100 nm SiO2) wafer. The photopatternable P3HT solution was spin-coated on top of the metal lines at 1,500 rpm for 30 s. The crosslinking reaction of the channel area was performed under selective UV irradiation (254 nm and 1000 W cm−2) through a metal shadow mask for 30 s. Then, unexposed P3HT solution was removed with chloroform to define the crosslinked channel area, and the sample was dried for 12 h in a glovebox. After deposition of the top metal lines (30-nm-thick Au) via thermal evaporation, the ion-gel layer was spin-coated at 1000 rpm and dried at 70 °C for 5 min. Finally, 50-nm-thick Au as a WC line was thermally deposited.

Device characterization

The thickness of the crosslinked P3HT film was analyzed using tapping-mode atomic force microscopy (Asylum Cypher S system). The electrical properties of the vertical synaptic device and logic gates were measured using a Keithley 4200 electrometer.

NL calculation

The NL value of the LTP/D curve was calculated using the following equations:

| 1 |

| 2 |

| 3 |

where GLTP and GLTD are the conductance values of the LTP and LTD regions, respectively; P is the number of applied pulses; A is a parameter representing NL; and B is a fitting constant used to normalize the conductance range. The A value was extracted from the experimental data using the MATLAB code provided as an open source44, and the corresponding NL values were derived from tables provided by the same source.

Simulation of two-layer neural network

The simulation was conducted on the basis of the platform “MLP + NeuroSim ver. 1.0”. A multilayer (two-layer) perceptron-based ANN with a size of 400 × 200 × 10 was theoretically constructed using non-ideal factors, including the dynamic range and NL. Then, 20 × 20 MNIST digit patterns were binarized to black-and-white patterns, and a logistic function was used as the activation function. The optimized learning rates for the first and second synaptic weight matrices were 0.2 and 0.025, respectively. After being trained with 1 million patterns, the two-layer ANN was used to perform a classification task for 10,000 separate testing images. The recognition rate was calculated for every 40,000 images during the training process.

Supplementary information

Acknowledgements

We acknowledge the grants from Basic Science Research Program and Nano Material Technology Development Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science, ICT & Future Planning (2020R1A2C2007819, 2016M3A7B4910426, and 2020R1A4A2002806) and the Creative Materials Discovery Program (NRF-2019M3D1A1078299) through the NRF of Korea funded by the Ministry of Science and ICT, Korea.

Author contributions

Y.C. and S.O. contributed equally to this work as the first author. Y.C. conducted the fabrication and analysis of the device. S.O. conducted the equipment setup for measuring synaptic characteristics as well as construction and evaluation of the ANN. C.Q. gave a general advice on measuring and analysis of synaptic properties. J.H.P. and J.H.C. initiated the research, designed all the experiments. All authors discussed the results and contributed to the paper.

Data availability

All data generated or analyzed during this study are included in this published article (and its Supplementary Information files).

Competing interests

The authors declare no competing interests.

Footnotes

Peer review information Nature Communications thanks Su-Ting Han, Matthew Marinella and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. Peer reviewer reports are available.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

These authors contributed equally: Yongsuk Choi, Seyong Oh.

Contributor Information

Jin-Hong Park, Email: jhpark9@skku.edu.

Jeong Ho Cho, Email: jhcho94@yonsei.ac.kr.

Supplementary information

Supplementary information is available for this paper at 10.1038/s41467-020-17850-w.

References

- 1.Fuller EJ, et al. Parallel programming of an ionic floating-gate memory array for scalable neuromorphic computing. Science. 2019;364:570–574. doi: 10.1126/science.aaw5581. [DOI] [PubMed] [Google Scholar]

- 2.LeCun Y, Bengio Y, Hinton G. Deep learning. Nature. 2015;521:436–444. doi: 10.1038/nature14539. [DOI] [PubMed] [Google Scholar]

- 3.Merolla PA, et al. A million spiking-neuron integrated circuit with a scalable communication network and interface. Science. 2014;345:668–673. doi: 10.1126/science.1254642. [DOI] [PubMed] [Google Scholar]

- 4.Xia Q, Yang JJ. Memristive crossbar arrays for brain-inspired computing. Nat. Mater. 2019;18:309–323. doi: 10.1038/s41563-019-0291-x. [DOI] [PubMed] [Google Scholar]

- 5.Xu X, et al. Scaling for edge inference of deep neural networks. Nat. Electron. 2018;1:216–222. [Google Scholar]

- 6.Gkoupidenis P, Koutsouras DA, Malliaras GG. Neuromorphic device architectures with global connectivity through electrolyte gating. Nat. Commun. 2017;8:15448. doi: 10.1038/ncomms15448. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 7.Ielmini D, Wong HSP. In-memory computing with resistive switching devices. Nat. Electron. 2018;1:333–343. [Google Scholar]

- 8.Roy K, Jaiswal A, Panda P. Towards spike-based machine intelligence with neuromorphic computing. Nature. 2019;575:607–617. doi: 10.1038/s41586-019-1677-2. [DOI] [PubMed] [Google Scholar]

- 9.van de Burgt Y, et al. A non-volatile organic electrochemical device as a low-voltage artificial synapse for neuromorphic computing. Nat. Mater. 2017;16:414–418. doi: 10.1038/nmat4856. [DOI] [PubMed] [Google Scholar]

- 10.van de Burgt Y, Melianas A, Keene ST, Malliaras G, Salleo A. Organic electronics for neuromorphic computing. Nat. Electron. 2018;1:386–397. [Google Scholar]

- 11.Kuzum D, Jeyasingh RGD, Lee B, Wong HSP. Nanoelectronic programmable synapses based on phase change materials for brain-inspired computing. Nano Lett. 2012;12:2179–2186. doi: 10.1021/nl201040y. [DOI] [PubMed] [Google Scholar]

- 12.Lenz J, del Giudice F, Geisenhof FR, Winterer F, Weitz RT. Vertical, electrolyte-gated organic transistors show continuous operation in the MA cm−2 regime and artificial synaptic behaviour. Nat. Nanotechnol. 2019;14:579–585. doi: 10.1038/s41565-019-0407-0. [DOI] [PubMed] [Google Scholar]

- 13.Moon K, et al. Rram-based synapse devices for neuromorphic systems. Faraday Discuss. 2019;213:421–451. doi: 10.1039/c8fd00127h. [DOI] [PubMed] [Google Scholar]

- 14.Shi J, Ha SD, Zhou Y, Schoofs F, Ramanathan S. A correlated nickelate synaptic transistor. Nat. Commun. 2013;4:2676. doi: 10.1038/ncomms3676. [DOI] [PubMed] [Google Scholar]

- 15.Boybat I, et al. Neuromorphic computing with multi-memristive synapses. Nat. Commun. 2018;9:2514. doi: 10.1038/s41467-018-04933-y. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 16.Josberger EE, Deng Y, Sun W, Kautz R, Rolandi M. Two-terminal protonic devices with synaptic-like short-term depression and device memory. Adv. Mater. 2014;26:4986–4990. doi: 10.1002/adma.201400320. [DOI] [PubMed] [Google Scholar]

- 17.Wang Z, et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. Nat. Mater. 2017;16:101–108. doi: 10.1038/nmat4756. [DOI] [PubMed] [Google Scholar]

- 18.Burr GW, et al. Experimental demonstration and tolerancing of a large-scale neural network (165 000 synapses) using phase-change memory as the synaptic weight element. IEEE Trans. Electron Devices. 2015;62:3498–3507. [Google Scholar]

- 19.Oh S, Shi Y, Liu X, Song J, Kuzum D. Drift-enhanced unsupervised learning of handwritten digits in spiking neural network with pcm synapses. IEEE Electron Device Lett. 2018;39:1768–1771. [Google Scholar]

- 20.Shi Y, et al. Neuroinspired unsupervised learning and pruning with subquantum cbram arrays. Nat. Commun. 2018;9:5312. doi: 10.1038/s41467-018-07682-0. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 21.Yao P, et al. Face classification using electronic synapses. Nat. Commun. 2017;8:15199. doi: 10.1038/ncomms15199. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 22.Zhu J, et al. Ion gated synaptic transistors based on 2D van der waals crystals with tunable diffusive dynamics. Adv. Mater. 2018;30:1800195. doi: 10.1002/adma.201800195. [DOI] [PubMed] [Google Scholar]

- 23.Seo S, et al. Artificial optic-neural synapse for colored and color-mixed pattern recognition. Nat. Commun. 2018;9:5106. doi: 10.1038/s41467-018-07572-5. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 24.Sangwan VK, et al. Multi-terminal memtransistors from polycrystalline monolayer molybdenum disulfide. Nature. 2018;554:500–504. doi: 10.1038/nature25747. [DOI] [PubMed] [Google Scholar]

- 25.Kim S, et al. Pattern recognition using carbon nanotube synaptic transistors with an adjustable weight update protocol. ACS Nano. 2017;11:2814–2822. doi: 10.1021/acsnano.6b07894. [DOI] [PubMed] [Google Scholar]

- 26.Fuller EJ, et al. Li-ion synaptic transistor for low power analog computing. Adv. Mater. 2017;29:1604310. doi: 10.1002/adma.201604310. [DOI] [PubMed] [Google Scholar]

- 27.Tian H, et al. Anisotropic black phosphorus synaptic device for neuromorphic applications. Adv. Mater. 2016;28:4991–4997. doi: 10.1002/adma.201600166. [DOI] [PubMed] [Google Scholar]

- 28.Sharbati MT, et al. Low-power, electrochemically tunable graphene synapses for neuromorphic computing. Adv. Mater. 2018;30:1802353. doi: 10.1002/adma.201802353. [DOI] [PubMed] [Google Scholar]

- 29.Dai S, et al. Light-stimulated synaptic devices utilizing interfacial effect of organic field-effect transistors. ACS Appl. Mater. Interfaces. 2018;10:21472–21480. doi: 10.1021/acsami.8b05036. [DOI] [PubMed] [Google Scholar]

- 30.Qian C, et al. Solar-stimulated optoelectronic synapse based on organic heterojunction with linearly potentiated synaptic weight for neuromorphic computing. Nano Energy. 2019;66:104095. [Google Scholar]

- 31.Yang J-T, et al. Artificial synapses emulated by an electrolyte-gated tungsten-oxide transistor. Adv. Mater. 2018;30:1801548. doi: 10.1002/adma.201801548. [DOI] [PubMed] [Google Scholar]

- 32.Qian C, et al. Artificial synapses based on in-plane gate organic electrochemical transistors. ACS Appl. Mater. Interfaces. 2016;8:26169–26175. doi: 10.1021/acsami.6b08866. [DOI] [PubMed] [Google Scholar]

- 33.Sun J, et al. Optoelectronic synapse based on IGZO-alkylated graphene oxide hybrid structure. Adv. Funct. Mater. 2018;28:1804397. [Google Scholar]

- 34.Lv Z, et al. Mimicking neuroplasticity in a hybrid biopolymer transistor by dual modes modulation. Adv. Funct. Mater. 2019;29:1902374. [Google Scholar]

- 35.Wang Y, et al. Photonic synapses based on inorganic perovskite quantum dots for neuromorphic computing. Adv. Mater. 2018;30:1802883. doi: 10.1002/adma.201802883. [DOI] [PubMed] [Google Scholar]

- 36.Xu W, Min S-Y, Hwang H, Lee T-W. Organic core-sheath nanowire artificial synapses with femtojoule energy consumption. Sci. Adv. 2016;2:e1501326. doi: 10.1126/sciadv.1501326. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 37.Kim SH, et al. Electrolyte-gated transistors for organic and printed electronics. Adv. Mater. 2013;25:1822–1846. doi: 10.1002/adma.201202790. [DOI] [PubMed] [Google Scholar]

- 38.Xie W, Liu F, Shi S, Ruden PP, Frisbie CD. Charge density dependent two-channel conduction in organic electric double layer transistors (EDLTs) Adv. Mater. 2014;26:2527–2532. doi: 10.1002/adma.201304946. [DOI] [PubMed] [Google Scholar]

- 39.Zhong Y-N, Wang T, Gao X, Xu J-L, Wang S-D. Synapse-like organic thin film memristors. Adv. Funct. Mater. 2018;28:1800854. [Google Scholar]

- 40.Buonomano DV, Maass W. State-dependent computations: Spatiotemporal processing in cortical networks. Nat. Rev. Neurosci. 2009;10:113–125. doi: 10.1038/nrn2558. [DOI] [PubMed] [Google Scholar]

- 41.Zhu LQ, Wan CJ, Guo LQ, Shi Y, Wan Q. Artificial synapse network on inorganic proton conductor for neuromorphic systems. Nat. Commun. 2014;5:3158. doi: 10.1038/ncomms4158. [DOI] [PubMed] [Google Scholar]

- 42.Png R-Q, et al. High-performance polymer semiconducting heterostructure devices by nitrene-mediated photocrosslinking of alkyl side chains. Nat. Mater. 2010;9:152–158. doi: 10.1038/nmat2594. [DOI] [PubMed] [Google Scholar]

- 43.Zhao S, et al. Electroluminescent synaptic devices with logic functions. Nano Energy. 2018;54:383–389. [Google Scholar]

- 44.Chen, P., Peng, X. & Yu, S. Neurosim+: An integrated device-to-algorithm framework for benchmarking synaptic devices and array architectures. in Proc. 2017 IEEE International Electron Devices Meeting (IEDM), p. 6.1.1–6.1.4. (IEEE, 2017).

- 45.Kim M-K, Lee J-S. Ferroelectric analog synaptic transistors. Nano Lett. 2019;19:2044–2050. doi: 10.1021/acs.nanolett.9b00180. [DOI] [PubMed] [Google Scholar]

- 46.Sun Z, Ambrosi E, Bricalli A, Ielmini D. Logic computing with stateful neural networks of resistive switches. Adv. Mater. 2018;30:1802554. doi: 10.1002/adma.201802554. [DOI] [PubMed] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Supplementary Materials

Data Availability Statement

All data generated or analyzed during this study are included in this published article (and its Supplementary Information files).