Abstract

The bandgap dependence on the number of atomic layers of some families of two-dimensional (2D) materials can be exploited to engineer and use lateral heterostructures (LHs) as high-performance field-effect transistors (FETs). This option can provide very good lattice matching as well as high heterointerface quality. More importantly, this bandgap modulation with layer stacking can give rise to steep transitions in the density of states (DOS) of the 2D material that can eventually be used to achieve sub-60 mV/decade subthreshold swing in LH-FETs thanks to an energy-filtering source. We have observed this effect in the case of a PdS2 LH-FET due to the particular DOS of its bilayer configuration. Our results are based on ab initio and multiscale materials and device modeling and incite the exploration of the 2D-material design space in order to find more abrupt DOS transitions and better suitable candidates.

Keywords: lateral heterostructures, two-dimensional materials, energy filtering source, field-effect transistor, sub-60 mV/decade subthreshold swing, multiscale simulations

Semiconductor heterostructures of the III–V and II–VI materials systems have played a fundamental role in the progress of electronics and optoelectronics. First proposed by Kroemer in the 1950s,1 they have been involved in the invention of quantum-well lasers2 and high-electron-mobility transistors.3 The large number of available two-dimensional (2D) materials and the possibility to combine them even in the presence of significant lattice mismatch has led to a new wave of interest in materials engineering based on heterostructures of 2D materials. In particular, 2D materials enable the realization of vertical heterostructures, also called “van der Waals” heterostructures, consisting in the vertical stacking of layers of different 2D materials loosely coupled by van der Waals interactions,4,5 and of lateral heterostructures (LHs), in which a single 2D layer consists of juxtaposed regions of different lattice-matched 2D materials.6−9

LHs have been shown to be particularly well suited as channel materials in high-performance field-effect transistors (FETs) for digital electronics.10 However, the quality of the heterojunction is one of the major obstacles toward the experimental demonstration of high-performance LH-FETs. The possibility of fabricating LHs by modulating the stacking order of a single 2D material provides the opportunity of perfect lattice matching and growth compatibility and therefore a chance to obtain high material quality.11

Recently, a particular group of transition-metal dichalcogenides (TMDs) involving noble transition metals (Pt, Pd, and Ni), combined with S, Se, and Te, have been predicted12 and demonstrated to have strong gap dependence on the number of stacked layers.13 The so-called “noble TMDs” are, thus, promising contenders to build 2D LHs by modulation of the number of layers of adjacent regions of the same material. Indeed, these structures based on noble TMDs, which strictly speaking could be considered homostructures instead of heterostructures, would be easier to realize than those made of different 2D materials. Ab initio calculations predict that the bandgap is reduced by more than 1 eV when these noble TMDs vary from monolayer (1L) to bilayer (2L), leading in some cases to a change of electronic phase from semiconductor to metal.12,14 Monolayer and few-layer PtS2 and PtSe2 have already been synthesized,15−17 and devices such as Schottky barrier diodes on silicon have been fabricated.18 More recently, FETs made of few-layer PdSe2 and PtSe2 have been experimentally realized showing ambipolar transfer characteristics,13,19,20 and a large dependence of PtSe2 conductance on the number of layers has been observed.13

There is an additional advantage of some noble TMDs in their bilayer form: Their density of states (DOS) exhibits a steep nonmonotonic variation around the Fermi energy that can be used as an energy filtering mechanism in order to obtain a subthreshold swing (SS) of the FET smaller than the Boltzmann limit of 60 mV/decade at room temperature. Indeed, in thermionic FETs, the inverse of the maximum slope of the current–voltage characteristics is limited to SS = kBT/q ln(10) per decade, where kB is Boltzmann constant, q is the elementary charge, and T is the absolute temperature.21−23 This provides a room-temperature SS value of 60 mV/decade. A lower value can only be obtained if (1) injection is energy constrained, such as in a Tunnel FET24,25 or using impact ionization26 or (2) if an effective negative capacitance is realized in the gate oxide stack, thus amplifying the surface potential at the channel.27,28 In particular, the energy-constrained injection from a steep DOS source has been demonstrated very recently using a graphene source in combination with a CNT channel in ref (21) or a MoS2 channel in refs (22 and 23). We show here that this effect can be achieved in a system based on a single 2D material, specifically PdS2, where a bilayer source (injecting into a monolayer channel) can provide sufficient energy filtering to yield an SS below the Boltzmann limit.

In this work we investigate the potential of noble TMDs as channel materials for LH-FETs, showing the possibility to engineer an energy-filtering source in order to obtain sub-60 mV/dec SS at room temperature and to design devices with competitive figures of merit when compared to the predictions of the International Roadmap for Devices and Systems (IRDS).29 Finally, we show that noble TMDs enable the realization of a 2D resonant tunneling diode (RTD) based on LHs obtained with modulation of the number of atomic layers.

Results and discussion

Lateral Heterostructure FETs

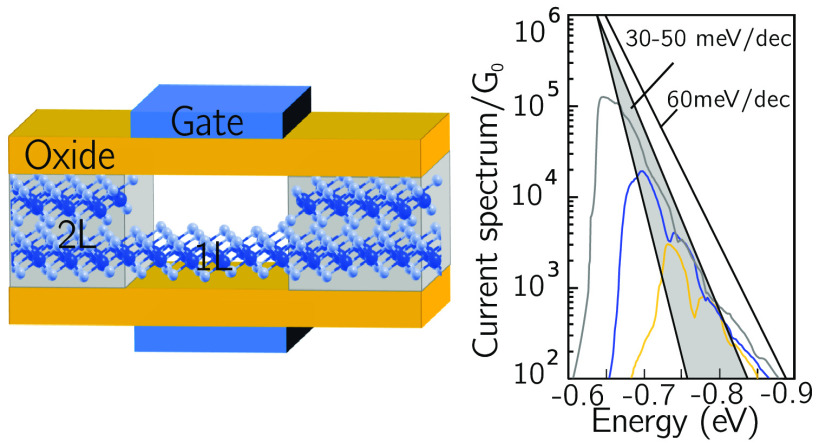

We have selected those noble TMDs exhibiting a sharp nonmonotonic DOS around the Fermi level and therefore potentially able to achieve SS < 60 mV/decade at room temperature. Following bandstructure calculations available in the literature,11,14 we have opted for PdS2 and NiS2. Both materials are semimetal in bilayer form and semiconductors in monolayer form, so it is possible to build a FET with a lateral heterostructure formed by a bilayer source, a monolayer central channel region, and a bilayer drain. This results in two semimetal–semiconductor Schottky barriers at the source and drain ends. For the sake of clarity, a semimetal is a material with zero gap but a relatively low DOS around the Fermi energy. We have also considered PtS2 which presents a strong modulation of the bandgap from monolayer to bilayer, still maintaining a semiconducting gap.

We have adopted a multiscale simulation approach combining different levels of physical abstraction, ranging from ab initio calculations of materials properties to full device simulations based on coherent quantum transport.30 We have calculated the electronic band-structure of monolayer and bilayer PdS2, PtS2, and NiS2 using density functional theory (DFT) as implemented in the Quantum Espresso suite31 (see Methods). The strong dependence of the electronic structure on the number of layers is highlighted in Figure 1a: When the crystal structure is varied from monolayer to bilayer, PdS2 and NiS2 undergo a phase change from semiconductor to semimetal, whereas PtS2 has its energy gap reduced from 1.59 to 0.48 eV. The drastic variation of the DOS of bilayer PdS2 and NiS2 around the Fermi level can be exploited to inject carriers from the source with submaxwellian energy tails, leading to SS < 60 mV/decade at room temperature.

Figure 1.

(a) Electronic band structure on a highly symmetric path along the Brillouin zone (depicted aside in gray with the path marked in red), and DOS integrated in the whole Brillouin zone, as computed with DFT, for monolayer (1L) and bilayer (2L) PdS2, NiS2, and PtS2. (b) Schematic representation of the construction of the lateral heterostructure Hamiltonian from the Hamiltonian of the bilayer and monolayer materials. (c) Schematic of the LH-FET, with bilayer source, monolayer channel, and bilayer-drain. (d) Illustration of the energy band edge profile of the PdS2 and NiS2 LH-FETs and (e) band edge profile of PtS2 LH-FET.

The plane-wave DFT basis set has been translated into a maximally localized Wannier functions (MLWFs) basis set by means of the Wannier90 code,32 which provides us with tight-binding (TB) Hamiltonians for every material and stacking (see Methods and Figure S1 in the Supporting Information). The TB Hamiltonians are then employed to build a total Hamiltonian of the lateral heterostructure devices, following the procedure developed and validated in ref (33) (Figure 1b and Methods). In order to accurately model the Schottky barrier formed at the bilayer/monolayer interfaces, we have performed an energy analysis from first-principles taking into account the band offsets and the formation of dipoles34 (see Supporting Information).

The considered LH-FETs are also illustrated in Figure 1c. The length of the bilayer source and drain regions are Ls/d = 11, 10.4, and 16.7 nm for PdS2, NiS2, and PtS2 respectively. They are assumed to be ohmically contacted by the external metal leads with work functions of 5.6 and 5.8 eV for PdS2 and NiS2, respectively, and 5.3 eV/6.0 eV for the n-type/p-type PtS2. The monolayer 2D channel, with length Lch, is embedded in top and bottom SiO2, with thickness tox = 0.5 nm.

Sketches of the band-edge profiles of the PdS2 and NiS2 LH-FETs with semimetal source and drain are shown in Figure 1d; the PtS2 LH-FET with small gap source and drain is shown in Figure 1e. The complete MLWF Hamiltonian describing the channel including source and drain regions feeds the open-boundary Schrödinger equation, within the non-equilibrium Green’s functions (NEGF)35 formalism, that is self-consistently solved with the electrostatics of the whole device (see Methods).36,37

In order to study the potential performance of the considered LH-FETs for logic applications, we set a supply voltage Vdd = 0.5 V, and we simulate the transfer characteristics for a drain-to-source voltage VDS = Vdd. Those are shown in Figure 2 in semilogarithmic scale for channel lengths ranging from Lch ≃ 5 nm up to Lch ≃ 10 nm and for the three different materials. As it can be seen, the bilayer metallic source/drain regions in PdS2 and NiS2 lead to an ambipolar behavior. For channel lengths longer than 10 nm, Ioff is not further reduced, being the ambipolarity determined by the bandgap of the monolayer channel and the capability of the bilayer source to inject both kinds of carriers. In this regard, some improvement might be achieved following the back-gate over/underlapping strategy at the source/drain discussed in ref (38). Here we have tuned the gate workfunction in the PdS2 and NiS2 devices to 5.52 eV so to observe the crossover between n-type and p-type conduction at VGS = 0 V.

Figure 2.

Transfer characteristic in semilogarithmic scale for the LH-FETs with PdS2 (a), NiS2 (b), and p-type/n-type PtS2 (c)/(d) considering a channel length ranging from ≃5 nm up to ≃10 nm and drain-to-source voltage |VDS| = 0.5 V. In the case of PdS2 and NiS2, an ambipolar behavior is observed due to the semimetallic source and drain. In the case of PtS2, we consider both the nFET and the pFET. The channel is always undoped. A metal gate workfunction of 5.52 eV is assumed in the PdS2 and NiS2 devices to observe the crossover between n-type and p-type conduction at VGS = 0 V. For the PtS2 nFET and pFET, the gate workfunction is tuned to 5.28 and 6.2 eV, respectively, to set Ioff = 100 nA/μm at VGS = 0 V.

The PtS2 LH-FET is not ambipolar since it has semiconductor source and drain. In this case we show in Figure 2c,d both the nFET and the pFET characteristics, where the gate workfunction is tuned to 5.28 and 6.2 eV, respectively, to obtain the current in the OFF state Ioff = 100 nA/μm at VGS = 0 V, as required by the IRDS29 for high-performance (HP) applications where the OFF state corresponds to VGS = 0 V and VDS= ±Vdd. The source and drain regions have a donor doping with molar fraction ND = 4.1 × 10–2 in the case of nFET and acceptor molar fraction NA = 9.5 × 10–2 in the case of pFET. The channel is undoped for all devices.

Interestingly, the p-type branch of the PdS2 LH-FET IDS–VGS curve exhibits a submaxwellian SS down to 52 mV/decade, as shown in Figure 3a. The possibility to achieve sub-60 mV/decade SS in a thermionic FET has been a subject of debate.39,40 In particular, in ref (40) the authors argue that the 60 mV/decade limit cannot be beaten in a single barrier device, although they eventually conclude that the role of the DOS can be essential to reverse this situation, as has already been experimentally demonstrated in the case of a graphene source.21

Figure 3.

SS, Ion/Ioff, τ, and PDP as a function of the channel length, Lch, for the LH-FETs based on PdS2, PtS2, and NiS2, evaluated according to the IRDS requirements for high-performance applications: Ioff = 100 nA/μm.

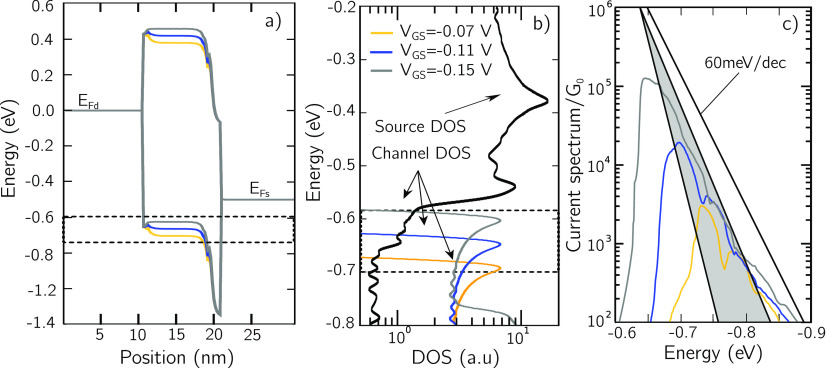

We can discuss the specific mechanism in the PdS2 LH-FET by considering the band edge profiles shown in Figure 4a for VDS = Vdd and for three different values of VGS in the subthreshold region of the p-type branch. The Schottky barriers of drain–channel and source–channel junctions are calculated from first principles (see Supporting Information). A variation of VGS modulates both the conduction and valence band edges in the channel and the transparency of the Schottky barrier between source and channel. The drop of the DOS in the source for energy below the source Fermi level (corresponding to −0.5 eV for the considered bias point) is clearly visible in Figure 4b, where the DOS is obtained from refined calculations applying, for visualization purposes, a Gaussian smoothing with σ = 10 meV (see Supporting Information), and is responsible for a sharper energy filtering than that provided by the Maxwell–Boltzmann tail of the occupation factor, and therefore for an SS lower than the so-called Boltzmann limit. This is even more apparent by considering the energy spectrum of the current, that is, the current density per unit energy, for different values of VGS shown in Figure 4c. The slope of the logarithm of the current spectrum as a function of energy would be exactly −1/(kBT) for a constant DOS, corresponding to one decade every 60 meV at room temperature. Due to the nonconstant DOS in the source, such a slope is however not constant, and in one decade around an energy of −0.7 eV, where the DOS is dramatically quenched, it is in the range of 30–50 meV, marked as a shaded region in Figure 4c. This more confined current spectrum is responsible for the sub-Maxwellian subthreshold swing of the p-type branch transfer characteristics of the PdS2 LH-FET.

Figure 4.

(a) Conduction and valence band edge profiles of the PdS2 LH-FET for VDS = −Vdd and three different values of VGS = −0.07, −0.11, and −0.15 V in the subthreshold region of the p-branch. (b) DOS of the source and of the channel for the corresponding values of VGS obtained in a dense k-mesh grid, see Supporting Information, and after a Gaussian smoothing for the energy integration with σ = 10 meV. (c) Current spectrum as a function of energy. The range of slopes between 30 mV/decade and 50 mV/decade is in the shaded gray. The 60 mV/decade Boltzmann limit is also plotted.

Energy filtering is not observed in the n-branch because the DOS of the conduction band states in PdS2 do not show a similar steep transition (see Supporting Information for more details). The effect is not observed in NiS2 where the small gap of the monolayer semiconductor results in large interband tunneling currents and very poor SS (above 200 meV/decade and therefore not shown in Figure 3a). The PtS2 LH-FET has a close to ideal Maxwellian SS of 60 mV/decade for HP applications due to the dominant Fermi window tail that restricts the SS.

Other transistor figures of merit for digital electronics are considered in Figure 3 following the IRDS specifications for HP applications. In particular, Figure 3b shows Ion/Ioff ratio, where Ion is the drain current in the ON state, corresponding to VGS = VDS = ±Vdd and Ioff = 100 nA/μm, is the current in the OFF state as defined by the IRDS for HP. To this purpose, the PdS2 LH-FET exhibits the highest Ion/Ioff ratio for channel length close to 10 nm thanks to the lower SS just discussed, but not for shorter channel lengths (down to 5 nm), because of the high Ioff due to ambipolarity and large source-to-drain tunneling. The situation is worse for the NiS2 LH-FET: Its smaller monolayer bandgap (0.47 eV) leads to a very poor Ion/Ioff ratio. The PtS2 LH-FET, instead, has a semiconducting bandgap and negligible source-to-drain tunneling and therefore exhibits high Ion/Ioff ratio for Lch down to 5 nm.

Relevant figures of merit for transistor performance in digital circuits are also the intrinsic delay time τ = (Qon – Qoff)/Ion and the power delay product (PDP) = VddτIon, where Qon and Qoff are the total mobile charge in the channel in the ON and OFF states, respectively (Figure 3c,d). The nFETs based on PdS2 and PtS2 exhibit expected τ and PDP compliant with IRDS requirements for next technology nodes,10,29 together with an Ion/Ioff ratio close to 104 for channel lengths of at least 10 nm, which implies acceptable stand-by power consumption for HP applications.29 The pFETs have slightly worse PDP and τ than the nFETs, due to the smaller source DOS in the valence band, apparent in Figure 1a, which is responsible for a smaller Ion, as can be seen in the asymmetric transfer characteristics of Figure 2.

While the ambipolarity of PdS2 and NiS2 FETs spoils their use in low-power (LP) applications, PtS2 FETs also satisfy the IRDS requirements to this purpose (i.e., they reach an Ioff = 100 pA/μm) achieving Ion/Ioff ratios above 106 and 105 for n-type and p-type FETs, respectively (see Supporting Information). For low stand-by power, SS is spoiled in shorter channel lengths since the tunneling current becomes comparable to the pursued Ioff: For Lch ≈ 5–8 nm it is in the range 80–100 mV/decade for nFETs and 70–90 mV/decade for pFETs, deviating considerably from the 60 mV/decade observed in longer channels. Finally, the PDP is slightly lower and the intrinsic delay time slightly higher than the values obtained for HP (see Supporting Information for details).

Resonant Tunneling Diode

Finally, we have studied the operation of a 2D resonant tunneling diode based on a PtS2 LH (LH-RTD). We have considered bilayer PtS2 drain and source regions with a length of 11.2 nm. Two monolayer regions act as energy barriers confining a bilayer well. The barrier length is Lb = 1.9 nm, and the length of the well Lw is varied from 1.9 nm up to 5.6 nm. The whole 2D channel is embedded in SiO2. Figure 5a shows the IDSvsVDS characteristics for Lw = 1.9 nm at room temperature. The current has a clear nonmonotonic behavior exhibiting a pronounced negative differential resistance, due to resonant tunneling through quantized states in the 2D well. The local DOS in the channel is plotted in Figure 5b as a function of energy and of position along the device length (y) for VDS = 0.25 and 0.5 V, corresponding to the main peak and to the valley of the current–voltage characteristics. Let us stress the fact that the bandstructure of different regions is fully considered in the calculation, but inelastic processes and heterojunction defects are not included.

Figure 5.

(a) IDSvsVDS characteristic of the LH-RTD based on PtS2 with Lw = 1.9 nm. Inset: Schematic of the LH-RTD. (b) Local DOS as a function of the energy and the position along the device length and current-density spectrum, normalized to the conductance quantum (G0 = 2q2/ℏ), for the RTD with a Lw = 1.9 nm, and for VDS = 0.25 and 0.5 V. (c) Current–voltage characteristics of the LH-RTD for different well lengths.

The Fermi level at the source (μs) and drain (μd) leads are marked. We have superimposed the conduction and valence band profiles to the local DOS colormaps. The alignment of μs with these quantized energy levels results in resonances in the current spectrum density and is controlled by VDS. We have also explored different well lengths: Lw = 1.9, 3.7, and 5.6 nm (Figure 5c), observing that the NDR effect is preserved, although the position of the peak varies with the well length as so does the energy quantization, while the position of the valley is not modified as it depends on the height of the barrier limiting the thermionic emission.

Conclusion

We have shown that the strong dependence of the bandgap upon the number of layers of noble TMDs can be used to devise electron devices based on transport through lateral heterostructures of TMDs, such as LH-FETs and LH-RTDs. We have used ab initio multiscale simulations to demonstrate that LH-FETs based on PdS2 and PtS2 can comply with IRDS performance requirements29 for future integrated circuit technology for high-performance digital applications. On the other hand, LH-FETs made of NiS2 cannot meet such requirements, due to the low gap and ambipolar behavior.

We have also predicted the steep (submaxwellian) subthreshold behavior of p-type FETs based on PdS, due to the asymmetry of the bilayer PdS2 DOS around the Fermi level, achieving SS = 52 mV/decade. The demonstration of this effect in an intrinsic 2D material observed here can be further exploited for device design. It must be noted that in the presence of electron–electron or electron–phonon scattering, the behavior of the studied devices would be degraded with respect to the optimum ballistic condition assumed here, with direct impact on the achieved sub-Boltzmann slope. Moreover, the SS value for PdS2 FETs is not expected to boost the device performance stunningly as compared to the conventional limit. However, and more importantly, the results presented here confirm that the 60 mV/decade limit can be beaten in 2D-based FETs, as it has been proved experimentally in graphene, encouraging the exploration of new 2D materials with sharper DOS and consequently steeper SSs.

Finally, we have also predicted the possibility of using 2D LHs to obtain a resonant tunneling diode, with a pronounced peak-to-valley ratio of the current–voltage characteristics, which is suitable for experimental observation.

Methods

Density functional theory as implemented in Quantum Espresso code has been employed to determine the electronic structure of PdS2, NiS2, and PtS2. The crystal geometry of monolayer and bilayer 2D crystals is characterized by a 1T arrangement, with a layer of Pt/Pd/Ni atoms sandwiched between two atomic layers of S atoms. The atom coordinates and lattice vectors have been obtained after,14 where a structural optimization of the unitary cell was performed. We have considered 40 Å of vacuum in the direction orthogonal to the 2D layers to minimize spurious interactions between periodic repetitions of the cell. For the exchange–correlation functional, the local density approximation has been considered under the Perdew–Zunger41 parametrization within norm-conserving pseudopotentials. The energy cutoffs for charge density and wave function expansions have been set to 360 and 60 Ry, respectively. A Monkhorst–Pack 10 × 5 × 1 k-mesh has been used for the Brillouin-zone integration, and an energy convergence threshold of 10–6 eV in the iterative solution of the Kohn–Sham equations was ensured. Additionally, an analysis of the Schottky barriers formed at the 2L/1L heterojunction has been performed (see Supporting Information).

Maximally localized Wannier functions (MLWFs) have been obtained by means of the Wannier90 code32 for every material and stacking. For the change of basis, the same k-sampling of the Brillouin zone as in the DFT simulations has been used to compute the overlap matrices required to determine the MLWFs. Twelve bands around the fundamental gap have been considered, and a threshold of 10–10 Å has been set for the total spread change in the MLWFs in 20 consecutive iterations. The MLWFs band structures have been calculated along the same path as in DFT, showing very good agreement (see Supporting Information Figure S1). The MLWF Hamiltonians of the 1L and 2L regions have been employed to build the total Hamiltonian of the lateral heterostructure following the procedure presented in ref (33).

The device simulations consist of the self-consistent solution of the open-boundary Schrödinger equation, within the non-equilibrium Green’s functions (NEGF)35 formalism, and the Poisson equation, for which we have used the open-source code NanoTCAD ViDES.36,37 The construction of the Hamiltonian of the heterostructure from the Hamiltonians of the different regions/materials requires a careful treatment, with special attention to the mixing of the interface elements. We have followed the procedure we developed and validated in ref (33). In particular, the off-diagonal elements connecting the 1L and 2L regions and determining their coupling have been assumed to be equal to those of the monolayer region. We have tested different alternatives for the off-diagonal coupling elements at the interface (see Supporting Information) observing little variation in the device behavior. This mixing procedure provides the best results in terms of robustness in the convergence, preserving computational accuracy as compared to ab initio simulations. For all devices we have considered operation at temperature of 300 K.

Acknowledgments

Authors gratefully acknowledge the support from the European Commission through the Graphene Flagship Core 2 (contract no. 785219) and through the QUEFORMAL h2020 Project (contract no. 829035), and from the Italian Ministry for Education and Research through the CROSSLAB project and the FIVE2D PRIN Project (2017SRYEJH). E.G.M. also acknowledges Juan de la Cierva Incorporación IJCI-2017-32297 (MINECO/AEI).

Supporting Information Available

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsnano.9b08489.

Additional details on the electronic band structure of monolayer and bilayer PtS2, PdS2, and NiS2 and on the Hamiltonian construction as well as the current spectrum for the PdS2 LH-FET (PDF)

The authors declare no competing financial interest.

Supplementary Material

References

- Kroemer H. Nobel Lecture: Quasielectric Fields and Band Offsets: Teaching Electrons New Tricks. Rev. Mod. Phys. 2001, 73, 783–793. 10.1103/RevModPhys.73.783. [DOI] [PubMed] [Google Scholar]

- van der Ziel J. P.; Dingle R.; Miller R. C.; Wiegmann W.; Nordland W. A. Laser Oscillation from Quantum States in very Thin GaAs-Al0.2 Ga0.8 As Multilayer Structures. Appl. Phys. Lett. 1975, 26, 463–465. 10.1063/1.88211. [DOI] [Google Scholar]

- Mimura T.; Hiyamizu S.; Fujii T.; Nanbu K. A New Field-Effect Transistor with Selectively Doped GaAs/n-AlxGa1–xAs Heterojunctions. Jpn. J. Appl. Phys. 1980, 19, L225–L227. 10.1143/JJAP.19.L225. [DOI] [Google Scholar]

- Geim A. K.; Grigorieva I. V. Van der Waals Heterostructures. Nature 2013, 499, 419. 10.1038/nature12385. [DOI] [PubMed] [Google Scholar]

- Novoselov K. S.; Mishchenko A.; Carvalho A.; Castro Neto A. H. 2D Materials and van der Waals Heterostructures. Science 2016, 353, aac9439. 10.1126/science.aac9439. [DOI] [PubMed] [Google Scholar]

- Ci L.; Song L.; Jin C.; Jariwala D.; Wu D.; Li Y.; Srivastava A.; Wang Z. F.; Storr K.; Balicas L.; Liu F.; Ajayan P. M. Atomic Layers of Hybridized Boron Nitride and Graphene Domains. Nat. Mater. 2010, 9, 430. 10.1038/nmat2711. [DOI] [PubMed] [Google Scholar]

- Levendorf M. P.; Kim C.-J.; Brown L.; Huang P. Y.; Havener R. W.; Muller D. A.; Park J. Graphene and Boron Nitride Lateral Heterostructures for Atomically Thin Circuitry. Nature 2012, 488, 627. 10.1038/nature11408. [DOI] [PubMed] [Google Scholar]

- Liu Z.; Ma L.; Shi G.; Zhou W.; Gong Y.; Lei S.; Yang X.; Zhang J.; Yu J.; Hackenberg K. P.; Babakhani A.; Idrobo J.-C.; Vajtai R.; Lou J.; Ajayan P. M. In-Plane Heterostructures of Graphene and Hexagonal Boron Nitride with Controlled Domain Sizes. Nat. Nanotechnol. 2013, 8, 119. 10.1038/nnano.2012.256. [DOI] [PubMed] [Google Scholar]

- Huang C.; Wu S.; Sanchez A. M.; Peters J. J.; Beanland R.; Ross J. S.; Rivera P.; Yao W.; Cobden D. H.; Xu X. Lateral Heterojunctions within Monolayer MoSe2–WSe2 Semiconductors. Nat. Mater. 2014, 13, 1096. 10.1038/nmat4064. [DOI] [PubMed] [Google Scholar]

- Iannaccone G.; Bonaccorso F.; Colombo L.; Fiori G. Quantum Engineering of Transistors Based on 2D Materials Heterostructures. Nat. Nanotechnol. 2018, 13, 183–191. 10.1038/s41565-018-0082-6. [DOI] [PubMed] [Google Scholar]

- Ghorbani-Asl M.; Kuc A.; Miro P.; Heine T. A Single-Material Logical Junction Based on 2D Crystal PdS2. Adv. Mater. 2016, 28, 853–856. 10.1002/adma.201504274. [DOI] [PubMed] [Google Scholar]

- Wang Y.; Li Y.; Chen Z. Not Your Familiar Two Dimensional Transition Metal Disulfide: Structural and Electronic Properties of the PdS2 Monolayer. J. Mater. Chem. C 2015, 3, 9603–9608. 10.1039/C5TC01345C. [DOI] [Google Scholar]

- Ciarrocchi A.; Avsar A.; Ovchinnikov D.; Kis A. Thickness-Modulated Metal-To-Semiconductor Transformation in a Transition Metal Dichalcogenide. Nat. Commun. 2018, 9, 919. 10.1038/s41467-018-03436-0. [DOI] [PMC free article] [PubMed] [Google Scholar]

- Miro P.; Ghorbani-Asl M.; Heine T. Two Dimensional Materials Beyond MoS2: Noble-Transition-Metal Dichalcogenides. Angew. Chem., Int. Ed. 2014, 53, 3015–3018. 10.1002/anie.201309280. [DOI] [PubMed] [Google Scholar]

- Zhao Y.; Qiao J.; Yu P.; Hu Z.; Lin Z.; Lau S. P.; Liu Z.; Ji W.; Chai Y. Extraordinarily Strong Interlayer Interaction in 2D Layered PtS2. Adv. Mater. 2016, 28, 2399–2407. 10.1002/adma.201504572. [DOI] [PubMed] [Google Scholar]

- Wang Y.; Li L.; Yao W.; Song S.; Sun J. T.; Pan J.; Ren X.; Li C.; Okunishi E.; Wang Y.-Q.; Wang E.; Shao Y.; Zhang Y. Y.; Yang H.-t.; Schwier E. F.; Iwasawa H.; Shimada K.; Taniguchi M.; Cheng Z.; Zhou S.; et al. Monolayer PtSe2, a New Semiconducting Transition-Metal-Dichalcogenide, Epitaxially Grown by Direct Selenization of Pt. Nano Lett. 2015, 15, 4013–4018. 10.1021/acs.nanolett.5b00964. [DOI] [PubMed] [Google Scholar]

- Yan M.; Wang E.; Zhou X.; Zhang G.; Zhang H.; Zhang K.; Yao W.; Lu N.; Yang S.; Wu S.; Yoshikawa T.; Miyamoto K.; Okuda T.; Wu Y.; Yu P.; Duan W.; Zhou S. High Quality Atomically Thin PtSe2 Films Grown by Molecular Beam Epitaxy. 2D Mater. 2017, 4, 045015. 10.1088/2053-1583/aa8919. [DOI] [Google Scholar]

- Yim C.; Lee K.; McEvoy N.; O’Brien M.; Riazimehr S.; Berner N. C.; Cullen C. P.; Kotakoski J.; Meyer J. C.; Lemme M. C.; Duesberg G. S. High-Performance Hybrid Electronic Devices from Layered PtSe2 Films Grown at Low Temperature. ACS Nano 2016, 10, 9550–9558. 10.1021/acsnano.6b04898. [DOI] [PubMed] [Google Scholar]

- Chow W. L.; Yu P.; Liu F.; Hong J.; Wang X.; Zeng Q.; Hsu C.-H.; Zhu C.; Zhou J.; Wang X.; Xia J.; Yan J.; Chen Y.; Wu D.; Yu T.; Shen Z.; Lin H.; Jin C.; Tay B. K.; Liu Z. High Mobility 2D Palladium Diselenide Field-Effect Transistors with Tunable Ambipolar Characteristics. Adv. Mater. 2017, 29, 1602969. 10.1002/adma.201602969. [DOI] [PubMed] [Google Scholar]

- Zhao Y.; Qiao J.; Yu Z.; Yu P.; Xu K.; Lau S. P.; Zhou W.; Liu Z.; Wang X.; Ji W.; Chai Y. High-Electron-Mobility and Air-Stable 2D Layered PtSe2 FETs. Adv. Mater. 2017, 29, 1604230. 10.1002/adma.201604230. [DOI] [PubMed] [Google Scholar]

- Qiu C.; Liu F.; Xu L.; Deng B.; Xiao M.; Si J.; Lin L.; Zhang Z.; Wang J.; Guo H.; Peng H.; Peng L.-M. Dirac-Source Field-Effect Transistors as Energy-Efficient, High-Performance Electronic Switches. Science 2018, 361, 387–392. 10.1126/science.aap9195. [DOI] [PubMed] [Google Scholar]

- Liu F.; Qiu C.; Zhang Z.; Peng L.; Wang J.; Guo H. Dirac Electrons at the Source: Breaking the 60-mV/Decade Switching Limit. IEEE Trans. Electron Devices 2018, 65, 2736–2743. 10.1109/TED.2018.2836387. [DOI] [Google Scholar]

- Logoteta D.; Pala M. G.; Choukroun J.; Dollfus P.; Iannaccone G. A Steep-Slope MoS2-Nanoribbon MOSFET Based on an Intrinsic Cold-Contact Effect. IEEE Electron Device Lett. 2019, 40, 1550–1553. 10.1109/LED.2019.2928131. [DOI] [Google Scholar]

- Appenzeller J.; Lin Y.-M.; Knoch J.; Avouris P. Band-To-Band Tunneling in Carbon Nanotube Field-Effect Transistors. Phys. Rev. Lett. 2004, 93, 196805. 10.1103/PhysRevLett.93.196805. [DOI] [PubMed] [Google Scholar]

- Seabaugh A. C.; Zhang Q. Low-Voltage Tunnel Transistors for Beyond CMOS Logic. Proc. IEEE 2010, 98, 2095–2110. 10.1109/JPROC.2010.2070470. [DOI] [Google Scholar]

- Gopalakrishnan K.; Griffin P. B.; Plummer J. D. I-MOS: A Novel Semiconductor Device with a Subthreshold Slope Lower Than kT/q. IEEE Int. Electron Devices Meet., Technol. Dig. 2002, 289–292. 10.1109/IEDM.2002.1175835. [DOI] [Google Scholar]

- Salahuddin S.; Datta S. Use of Negative Capacitance to Provide Voltage Amplification for Low Power Nanoscale Devices. Nano Lett. 2008, 8, 405–410. 10.1021/nl071804g. [DOI] [PubMed] [Google Scholar]

- Salvatore G. A.; Bouvet D.; Ionescu A. M. Demonstration of Subthrehold Swing Smaller Than 60mV/Decade in Fe-FET with P (VDF-TrFE)/SiO2 Gate Stack. IEEE Int. Electron Devices Meet., Technol. Dig. 2008, 1–4. 10.1109/IEDM.2008.4796642. [DOI] [Google Scholar]

- International Roadmap for Devices and Systems,, 2018 edition. https://irds.ieee.org/editions/2018 (accessed May 20, 2019).

- Marin E. G.; Perucchini M.; Marian D.; Iannaccone G.; Fiori G. Modeling of Electron Devices Based on 2-D Materials. IEEE Trans. Electron Devices 2018, 65, 4167–4179. 10.1109/TED.2018.2854902. [DOI] [Google Scholar]

- Giannozzi P.; Baroni S.; Bonini N.; Calandra M.; Car R.; Cavazzoni C.; Ceresoli D.; Chiarotti G. L.; Cococcioni M.; Dabo I.; Dal Corso A.; de Gironcoli S.; Fabris S.; Fratesi G.; Gebauer R.; Gerstmann U.; Gougoussis C.; Kokalj A.; Lazzeri M.; Martin-Samos L.; et al. QUANTUM ESPRESSO: A Modular and Open-Source Software Project for Quantum Simulations of Materials. J. Phys.: Condens. Matter 2009, 21, 395502. 10.1088/0953-8984/21/39/395502. [DOI] [PubMed] [Google Scholar]

- Marzari N.; Mostofi A. A.; Yates J. R.; Souza I.; Vanderbilt D. Maximally Localized Wannier Functions: Theory and Applications. Rev. Mod. Phys. 2012, 84, 1419–1475. 10.1103/RevModPhys.84.1419. [DOI] [Google Scholar]

- Marian D.; Dib E.; Cusati T.; Marin E. G.; Fortunelli A.; Iannaccone G.; Fiori G. Transistor Concepts Based on Lateral Heterostructures of Metallic and Semiconducting Phases of MoS2. Phys. Rev. Appl. 2017, 8, 054047. 10.1103/PhysRevApplied.8.054047. [DOI] [Google Scholar]

- Katagiri Y.; Nakamura T.; Ishii A.; Ohata C.; Hasegawa M.; Katsumoto S.; Cusati T.; Fortunelli A.; Iannaccone G.; Fiori G.; Roche S.; Haruyama J. Gate-Tunable Atomically Thin Lateral MoS2 Schottky Junction Patterned by Electron Beam. Nano Lett. 2016, 16, 3788–3794. 10.1021/acs.nanolett.6b01186. [DOI] [PubMed] [Google Scholar]

- Datta S. Nanoscale Device Modeling: The Green’s Function Method. Superlattices Microstruct. 2000, 28, 253–278. 10.1006/spmi.2000.0920. [DOI] [Google Scholar]

- Bruzzone S.; Iannaccone G.; Marzari N.; Fiori G. An Open-Source Multiscale Framework for the Simulation of Nanoscale Devices. IEEE Trans. Electron Devices 2014, 61, 48–53. 10.1109/TED.2013.2291909. [DOI] [Google Scholar]

- NanoTCAD ViDES. http://vides.nanotcad.com/vides/ (accessed May 20, 2019).

- Wu P.; Appenzeller J. High Performance Complementary Black Phosphorus FETs and Inverter Circuits Operating at Record-Low VDD Down to 0.2 V. Proc. Device Res. Conf. 2018, 76th, 1–2. 10.1109/DRC.2018.8442224. [DOI] [Google Scholar]

- Cheung K. P. On the 60 mV/dec @300 K Limit for MOSFET Subthreshold Swing. Int. Symp. VLSI Technol., Syst., Appl., Proc. Technol. Pap. 2010, 72–73. 10.1109/VTSA.2010.5488941. [DOI] [Google Scholar]

- Solomon P. M. Inability of Single Carrier Tunneling Barriers to Give Subthermal Subthreshold Swings in MOSFETs. IEEE Electron Device Lett. 2010, 31, 618–620. 10.1109/LED.2010.2046713. [DOI] [Google Scholar]

- Perdew J. P.; Zunger A. Self-Interaction Correction to Density-Functional Approximations for Many-Electron Systems. Phys. Rev. B: Condens. Matter Mater. Phys. 1981, 23, 5048–5079. 10.1103/PhysRevB.23.5048. [DOI] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.