Abstract

The potentialities of silicon as a starting material for electronic devices are well known and largely exploited, driving the worldwide spreading of integrated circuits. When nanostructured, silicon is also an excellent material for thermoelectric applications, and hence it could give a significant contribution in the fundamental fields of energy micro-harvesting (scavenging) and macro-harvesting. On the basis of recently published experimental works, we show that the power factor of silicon is very high in a large temperature range (from room temperature up to 900 K). Combining the high power factor with the reduced thermal conductivity of monocrystalline silicon nanowires and nanostructures, we show that the foreseen figure of merit could be very high, reaching values well above 1 at temperatures around 900 K. We report the best parameters to optimize the thermoelectric properties of silicon nanostructures, in terms of doping concentration and nanowire diameter. At the end, we report some technological processes and solutions for the fabrication of macroscopic thermoelectric devices, based on large numbers of silicon nanowire/nanostructures, showing some fabricated demonstrators.

Keywords: silicon nanowire, thermoelectricity, thermal conductivity, figure of merit

1. Introduction

Thermoeletric devices can convert heat directly into electrical power, and vice versa. They are compact and reliable, because they do not have any moving mechanical parts, and potentially they have a broad range of applications: energy recovery and green energy harvesting; energy micro-harvesting (scavenging) for the capillary supply of small systems, such as sensor nodes for Internet of Things (IoT); powering of systems in remote and harsh environments typical, for example, of spatial exploration; localized and optimized cooling of small systems, where the reliability and the compactness can play a fundamental role. Unfortunately, at the present state of the art, all these potentialities offered by thermoelectric devices [1] (Thermoelectric Generators, TEG, and Thermoelectric Coolers, TEC) are limited by the available materials with thermoelectric properties good enough for an acceptable thermal to electrical conversion efficiency. The parameter expressing the thermoelectric properties of a material is the dimensionless figure of merit , where T is the absolute temperature and , S is the Seebeck coefficient, is the electrical conductivity and is the thermal conductivity. A good thermoelectric material should have as high as possible, that means S and as great as possible, and as low as possible. However, more factors must be taken into account in the evaluation of materials for thermoelectric conversion: (1) Sustainability: devices for green application must be manufacturable with materials that are not toxic or polluting. (2) Availability and costs: wide scale applications need to be based on abundant and cheap materials. (3) Technical feasibility: a material with good transport properties is only a starting point; making a device requires the possibility to tailor the doping concentration, either n and p, to make good electrical contacts and so on. (4) Stability on long times and, in particular, in a large temperature range: for the second principle of thermodynamics, machines for conversion of heat into other energy forms must exploit high temperature differences to achieve high conversion efficiencies. Hence, materials able to maintain good thermoelectric properties on large temperature ranges are required. At the current state of the art, most of the commercial TEG/TEC are based on a tellurium compound, which is a poisoning and a very rare element: its abundancy is less than 0.001 ppm on the Earth’s crust, comparable with that of platinum. Standard TEG/TEC devices, based on bismuth telluride, have good thermoelectric characteristics, with approaching 1, but in a limited temperature range around room temperature. Its thermoelectric properties drop very fast for temperatures over 150 °C. Research is focusing on a large plethora of materials with good thermoelectric properties [2,3]. In this article, we focus on the thermoelectric properties of silicon [4,5]. Silicon satisfies all the points requested for an excellent material for the fabrication of devices, being sustainable, biocompatible, abundant (the Earth’s crust is essentially made of silicon). It can be said that silicon is the most investigated material ever, because of its large use in the microelectronic industry. A huge amount of data is available about doping processes and electrical conductivity; there are many studies on interfaces between silicon and a large range of materials, for the fabrication of contacts, and so on. The key point is the nanostructuration of silicon: silicon nanowires showed a thermal conductivity as small as 2 W/(m K). This overcomes the Achilles heel of silicon for thermoelectric applications, that is its high thermal conductivity: in its bulk form, for silicon is 148 W/(m K). Combined with the high power factor value, this strong reduction of the thermal conductivity places silicon in an excellent position as a material with a very high value of . At first, in Section 2, we report the figure of merit of silicon as a function of temperature, achieved by crossing available experimental measurements, and we show that is very high on a large temperature range if the correct parameters (doping concentration and nanowire size) are chosen. The price to be payed for the exploitation of these excellent thermoelectric potentialities of silicon is the development of techniques for its nanostructuration, which need to be reliable and low-cost. For this reason, as a second point of our work, in Section 3, we discuss and report some of these techniques, based on standard silicon technologies, and we show some demonstrators that we developed.

2. Thermoelectric Properties of Nanostructured Silicon

2.1. Electrical Conductivity, Seebeck Coefficient and Power Factor

On the basis of available experimental measurements, we evaluate the power factor of silicon as a function of the doping concentration, both n and p, and of the temperature. To this end, we need to extrapolate the electrical conductivity and the Seebeck coefficient.

The electrical conductivity of silicon has been largely investigated in the past, due to the relevance of silicon for the fabrication of integrated circuits. Data on the electrical conductivity as a function of doping concentration and temperature, and for several doping species (Boron, Phosphorous, Arsenic), are largely available. Several semi-empirical models, which give a good fit of conductivity measurements, have been developed. To be mentioned are the Arora’s formulas [6], available both for n and for p doping, and the Masetti’s model [7] in its extended version developed by the group of the University of Bologna [8]. These semi-empirical models of silicon conductivity are very reliable, and they are largely used by several computer aided design (CAD) codes for electron device simulation, such as Synopsis. The electrical conductivity of silicon nanowires can be affected by the surface scattering, in particular for nanowires smaller than 20 nm (see ahead).

The Seebeck coefficient of silicon is not as much investigated as the electrical conductivity. One of the first studies was performed in 1955 by Geballe et al. [9], which reported the Seebeck coefficient for several n and p doping concentrations, for temperature up to 300 K. The Seebeck coefficient of n-doped silicon has been reported by Brinson [10] in 1970 for temperatures in the range 0–300 K. More recently, in 2013, Stranz et al. [11] reported the Seebeck coefficient for n a p heavily doped silicon, for temperatures up to 700 K. Ohishi et al. [12] (2015) reported the electrical conductivity and the Seebeck coefficient for heavily boron and phosphorous doped silicon, for temperatures up to 1000 °C. In 2017, Bennett [13] made a study of the Seebeck coefficient at room temperature, for different n doping species (phosphorous, arsenic and antimony), as a function of the Hall carrier concentration. Given a doping concentration, a rough approximation of the Seebeck coefficient can be achieved with the Stratton formula:

| (1) |

where is the Boltzmann constant, e is the elemental charge, n is the electron density in the conduction band, which, at room temperature, is approximately the doping concentration, and is the equivalent density of states in the conduction band for silicon, m at room temperature. For a better extrapolation of the Seebeck coefficient as a function of the doping concentration, we propose to use a logarithmic fit [14] of the available experimental data.

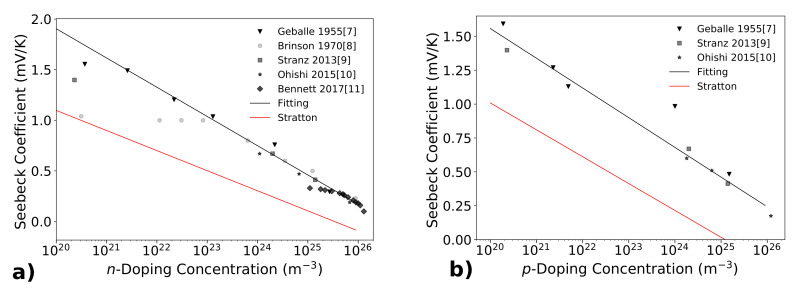

Figure 1a shows the experimental values of the Seebeck coefficient at room temperature for n doped silicon (in absolute value, it is negative for n doping). Data on n doping are reported by Geballe [9], Brinson [10], Stranz [11], Ohishi [12] and Bennett [13]. The best log fit shown in the graph resulted:

| (2) |

where n is the electron concentration in m (International System of Units). The Seebeck coefficient evaluated with the Stratton formula was also reported, which in general gives an underestimation with respect to the experimental data. For p doping, there are less experimental data, reported by Geballe [9], Stranz [15] and Ohishi [12]. These data are reported in Figure 1b, together with the log fit, which resulted as:

| (3) |

Figure 1.

Available experimental data of the Seebeck coefficient are reported both for n-doping (Panel (a)) and for p-doping (Panel (b)). The logarithmic fit (see text) is also shown. The red lines show the Seebeck coefficient calculated with the Stratton formula (both for n and for p doping): experimental measurement give higher values of the Seebeck coefficient. Panel (a) is a modification of the figure published on [14].

The Seebeck coefficient evaluated by means of the Stratton formula is also reported.

The estimation of the Seebeck coefficient through Formulas (2) and (3) can be used for the evaluation of the power factor as a function of doping. In this work, we used the Arora’s formula for the evaluation of .

Figure 2 shows the silicon power factor at 300 K, as a function of the doping concentration, both for n-doped (Panel (a)) and p-doped (Panel (b)) silicon (Panel (a) has been taken from [14] with permission). It is well known that the Seebeck coefficient and the electrical conductivity have an opposite trend with the increasing of doping concentration: the Seebeck coefficient decreases with the doping, meanwhile the electrical conductivity increases. Therefore, the power factor at first increases with the doping, when the weight of the increasing of overcomes that of S, and then decreases for very high doping, where the decreasing of S, which appears squared in the power factor, begins to predominate. As a consequence, the doping concentration must be tailored to get the maximum power factor. For n-doped silicon, at room temperature, the maximum power factor resulted 0.0054 W/mK for a doping concentration m ( cm). For p-doped silicon, the maximum power factor resulted 0.0054 W/mK for a doping concentration m ( cm). These results for the power factor are quite high, comparable and even better of those achieved with the best thermoelectric materials.

Figure 2.

The room temperature power factor is reported as a function of the doping concentration, both for n (Panel (a)) and for p type silicon (Panel (b)). An optimal doping for the maximum power factor is established both for n ( m) and for p ( m) type silicon. Panel (a) has been reprinted from [14] with permission.

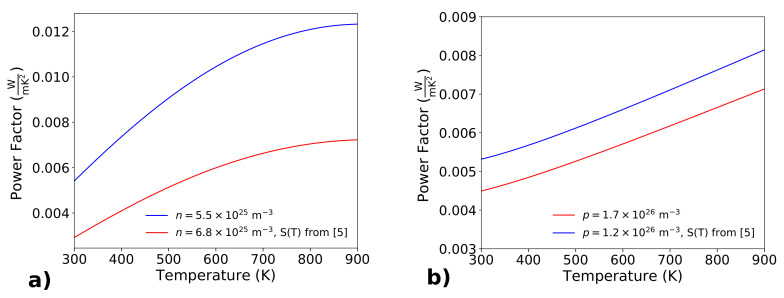

An important evaluation that must be done is the power factor as a function of the temperature, especially for temperatures higher than 300 K, where thermoelectric devices can find useful applications. Most of the semi-empirical formulas for the evaluation of the electrical conductivity, such as the Arora one, gives its dependence on the temperature. Instead, very few data are available for the temperature dependence of the Seebeck coefficient . Geballe [9] reports S in the temperature range 300–1000 K, but for low values of doping concentration (around 10 m). Both Stranz [15] and Ohishi [12] report S for doping concentration between 10 m and 10 m. In particular, Ohishi [12] reports S for and m, for temperatures up to 1000 K. These values are very interesting, because they are very close to those for which both n and p type silicon show the maximum power factor at room temperature. It must be noted that, regarding n type silicon, the increasing of temperature brings an increase of the electrons at higher energies, and hence the absolute value of the Seebeck coefficient increases. This is true up to temperatures for which the concentration of the thermally generated electron-hole pairs becomes comparable with that of the electrons coming from the donor level. A further increasing of the temperature produces a decreasing of the Seebeck coefficient, because the electrical conduction is dominated by a comparable number of electrons and holes, which give an opposite contribution to the Seebeck coefficient. The same behavior can be noticed for p type silicon. This is visible in the graphs of Figure 8 of Geballe [9], where it is shown that S decreases for temperature greater than 500 K, for doping concentration of about 10 m. In Figure 2, Ohishi [12] reports for a few doping concentrations: for doping concentrations of about 10 m, S at first increases, both for n and for p doping, and then S begins to decrease for temperatures higher than 800 K. However, the maximization of the power factor is achieved with very high doping concentrations, above 10 m. For these concentration values, the Seebeck coefficient increases from room temperature to temperatures in excess to 1000 K. As a reference number for the thermally generated electron-hole pairs, we can consider the intrinsic carrier concentration , which is about 10 m at room temperature, and increases to 10 m for K. The temperature must exceed 1400 K to have m. Figure 3 shows the power factor as a function of temperature for n (Panel (a)) and p (Panel (b)) doped silicon, for different values of doping concentrations. In Panel (a), the red curve shows the power factor for m. For this concentration, experimental values for have been made available by Ohishi [12] (see Figure 2). For Figure 3a a parabolic fitting of the Ohishi’s data has been used:

| (4) |

where mV/K, and , . The blue curve shows the power factor for a doping concentration of m, for which it is maximum at room temperature. In the Formula (4) mV/K, evaluated by the Formula (2), has been used; this value is very close to the experimental data of Bennett [13], which measured mV/K for m. For a and b the same values achieved with the doping concentration m have been taken, assuming that they do not change very much for doping concentrations around that number. More experimental measurements should be performed to confirm this assumption. It must be noted that the value of mV/K achieved by Ohishi [12] is not consistent with the fit for S at room temperature (Formula (2)), which gives mV/K for m. >From the curve, we can see that the power factor increases with temperature: from one side the electrical conductivity decreases with temperature for the increasing of the scattering rate; on the other side, S increases with temperature, and it predominates as it appears squared in the power factor. The power factor is W/mK at room temperature, and reaches an astonishing value of W/mK at 900 K. A similar behavior is achieved for p doped silicon (Figure 3b), where together with the values based on the measured for m (red curve), is reported that for m, which maximizes the power factor at room temperature. Furthermore, in the case of p doped silicon, the power factor increases in the temperature range 300–900 K.

Figure 3.

The power factor of n (Panel (a)) and p (Panel (b)) doped silicon is reported as a function of temperature. The blue curves concern the doping concentration, which maximizes the power factor at room temperature, the red curves have been calculated considering experimentally determined by Ohishi [12] for doping concentrations different from that for the maximum power factor.

It must be noted that, even if the power factor of silicon is already quite high, it can be further increased implementing techniques of energy filtering [16,17]. As an example, thanks to energy filtering effects, heavily p-doped bulk nanocrystalline silicon [18,19] showed an increase both of the electrical conductivity and of the Seebeck coefficient.

2.2. Thermal Conductivity and Figure of Merit

The strong reduction of the thermal conductivity in nanostructured materials [20] has been largely demonstrated. In particular, a conductivity smaller than 10 W/(m K) has been reported in 2003 by Li et al. [21] for monocrystalline silicon nanowires smaller than 30 nm. Since that year, many experimental works have been devoted to the measurement of the thermal conductivity together with other thermoelectric parameters of silicon nanowires and nanostructures [14,22,23,24,25,26,27,28,29,30,31,32,33,34,35]. In 2008, two famous works have been published on Nature Letters: both Hockbaum et al. [23] (who used Metal Assisted Chemical Etching for the production of nanowires) and Boukay et al. [36] reported the thermal conductivity of SiNWs; they positioned one, or very few, nanowires on suspended platforms, completed with microfabricated heaters and thermometers, and both of them achieved a thermal conductivity below 2 W/(m K). These results have been confirmed by macroscopic measurements on a huge number of nanowires, organized in vertical forests [29,34,37]: a thermal conductivity of 4.6 W/(m K) [37] has been measured on nanowire forests with low doping values and with an average nanowire diameter around 80 nm; the thermal conductivity resulted as small as 1.7 W/(m K) for heavily doped nanowire forests [34], whose average nanowire diameter is of 40 nm. Several theoretical works [38,39] demonstrated that the enhancement of the phonon scattering, due to the roughness of the nanowire walls, limits the phonon propagation, reducing the thermal conductivity. The phonon mean free path, at room temperature, is of the order of several tens of nanometers, and hence nanowires narrower than 100 nm represent an almost 1D conductor for phonon transport, which can freely move only in one direction. Several experimental works confirmed this strong relation between thermal conductivity reduction, nanowire diameter and surface roughness of nanowires [25,26,27]. In particular, the thermal conductivity of top-down fabricated smooth nanowires, 100 nm wide, resulted as 40 W/(m K) [24]. Lim et al. [27] demonstrated that, in Si nanowires with diameter of about 70 nm, the thermal conductivity drops from more than 20 W/(m K) to less than 2 W/(m K), increasing the surface roughness [27]. For this reason, values of thermal conductivity smaller than 5 W/(m K) have been measured with Si nanowires fabricated by Metal Assisted Chemical Etching [23,30,34,36,37], which produces nanowires with very rough surfaces. Meanwhile, smooth nanowires fabricated by top-down lithography and etching [24] or by CVD [35,40] always showed thermal conductivities of a few tens of W/(m K).

The thermal conductivity of thin monocrystalline silicon membranes, which are silicon structures where one dimension is very small if compared with the other two (almost 2D structures), has also been measured. In this case, we can think of a 2D phonon transport, and the thermal conductivity in the film plane is reduced for the scattering on the top and bottom surfaces of the film. A strong reduction of thermal conductivity has been measured on Si membranes thinner than 200 nm [41,42]. In particular, in our previous paper [42], we demonstrated a strong relationship between thermal conductivity and surface roughness of Si nanomembranes. The surface roughness has been characterized by AFM measurements, and a dedicated 3 technique, applied to suspended nanomembranes, has been used for in-plane thermal conductivity measurements [43]. A thermal conductivity of 17 W/(m K) has been measured on a 120 nm thick Si nanombembranes.

As anticipated by Dresselhaus and co. [44,45], the benefits of nanostructuring consists both in the decreasing of the thermal conductivity and in the increasing of the Seebeck coefficient S. However, nanowires narrower than 5 nm are required for an effective increasing of the Seebeck coefficient [46], and at these dimensions the electrical conductivity is strongly reduced for the scattering of the charged carriers on the nanowire walls [5]. For a good electrical conductivity, comparable to that of bulk silicon, nanowires wider than 30 nm should be considered. On the other hand, a width smaller than 100 nm is sufficient for a strong reduction of the thermal conductivity. In Figure 4, it is shown that the optimal diameter of nanowires/nanostructures for good thermoelectric properties is between 30 nm and 100 nm: for this diameter range, the thermal conductivity can be very small if rough nanowires are fabricated, meanwhile the electrical conductivity and the Seebeck coefficient are very close to those of the bulk silicon.

Figure 4.

The electrical conductivity for m, normalized with respect to the bulk value, is reported as a function of the nanowire width (continuous curve). Furthermore, the experimental measurements of the thermal conductivity (scatters) are reported. For diameters between 30 nm and 100 nm (roughly), the electrical conductivity is comparable with that in the bulk, the thermal conductivity results were instead strongly reduced for sufficiently rough nanowires.

Figure 5 reports the parameter and the figure of merit as a function of temperature T. For the power factor the data of Figure 3, for a doping concentration m, have been used. Different values of the thermal conductivity , which has been considered constant with temperature, have been considered. It has been demonstrated that the thermal conductivity of silicon nanowires decreases with temperature, for temperatures above 300 K [47] up to 700 K. To our knowledge, there are no available data of for temperatures up to 900 K, but it can be assumed that the thermal conductivity further decreases with the increasing of temperature, therefore the data shown in Figure 5 are prudential because they consider constant with temperature. In general, it must be noted that the figure of merit increases with temperature even in the case that does not change with temperature. Hence, the parameter Z (K) is a better indicator of the properties of the material, because an increasing of Z with temperature really demonstrates the goodness of a material for thermoelectric applications. Figure 5a shows the parameter for silicon, for different values of the thermal conductivity . The lower value considered is 2 W/(m K), which is reasonably achievable with rough nanowires. Even intermediate values of 5 or 10 W/(m K) give a high Z value, always increasing with temperature. For comparison with other materials, the parameter is shown on Panel (b). For a thermal conductivity of 2 W/(m K), and for an optimized doping value, we have at room temperature, and an astonishing value of about 5 is achieved at temperatures around 900 K.

Figure 5.

The factor Z (Panel (a)) and the figure of merit (Panel (b)) are reported as a function of temperature, for the optimum thermoelectric doping of n type silicon. Different curves consider different values of the thermal conductivity . The highest values of Z are related to W/(m K), achievable in rough silicon nanowires.

3. Techniques for All-Silicon Thermoelectric Devices

The main issue for the use of silicon in thermoelectric applications is the development of strategies and techniques for the fabrication of a large number of silicon nanowires and nanostructures, to be interconnected in a suitable way for making possible the thermal and electrical transport. Starting from the enormous background of silicon, developed within the last decades to support the world widespread market of electronic circuits, a large variety of nanostructured silicon thermoelectric devices are being investigated and developed, with the possibility to cover both the aspect of energy harvesting on large scale (macroharvesting) and on millimetric/micrometric scale (microharvesting, or scavenging). The main fabrication strategies currently under investigation are [48,49]: (1) the planar strategy, consisting in the fabrication of many Si nanostructures parallel to the silicon substrate. (2) The vertical strategy, which relies on highly selective etching processes for the definition of Si nanowires perpendicular to a silicon substrate.

3.1. On-Chip Si Nanowires/Nanostructures for Energy Scavenging

One of the strengths of silicon thermoelectric nanodevices is that processes for their fabrication can be based on well-assessed integrated circuit fabrication techniques. Micromachining techniques can be used to fabricate nanowires interconnected and placed across microfabricated heat exchangers, to be connected to the hot and cold heat sources. These technologies are suitable for device areas of the order of several millimeters square at maximum, so that they are suitable for microharvesting/energy scavenging. The range of applications is in any case very wide, because on-chip integrated devices can directly produce electrical power from any hot surface, and they could be fabricated side by side with other integrated electronic circuits, providing their supply.

As the typical processes for IC fabrication are planar (electronic devices are fabricated on the surface of a silicon wafer), the best strategy for on-chip thermoelectric devices for energy scavenging is the planar one, also if solutions based on lithography/etching of very short nanowires perpendicular to the silicon substrate have been proposed [50]. The main point of the planar strategy is that it requires the suspension of nanostructures which must interconnect the hot side with the cold side, avoiding any heat conduction through the substrate. Hence, one of the difficult tasks involved with the use of this technique is the connection of these very fragile suspended silicon platforms [51] with the heat sources. On-chip thermoelectric devices can be fabricated by CVD growth (bottom-up approach) of Si, or SiGe, nanowires between a suspended silicon platform, which can be used as hot part of the device, and the body of the chip [52,53,54,55,56] (heat sink, cold part of the device). Millions of nanowires can be simultaneously grown by VLS-CVD [57] through catalyzing gold seeds, deposited by galvanic displacement [58,59]. Therefore, this technique does not require high resolution lithography for the definition of nanowires: it requires only almost standard micromachining techniques, with relaxed lithography, for the fabrication of the platforms and of the electrical contacts. The metal-nanowire electrical contact has been investigated, and very low values of contact resistances have been achieved, by Gaeda and co. [60]. As alternative, suspended silicon platforms can be used to host junction made of polysilicon [61,62] or porous silicon [63].

A possible alternative approach is to define the nanostructures/nanowires by lithography and etching [64,65] (top down approach), using a suitable design to connect silicon platforms, which can be fabricated simultaneously with the nanostructures. The main advantage of this strategy is the high flexibility in the design of the device: nanostructures can be fabricated and positioned in precise positions and configurations. Another great advantage is that there is crystalline continuity between silicon platforms and silicon nanowires, so that any problem of electrical and thermal contact resistance is avoided: metal contacts can be fabricated in large areas, even not very close to the nanostructures, as silicon is heavily doped (low resistance) for thermoelectric purposes. The challenging point, and main draw-back, of this top-down strategy is that it requires high resolution lithography because the reduced dimensions of the nanostructures rely on the potentialities of the lithographic step. Nanowires narrower than 60 nm arranged in large area networks of the order of mm have been fabricated, and the design has been studied so that the large number of interconnections gives a high reliability with respect to nanowire failure [64]. An alternative approach to the use of nanowires is to use silicon lamellae (bidimensional, narrow and tall silicon nanostructures) [66]. They can be fabricated with the large side perpendicular to the silicon substrate, so that a larger number of them can be packed side by side on the same device area. From one side, the reduction of thermal conductivity is less effective (they are bidimentional structures), but on the other side the mechanical stability is increased as also the overall cross-section: this increases both the electrical current (more power) and the heat flux, whit respect to the case of using nanowires with the same width. Figure 6 shows SEM images of a demonstrator based on silicon nano-lamellae fabricated on a Silicon-On-Insulator (SOI) wafer with a top silicon layer 260 nm thick, a buried oxide layer 2 m thick and a handler layer 500 m thick. We developed this demonstrator just to prove the feasibility of a large collection of interconnected silicon nanostructures. The lamellae are as narrow as 100 nm and as tall as the thickness of the top silicon layer (260 nm, used for the demonstrator). The large side is perpendicular to the surface, therefore this design allows the packing of a large number of nanostructures, limited only by the width and the pitch between the nano-lamellae. Thicker SOI wafer can be considered: the limit of the width/height ratio is determined by the aspect ratio of the selective plasma etching process, which could reach 100:1 [67,68,69,70,71] (10 m for a width of 100 nm) if deep reactive etching is used.

Figure 6.

Original SEM micrographs of fabricated prototypes, together with a sketch of these planar thermoelectric devices. These prototypes confirm the feasibility of an all-silicon thermoelectric device, based on large arrays of silicon nanostructures.

3.2. Si Nanowires/Nanostructures for Energy Macroharvesting

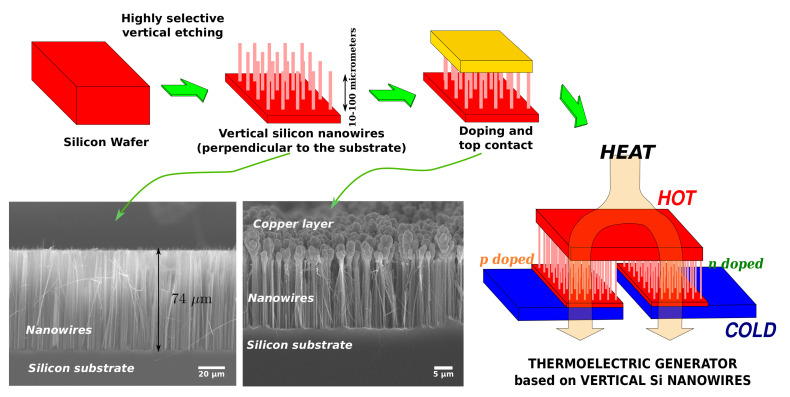

The use of nanostructured silicon for macroharvesting requires the development of low-cost nanostructuration techniques that can be applied on large areas. This excludes the use of advanced high-resolution lithography, whose costs increase rapidly with the increasing of the surface. This also makes the implementation of planar strategies difficult, because high power output means having high current and hence a very large number of parallel nanostructures, which cannot be fabricated with planar standard CMOS technologies. The reasonable configuration for large-area nanostructured silicon thermoelectric devices consists of nanowires/nanostructures placed perpendicularly to the silicon substrate, which can be fabricated by means of maskless (no lithography), highly selective etching processes, such as metal assisted chemical etching (MACE) [72,73]. Very shortly, it consists in depositing metal nanoparticles, which can be gold, silver [74,75,76] and also ruthenium [77] (investigated very recently), on the top of a standard (and hence low-cost) silicon wafer. Soaking the wafer in an acqueous solution containing an oxidizing agent and HF, the silicon is locally oxidized very close to the nanoparticles (catalyzing agent) and then removed by HF. Therefore, the nanoparticles soak into the silicon wafer leaving monocrystalline silicon pillars all around. The deposition of nanoparticles does not necessarily require expensive lithographic processes, it can be done by galvanic displacement. Nanowires have a random diameter, but the achievable average is of few tens of nanometers, well within the thermoelectric range. The best and more reliable procedure is just to soak a bare silicon wafer in a solution containing hydrofluoric acid (HF) and silver nitrate [72,75,78,79]. In the same step, silver nanoparticles are deposited on the surface and silicon is locally etched by their catalysis. Billions of nanowires per cm can be fabricated with this technique: the average diameter is around 80 nm, the length depends on the etching time and can easily reach 100 m [14], resulting in an impressive aspect ratio (>1000:1). Several works [22,27] used single silicon nanowire, produced by MACE, for the measurement of the thermal conductivity: once fabricated by MACE, a single or very few nanowires have been positioned on suspended platforms for the characterization. However, as shown in Figure 7 a thermoelectric device can exploit the overall forest, hence it is important to measure the thermal conductivity of large area samples. It has been demonstrated that, even if the nanowire diameters are not uniform, the thermal conductivity of the overall nanowire forest is strongly reduced because the dispersion of the nanowire diameter is mostly in the thermoelectric range [30,37]. Two very important issues have been faced for the fabrication of thermoelectric devices based on vertical silicon nanowire forests.

Figure 7.

Sketches and SEM micrographs of thermoelectric devices based on silicon nanowires fabricated perpendicular to the substrate.

The first issue is related with the doping of the nanowires, because the MACE process is reliable only on slightly doped silicon substrates [80,81], with doping concentrations very low with respect to those for optimal thermoelectric properties. However, a thermal diffusion doping step can be performed after the nanowire fabrication [82,83,84]. The second issue is the fabrication of contacts for the electrical and thermal transport. In particular, the bottom of the nanowires is contacted because they are anchored to the silicon substrate, the top can be contacted by means of copper electrodeposition [85]. Very high power output density, of the order of W/(cm K) [34] have been achieved with p nanowire forest. This power has been measured on “macroscopic” samples of several mm of surface.

4. Conclusions

It is well assessed, on the basis of a large number of experimental results, that the thermal conductivity of silicon nanowires/nanostructures is strongly reduced with respect to the bulk status. This fact, together with the high power factor of silicon, which increases on a large temperature range, makes silicon one of the best materials for thermoelectric applications. Combining experimental measurements published by the more recent works, at first we show that the figure of merit of monocrystalline silicon nanostructures is very high in a large temperature range, and overcomes 1 for temperatures greater than 700 K. The main drawback is that the use of silicon for thermoelectric applications must get through nanofabrication issues. An advancement of these technologies can easily bring to on-chip all-silicon thermoelectric devices, to be used for microharvesting/scavenging. As a second point of our paper, we show the feasibility of macroscopic devices based on large collections of monocrystalline silicon nanostructures, reporting the fabrication processes based on top-down approaches and showing SEM micrographs of demonstrators.

These techniques open the way for a rapid application and commercialization at an industrial level of all-silicon devices for the direct conversion of heat into electrical power.

Author Contributions

Conceptualization, formal analysis, original draft preparation G.P.; fabrication, characterization of the devices, A.M, and E.D, review and editing, G.P., E.D., and A.M. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Conflicts of Interest

The authors declare no conflict of interest.

Footnotes

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

References

- 1.Pourkiaei S.M., Ahmadi M.H., Sadeghzadeh M., Moosavi S., Pourfayaz F., Chen L., Pour Yazdi M.A., Kumar R. Thermoelectric cooler and thermoelectric generator devices: A review of present and potential applications, modeling and materials. Energy. 2019;186:115849. doi: 10.1016/j.energy.2019.07.179. [DOI] [Google Scholar]

- 2.Caballero-Calero O., Ares R., Martin-Gonzalez M. Environmentally Friendly Thermoelectric Materials: High Performance from Inorganic Components with Low Toxicity and Abundance in the Earth. Adv. Sustain. Syst. 2021:2100095. doi: 10.1002/adsu.202100095. [DOI] [Google Scholar]

- 3.Chen L., Meng F., Ge Y., Feng H., Xia S. Performance optimization of a class of combined thermoelectric heating devices. Sci. China Technol. Sci. 2020;63:2640–2648. doi: 10.1007/s11431-019-1518-x. [DOI] [Google Scholar]

- 4.Pennelli G. Review of nanostructured devices for thermoelectric applications. Beilstein J. Nanotechnol. 2014;5:1268. doi: 10.3762/bjnano.5.141. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 5.Pennelli G. Top-down fabrication of silicon nanowire devices for thermoelectric applications: Properties and perspectives. Eur. Phys. J. B. 2015;88:121. doi: 10.1140/epjb/e2015-50638-0. [DOI] [Google Scholar]

- 6.Arora N.D., Hauser R.J., Roulston J.D. Electron and Hole Mobilities in Silicon as a Function of Concentration and Temperature. IEEE Trans. Electron Devices. 1982;ED-29:292. doi: 10.1109/T-ED.1982.20698. [DOI] [Google Scholar]

- 7.Masetti G., Severi M., Solmi S. Modeling of Carrier Mobility Against Carrier Concentration in Arsenic-, Phosphorus-, and Boron-doped Silicon. IEEE Trans. Electron Devices. 1983;30:764. doi: 10.1109/T-ED.1983.21207. [DOI] [Google Scholar]

- 8.Reggiani S., Valdinoci M., Colalongo L., Rudan M., Baccarani G., Stricker A.D., Illien F., Felber N., Fichtner W., Zullino L. Electron and Hole Mobility in Silicon at Large Operating Temperatures—Part I: Bulk Mobility. IEEE Trans. Electron Devices. 2002;49:490. doi: 10.1109/16.987121. [DOI] [Google Scholar]

- 9.Geballe T.H., Hull G.W. Seebeck Effect in Silicon. Phys. Rev. 1955;98:940. doi: 10.1103/PhysRev.98.940. [DOI] [Google Scholar]

- 10.Brinson M.E., Dunstant W. Thermal conductivity and thermoelectric power of heavily doped n-type silicon. J. Phys. C Solid State Phys. 1970;3:483. doi: 10.1088/0022-3719/3/3/001. [DOI] [Google Scholar]

- 11.Stranz A., Kahler J., Waag A., Peiner E. Thermoelectric Properties of High-Doped Silicon from Room Temperature to 900 K. J. Electron. Mater. 2013;42:2381. doi: 10.1007/s11664-013-2508-0. [DOI] [Google Scholar]

- 12.Ohishi Y., Xie J., Miyazaki Y., Aikebaier Y., Muta H., Kurosaki K., Yamanaka S., Uchida N., Tada T. Thermoelectric properties of heavily boron- and phosphorus-doped silicon. Jpn. J. Appl. Phys. 2015;54:071301. doi: 10.7567/JJAP.54.071301. [DOI] [Google Scholar]

- 13.Bennett N.S. Thermoelectric performance in n-type bulk silicon: The influence of dopant concentration and dopant species. Phys. Status Solidi. 2017;214:1700307. doi: 10.1002/pssa.201700307. [DOI] [Google Scholar]

- 14.Dimaggio E., Pennelli G. Potentialities of silicon nanowire forests for thermoelectric generation. Nanotechnology. 2018;29:135401. doi: 10.1088/1361-6528/aaa9a2. [DOI] [PubMed] [Google Scholar]

- 15.Stranz A., Kahler J., Merzsch A., Peiner E. Nanowire silicon as a material for thermoelectric energy conversion. Microsyst. Technol. 2012;18:857. doi: 10.1007/s00542-011-1390-z. [DOI] [Google Scholar]

- 16.Neophytou N., Foster S., Vargiamidis V., Pennelli G., Narducci D. Nanostructured potential well/barrier engineering for realizing unprecedentedly large thermoelectric power factors. Mater. Today Phys. 2019;11:100159. doi: 10.1016/j.mtphys.2019.100159. [DOI] [Google Scholar]

- 17.Graziosi P., Kumarasinghe C., Neophytou N. Impact of the scattering physics on the power factor of complex thermoelectric materials. J. Appl. Phys. 2019;126:155701. doi: 10.1063/1.5116793. [DOI] [Google Scholar]

- 18.Neophytou N., Zianni X., Kosina H., Frabboni S., Lorenzi B., Narducci D. Simultaneous increase in electrical conductivity and Seebeck coefficient in highly boron-doped nanocrystalline Si. Nanotechnology. 2013;24:205402. doi: 10.1088/0957-4484/24/20/205402. [DOI] [PubMed] [Google Scholar]

- 19.Zulian L., Segrado F., Narducci D. Annealing of heavily boron-doped silicon: Effect on electrical and thermoelectric properties. J. Nanosci. Nanotechnol. 2017;17:1657–1662. doi: 10.1166/jnn.2017.13725. [DOI] [PubMed] [Google Scholar]

- 20.Bux S., Blair R., Gogna P., Lee H., Chen G., Dresselhaus M., Kaner R., Fleurial J. Nanostructured Bulk Silicon as an Effective Thermoelectric Material. Adv. Funct. Mater. 2009;19:2445–2452. doi: 10.1002/adfm.200900250. [DOI] [Google Scholar]

- 21.Li D., Wu Y., Kim P., Shi L., Yang P., Majumdar A. Thermal conductivity of individual silicon nanowires. Appl. Phys. Lett. 2003;83:2934–2936. doi: 10.1063/1.1616981. [DOI] [Google Scholar]

- 22.Boukay A., Bunimovich Y., Tahir-Kheli J., Yu J.K., Goddard W.A., III, Heat J.R. Silicon nanowires as efficient thermoelectric materials. Nat. Lett. 2008;451:168–171. doi: 10.1038/nature06458. [DOI] [PubMed] [Google Scholar]

- 23.Hochbaum A.I., Chen R., Delgrado R.D., Liang W., Garnett C.E., Najarian M., Majumdar A., Yang P. Enhanced thermoelectric performance of rough silicon nanowires. Nat. Lett. 2008;451:163–167. doi: 10.1038/nature06381. [DOI] [PubMed] [Google Scholar]

- 24.Pennelli G., Nannini A., Macucci M. Indirect measurement of thermal conductivity in silicon nanowires. J. Appl. Phys. 2014;115:084507. doi: 10.1063/1.4866994. [DOI] [Google Scholar]

- 25.Park Y.H., Kim J., Kim H., Kim I., Lee K.Y., Seo D., Choi H.J., Kim W. Thermal conductivity of VLS-grown rough Si nanowires with various surface roughnesses and diameters. Appl. Phys. A. 2011;104:7–14. doi: 10.1007/s00339-011-6474-1. [DOI] [Google Scholar]

- 26.Feser J., Sadhu J., Azeredo B., Hsu H., Ma J., Kim J., Seong M., Fang N., Li X., Ferreira P., et al. Thermal conductivity of silicon nanowire arrays with controlled roughness. J. Appl. Phys. 2012;112:114306. doi: 10.1063/1.4767456. [DOI] [Google Scholar]

- 27.Lim J., Hippalgaonkar K., Andrews C.S., Majumdar A., Yang P. Quantifying surface roughness effects on phonon transport in silicon nanowires. Nano Lett. 2012;12:2475–2482. doi: 10.1021/nl3005868. [DOI] [PubMed] [Google Scholar]

- 28.Karg S., Mensch P., Gotsmann B., Schmid H., DasKanungo P., Ghoneim H., Schmidt V., Bjork M., Troncale V., Riel H. Measurement of thermoelectric properties of single semiconductor nanowires. J. Electron. Mater. 2013;42:2409. doi: 10.1007/s11664-012-2409-7. [DOI] [Google Scholar]

- 29.Zhang T., Wu S., Zheng R., Cheng G. Significant reduction of thermal conductivity in silicon nanowire arrays. Nanotechnology. 2013;24:505718. doi: 10.1088/0957-4484/24/50/505718. [DOI] [PubMed] [Google Scholar]

- 30.Sadhu J., Tian H., Ma J., Azeredo B., Kim J., Balasundaram K., Zhang C., Li X., Ferreia P., Sinha S. Quenched Phonon Drag in Silicon Nanowires Reveals Significant Effect in the Bulk at Room Temperature. Nano Lett. 2015;15:3159. doi: 10.1021/acs.nanolett.5b00267. [DOI] [PubMed] [Google Scholar]

- 31.Raja S.N., Rhyner R., Vuttivorakulchai K., Luisier M., Poulikakos D. Length Scale of Diffusive Phonon Transport in Suspended Thin Silicon Nanowires. Nano Lett. 2017;17:276–283. doi: 10.1021/acs.nanolett.6b04050. [DOI] [PubMed] [Google Scholar]

- 32.Glynn C., Jones K., Mogili V., McSweeney W., O’Dwyer C. The Nature of Silicon Nanowire Roughness and Thermal Conductivity Suppression by Phonon Scattering Mechanisms. ECS J. Solid State Sci. Technol. 2017;6:N3029. doi: 10.1149/2.0071703jss. [DOI] [Google Scholar]

- 33.Fan D., Sigg H., Spolenak R., Ekinci Y. Strain and thermal conductivity in ultrathin suspended silicon nanowires. Phys. Rev. B. 2017;96:115307. doi: 10.1103/PhysRevB.96.115307. [DOI] [Google Scholar]

- 34.Elyamny S., Dimaggio E., Magagna S., Narducci D., Pennelli G. High Power Thermoelectric Generator Based on Vertical Silicon Nanowires. Nano Lett. 2020;20:4748–4753. doi: 10.1021/acs.nanolett.0c00227. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 35.Diez G., Gordillo J., Pujadó M., Salleras M., Fonseca L., Morata A., Rubio A. Enhanced thermoelecric figure of merit of individual Si nanowires with ultralow contact resistance. Nano Energy. 2020;67:104191. doi: 10.1016/j.nanoen.2019.104191. [DOI] [Google Scholar]

- 36.Melosh N., Boukay A., Diana F., Gerardot B., Badolato A., Petroff P., Heath J. Ultrahigh-Density Nanowires Lattices and Circuits. Science. 2003;300:112–115. doi: 10.1126/science.1081940. [DOI] [PubMed] [Google Scholar]

- 37.Pennelli G., Elyamny S., Dimaggio E. Thermal conductivity of silicon nanowire forests. Nanotechnology. 2018;2018:505402. doi: 10.1088/1361-6528/aae5b6. [DOI] [PubMed] [Google Scholar]

- 38.Donadio D., Galli G. Temperature dependence of the thermal conductivity of thin silicon nanowires. Nano Lett. 2004;10:847. doi: 10.1021/nl903268y. [DOI] [PubMed] [Google Scholar]

- 39.Martin P., Aksamija Z., Pop E., Ravaioli U. Impact of phonon-surface roughness scattering on thermal conductivity of thin Si nanowires. Phys. Rev. Lett. 2009;102:125503. doi: 10.1103/PhysRevLett.102.125503. [DOI] [PubMed] [Google Scholar]

- 40.Sojo Gordillo J., Gadea Diez G., Pacios Pujadó M., Salleras M., Estrada-Wiese D., Dolcet M., Fonseca L., Morata A., Tarancón A. Thermal conductivity of individual Si and SiGe epitaxially integrated NWs by scanning thermal microscopy. Nanoscale. 2021;13:7252–7265. doi: 10.1039/D1NR00344E. [DOI] [PubMed] [Google Scholar]

- 41.Liu W., Asheghi M. Thermal conduction in ultrathin pure and doped single-crystal silicon layers at high temperatures. J. Appl. Phys. 2005;98:123523. doi: 10.1063/1.2149497. [DOI] [Google Scholar]

- 42.Dimaggio E., Pennelli G., Macucci M. Thermal conductivity reduction in rough silicon nanomembranes. IEEE Trans. Nanotechnol. 2018;17:500. [Google Scholar]

- 43.Pennelli G., Dimaggio E., Macucci M. Improvement of the 3ω thermal conductivity measurement technique for its application at the nanoscale. Rev. Scient. Instrum. 2018;89:016104. doi: 10.1063/1.5008807. [DOI] [PubMed] [Google Scholar]

- 44.Hics L., Dresselhaus M. Effect of quantum-well structures on the thermoelectric figure of merit. Phys. Rev. B. 1993;47:12727–12731. doi: 10.1103/PhysRevB.47.12727. [DOI] [PubMed] [Google Scholar]

- 45.Hics L., Dresselhaus M. Thermoelectric figure of merit of a one-dimensional conductor. Phys. Rev. B. 1993;47:16631–16634. doi: 10.1103/PhysRevB.47.16631. [DOI] [PubMed] [Google Scholar]

- 46.Pennelli G., Macucci M. Optimization of the thermoelectric properties of nanostructured silicon. J. Appl. Phys. 2013;114:214507. doi: 10.1063/1.4842835. [DOI] [Google Scholar]

- 47.Lee J., Lee W., Lim J., Yu Y., Konq Q., Urban J., Yang P. Thermal transport in silicon nanowires at high temperature up to 700 K. Nano Lett. 2016;16:4133. doi: 10.1021/acs.nanolett.6b00956. [DOI] [PubMed] [Google Scholar]

- 48.Pennelli G., Dimaggio E., Macucci M. Fabrication Techniques for Thermoelecric Devices based on Nanostructured Silicon. J. Nanosci. Nanotechnol. 2017;17:1627. doi: 10.1166/jnn.2017.13724. [DOI] [PubMed] [Google Scholar]

- 49.Gaeda G., Pacios M., Morata A., Tarancon A. Silicon-based Nanostructures for Integrated Thermoelectric Generators. J. Phys. D Appl. Phys. 2018;51:423001. doi: 10.1088/1361-6463/aad683. [DOI] [Google Scholar]

- 50.Li Y., Buddharaju K., Singh N., Lo G., Lee S. Chip-level thermoelectric power generators based on high-density silicon nanowire array prepared with top-down CMOS technology. IEEE Electron Device Lett. 2011;32:674–676. doi: 10.1109/LED.2011.2114634. [DOI] [Google Scholar]

- 51.Donmez Noyan I., Dolcet M., Salleras M., Stranz A., Calaza C., Gadea G., Pacios M., Morata A., Tarancon A., Fonseca L. All-silicon thermoelectric micro/nanogenerator including a heat exchanger for harvesting applications. J. Power Sources. 2019;413:125–133. doi: 10.1016/j.jpowsour.2018.12.029. [DOI] [Google Scholar]

- 52.Fonseca L., Donmez-Noyan I., Dolcet M., Estrada-Wiese D., Santander J., Salleras M., Gadea G., Pacios M., Sojo J.M., Morata A., et al. Transitioning from Si to sige nanowires as thermoelectric material in silicon-based microgenerators. Nanomaterials. 2021;11:517. doi: 10.3390/nano11020517. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 53.Domnez Noyan I., Gadea G., Salleras M., Pacios M., Calaza C., Stranz A., Dolcet M., Morata A., Tarancon A., Fonseca L. SiGe nanowire arrays based thermoelectric microgenerator. Nano Energy. 2019;57:492–499. doi: 10.1016/j.nanoen.2018.12.050. [DOI] [Google Scholar]

- 54.Tomita M., Oba S., Himeda Y., Yamato R., Shima K., Kumada T., Xu M., Takezawa H., Mesaki K., Tsuda K., et al. Modeling, simulation, fabrication, and characterization of a 10-μW/cm2 class si-nanowire thermoelectric generator for IoT applications. IEEE Trans. Electron Devices. 2018;65:5180–5188. doi: 10.1109/TED.2018.2867845. [DOI] [Google Scholar]

- 55.Davila D., Tarancon A., Calaza C., Salleras M., Fernandez-Regulez M., SanPaulo A., Fonseca L. Monolithically integrated thermoelectric energy harvester based on silicon nanowire arrays for powering micro/nanodevices. Nano Energy. 2012;1:812. doi: 10.1016/j.nanoen.2012.06.006. [DOI] [Google Scholar]

- 56.Davila D., Tarancon A., Fernandez-regulez M., Calaza C., Salleras M., SanPaulo A., Fonseca L. Silicon nanowire arrays as thermoelectric material for a power microgenerator. J. Micromechan. Microeng. 2011;21:104007. doi: 10.1088/0960-1317/21/10/104007. [DOI] [Google Scholar]

- 57.Gadea G., Morata A., Tarancon A. Semiconductor Nanowires for Thermoelectric Generation. Semicond. Semimetals. 2018;98:321–407. doi: 10.1016/bs.semsem.2018.01.001. [DOI] [Google Scholar]

- 58.Fonseca L., Santos J.D., Roncaglia A., Narducci D., Calaza C., Salleras M., Donmez I., Tarancon A., Morata A., Gadea G., et al. Smart integration of silicon nanowire arrays in all-silicon thermoelectric micro-nanogenerators. Semicond. Sci. Technol. 2016;31:084001. doi: 10.1088/0268-1242/31/8/084001. [DOI] [Google Scholar]

- 59.Calaza C., Fonseca L., Salleras M., Donmez I., Tarancón A., Morata A., Santos J., Gadea G. Thermal Test of an Improved Platform for Silicon Nanowire-Based Thermoelectric Micro-generators. J. Electron. Mater. 2016;45:1689–1694. doi: 10.1007/s11664-015-4168-8. [DOI] [Google Scholar]

- 60.Gadea Díez G., Sojo Gordillo J., Pacios Pujadó M., Salleras M., Fonseca L., Morata A., Tarancón Rubio A. Enhanced thermoelectric figure of merit of individual Si nanowires with ultralow contact resistances. Nano Energy. 2020;67:104191. doi: 10.1016/j.nanoen.2019.104191. [DOI] [Google Scholar]

- 61.Yuan Z., Ziouche K., Bougrioua Z., Lejeune P., Lasri T., Leclercq D. A planar micro thermoelectric generator with high thermal resistance. Sens. Actuators A Phys. 2015;221:67–76. doi: 10.1016/j.sna.2014.10.026. [DOI] [Google Scholar]

- 62.Ziouche K., Yuan Z., Lejeune P., Lasri T., Leclercq D., Bougrioua Z. Silicon-Based Monolithic Planar Micro Thermoelectric Generator Using Bonding Technology. J. Microelectromechan. Syst. 2017;26:45–47. doi: 10.1109/JMEMS.2016.2633442. [DOI] [Google Scholar]

- 63.Ziouche K., Bel-Hadj I., Bougrioua Z. Thermoelectric properties of nanostructured porous-polysilicon thin films. Nano Energy. 2021;80:105553. doi: 10.1016/j.nanoen.2020.105553. [DOI] [Google Scholar]

- 64.Pennelli G., Totaro M., Piotto M., Bruschi P. Seebeck coefficient of nanowires interconnected into large area networks. Nano Lett. 2013;13:2592. doi: 10.1021/nl400705b. [DOI] [PubMed] [Google Scholar]

- 65.Totaro M., Bruschi P., Pennelli G. Top down fabricated silicon nanowire networks for thermoelectric applications. Microelectron. Eng. 2012;97:157. doi: 10.1016/j.mee.2012.04.007. [DOI] [Google Scholar]

- 66.Pennelli G., Macucci M. High-power thermoelectric generators based on nanostructured silicon. Semicond. Sci. Technol. 2016;31:054001. doi: 10.1088/0268-1242/31/5/054001. [DOI] [Google Scholar]

- 67.Pournia M., Firoozabadi S., Fathipour M., Kolahdouz M. Fabrication of ultra-high-aspect-ratio nano-walls and nano-structures on silicon substrates. J. Micromechan. Microeng. 2020;30:125008. doi: 10.1088/1361-6439/abbcb9. [DOI] [Google Scholar]

- 68.Nguyen V., Shkondin E., Jensen F., Hübner J., Leussink P., Jansen H. Ultrahigh aspect ratio etching of silicon in SF6-O2plasma: The clear-oxidize-remove-etch (CORE) sequence and chromium mask. J. Vac. Sci. Technol. A Vac. Surfaces Film. 2020;38:053002. doi: 10.1116/6.0000357. [DOI] [Google Scholar]

- 69.Bagolini A., Scauso P., Sanguinetti S., Bellutti P. Silicon Deep Reactive Ion Etching with aluminum hard mask. Mater. Res. Express. 2019;6:085913. doi: 10.1088/2053-1591/ab2423. [DOI] [Google Scholar]

- 70.Parasuraman J., Summanwar A., Marty F., Basset F., Angelescu D., Bourouina T. Deep reactive ion etching of sub-micrometer trenches with ultra high aspect ratio. Microelectron. Eng. 2014;113:35. doi: 10.1016/j.mee.2013.06.010. [DOI] [Google Scholar]

- 71.Stranz A., Waag A., Peiner E. High-temperature performance of stacked silicon nanowires for thermoelectric power generation. J. Electron. Mat. 2013;42:2233. doi: 10.1007/s11664-013-2590-3. [DOI] [Google Scholar]

- 72.Huang Z., Geyer N., Werner P., de Boor J., Gosele U. Metal-assisted chemical etching of silicon: A review. Adv. Mater. 2011;23:285–308. doi: 10.1002/adma.201001784. [DOI] [PubMed] [Google Scholar]

- 73.Kim J., Han H., Kim Y., Choi S.H., Kim J.C., Lee W. Au/Ag bilayered metal mesh as a Si etching catalyst for controlled fabrication of Si nanowires. ACS Nano. 2011;5:3222. doi: 10.1021/nn2003458. [DOI] [PubMed] [Google Scholar]

- 74.Magagna S., Narducci D., Alfonso C., Dimaggio E., Pennelli G., Charaï A. On the mechanism ruling the morphology of silicon nanowires obtained by one-pot metal-assisted chemical etching. Nanotechnology. 2020;31:404002. doi: 10.1088/1361-6528/ab9b47. [DOI] [PubMed] [Google Scholar]

- 75.To W., Tsang C., Li H., Huang Z. Fabrication of n-Type Mesoporous Silicon Nanowires by One-Step Etching. Nano Lett. 2011;11:5252–5258. doi: 10.1021/nl202674t. [DOI] [PubMed] [Google Scholar]

- 76.Bollani M., Osmond J., Nicotra G., Spinella C., Narducci D. Strain-induced generation of silicon nanopillars. Nanotechnology. 2013;24:335302. doi: 10.1088/0957-4484/24/33/335302. [DOI] [PubMed] [Google Scholar]

- 77.Mallavarapu A., Ajay P., Barrera C., Sreenivasan S. Ruthenium-Assisted Chemical Etching of Silicon: Enabling CMOS-Compatible 3D Semiconductor Device Nanofabrication. ACS Appl. Mater. Interfaces. 2021;13:1169–1177. doi: 10.1021/acsami.0c17011. [DOI] [PubMed] [Google Scholar]

- 78.Peng K., Yan Y., Gao S., Zhu J. Dendride-assisted growth of silicon nanowires in electroless metal deposition. Adv. Funct. Mater. 2003;13:127. doi: 10.1002/adfm.200390018. [DOI] [Google Scholar]

- 79.Peng K., Hu J., Yan Y., Wu Y., Fang H., Xu Y., Lee S., Zhu J. Fabrication of single-crystalline silicon nanowires by scratching a silicon surface with catalytic metal particles. Adv. Funct. Mater. 2006;16:387–394. doi: 10.1002/adfm.200500392. [DOI] [Google Scholar]

- 80.Qi Y., Wang Z., Zhang M., Yang F., Wang Z. A Processing Window for Fabricating Heavily Doped Silicon Nanowires by Metal-Assisted Chemical Etching. J. Phys. Chem. C. 2013;117:25090. doi: 10.1021/jp407720e. [DOI] [Google Scholar]

- 81.Dimaggio E., Narducci D., Pennelli G. Fabrication of Silicon Nanowire Forests for Thermoelectric Applications by Metal-Assisted Chemical Etching. J. Mater. Eng. Perform. 2018;27:6279–6285. doi: 10.1007/s11665-018-3605-2. [DOI] [Google Scholar]

- 82.Elyamny S., Dimaggio E., Pennelli G. Seebeck coefficient of silicon nanowire forests doped by thermal diffusion. Beilstein J. Nanotechnol. 2020;11:1707–1713. doi: 10.3762/bjnano.11.153. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 83.Sadhu J.S., Tian H., Spila T., Kim J., Azeredo B., Ferreira P., Sinha S. Controllable doping and wrap-around contacts to electrolessly etched silicon nanowire arrays. Nanotechnology. 2014;25:375701. doi: 10.1088/0957-4484/25/37/375701. [DOI] [PubMed] [Google Scholar]

- 84.Xu B., Fobelets K. Spin-on-doping for output power improvement of silicon nanowire array based thermoelectric power generators. J. Appl. Phys. 2014;115:214306. doi: 10.1063/1.4881781. [DOI] [Google Scholar]

- 85.Dimaggio E., Pennelli G. Reliable Fabrication of Metal Contacts on Silicon Nanowire Forests. Nano Lett. 2016;7:4348. doi: 10.1021/acs.nanolett.6b01440. [DOI] [PubMed] [Google Scholar]