Graphene and two-dimensional materials (2DM) remain an active field of research in science and engineering over 15 years after the first reports of 2DM. The vast amount of available data and the high performance of device demonstrators leave little doubt about the potential of 2DM for applications in electronics, photonics and sensing. So where are the integrated chips and enabled products? We try to answer this by summarizing the main challenges and opportunities that have thus far prevented 2DM applications.

Subject terms: Electrical and electronic engineering, Two-dimensional materials, Electronic devices, NEMS, Two-dimensional materials

Graphene and related two-dimensional (2D) materials have remained an active field of research in science and engineering for over fifteen years. Here, the authors investigate why the transition from laboratories to fabrication plants appears to lag behind expectations, and summarize the main challenges and opportunities that have thus far prevented the commercialisation of these materials.

Manufacturing technology

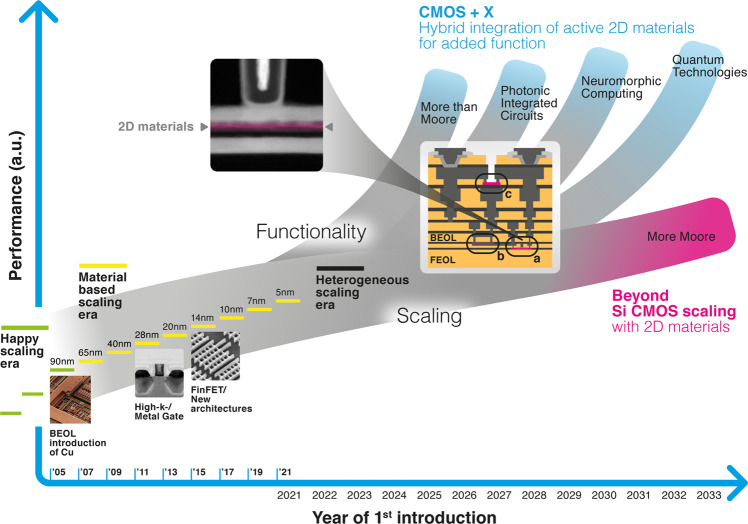

The key answer to this question, in our opinion, can be found by comparing the manufacturing readiness level of 2DM with standard semiconductor technology. What is needed, but not available yet, are turnkey manufacturing solutions that bring 2DM into silicon (Si) semiconductor factories. These “unit processes” then serve to integrate 2DMs with Si complementary metal oxide semiconductor (CMOS) chips in the back-end or front-end of the line1,2. Deposition and growth technology of 2DMs is generally available at the wafer scale, but defects and contaminations are not yet compliant with specifications defined for production3. In addition, high process temperatures are typically required for high quality materials, which complicates direct growth on wafers and makes transfer technologies desirable. In principle, wafer bonding techniques could solve this, but have not reached full manufacturing levels4. At the device level, challenges are linked to the control of the dielectric- and contact interfaces to the 2DMs. The self-passivated nature of 2DM surfaces requires seeding to achieve the deposition of dielectrics with manufacturable methods, e.g. through atomic layer deposition. The resulting non-ideal interfaces limit device performance compared to the best laboratory demonstrators that use crystalline 2D insulators such as hexagonal boron nitride5. The same is true for electrical contacts to 2DMs, which only partly meet industry specifications6, and have not reached manufacturing readiness. The removal or etching of materials with high selectivity towards underlying layers is particularly challenging for 2DMs, because it requires atomic precision that can only be achieved with specific chemistry and dedicated atomic layer etching tools. Developing suitable processes will be tedious, because of the wide range of potential 2DMs and their combinations. As a result, etching chemistry and other, physical process parameters depend strongly on the specific situation which each require individual solutions. Doping, or the replacement of atoms in the crystal lattice, is a standard but crucial technology for silicon that relies on statistical distributions. In the 2DM field, the term doping is often used to describe charge transfer to the 2D layer from defects or molecular adsorbates in its vicinity. Controlling this “effective-doping” with precision and long-term stability remains a challenge, but so would classic doping, which would ideally require replacing 2D crystal atoms in a deterministic way, as shown for silicon technology7. Solving these crucial manufacturing bottlenecks is the explicit goal of the European Experimental Pilot Line for 2D Materials8. Co-integration of 2DMs with silicon CMOS technology will lead to a vast increase in chip functionality and enable the arrival of 2DM applications in the order of their device complexity, as illustrated in Fig. 1 and presented in the following.

Fig. 1. The era of geometrical or Dennard9 scaling of silicon technology ended around the turn of the century (green lines, “happy scaling”).

Since then, material and architecture innovations like copper interconnects10, high-k dielectrics with metal gates11 and FinFETs12 continued to drive Moore’s law (yellow lines, “less happy scaling”). Future scaling, or “More Moore”, may require thin nanosheet transistors, where 2D materials are considered ideal candidates (magenta, inset a and transmission electron micrograph)13,14. Substantial performance and functionality gains are expected through “CMOS + X” integration, for example through sensors or high frequency electronics integrated on CMOS chips in the “More Than Moore” domain (inset c). Photonic integrated circuits may boost overall system performance and data handling capabilities, as well as unlock spectroscopic sensing applications, enabled by the optoelectronic performance of 2DMs. Computing-In-Memory or memristors will enable future neuromorphic computing applications and 2DMs may be ideally suited to be integrated with silicon CMOS (inset b). 2D quantum technologies are the least mature even at the laboratory level, but will benefit from all expected achievements as 2DMs enter semiconductor processing lines. 2D materials hold great promise to become the X-Factor for CMOS. This may be described as the era of heterogenous scaling, where new and additional materials provide unprecedented performance in three-dimensional chip stacks. Note that the Y-axis had a unit of “log2(#transistors/$)“ during the classic “Moore’s law” period. This has to be replaced in the era of heterogeneous scaling, and we suggest labeling it “Performance (a.u.)”, because the increase in performance will become application specific. It will be determined by (combined) factors like power consumption and efficiency, capability to perform pattern recognition, sensor fusion, etc., which results in somewhat arbitrary units due to the diverse functionalities and underlying technologies. (Insets: BEOL Introduction of Cu: Reproduced with permission from the AAAS, reference;10 High-k/Metal Gate: © 2007 IEEE. Reprinted, with permission, from Mistry, K. et al. A 45 nm Logic technology with high-k+metal gate transistors, strained silicon, 9 Cu interconnect layers, 193 nm dry patterning, and 100% Pb-free packaging. In 2007 IEEE International Electron Devices Meeting 247–250 (2007);11 FinFET/New architectures: Republished with permission of IEEE, from Jan, C. -H. et al. A 22 nm SoC platform technology featuring 3-D tri-gate and high-k/metal gate, optimized for ultra low power, high performance and high density SoC applications. In 2012 International Electron Devices Meeting 3.1.1–3.1.4, 2012;12 permission conveyed through Copyright Clearance Center, Inc.; 2D Materials: source: ref. 14).

More Moore

In general, gains in advanced semiconductor technology nodes are enabled through increased complexity of the integration architectures as well as holistic system-technology co-optimization. On the device level, leading semiconductor manufacturers are turning from FinFETs to stacked nanosheet FET architectures for the most advanced nodes of CMOS technology15. These nanosheet devices are currently still based on Si channels. Different flavors of such nanosheet architectures are in evaluation for future technology nodes, e.g. a so-called fork sheet design that allows tighter n-to-p spacing16, or integration of p and n-type nanosheets on top of each other17. Further scaling of the channel length requires shrinking the channel thickness by a similar factor to guarantee sufficient electrostatic control to suppress short channel effects. Trimming down the Si sheet thickness to the required values increases the charge scattering at the interfaces and results in a dramatic drop of the carrier mobility in the channel18, which ruins device performance. 2D semiconductors would be the ultimate version of nanosheets, because they are self-passivated in the 3rd dimension and charge carrier mobility is not strongly affected from surface scattering. Therefore, mobility remains high even at the atomic thickness limit. This unique behavior in principle enables real scaling for several technology nodes and is a strong incentive for the semiconductor industry to finally consider replacing silicon as the transistor channel material for future advanced nodes13,14,19. This takes us back to the fundamental technical and scientific challenges which are linked to 2D integration. Here, identifying a suitable gate oxide stack and finding low ohmic contact schemes are particularly important. The former is essential to preserve the 2D material properties and to provide sufficient electrostatic control while limiting gate leakage currents5. 2D hexagonal boron (hBN) nitride has been widely applied to demonstrate high performance devices based on 2DMs, but its band gap and band offsets dictate that sufficient electrostatic control can only be achieved with one or two monolayers. This additional boundary condition leads to intolerably high gate leakage currents and other solutions will have to be found20. Low ohmic contacts are required to maintain the benefits of the channel material in integrated circuits, because high resistance contacts can dominate and severely limit the integrated device performance21. Recently, substantially improved electrical contact resistance to MoS2 has been reported by using semi-metallic Bismuth, which strongly suppresses metal induced gap states and the spontaneous formation of degenerate states in the MoS222. Nevertheless, more breakthroughs like this are needed to uncover and fully exploit the potential of monolayer transistors in CMOS circuits, to revive transistor downscaling and continue Moore’s law.

More than Moore

Applications in this category are likely first to enter the market, because they are manyfold, yet often very specific, so that they may tolerate defects and larger device variations.

2DMs are well-suited for gas, chemical and biosensing, because of their inherently high surface to volume ratio and versatile functionalization23. Thus, any charged particle or molecule in the vicinity of certain 2D layered materials can modify their conductivity. However, ideal 2DMs are chemically inert, which means that chemically active defect sites strongly enhance the reactivity of 2D based sensors. Precise defect engineering is therefore essential for controlling sensitivity. In addition, sensor selectivity is essential. It may be achieved through surface functionalization or via arrays made from different sensors to mimic complex biological systems like the nose. Here, the portfolio of 2DMs with diverse sensor “fingerprints” may be utilized in conjunction with machine learning algorithms for sensor read-out.

Micro- and nanoelectromechanical systems (MEMS/NEMS) typically rely on mechanically movable parts on the chip. 2DMs exhibit exceptional mechanical properties that produce ultra-thin membranes, which translates directly to extremely high sensitivities in piezoresistive and opto-mechanical read out schemes, providing efficient signal transduction in NEMS. 2D membrane-based NEMS applications include pressure sensors, accelerometers, oscillators, resonant mass sensors, gas sensors, Hall effect sensors, and bolometers24.

2DMs possess a range of advantages over existing technologies for optoelectronic and photonic applications25, in particular outside of the spectral range that can be addressed with silicon. But even there, the direct band gaps of many semiconducting 2DMs provide advantages over silicon when it comes to light emission26. Semi-metallic and small band gap materials like graphene, platinum diselenide or black phosphorous open up the infrared (IR) regime, where they compete with often costly III–V semiconductor technologies. Although the 2D nature translates into low absolute absorption in the vertical direction, the combination with IR-sensitive absorption layers leads to high detector responsivity27.

Photonic integrated circuits

Photonic integrated circuits are considered as ultimate performance boosters for data transmission on and across computer chips28. Connecting them to silicon electronics through optoelectronic converters at extremely high data rates is a key enabling technology. 2DMs, and in particular graphene, can be transferred onto photonic waveguides and provide wide-band photodetection and modulation25,29,30. By removing the need for epitaxy, 2D-based photonics thus allows integrating active device components with Si photonics, but also with passive amorphous waveguide materials, like silicon nitride. This opens the door for facile integration of complex photonics applications on top of CMOS. In fact, some 2DMs like platinum diselenide can also be directly and conformally grown at temperatures below 400 °C31, which is a clear advantage in the quest to co-integrate photonic integrated circuits with silicon CMOS technology32. With the potential for integrated 2D light sources26, 2DMs could ultimately enable the convergence of electronics and photonics and bridge the spectrum across the THz gap.

Neuromorphic computing

Neuromorphic computing aims to provide brain-inspired computing devices and architectures to realize energy efficient hardware for artificial intelligence applications33. On the device level, requirements for neuromorphic computing include merging memory with logic to enable Computing-In-Memory and memristive device characteristics that mimic synapses and neurons. The former can already be realized with conventional memory technologies while the latter translates to threshold switches, and non-volatile memristors with a wide range of programmable resistance states34,35. Though relatively nascent, 2D memristors have shown promising performance including switching energies on the order of zeta-joules, sub nano-second switching times, dozens of programmable states, and prototype artificial neural networks at the wafer-scale36. This may enable applications in sensor systems and edge computing, for example by preprocessing of sensor data or on-chip sensor fusion37. In addition to neuromorphic computing, 2D memristive devices have been shown to provide a wide range of non-computing functions including physically unclonable functions for security systems, and radio-frequency switching for communication systems38.

From a scientific view, the phenomena of resistive switching in 2D devices have been attributed to ionic transport39,40, defect/filament formation41 or phase change effects42. Notwithstanding these fundamental aspects, 2D memristive switching remains a topic enjoying increasing discussion and research. At the device level, a fundamental challenge is improving the number of times the resistance can be switched, so-called endurance, which requires further studies into the aging effect of the underlying mechanism(s). Similarly, improving material uniformity will be essential in order to realize massively connected device arrays that can mimic the hyper-connectivity and efficiency of the brain. Hearteningly, over a dozen 2DMs have exhibited memristive effect with this collection likely to grow in the coming years. Therefore, computational methods will be increasingly needed to guide experimental studies and optimize memristive devices for maximum performance.

Quantum technologies

2D materials and related van-der-Waals heterostructures offer also a variety of properties that make them highly tunable quantum materials interesting for spintronics and future quantum technologies43. Two-dimensional material systems not only have the ability to enable artificial states of quantum matter, but fulfil a number of promises for solid-state quantum computing, to serve as key components in quantum communication circuits or allow interesting quantum sensing schemes. Indeed, 2DMs are a promising solid-state platform for quantum-dot qubits, as recognized quite early44, for topological quantum computing elements, as well as coherent sources of single-photon emitters.

Quantum computing based on semiconductor quantum dots (DQs) uses individual spin states of trapped electrons. It relies, among other aspects, on long spin coherence times for which the host material plays an important role. This makes graphene a very interesting materials for spin qubits, thanks to its weak spin-orbit coupling (carbon atoms are very light) and weak hyperfine coupling (Carbon 12 is nuclear spin free). With the recent progress in confining single-electrons in gate-controlled QDs in gapped bilayer graphene45,46, first spin-qubits are now around the corner. The possibility to make spin qubits in 2DMs will also allow evaluating the additional valley degree of freedom as possible qubit states; interesting proposals of valley- and spin-valley qubits exist. In addition, stationary qubits in 2DMs may afford coupling to photonic qubits realized by single-photon emitters (SPEs), for example in nearby wide band-gap hexagonal boron nitride or semiconducting transition metal dichalcogenides, such as WSe247. In these 2DMs, SPEs have been demonstrated in recent years and this opens the door to distributed quantum networks, where photonic qubits could act as interlinks that entangle distant stationary qubits, e.g., spin-qubits. Such robust, bright and indistinguishable single-photon emitters are essential for creating photonic (flying) qubits for efficient quantum communication.

2D heterostructures are, moreover, promising materials for topological quantum computing, where quantum states are potentially better (i.e. topologically) protected against disorder, compared to standard quantum computing48. Combining, for example, a quantum anomalous Hall insulator or graphene tuned into the canted anti-ferromagnetic quantum Hall phase with s-wave superconductors is a promising platform for topological quantum computing. In short, these advances make 2DMs and their heterostructures in many ways an exciting and promising platform for future quantum technologies.

Conclusions

2DMs provide exceptional performance benefits over existing technologies at the device level. They also carry the promise of easy integration with silicon CMOS technology. This makes them prime candidates for substantially expanding the functionality of silicon chips, also referred to as “CMOS + X”. We are confident that 2DMs will increasingly become such an X-factor in future integrated products. The bottleneck towards 2D material-based heterogeneous electronics is reaching the required manufacturing readiness levels, which may be different depending on the targeted application.

Acknowledgements

The authors acknowledge funding from the European Union’s Horizon 2020 research and innovation program under grant agreements 881603 (Graphene Flagship), 952792 (2D-EPL), 101017186 (AEOLUS), 101016734 (MISEL), 971398 (ULTRAPHO), 101006963 (GreEnergy), 956813 (2Exciting), 863337 (WIPLASH), 825272 (ULISSES) and 829035 (QUEFORMAL) as well as the European Research Council (ERC) under grant agreements 820254 and 307311. We further acknowledge support from the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation) under Germany’s Excellence Strategy-Cluster of Excellence Matter and Light for Quantum Computing (ML4Q) EXC 2004/1 -390534769 and through the DFG grants STA 1146/11-1, STA 1146/12-1, LE 2440/7-1, LE 2440/8-1 and LE 2440/11-1. Furthermore, support by the Bundesministerium für Bildung und Forschung (BMBF, German Ministry of Education and Research) through the grants 03XP0210 (GIMMIK), 16ES1121 (NobleNEMS) and 16ME0399 (NEUROTEC II) is acknowledged, as is the Alexander von Humboldt-Foundation. Part of the work leading to this manuscript has been carried out in the Aachen Graphene & 2D Materials Center.

Author contributions

M.C.L., D.A., C.H., and C.S. co-wrote the manuscript and co-created the figure.

Peer review

Peer review information

Nature Communications thanks Peng Zhou for their contribution to the peer review of this work.

Competing interests

The authors declare no competing interests.

Footnotes

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

References

- 1.Akinwande D, et al. Graphene and two-dimensional materials for silicon technology. Nature. 2019;573:507–518. doi: 10.1038/s41586-019-1573-9. [DOI] [PubMed] [Google Scholar]

- 2.Neumaier D, Pindl S, Lemme MC. Integrating graphene into semiconductor fabrication lines. Nat. Mater. 2019;18:525. doi: 10.1038/s41563-019-0359-7. [DOI] [PubMed] [Google Scholar]

- 3.Lupina G, et al. Residual metallic contamination of transferred chemical vapor deposited graphene. ACS Nano. 2015;9:4776–4785. doi: 10.1021/acsnano.5b01261. [DOI] [PubMed] [Google Scholar]

- 4.Quellmalz A, et al. Large-area integration of two-dimensional materials and their heterostructures by wafer bonding. Nat. Commun. 2021;12:917. doi: 10.1038/s41467-021-21136-0. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 5.Illarionov YYU, et al. Insulators for 2D nanoelectronics: the gap to bridge. Nat. Commun. 2020;11:3385. doi: 10.1038/s41467-020-16640-8. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 6.Passi V, et al. Ultralow specific contact resistivity in metal–graphene junctions via contact engineering. Adv. Mater. Interfaces. 2019;6:1801285. doi: 10.1002/admi.201801285. [DOI] [Google Scholar]

- 7.Fuechsle M, et al. A single-atom transistor. Nat. Nanotechnol. 2012;7:242–246. doi: 10.1038/nnano.2012.21. [DOI] [PubMed] [Google Scholar]

- 8.The Graphene Fagship. Graphene Flagship launches first European Experimental Pilot Line. https://www.mynewsdesk.com/graphene-flagship/pressreleases/graphene-flagship-launches-first-european-experimental-pilot-line-3040987.

- 9.Baccarani G, Wordeman MR, Dennard RH. Generalized scaling theory and its application to a 1/4 micrometer MOSFET design. IEEE Trans. Electron Devices. 1984;31:452–462. doi: 10.1109/T-ED.1984.21550. [DOI] [Google Scholar]

- 10.Miller RD. In search of low-k dielectrics. Science. 1999;286:421–423. doi: 10.1126/science.286.5439.421. [DOI] [Google Scholar]

- 11.Mistry, K. et al. A 45 nm Logic technology with high-k+metal gate transistors, strained silicon, 9 Cu interconnect layers, 193 nm dry patterning, and 100% Pb-free packaging. In 2007 IEEE International Electron Devices Meeting 247–250 (IEEE, 2007).

- 12.Jan, C. -H. et al. A 22 nm SoC platform technology featuring 3-D tri-gate and high-k/metal gate, optimized for ultra low power, high performance and high density SoC applications. In 2012 International Electron Devices Meeting 3.1.1–3.1.4 (IEEE, 2012).

- 13.Zhou, R. & Appenzeller, J. Three-dimensional integration of multi-channel MoS2 devices for high drive current FETs. In 2018 76th Device Research Conference (DRC) 1–2 (IEEE, 2018).

- 14.Schram, T. et al. High yield and process uniformity for 300 mm integrated WS2 FETs. In 2021 Symposium on VLSI Technology 1–2 (IEEE, 2021).

- 15.Loubet, N. et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In 2017 Symposium on VLSI Technology T230–T231 (IEEE, 2017).

- 16.Mertens, H. et al. Forksheet FETs for advanced CMOS scaling: forksheet-nanosheet co-integration and dual work function metal gates at 17 nm N-P space. In 2021 Symposium on VLSI Technology 1–2 (IEEE, 2021).

- 17.Huang, C.-Y. et al. 3-D Self-aligned stacked NMOS-on-PMOS nanoribbon transistors for continued Moore’s Law scaling. In 2020 IEEE International Electron Devices Meeting 20.6.1-20.6.4 (2020).

- 18.Schmidt M, et al. Mobility extraction in SOI MOSFETs with sub 1 nm body thickness. Solid-State Electron. 2009;53:1246–1251. doi: 10.1016/j.sse.2009.09.017. [DOI] [Google Scholar]

- 19.Das S, et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 2021;4:786–799. doi: 10.1038/s41928-021-00670-1. [DOI] [Google Scholar]

- 20.Knobloch T, et al. The performance limits of hexagonal boron nitride as an insulator for scaled CMOS devices based on two-dimensional materials. Nat. Electron. 2021;4:98–108. doi: 10.1038/s41928-020-00529-x. [DOI] [Google Scholar]

- 21.Bittle EG, Basham JI, Jackson TN, Jurchescu OD, Gundlach DJ. Mobility overestimation due to gated contacts in organic field-effect transistors. Nat. Commun. 2016;7:1–7. doi: 10.1038/ncomms10908. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 22.Shen P-C, et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature. 2021;593:211–217. doi: 10.1038/s41586-021-03472-9. [DOI] [PubMed] [Google Scholar]

- 23.Anichini C, et al. Chemical sensing with 2D materials. Chem. Soc. Rev. 2018;47:4860–4908. doi: 10.1039/C8CS00417J. [DOI] [PubMed] [Google Scholar]

- 24.Lemme MC, et al. Nanoelectromechanical sensors based on suspended 2D materials. Research. 2020;2020:8748602. doi: 10.34133/2020/8748602. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 25.Romagnoli M, et al. Graphene-based integrated photonics for next-generation datacom and telecom. Nat. Rev. Mater. 2018;3:392–414. doi: 10.1038/s41578-018-0040-9. [DOI] [Google Scholar]

- 26.Pospischil A, Furchi MM, Mueller T. Solar-energy conversion and light emission in an atomic monolayer p-n diode. Nat. Nano. 2014;9:257–261. doi: 10.1038/nnano.2014.14. [DOI] [PubMed] [Google Scholar]

- 27.Konstantatos G, et al. Hybrid graphene-quantum dot phototransistors with ultrahigh gain. Nat. Nano. 2012;7:363–368. doi: 10.1038/nnano.2012.60. [DOI] [PubMed] [Google Scholar]

- 28.Alexoudi T, et al. Optics in computing: from photonic network-on-chip to chip-to-chip interconnects and disintegrated architectures. J. Lightwave Technol. 2019;37:363–379. doi: 10.1109/JLT.2018.2875995. [DOI] [Google Scholar]

- 29.Liu M, et al. A graphene-based broadband optical modulator. Nature. 2011;474:64–67. doi: 10.1038/nature10067. [DOI] [PubMed] [Google Scholar]

- 30.Schall D, et al. 50 GBit/s Photodetectors based on wafer-scale graphene for integrated silicon photonic communication systems. ACS Photonics. 2014 doi: 10.1021/ph5001605. [DOI] [Google Scholar]

- 31.Prechtl, M. et al. Conformal and selective deposition of layered PtSe2: 2D goes 3D. Adv. Funct. Mater. 2103936 (2021).

- 32.Parhizkar, S. et al. Two-dimensional platinum diselenide waveguide-integrated infrared photodetectors. 10.1021/acsphotonics.1c01517 (2021). [DOI] [PMC free article] [PubMed]

- 33.Christensen, D. V. et al. 2022 Roadmap on neuromorphic computing and engineering. Neuromorph. Comput. Eng.10.1088/2634-4386/ac4a83 (2022). in press.

- 34.Liu C, et al. Two-dimensional materials for next-generation computing technologies. Nat. Nanotechnol. 2020;15:545–557. doi: 10.1038/s41565-020-0724-3. [DOI] [PubMed] [Google Scholar]

- 35.Sangwan VK, Hersam MC. Neuromorphic nanoelectronic materials. Nat. Nanotechnol. 2020;15:517–528. doi: 10.1038/s41565-020-0647-z. [DOI] [PubMed] [Google Scholar]

- 36.Chen S, et al. Wafer-scale integration of two-dimensional materials in high-density memristive crossbar arrays for artificial neural networks. Nat. Electron. 2020;3:638–645. doi: 10.1038/s41928-020-00473-w. [DOI] [Google Scholar]

- 37.Mennel L, et al. Ultrafast machine vision with 2D material neural network image sensors. Nature. 2020;579:62–66. doi: 10.1038/s41586-020-2038-x. [DOI] [PubMed] [Google Scholar]

- 38.Kim M, et al. Analogue switches made from boron nitride monolayers for application in 5G and terahertz communication systems. Nat. Electron. 2020;3:479–485. doi: 10.1038/s41928-020-0416-x. [DOI] [Google Scholar]

- 39.Sangwan VK, et al. Gate-tunable memristive phenomena mediated by grain boundaries in single-layer MoS2. Nat. Nanotechnol. 2015;10:403–406. doi: 10.1038/nnano.2015.56. [DOI] [PubMed] [Google Scholar]

- 40.Belete, M. et al. Nonvolatile resistive switching in nanocrystalline molybdenum disulfide with ion-based plasticity. Adv. Electron. Mater. 1900892 (2020) 10.1002/aelm.201900892.

- 41.Hus, S. M. et al. Observation of single-defect memristor in an MoS 2 atomic sheet. Nat. Nanotechnol. 1–5 (2020) 10.1038/s41565-020-00789-w. [DOI] [PubMed]

- 42.Zhang F, et al. Electric-field induced structural transition in vertical MoTe2 - and Mo1–xWxTe2-based resistive memories. Nat. Mater. 2019;18:55. doi: 10.1038/s41563-018-0234-y. [DOI] [PubMed] [Google Scholar]

- 43.Liu X, Hersam MC. 2D materials for quantum information science. Nat. Rev. Mater. 2019;4:669–684. doi: 10.1038/s41578-019-0136-x. [DOI] [Google Scholar]

- 44.Trauzettel B, Bulaev DV, Loss D, Burkard G. Spin qubits in graphene quantum dots. Nat. Phys. 2007;3:192–196. doi: 10.1038/nphys544. [DOI] [Google Scholar]

- 45.Eich M, et al. Spin and valley states in gate-defined bilayer graphene quantum dots. Phys. Rev. X. 2018;8:031023. [Google Scholar]

- 46.Banszerus L, et al. Single-electron double quantum dots in bilayer graphene. Nano Lett. 2020;20:2005–2011. doi: 10.1021/acs.nanolett.9b05295. [DOI] [PubMed] [Google Scholar]

- 47.He Y -M, et al. Single quantum emitters in monolayer semiconductors. Nat. Nanotechnol. 2015;10:497–502. doi: 10.1038/nnano.2015.75. [DOI] [PubMed] [Google Scholar]

- 48.Kennes DM, et al. Moiré heterostructures as a condensed-matter quantum simulator. Nat. Phys. 2021;17:155–163. doi: 10.1038/s41567-020-01154-3. [DOI] [Google Scholar]