Abstract

This paper presents a new mixed-mode universal filter based on a differential difference transconductance amplifier (DDTA). Unlike the conventional transconductance amplifier (TA), this DDTA has both advantages of the TA and the differential difference amplifier (DDA). The proposed filter can offer four-mode operations of second-order transfer functions into a single topology, namely, voltage-mode (VM), current-mode (CM), transadmittance-mode (TAM), and transimpedance-mode (TIM) transfer functions. Each operation mode offers five standard filtering responses; therefore, at least twenty filtering transfer functions can be obtained. For the filtering transfer functions, the matching conditions for the input and passive component are absent. The natural frequency and the quality factor can be set orthogonally and electronically controlled. The performance of the proposed topology was evaluated by PSPICE simulator using the 0.18 µm CMOS technology from the Taiwan Semiconductor Manufacturing Company (TSMC). The voltage supply was 1.2 V and the power dissipation of the DDTA was 66 µW. The workability of the filter was confirmed through experimental test by DDTA-based LM13600 discrete-component integrated circuits.

Keywords: mixed-mode filter, universal filter, differential difference transconductance amplifier, analog signal processing

1. Introduction

Universal filters are basic electronic blocks that usually provide five filtering responses into a single topology, namely, low-pass (LP), high pass (HP), band pass (BP), band stop (BS), and all pass (AP) filters. The applications such as three crossover network high-fidelity loudspeakers [1,2], touch-tone telephone tone decoders [2], and high-order filters [3] require universal filters as the basic building blocks. Moreover, universal filters can be fabricated as commercial programmable filter-integrated circuits [4]. As a commercially available IC, it is valuable if a single IC can provide a multi-mode filter that depends on the applications of the circuit designer. There are many universal filters available in the open literature, for example, see [5,6,7,8,9,10,11,12,13,14]. Considering input and output signals, these universal filters can be classified as four-mode operations as follows: voltage-mode (VM) filter when both input and output signals are in voltage form [5,6]; current-mode (CM) filter when both input and output signals are in current form [7,8]; transadmittance-mode (TAM) filter when the input signal is in voltage form while the output signal is in current form [9,10,11], and finally transimpedance-mode (TIM) filter when the input signal is in current form while the output signal is in voltage form [12,13,14]. It should be noted that the universal filters in [12,13,14] offer only a single-mode filter.

Recently, universal filters that operate as multi-mode filters into a single topology, the so-called mixed-mode universal filters, have been reported [15,16,17,18,19,20,21,22]. Compared with single-mode universal filters in [5,6,7,8,9,10,11,12,13,14,15], mixed-mode universal filters in [15,16,17,18,19,20,21,22] can provide larger filtering responses. Unfortunately, these mixed-mode universal filters cannot realize four modes of operation into a single topology. There are mixed-mode universal filters that can realize VM, CM, TAM, and TIM filters into a single topology available in the literature [23,24,25,26,27,28,29,30,31,32,33,34,35,36,37,38,39,40,41,42,43,44,45]. However, some of these topologies suffer from some drawbacks as follows:

Lack of electronic tunability [24,25,26,27,28,29,34,35,38,39,40,41];

Employment of floating passive components [24,25,26,27,28,29,32,35,38,39,41,44,45,46];

Active or passive component matching condition [24,25,26,27,28,29,30,31,32,33,34,35,37,39,41,44,46];

Input signal matching condition or requirement of a minus-type input signal [30,31,33,34,37,39,45];

Input voltage signal being applied via capacitor or resistor [24,25,26,27,28,29,32,34,35,38,39,41,44,45,46]; and

Inability to provide at least twenty filtering responses into a single topology [23,24,27,29,33,36,38,40,42,45].

A universal filter that allows electronic tunability can offer some advantages such as the ease of compensation when the natural frequency is deviated by the effect of temperature or process variations, while a universal filter without a floating capacitor and resistor and free from the passive component matching condition is more suitable for integrated circuit implementation. A universal filter that requires a minus-type input signal or an input signal matching condition needs additional circuits such as current-mirror for CM operation or inverting amplifier for VM operation. This requirement defects VM operation because many passive components are usually required, unless the universal filter provides a fully differential structure. Finally, a universal filter that provides at least twenty filtering responses means that each operation mode can realize five standard filtering responses; hence, the full capability of the mixed-mode universal filter can be obtained.

This study focused on a mixed-mode universal filter that could realize VM, CM, TAM, and TIM filters into a single topology. Each operation mode could realize five standard filtering responses; thus, twenty filtering responses could be obtained. The active device, named differential difference transconductance amplifier (DDTA), was used in this study. This device employs high-input impedance terminals with the advantage of input voltage arithmetic operation such as the differential difference amplifier (DDA) [47], and the capability of electronic tuning such as the transconductance amplifier. Thus, a DDTA-based circuit is easy for addition and subtraction of voltage signals and possesses an electronic tuning capability [48,49,50,51]. Unlike the standard differential difference transconductance amplifier that was created by two differential pair DDAs followed by the transconductance amplifier presented in [52], the proposed DDTA is based on one multiple-input differential pair DDA [53,54,55,56] that serves as a differential difference transconductance amplifier followed by a voltage buffer. Therefore, the proposed DDTA could reduce the count of active blocks, power dissipation, and chip area as a result of using the multiple-input MOS transistor (MI−MOST) technique [57]. It is worth noting that the MI-MOST comes with several advantages compared with the multiple-input floating-gate (MIFG) transistor [58]. The MIFG transistor uses the charge conversation principle and hence it is incompatible with modern nanoscale gate-leakage CMOS technologies [59]. The MIFG implementation requires two-polysilicon technology, and the remaining residual charge on its gate causes voltage offset. Therefore, a new DDTA-based mixed-mode universal filter that could provide at least twenty filtering responses of VM, CM, TAM, and TIM filters is presented in this paper. The DDTA uses the MI−MOST technique that offers simplification of its overall structure and a reduction in the power dissipation. The proposed mixed-mode universal filter offers the following advantages such as:

electronic tuning capability;

being free from a floating passive component;

being free from a passive component matching condition;

lacking a minus-type input signal or an input signal matching condition;

not applying the input voltage signal via a capacitor or resistor; and

each operation of VM, TAM, CM and TIM offering five standard filtering responses.

The comparison of the proposed filter with the previous mixed-mode universal filters is shown in Table 1. Compared with [30,31] that have equal active and passive components, the proposed filter is free from active and passive component matching conditions as well as the minus-type input signal requirement. Compared with [43] that offers similar performances, the proposed filter employs fewer components and provides more filtering functions. Compared with [44,45,46] that employ fewer devices, the proposed filter applies the input voltage signal via a high-impedance node whereas the filters in [44,45,46] apply the input voltage signal via a capacitor or resistor.

Table 1.

Comparison the proposed filter with the previous mixed-mode universal filter.

| Ref. | No. of Device | Power Supply | No. of C & R | Obtaining Function | PD [mW] |

THD of LP [%] |

BW [kHz] |

(i) | (ii) | (iii) | (iv) | (v) | (vi) |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| [23] 2003 | 4-CCCII | - | 2 & 0 | 14 | - | - | - | Yes | Yes | Yes | Yes | Yes | No |

| [24] 2004 | 5-CCII | - | 2 & 7 | 12 | - | - | - | No | No | No | Yes | No | No |

| [25] 2005 | 4-CFOA | ±12 V | 2 & 9 | 20 | - | - | 112.5 | No | No | No | Yes | No | Yes |

| [26] 2006 | 3-CCII | ±12 V | 3 & 4 | 20 | - | - | - | No | No | No | Yes | No | Yes |

| [27] 2006 | 3-FTFN | - | 2 & 3 | 11 | - | - | 31.8 | No | No | Yes | Yes | No | No |

| [28] 2007 | 2-DDCC | ±1.25 V | 2 & 4 | 20 | - | - | 4.973 × 103 | No | No | No | Yes | No | Yes |

| [29] 2008 | 1-FDCCII | ±1.25 V | 2 & 3 | 17 | - | - | 3.316 × 103 | No | No | No | Yes | No | No |

| [30] 2009 | 5-OTA | ±1.65 V | 2 & 0 | 24 | 30.95 | - | 1 × 103 | Yes | Yes | No | No | Yes | Yes |

| [31] 2010 | 5-OTA | ±1.25 V | 2 & 0 | 20 | - | 0.777@400 mVpp | 1.591 × 103 | Yes | Yes | No | No | Yes | Yes |

| [32] 2010 | 2-CCCII | ±2.5 V | 2 & 1 | 20 | - | <5@500 μApp | 1.27 × 103 | Yes | No | No | Yes | No | Yes |

| [33] 2011 | 3-CCCCTA | ±1 V | 2 & 0 | 16 | 4.84 | - | 1.06 × 103 | Yes | Yes | No | No | Yes | No |

| [34] 2011 | 3-DDCC | ±1.25 V | 2 & 3 | 30 | - | 0.723@60 μApp | 3.978 × 103 | No | Yes | No | No | Yes | Yes |

| [35] 2011 | 3-DDCC | ±1.25 V | 2 & 4 | 20 | - | - | 3.978 × 103 | No | No | No | Yes | No | Yes |

| [36] 2012 | 4-MOCCCII | ±2.5 V | 2 & 0 | 12 | - | - | - | Yes | Yes | Yes | Yes | Yes | No |

| [37] 2013 | 4-MOCCCII | ±1.25 V | 2 & 0 | 20 | - | 0.5@300 μApp | - | Yes | Yes | No | No | Yes | Yes |

| [38] 2015 | 2-CCII | ±1.25 V | 2 & 2 | 11 | - | - | 2 × 103 | No | No | Yes | Yes | No | No |

| [39] 2016 | 1-FDCCII, 1-DDCC | ±0.9 V | 2 & 6 | 46 | - | 2.2@300 mVpp | 1.591 × 103 | No | No | No | No | No | Yes |

| [40] 2016 | 2-DVCC | ±1.25 V | 2 & 3 | 14 | - | - | 3.978 × 103 | No | Yes | Yes | Yes | Yes | No |

| [41] 2016 | 2-FDCCII | ±0.9 V | 2 & 5 | 25 | - | 0.971@200 mVpp | 1.591 × 103 | No | No | No | Yes | No | Yes |

| [42] 2017 | 3-CCCCTA | ±0.9 V | 2 & 0 | 18 | 1.99 | 2.16@500 mVpp | 3.183 × 103 | Yes | Yes | Yes | Yes | Yes | No |

| [43] 2017 | 6-MI-OTA | ±0.5 V | 2 & 0 | 20 | 0.075 | 2@50 mVpp | 1.5 × 103 | Yes | Yes | Yes | Yes | Yes | Yes |

| [44] 2020 | 2-EXCCTA | ±1.25 V | 2 & 4 | 20 | - | <5@520 mVpp | 7.622 × 103 | Yes | No | No | Yes | No | Yes |

| [45] 2021 | 1-EX-CCCII | ±0.5 V | 2 & 1 | 17 | 1.35 | 0.2@520 mVpp | 23 × 103 | Yes | No | Yes | No | No | No |

| [46] 2021 | 1-VD-EXCCII | ±1.25 V. | 2 & 3 | 20 | 5.76 | <7.5@650 mVpp | 8.084 × 103 | Yes | No | No | Yes | No | Yes |

| This study | 5-DDTA | 1.2 V | 2 & 0 | 36 | 0.33 | 1.09@650 mVpp | 1.04 | Yes | Yes | Yes | Yes | Yes | Yes |

Note: PD = power dissipation, THD = total harmonic distortion, and BW = bandwidth.

This paper is organized as follows: in Section 2, the TA-based DDA using MI-MOSTs and the proposed mixed-mode universal filter are presented; Section 3 presents the simulation results and experimental results; and Section 4 concludes the paper.

2. Proposed Circuit

2.1. Proposed Mixed-Mode Universal Filter

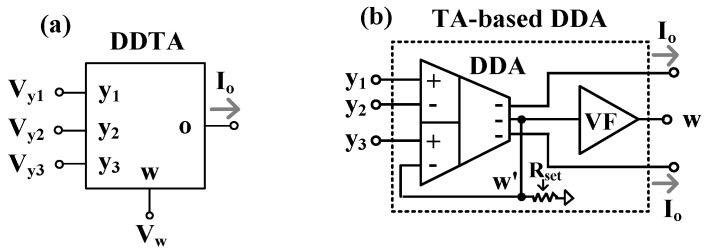

The symbol of DDTA is shown in Figure 1a. The relationship of the terminals can be expressed by

| (1) |

Figure 1.

TA-based DDA: (a) symbol; (b) internal structure.

It should be noted that the output is the addition and subtraction of inputs , and , while the output is the current that is converted from by , where is the internal transconductance of DDTA. Therefore, DDTA included the DDA as an input stage that serves also as a transconductance amplifier (TA) as an output stage. Compared with the differential difference current conveyor transconductance amplifier (DDCCTA) [60], the DDTA structure employs less MOS transistors. Figure 1b shows the internal structure of the proposed DDTA. The voltage follower (VF) circuit was used to avoid the loading effect. Therefore, the w-terminal possessed a low-impedance level that could be directly connected to a low-resistance external load.

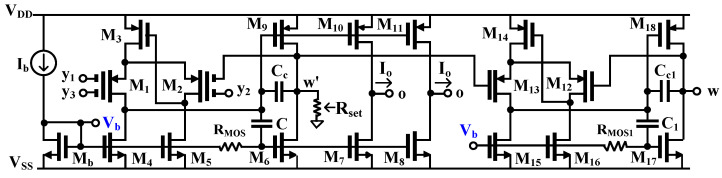

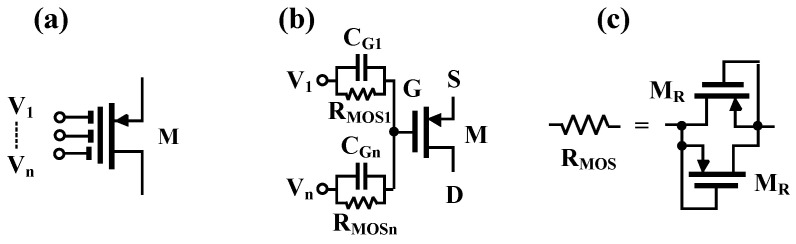

The structure of DDTA in [52] was developed to the DDTA using MI-MOST as shown in Figure 2. Figure 3a shows the MI-MOST symbol with n number of inputs where the input terminals V1, …, Vn are coupled to the gate terminal of the conventional MOST by n input capacitors CG1, …, CGn. To guarantee the DC operation, the high resistances RMOS1, …, RMOSn are connected in parallel to each input capacitor, as shown in Figure 3b. The high resistance is implemented by two MOSTs (MR) operating in the cut-off region as shown in Figure 3c, which offers a minimum area of chip. It is worth noting that the pseudo-resistors shunt the input capacitors for proper DC operation of the input transistor; therefore, there are no floating-gate issues as in the case of the MIFG transistor. However, for AC operation, the input capacitors create a short circuit for the AC signal, the same as in the case of the MIFG technique.

Figure 2.

TA-based DDA using MI-MOSTs.

Figure 3.

MI-MOST: (a) symbol; (b) realization; (c) realization of the large resistance value.

It is worth noting that the multiple input techniques are simply created by a set of parallel capacitors shunted with high-resistance pseudo-resistors (MR). This technique can be applied to the gate-, bulk-, gate-bulk (DTMOS), or bulk-quasi-floating-gate terminals of a standard MOS transistor [61].

In Figure 2, the transistors M1–M6 and M9 create the DDA core circuit. The MI-MOST differential pairs M1 and M2, the transistor M3, and the two current sources M4 and M5 create the differential stage of the DDA. The transistor M3 along with M2 and M5 create a flipped voltage follower (FVF) [62] and it is used to enforce the current of M3 (i.e., IM3) to be equal to the tail current, same as in the case of the differential stage of the conventional structure. The FVF modifies the gate of M3 to ensure equal drain currents for both differential pairs M1 and M2 [63]. Furthermore, due to the FVF, the minimum voltage supply is the sum of one gate-source and one drain-source voltage ().

Transistors M6 and M9 form a super class AB second stage [64]. The is responsible for the gate DC biasing of the transistor M6, whereas the capacitor C delivers the AC signal to this gate. The node is connected to the input terminal of M2, creating negative feedback for obtaining a unity-gain voltage follower. The DDA stability is insured by the compensation capacitor Cc. The transistors M12–M18, RMOS1, and capacitors Cc1 and C1 are used to work as a voltage follower circuit. The operation is similar to the first stage of DDTA that was previously explained. Therefore, the relationship () can be obtained. The bias current and Mb generated the bias voltage for M4−M8 and M15−M17. The terminal is connected to a linear adjustable resistor that converts the voltage to current . This current is mirrored by M7−M10 to the o-terminals; thus, can be achieved. Additional output current o-terminals can be obtained using complementary transistors such as M8 and M11. Hence, this part works as a transconductance amplifier. The output current is obtained as

| (2) |

| (3) |

| (4) |

Note that the high linearity is achieved due to the linear resistance Rset. The DDA operates in a closed loop, just forming a second-generation current conveyor, with the output terminal loaded by Rset, and such a configuration can be considered as a transconductance amplifier. However, the attenuation of the input signal by capacitors allows enlarging the input common mode range, as well as the range of linear operation (the range where the so-called hard nonlinearities associated with changing the region of operation of transistors do not appear).

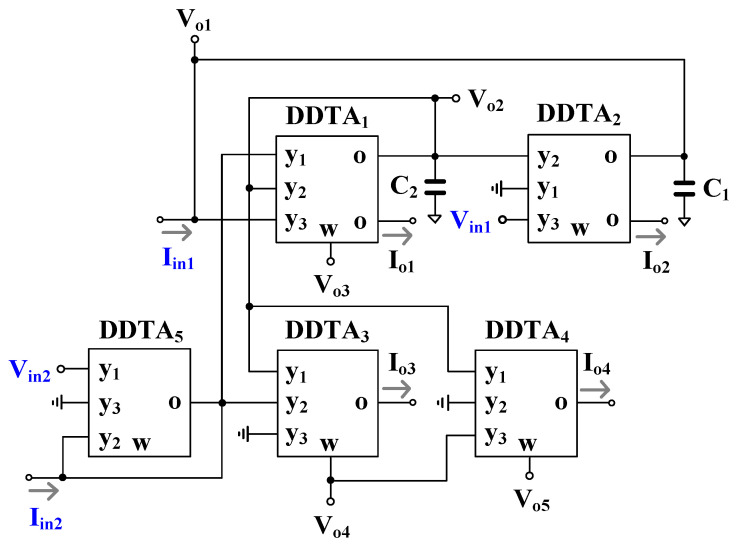

The proposed mixed-mode universal filter using DDTAs is shown in Figure 4. It consisted of five DDTAs and two grounded capacitors. The variant transfer functions could be obtained by applying the appropriate input signals , and and selecting the appropriate output signals , and . The input voltage which is not used () should be attached to ground while the input current which is not used () should be floated. The () is the transconductance of (). Using (1) and nodal analysis, the output voltages and currents of the proposed mixed-mode universal filter can be expressed by

| (5) |

| (6) |

| (7) |

| (8) |

| (9) |

| (10) |

| (11) |

| (12) |

| (13) |

where . By appropriately applying the input signals (, , , and ) and choosing the output terminals (, , , , , , , , and ), the VM, CM, TAM, and TIM filters can be expressed as in Table 2. It was evident that the proposed filter offers four modes of operation into a single topology. Each mode of operation provides five standard filtering transfer functions; hence, at least twenty transfer functions can be obtained. In addition, several filtering functions can be obtained from the same mode of operation; thus, the proposed topology can provide 36 filtering functions.

Figure 4.

Proposed mixed-mode universal filter using DDTAs.

Table 2.

Parameters of the components of DDTA in Figure 2.

| Transistor | W/L (µm/µm) |

|---|---|

| M1, M2, M13, M12 | 9 × 9/0.3 |

| M3, M14 | 15/0.3 |

| Mb, M4, M5, M15, M16 | 12/3 |

| M6, M7, M8, M17 | 2 × 12/3 |

| M9, M10, M11, M18 | 2 × 25/2 |

| MR | 4/5 |

| CG = 0.5 pF, Cc = C = 2.6 pF | |

It should be noted that some filtering functions offer some advantages such as the gain of transfer function when is the input and is the output for LP of the VM filter, the high-Q filter when = is the input and is the output for BP of the VM filter, and offer both non-inverting and inverting filtering functions for HP of TAM filter.

The natural frequency () and the quality factor () of the proposed filter can be given as

| (14) |

| (15) |

From (14) and (15), the parameter can be adjusted electronically by and whereas the parameter can be given by by keeping = . Thus, the proposed filter can be electronically controlled for parameter and orthogonally controlled for parameters and .

It should be noted that the terminals , , and possess low-output impedance whereas the terminals , , , and possess a high-output impedance, and thus the loads can be connected directly without additional buffer circuit requirements. The terminals and possess a high-input impedance, hence the condition such as = is not required for additional buffer circuits. However, the terminals and do not provide a low-output impedance and the terminals and do not provide a low-input impedance; therefore, the buffer circuits may be required if low-impedance loads are connected and if low-impedance current signals are supplied. In the case of CM and TIM filters, the matching condition is absent and in the case of VM and TAM, the inverting-type input is not used.

2.2. Non-Ideality Analysis

Considering non-idealities of DDTA, (1) can be rewritten as

| (16) |

where and ) denote the voltage tracking error from to of -th DDTA, and ) denote the voltage tracking error from to of -th DDTA and and ) denote the voltage tracking error from to of -th DDTA.

The non-ideal transconductance gain is given by

| (17) |

where and denote the first-order pole frequency and the open-loop transconductance gain of -th DDTA.

The non-ideal transconductance gain of DDTA is caused by the parasitic capacitor and parasitic resistor at o-terminal. In the frequency range that can generate these parasitic parameters, can be modified as [65]

| (18) |

where .

The filter in Figure 4 was re-analyzed by using (16), and the denominator of the transfer functions can be rewritten as

| (19) |

Using (18), (19) becomes

| (20) |

From (20), the non-idealities of the DDTAs affect the circuit characteristics which depart from ideal values. The parasitic effects from the DDTA could be made negligible by satisfying the following condition:

| (21) |

| (22) |

Therefore, the non-ideal natural frequency () and the non-ideal quality factor () can be expressed, respectively, by

| (23) |

| (24) |

The sensitivity of the and with respect to circuit components and non-ideal parameters can be expressed as follows:

| (25) |

| (26) |

| (27) |

It can be expressed from (25)–(27) that the proposed filter showed good active and passive sensitivities because all the sensitivities were within unity in magnitude.

3. Results

3.1. Simulation Results

The DDTA in Figure 2 was designed using a 1.2 V voltage supply (VDD = −VSS = 0.6 V) and 5 µA bias current. The circuit consumed 66 µW of power. The PSPICE simulation was used to simulate the circuit using a 0.18 µm CMOS technology from TSMC. The parameters of the components and the simulated performances of the used DDTA are shown in Table 2 and Table 3, respectively.

Table 3.

Simulated parameters of used DDTA.

| Parameters | Simulated Value |

|---|---|

| Technology | 0.18 μm |

| Supply voltage | 1.2 V (±0.6 V) |

| Static power consumption | 66 μW |

| Transconductance | 1/Rset |

| −3 dB bandwidth | |

| Vw/Vy1, Vw/Vy2, Vw/Vy3 | 2.4 MHz |

| Io/Vy1 (Rset = 15 kΩ) | 6.4 MHz |

| Voltage gain: Vw/Vy1, Vw/Vy2, Vw/Vy3 | 0.988 |

| DC voltage range (Rset = 15 kΩ) | ±100 mV |

| DC offset | −0.13 mV |

| Rw&Lw | 1.25 kΩ & 0.4 mH |

| Ro//Co | 947.78 kΩ//0.22 pF |

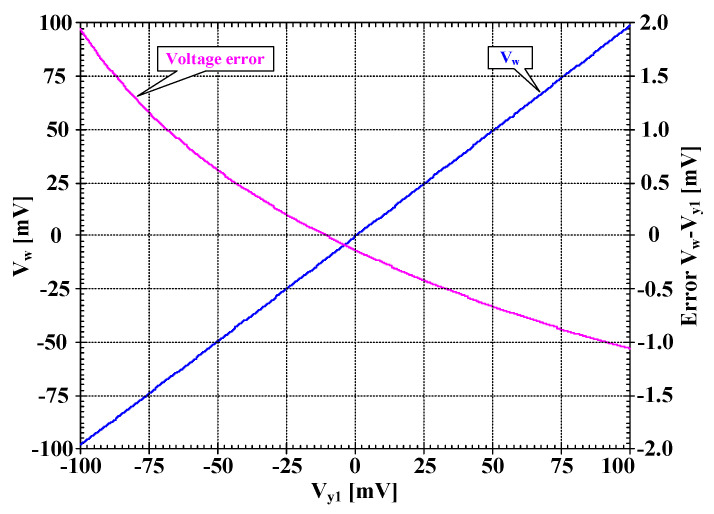

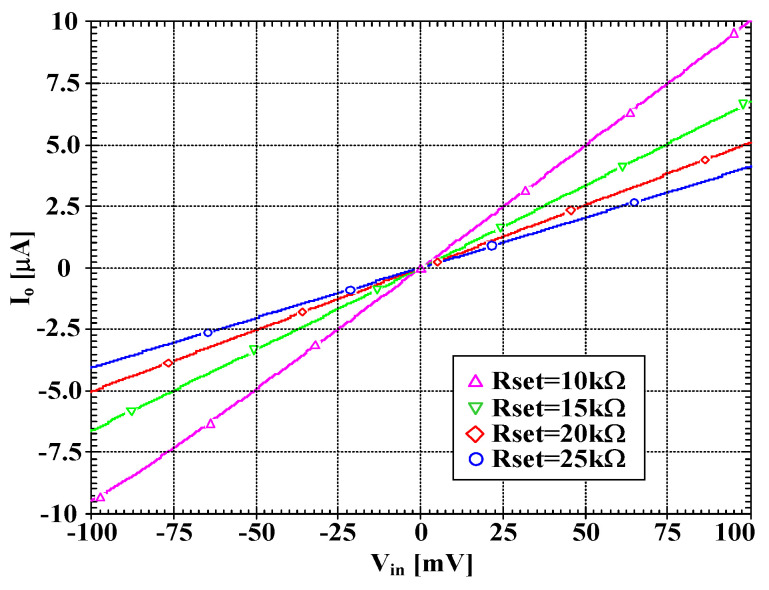

Figure 5 shows the relation between voltages and with = 15 kΩ and its voltage error. At = 0 mV, the voltage error was −0.13 mV and at = ±100 mV, the voltage error was less than 2 mV. To show the voltage-to-current converter of DDTA, the voltage ( = ) was applied to the input, and the current at o-terminal was measured. Figure 6 shows the relation between Io and Vin with different values of ( = 10, 15, 20, 25 kΩ). The transconductances of DDTA can be given by ( = ). The simulated performances of DDTA in Figure 2 are summarized in Table 3.

Figure 5.

The simulated large signal DC transfer characteristic VW = f(Vy1) and the corresponding error.

Figure 6.

The simulated large-signal DC transfer characteristic Io = f(Vin) for different values of Rset.

The proposed mixed-mode filter in Figure 4 was designed for obtaining 1 kHz of the natural frequency. The capacitors 10 nF and 15 kΩ. These resistors can be integrated on chip using a high-resistance poly resistor; however, the high value 10 nF capacitors should be off-chip.

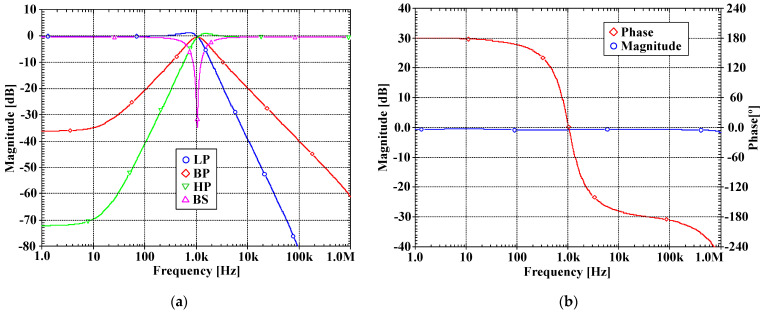

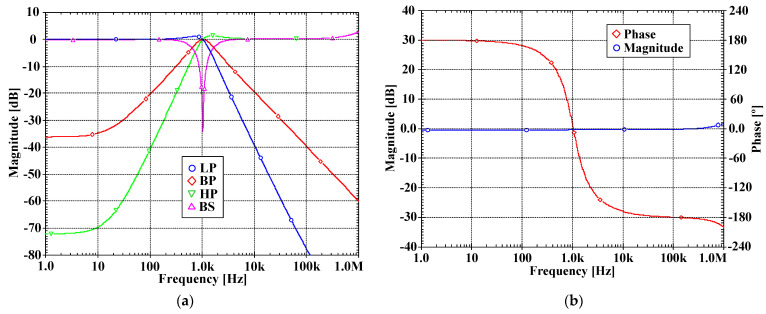

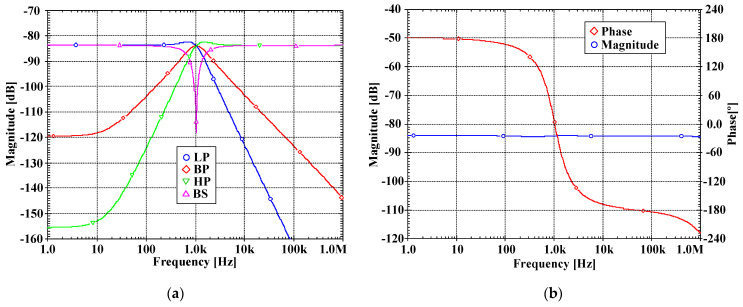

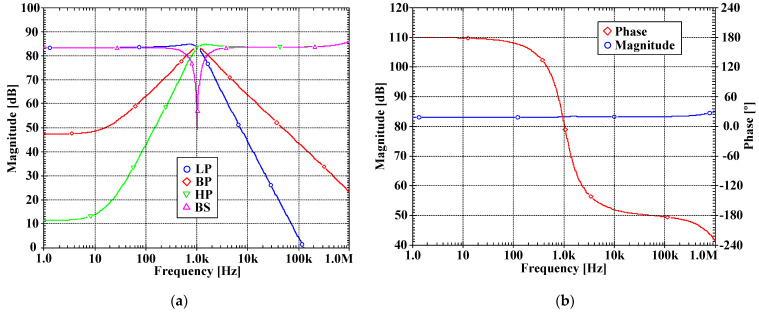

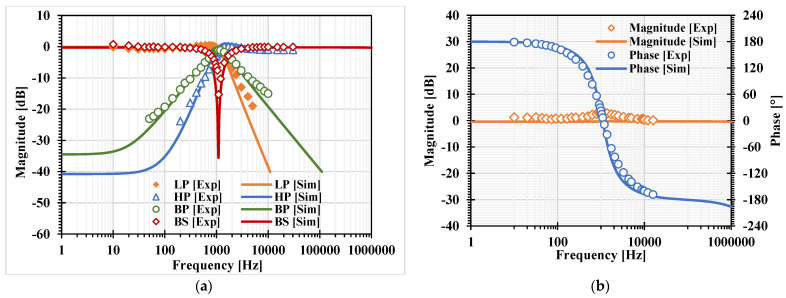

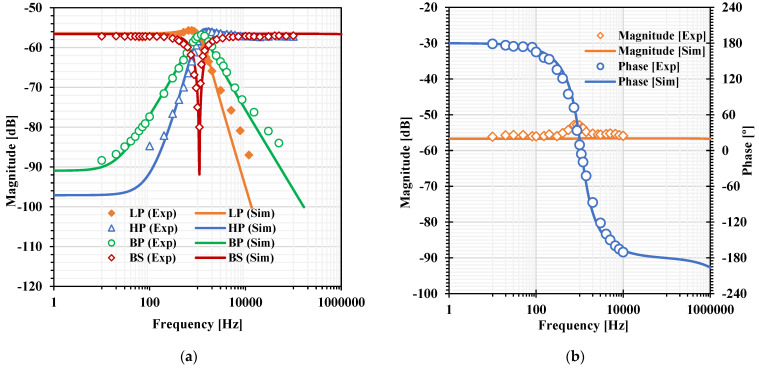

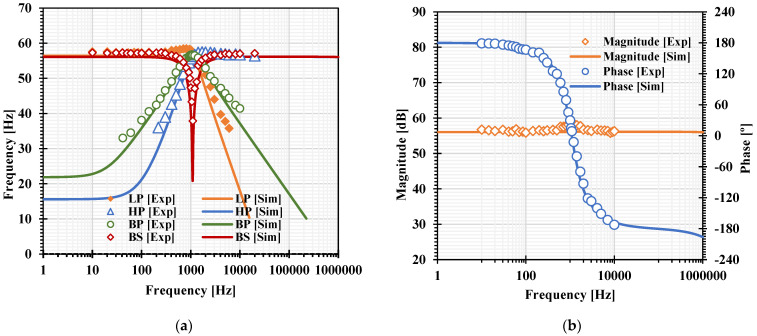

Figure 7a, Figure 8a, Figure 9a and Figure 10a show, respectively, the simulated magnitude frequency responses of the LP, HP, BP, and BS responses of the VM, CM, TAM, and TIM filters. The natural frequency of these results was 1.04 kHz. The simulated magnitude and phase characteristics of the AP filter of the VM, CM, TAM, and TIM filters are shown respectively in Figure 7b, Figure 8b, Figure 9b and Figure 10b. The total power consumption of the filter was 330 µW. It can be confirmed from Figure 7, Figure 8, Figure 9 and Figure 10 that the proposed mixed-mode filter provides five standard filtering responses of VM, CM, TAM, and TIM filters.

Figure 7.

The simulated frequency responses of the VM filter: (a) LP, BP, HP, BS filters; (b) AP filter.

Figure 8.

The simulated frequency responses of the CM filter: (a) LP, BP, HP, BS filters; (b) AP filter.

Figure 9.

The simulated frequency responses of the TAM filter: (a) LP, BP, HP, BS filters; (b) AP filter.

Figure 10.

The simulated frequency responses of the TIM filter: (a) LP, BP, HP, BS filters; (b) AP filter.

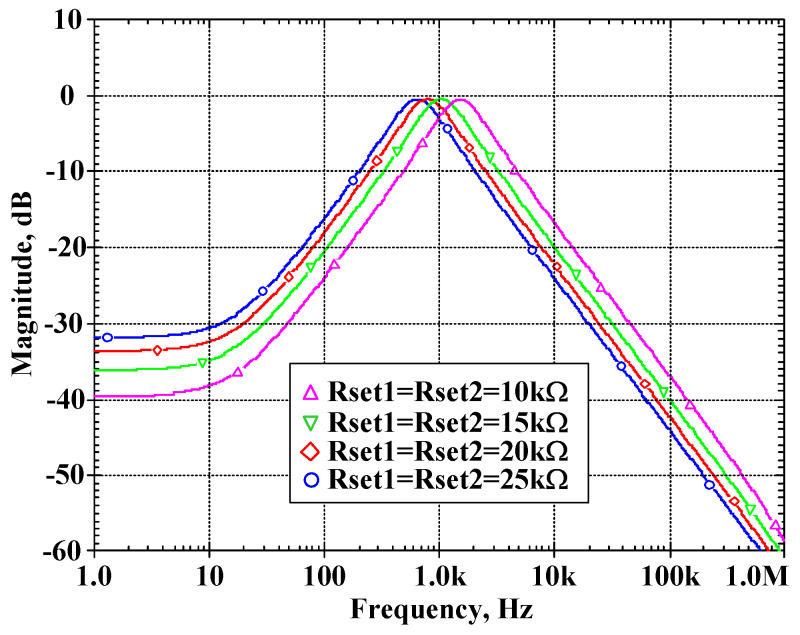

To confirm that the proposed filter provided electronic tuning ability, the BP filter was simulated by adjusting = = 10 kΩ, 15 kΩ, 20 kΩ, 25 kΩ while = = = 15 kΩ. Figure 11 shows the center frequency of 0.64 kHz, 0.79 kHz, 1.04 kHz, and 1.51 kHz when the resistance = was 25 kΩ, 20 kΩ, 15 kΩ, and 10 kΩ, respectively.

Figure 11.

The simulated frequency responses of the VM BP filter when variation in fo by ( = = 10 kΩ, 15 kΩ, 20 kΩ and 25 kΩ while = = = 15 kΩ).

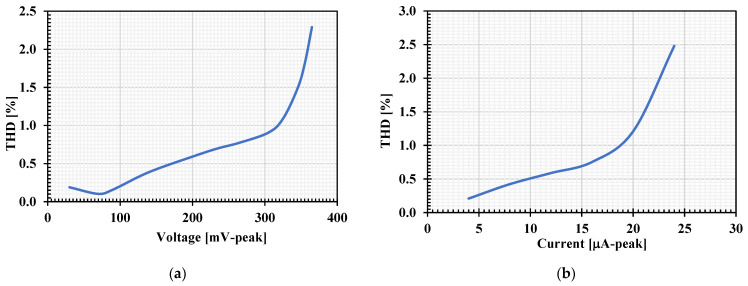

The total harmonic distortion (THD) of the LP response of VM and CM filters was investigated by applying the single-tone input signal of 100 Hz to the input. The simulated THDs of VM and CM filters with different amplitudes are respectively shown in Figure 12a,b. The THD was less than 1.09% for input amplitude of 325 mV (peak) of the VM filter and the THD was less than 1.21 for input amplitude of 20 A (peak) of the CM filter. The RMS output noise of the LP filter integrated in the bandwidth of 1 kHz was performed and the value of this noise was 150 µV. Thus, the dynamic range for 1.09% THD was 63.69 dB.

Figure 12.

The simulated THD of the LP filters with different amplitude of input signal at 100 Hz: (a) VM filter; (b) CM filter.

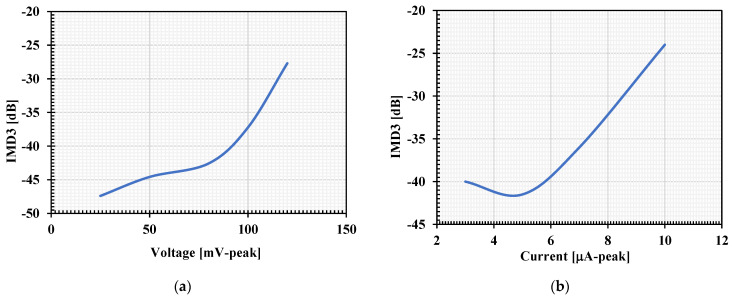

The proposed filter was investigated by applying two tones closely spaced in frequency into the input of the BP filter and the third-order distortion products (IMD3s) produced by the circuit nonlinearity were determined. In this case, the IMD3 of the VM and CM filters was investigated by applying the first tone with a sine wave frequency of 0.9 kHz and the second tone with 1.1 kHz. The simulated IMD3s of the VM and CM filters are respectively shown in Figure 13a,b. The IMD3 was around −37.23 dB for 100 mV (peak) of the VM filter and the IMD3 was around −36 dB for 7 μA (peak) of the CM filter.

Figure 13.

The simulated IMD3 versus the input signal for the BP filters: (a) voltage (Vin-peak); (b) voltage (Iin-peak).

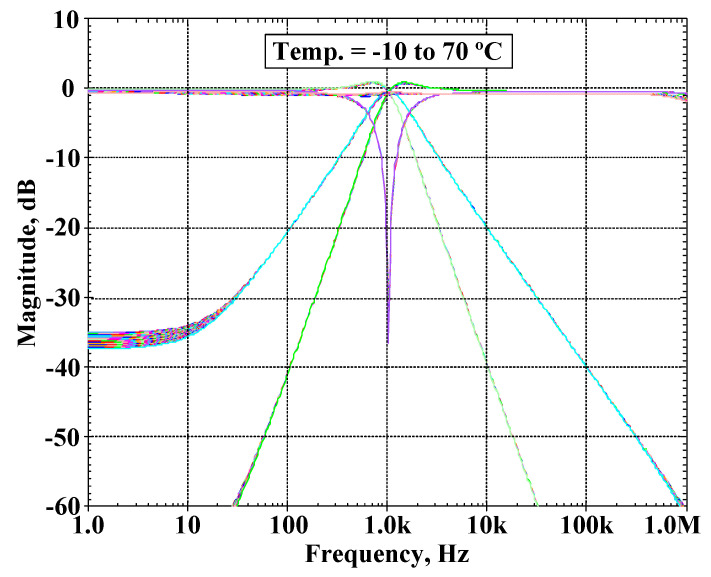

The VM filter was used to test its temperature performance. The simulated magnitude frequency responses of the LP, BP, HP, BS, and AP filter when the temperature was varied from −10 to 70 °C are shown in Figure 14. The proposed filter was also investigated using a Monte Carlo analysis by assuming that the fluctuation of the natural frequency changes caused by deviation of the capacitors and the threshold voltage of the MOS transistor. The BP response of the VM filter was simulated by setting 5% tolerances of the capacitors C1 and C2 and 5% variations of the transistor threshold voltage at 1.04 kHz, Q ≅ 1, and 200 Gaussian distribution runs. Figure 15 shows the derived histogram of the natural frequency which expressed that the standard deviation (σ) of fo was 33.339 Hz and the maximal and minimal values of fo were 1.132 kHz and 0.967 kHz, respectively.

Figure 14.

The simulated magnitude frequency responses of the universal filter with temperature variation.

Figure 15.

The histogram of the cutoff frequency of the universal filter with 200 runs of MC analysis.

3.2. Experimental Results

The proposed mixed-mode universal filter was also tested experimentally to confirm its functionality. The simulation results based on the macro model and the measured results are included for comparison. The DDTA was realized using OTAs as shown in Figure 16 [52]. The prototype circuit was realized using commercially available integrated circuit LM13700N that consists of two current-controlled transconductance amplifiers. Note the benefit of the MI-MOST on the TA-based DDA in Figure 2 in simplifying the CMOS structure and reducing the number of ICs needed to build the filter application. For instance, to create the multiple input (y1, y2, and y3) of the DDA in Figure 16, two transconductance amplifiers (OTA1, OTA2) are needed and another two OTAs are needed to construct the TA, hence two LM13700Ns are needed for each DDTA.

Figure 16.

OTA-based DDTA [52].

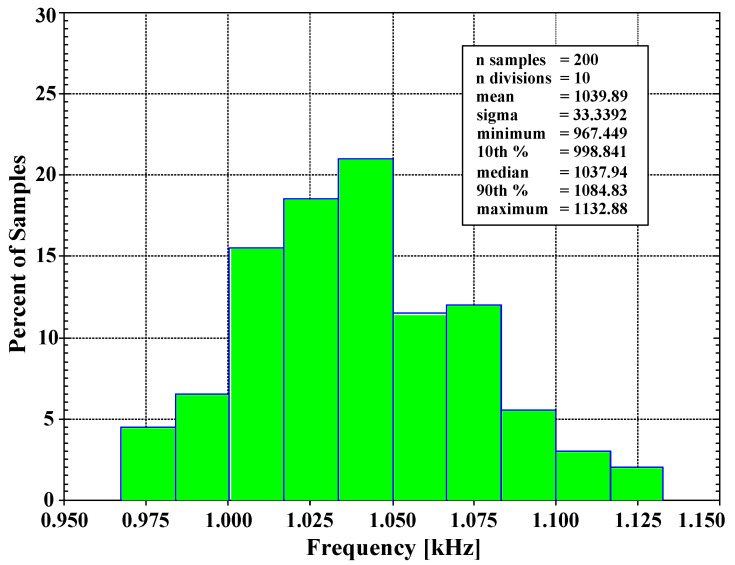

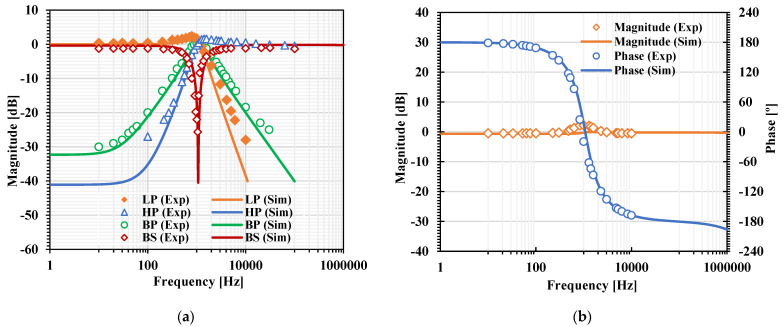

For measurement setup, the supply voltage was ±5 V and the capacitances C1 and C2 were 220 nF. The Agilent Technology DSOX 1102G oscilloscope was used for supplying the sinusoidal input signal and measuring the output waveforms. The transconductances = = = = = 1.51 mS were designed to obtain the mixed-mode filter with the natural frequency of 1.09 kHz and the quality factor of 1 ( 1). Figure 17a, Figure 18a, Figure 19a and Figure 20a show the experimental frequency responses of the LP, HP, BP, and BS responses of the VM, CM, TAM, and TIM filters, respectively. Figure 17b, Figure 18b, Figure 19b and Figure 20b show the experimental frequency response of magnitude and phase characteristics of the AP responses of the VM, CM, TAM, and TIM filters, respectively. To measure the frequency responses of TAM filter, a resistor was used to convert the output current to voltage, and the voltage according to this resistance was calculated to the output current for plotting. In case of CM and TIM filters, the high resistances (i.e., ≫ 662 Ω) were used to convert the input voltage to the input current at input terminals and convert the output current to the output voltage output terminals. The voltage according to the resistances was calculated as currents for plotting.

Figure 17.

Experimental frequency responses of the VM filter: (a) LP, BP, HP, BS filters; (b) AP filter.

Figure 18.

Experimental frequency responses of the CM filter: (a) LP, BP, HP, BS filters; (b) AP filter.

Figure 19.

Experimental frequency responses of the TAM filter: (a) LP, BP, HP, BS filters; (b) AP filter.

Figure 20.

Experimental frequency responses of the TIM filter: (a) LP, BP, HP, BS filters; (b) AP filter.

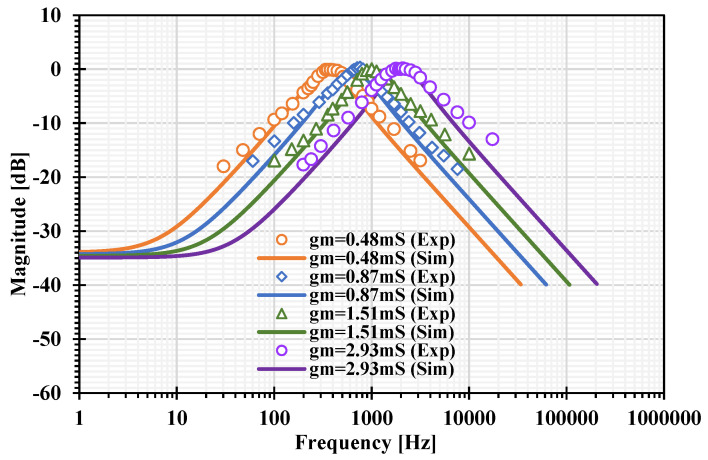

The experimental frequency responses of the BP response of the VM filter with different transconductances ( = 0.48 mS, 0.87 mS, 1.51 mS, and 2.93 mS) are shown in Figure 21. This result was used to confirm that the proposed mixed-mode filter provides an electronic tuning ability without drubbing the quality factor. The Experimental setup of the universal filter is shown in Figure S1 in the Supplementary Materials.

Figure 21.

The experimental frequency responses of the BP response of the VM filter with different transconductances.

4. Conclusions

A new mixed-mode universal filter using five DDTAs and two grounded capacitors was shown in this paper. The proposed filter offers 36 filtering responses into a single topology using the DDTA-based circuit. The natural frequency and the quality factor can be set orthogonally and electronically controlled. The performance of the proposed filter was evaluated in PSPICE simulation using the TSMC 0.18 µm CMOS technology and investigated by experiment tests using LM13600 discrete component integrated circuit as DDTAs. The simulation results were in agreement with the experimental results.

Supplementary Materials

The following supporting information can be downloaded at: https://www.mdpi.com/article/10.3390/s22093535/s1, Figure S1: Experimental setup of the universal filter.

Author Contributions

Conceptualization, F.K. and M.K.; methodology, M.K. and T.K.; software, M.K. and P.S.; expermentation, F.K.; validation, F.K., P.S. and M.K.; formal analysis, M.K. and T.K.; investigation, F.K., M.K. and T.K.; writing—original draft preparation, M.K. and F.K.; writing—review and editing, M.K., F.K. and T.K. All authors have read and agreed to the published version of the manuscript.

Conflicts of Interest

The authors declare no conflict of interest.

Funding Statement

This work was supported by King Mongkut’s Institute of Technology Ladkrabang under Grant KREF026201, and by the University of Defence Brno within the Organization Development Project VAROPS.

Footnotes

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

References

- 1.Wang S.-F., Chen H.-P., Ku Y., Le C.-L. Versatile voltage-modde biquadratic filter and quadrature oscillator using four OTAs and two grounded capacitors. Electronics. 2020;9:1493. doi: 10.3390/electronics9091493. [DOI] [Google Scholar]

- 2.Alexander C.K., Sadiku M.N.O. Fundamentals of Electric Circuits. 6th ed. McGraw-Hill; New York, NY, USA: 2017. pp. 658–660. [Google Scholar]

- 3.Li Y. A modified CDTA (MCDTA) and its applications: Designing Current-Mode Sixth-Order Elliptic Band-Pass Filter. Circuits Syst. Signal Process. 2011;30:1383–1390. doi: 10.1007/s00034-011-9329-2. [DOI] [Google Scholar]

- 4.MAX260 Maxim Integrated. [(accessed on 5 January 2022)]. Available online: https://www.maximintegrated.com/en/products/analog/analog-filters/MAX260.html.

- 5.Psychalinos C., Kasimis C., Khateb F. Multiple-input single-output universal biquad filter using single output operational transconductance amplifiers. Int. J. Electron. Commun. 2018;93:360–367. doi: 10.1016/j.aeue.2018.06.037. [DOI] [Google Scholar]

- 6.Wang S.-F., Chen H.-P., Ku Y., Yang C.-M. Independently tunable voltage-mode OTA-C biquadratic filter with five inputs and three outputs and its fully-uncoupled quadrature sinusoidal oscillator application. AEU Int. J. Electron. Commun. 2019;110:152822. doi: 10.1016/j.aeue.2019.152822. [DOI] [Google Scholar]

- 7.Kumar A., Paul S.K. Nth order current mode universal filter using MOCCCIIs. Analog. Integr. Circuits Signal Process. 2018;95:181–193. doi: 10.1007/s10470-018-1127-3. [DOI] [Google Scholar]

- 8.Tangsrirat W., Channumsin O. Minimum-component current-mode universal filter. Indian J. Pure Appl. Phys. 2021;49:137–141. [Google Scholar]

- 9.Shah N., Iqbal S., Parveen B. SITO high output impedance transadmittance filter using FTFNs. Analog. Integr. Circuits Signal Process. 2004;40:87–89. doi: 10.1023/B:ALOG.0000031438.72455.b1. [DOI] [Google Scholar]

- 10.Shah N.A., Quadri M., Iqbal S.Z. CDTA based universal transadmittance filter. Analog. Integr. Circuits Signal Process. 2007;52:65–69. doi: 10.1007/s10470-007-9091-3. [DOI] [Google Scholar]

- 11.Lee C.-N. High-order multiple-mode and transadmittance-mode OTA-C universal filters. J. Circuits Syst. Comput. 2012;21:1250048. doi: 10.1142/S021812661250048X. [DOI] [Google Scholar]

- 12.Horng J.-W. High-order current-mode and transimpedance-mode universal filters with multiple-inputs and two-outputs using MOCCIIs. Radioenineering. 2009;18:537–543. [Google Scholar]

- 13.Horng J.-W., Herencsar N., Wu C.-M. Current-mode and transimpedance-mode universal biquadratic filter using two current conveyors. Indian J. Eng. Mater. Sci. 2017;24:461–468. [Google Scholar]

- 14.Cevik I., Metin B., Herencsar N., Cicekoglu O., Kuntman H. Transimpedance type MOS-C bandpass analog filter core circuits. Analog. Integr. Circuits Signal Process. 2021;106:543–551. doi: 10.1007/s10470-020-01754-2. [DOI] [Google Scholar]

- 15.Abuelma’atti M.T., Bentrcia A., Shahrani S.M.A. A novel mixed-mode current-conveyor-based filter. Int. J. Electron. 2004;91:191–197. doi: 10.1080/00207210410001677039. [DOI] [Google Scholar]

- 16.Bhaskar D.R., Singh A.K., Sharma R.K., Senani R. New OTA-C universal current-mode/trans-admittance biquads. IEICE Electron. Express. 2005;2:8–13. doi: 10.1587/elex.2.8. [DOI] [Google Scholar]

- 17.Minaei S., Ibrahim M.A. A mixed-mode KHN-biquad using DVCC and grounded passive elements suitable for direct cascading. Int. J. Circuit Theory Appl. 2008;37:793–810. doi: 10.1002/cta.493. [DOI] [Google Scholar]

- 18.Zhijun L. Mixed-mode universal filter using MCCCII. Int. J. Electron. Commun. 2009;63:1072–1075. doi: 10.1016/j.aeue.2008.09.003. [DOI] [Google Scholar]

- 19.Shah N.A., Rather M.F. Design of voltage-mode, trans-admittance-mode, trans-impedance-mode and current-mode biquad filter employing plus type current feedback amplifiers. J. Act. Passiv. Devices. 2010;5:29–46. [Google Scholar]

- 20.Yesil A., Kacar F. Electronically tunable resistorless mixed-mode biquad filters. Radioengineering. 2013;22:1016–1125. [Google Scholar]

- 21.Kumngern M., Junnapiya S. Mixed-mode universal filter using OTAs; Proceedings of the 2012 IEEE International Conference on Cyber Technology in Automation, Control, and Intelligent Systems (CYBER); Bangkok, Thailand. 27–31 May 2012; pp. 119–122. [Google Scholar]

- 22.Bhaskar D.R., Raj A., Kumar P. Mixed-mode universal biquad filter using OTAs. J. Circuits Syst. Comput. 2020;29:2050162. doi: 10.1142/S0218126620501625. [DOI] [Google Scholar]

- 23.Abuelma’atti M.T. A novel mixed-mode current-controlled current-conveyor-based filter. Act. Passiv. Electron. Compon. 2003;26:185–191. doi: 10.1080/1042015031000073841. [DOI] [Google Scholar]

- 24.Abuelma’atti M.T., Bentrcia A. A novel mixed-mode CCII-based filter. Act. Passiv. Electron. Compon. 2004;27:197–205. doi: 10.1080/08827510310001648933. [DOI] [Google Scholar]

- 25.Singh V.K., Singh A.K., Bhaskar D.R., Senani R. Novel mixed-mode universal biquad configuration. IEICE Electron. Express. 2005;2:548–553. doi: 10.1587/elex.2.548. [DOI] [Google Scholar]

- 26.Pandey N., Paul S.K., Bhattacharyya A., Jain S.B. A new mixed mode biquad using reduced number of active and passive elements. IEICE Electron. Express. 2006;3:115–121. doi: 10.1587/elex.3.115. [DOI] [Google Scholar]

- 27.Shah N.A., Malik M. Multifunction mixed-mode filter using FTFNs. Analog. Integr. Circuits Signal Process. 2006;47:339–343. doi: 10.1007/s10470-006-5539-0. [DOI] [Google Scholar]

- 28.Horng J.W. Multiple-mode universal biquad filter using two DDCCs. Int. J. Electr. Eng. 2007;14:219–297. [Google Scholar]

- 29.Lee C.-N., Chang C.-M. Single FDCCII-based mixed-mode biquad filter with eight outputs. Int. J. Electron. Commun. 2008;63:736–742. doi: 10.1016/j.aeue.2008.06.015. [DOI] [Google Scholar]

- 30.Chen H.P., Liao Y.Z., Lee W.T. Tunable mixed-mode OTA-C universal filter. Analog. Integr. Circuits Signal Process. 2009;58:135–141. doi: 10.1007/s10470-008-9228-z. [DOI] [Google Scholar]

- 31.Lee C.N. Multiple-mode OTA-C universal biquad filters. Circuits Syst. Signal Process. 2010;29:263–274. doi: 10.1007/s00034-009-9145-0. [DOI] [Google Scholar]

- 32.Pandey N., Paul S.K., Bhattacharyya A., Jain S.B. Realization of generalized mixed mode universal filter using CCCIIs. J. Act. Passiv. Electron. Devices. 2010;5:279–293. [Google Scholar]

- 33.Maheshwari S., Singh S.V., Chauhan D.S. Electronically tunable low-voltage Mixed-mode universal biquad filter. IET Circuits Devices Syst. 2011;5:149–158. doi: 10.1049/iet-cds.2010.0061. [DOI] [Google Scholar]

- 34.Lee C.-N. Fully cascadable mixed-mode universal filter biquad using DDCCs and grounded passive components. J. Circuits Syst. Comput. 2011;20:607–620. doi: 10.1142/S0218126611007499. [DOI] [Google Scholar]

- 35.Liao W.B., Gu J.C. SIMO type universal mixed-mode biquadratic filter. Indian J. Eng. Mater. Sci. 2011;18:443–448. [Google Scholar]

- 36.Pandey N., Paul S.K. SIMO mixed mode universal filter. J. Act. Passiv. Electron. Devices. 2012;7:215–226. [Google Scholar]

- 37.Pandey N., Paul S.K. Mixed mode universal filter. J. Circuits Syst. Comput. 2013;22:1250064. doi: 10.1142/S0218126612500648. [DOI] [Google Scholar]

- 38.Lee C.N. MISO type mixed-mode biquad filter using basic active elements. Int. J. Emerg. Technol. Adv. Eng. 2015;5:309–315. [Google Scholar]

- 39.Lee C.N. Independently tunable mixed-mode universal biquad filter with versatile input/output function. Int. J. Electron. Commun. 2016;70:1006–1019. doi: 10.1016/j.aeue.2016.04.006. [DOI] [Google Scholar]

- 40.Lee C.N. Mixed-mode biquadratic filter using only two DVCC and grounded passive components. Int. J. Emerg. Technol. Adv. Eng. 2016;6:228–234. [Google Scholar]

- 41.Lee C.N. Mixed-Mode universal biquadratic filter with no need of matching conditions. J. Circuits Syst. Comput. 2016;25:1650106. doi: 10.1142/S0218126616501061. [DOI] [Google Scholar]

- 42.Chen H.P., Yang W.S. Electronically tunable current controlled current conveyor transconductance amplifier-based mixed-mode biquadratic filter with resistorless and grounded capacitors. Appl. Sci. 2017;7:244. doi: 10.3390/app7030244. [DOI] [Google Scholar]

- 43.Parvizi M., Taghizadeh A., Mahmoodian H., Kozehkanani Z.D. A low-power mixed-mode SIMO universal Gm-C filter. J. Circuits Syst. Comput. 2017;26:1750164. doi: 10.1142/S021812661750164X. [DOI] [Google Scholar]

- 44.Albrni M.I.A., Mohammad F., Herenscar N., Sampe J., Ali S.H.M. Novel electronically tunable biquadratic mixed-mode universal filter capable of operating in MISO and SIMO configurations. J. Microelectron. Electron. Compon. Mater. 2020;50:189–203. [Google Scholar]

- 45.Agrawal D., Maheshwarl S. High-performance electronically tunable analog filter using a single EX-CCCII. Circuits Syst. Singnal Process. 2021;40:1127–1151. doi: 10.1007/s00034-020-01530-7. [DOI] [Google Scholar]

- 46.Faseehuddin M., Herencsar N., Albrni M.A., Sampe J. Electronically tunable mixed-mode universal filter employing a single active block and a minimum number of passive components. Appl. Sci. 2021;11:55. doi: 10.3390/app11010055. [DOI] [Google Scholar]

- 47.Sackinger E., Guggenbuhl W. A versatile building block: The CMOS Differential Difference Amplifier. IEEE J. Solid State Circuits. 1987;22:287–294. doi: 10.1109/JSSC.1987.1052715. [DOI] [Google Scholar]

- 48.Kumngern M. CMOS differential difference voltage follower transconductance amplifier; Proceedings of the 2015 IEEE International Circuits and Systems Symposium (ICSyS); Langkawi, Malaysia. 2–4 September 2015; pp. 133–136. [DOI] [Google Scholar]

- 49.Yesil A., Konal M., Kacar F. Electronically tunable quadrature oscillator employing single differential difference transconductance amplifier. Acta Phys. Pol. A. 2017;132:843. doi: 10.12693/APhysPolA.132.843. [DOI] [Google Scholar]

- 50.Denisenko D.Y., Bugakova A.V., Prokopenko N.N., Ivanov Y.I. The third order active low-pass rc-filters based on differential and differential difference operational amplifiers; Proceedings of the 2019 20th International Conference of Young Specialists on Micro/Nanotechnologies and Electron Devices (EDM); Erlagol, Russia. 29 June–3 July 2019; pp. 695–699. [Google Scholar]

- 51.Rana P., Ranjan A. Odd-and even-order electronically controlled wave active filter employing differential difference trans-conductance amplifier (DDTA) Int. J. Electron. 2020;108:1623–1651. doi: 10.1080/00207217.2020.1870737. [DOI] [Google Scholar]

- 52.Kumngern M. DDTA and DDCCTA: New Active Elements for Analog Signal Processing; Proceedings of the 2012 IEEE International Conference on Electronics Design, Systems and Applications (ICEDSA); Kuala Lumpur, Malaysia. 5–6 November 2012; pp. 141–145. [Google Scholar]

- 53.Kumngern M., Khateb F., Kulej T., Psychalinos C. Multiple-input universal filter and quadrature oscillator using multiple-input operational transconductance amplifiers. IEEE Access. 2021;9:56253–56263. doi: 10.1109/ACCESS.2021.3071829. [DOI] [Google Scholar]

- 54.Prommee P., Karawanich K., Khateb F., Kulej T. Voltage-mode elliptic band-pass filter based on multiple-input transconductor. IEEE Access. 2021;9:32582–32590. doi: 10.1109/ACCESS.2021.3060939. [DOI] [Google Scholar]

- 55.Jaikla W., Khateb F., Kulej T., Pitaksuttayaprot K. Universal filter based on compact cmos structure of VDDDA. Sensors. 2021;21:1683. doi: 10.3390/s21051683. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 56.Jaikla W., Bunrueangsak S., Khateb F., Kulej T., Suwanjan P., Supavarasuwat P. Inductance simulators and their application to the 4th order elliptic lowpass ladder filter using CMOS VD-DIBAs. Electronics. 2021;10:684. doi: 10.3390/electronics10060684. [DOI] [Google Scholar]

- 57.Khateb F., Kulej T., Kumngern M., Psychalinos C. Multiple-input bulk-driven MOS transistor for low-voltage low-frequency applications. Circuits Syst. Signal Process. 2019;38:2829–2845. doi: 10.1007/s00034-018-0999-x. [DOI] [Google Scholar]

- 58.Lopez–Martin A.J., Ramirez–Angulo J., Carvajal R.G., Acosta L. CMOS transconductors with continuous tuning using FGMOS balanced output current scaling. IEEE J. Solid State Circuits. 2008;43:1313–1323. doi: 10.1109/JSSC.2008.920333. [DOI] [Google Scholar]

- 59.Rico-Aniles H.D., Ramirez-Angulo J., Lopez-Martin A.J., Carvajal R.G. 360 nW Gate-Driven Ultra-Low Voltage CMOS Linear Transconductor with 1 MHz Bandwidth and Wide Input Range. IEEE Trans. Circuits Syst. Part II Express Briefs. 2020;67:2332–2336. doi: 10.1109/TCSII.2020.2968246. [DOI] [Google Scholar]

- 60.Pandey N., Paul S.K. Differential difference current conveyor transconductance amplifier: A New Analog Building Block for Signal Processing. J. Electr. Comput. Eng. 2011;2011:361384. doi: 10.1155/2011/361384. [DOI] [Google Scholar]

- 61.Khateb F., Kulej T., Kumngern M., Arbet D., Jaikla W. A 0.5-V 95-dB rail-to-rail DDA for biosignal processing. AEU Int. J. Electron. Commun. 2022;145:1–9. doi: 10.1016/j.aeue.2021.154098. [DOI] [Google Scholar]

- 62.Martin A.J.L., Carlosena A., Ramirez-Angulo J. Very low voltage MOS translinear loops based on flipped voltage followers. Analog. Integr Circ Signal Process. 2004;40:71–74. doi: 10.1023/B:ALOG.0000031435.96974.30. [DOI] [Google Scholar]

- 63.Raikos G., Vlassis S., Psychalinos C. 0.5 V bulk-driven analog building blocks. Int. J. Electron. Commun. 2012;66:920–927. doi: 10.1016/j.aeue.2012.03.015. [DOI] [Google Scholar]

- 64.Lopez-Martin A.J., Baswa S., Ramirez-Angulo J., Carvajal R.G. Low-Voltage Super class AB CMOS OTA cells with very high slew rate and power efficiency. IEEE J. Solid State Circuits. 2005;40:1068–1077. doi: 10.1109/JSSC.2005.845977. [DOI] [Google Scholar]

- 65.Tsukutani T., Higashimura M., Takahashi N., Sumi Y., Fukui Y. Versatile voltage-mode active-only biquad with lossless and lossy integrator loop. Int. J. Electron. 2001;88:1093–1102. doi: 10.1080/00207210110071279. [DOI] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.