Abstract

A new cell topology named the dodecagonal (a polygon with twelve sides, short for Dod) cell is proposed to optimize the gate-to-drain capacitance () and reduce the specific ON-resistance () of 4H-SiC planar power MOSFETs. The Dod and the octagonal (Oct) cells are used in the layout design of the 650 V SiC MOSFETs in this work. The experimental results confirm that the Dod-cell MOSFET achieves a 2.2× lower , 2.1× smaller high-frequency figure of merit (HF-FOM), higher turn on/off dv/dt, and 29% less switching loss than the fabricated Oct-cell MOSFET. The results demonstrate that the Dod cell is an attractive candidate for high-frequency power applications.

Keywords: SiC power MOSFET; cell topology; dodecagonal cell; octagonal cell; gate-to-drain capacitance (Cgd); specific ON-resistance (Ron,sp); high-frequency figure of merit (HF-FOM); switching performance

1. Introduction

The silicon carbide (SiC) power MOSFET has been expected to be the alternative to silicon power devices in multiple applications, such as renewable energy, drivers for electrical machines, and power converters for hybrid and electric vehicles, due to its various advantages, including a low power loss, high switching frequency, and high operating temperature [1,2,3]. Improving energy efficiency (reducing power dissipation) is the driving force for the commercialization of SiC power MOSFETs [3]. The total power loss of a SiC power MOSFET consists of an on-state conduction loss and switching loss. The conduction loss can be reduced by reducing the ON-resistance (). The switching loss of a SiC power MOSFET can be reduced by decreasing device capacitances [4,5]. Studies show that the layout topology design affects the on-state and dynamic performances of SiC power devices [6,7]. Different cell topologies (Linear, Hexagonal, Square, and Octagonal) were used on 600 V SiC planar MOSFETs [7]. All the figure of merits (FOMs) for the Octagonal cell topology are comparable to those of the state-of-the-art Si COOLMOS and are much better than the ROHM SiC MOSFET product [7]. In addition, simulations show that the oxide electric field for an Octagonal cell is much lower in comparison to other topologies [7]. The Linear, Hexagonal, and Octagonal cell topologies were used on 650 V SiC planar JBSFETs and reported in [8]. It is demonstrated that the Hexagonal cell topology provides the lowest specific ON-resistance () but a higher gate–drain charge than Linear and Octagonal cells [8]. It indicates that the Hexagonal cell is suitable for power-switching applications at a nominal frequency. However, for applications where a faster switching frequency is desired, such as reducing the size of power converters, the layout, such as the Octagonal (Oct) cell, is preferred, which tends to reduce the at the cost of a higher [9].

In this work, a new cell topology named the dodecagonal (Dod) cell is proposed and compared with the Oct cell. Additionally, 650 V SiC power MOSFETs with the Dod and Oct cells have been designed, fabricated, and characterized. The static and dynamic performances of the fabricated 650 V SiC power MOSFETs are compared.

2. Device Design and Fabrication

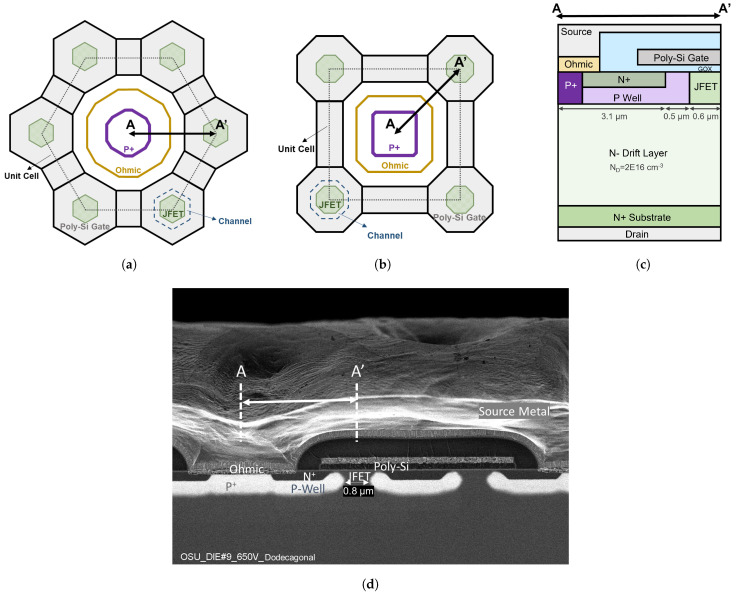

Figure 1a shows the structure of the proposed Dod cell. A twelve-sided region with the ohmic contact on top is surrounded by six hexagonal poly-Si gate regions. The hexagonal gate regions are connected by poly-Si bars. The hexagonal JFET regions are placed inside gate regions. This Dod cell is applied to 650 V SiC power MOSFETs. The Oct cell is shown in Figure 1b. The cross-sectional views along the AA’ direction for both Dod-cell and Oct-cell MOSFETs in this work are shown in Figure 1c. All MOSFETs have the same edge termination design and die size. The die size is 1.15 × 1.15 , including the termination. The MOSFETs are fabricated on a 6-inch SiC wafer by X-Fab using the same SiC power MOSFET process. Figure 1d shows the cross-sectional SEM image of the fabricated Dod-cell MOSFETs. Due to the lateral straggle of Aluminum implantation in the P-well, the narrowest portion of the JFET region is reduced by on each side. Five Dod-cell and five Oct-cell MOSFETs are packaged into open-cavity TO-247 packages for device characterization. Design parameters and experimental results are listed in Table 1.

Figure 1.

(a) Dodecagonal cell topology, (b) Octagonal cell topology, (c) A-A’ cross-sectional view of the 650 V SiC power MOSFET. (d) Cross-sectional SEM image of the fabricated 650 V SiC power MOSFET with the Dod cell.

Table 1.

Design parameters and experimental results.

| Cell Topology | Oct | Dod | |

|---|---|---|---|

| Design parameters |

Cell pitch (m) | 8.4 | 8.4 |

| Active area (mm) | 0.643 | 0.634 | |

| Channel density (m) | 0.113 | 0.181 | |

| JFET density | 0.034 | 0.055 | |

| Experimental results |

(V) | 4.09 ± 0.09 * | 4.35 ± 0.10 |

| BV (V) @ = 100 A | 756.3 ± 22.6 | 753.4 ± 23.6 | |

| (mcm) @ = 1.5 V | 24.4 ± 7.52 | 10.9 ± 3.06 | |

| (pF) @ = 400 V | 1.59 ± 0.01 | 1.63 ± 0.04 | |

| HF-FOM (mpF) () | 6031 ± 1896 | 2817 ± 749 | |

| dv/dt turn-on () | 6.1 | 12.5 | |

| Switching loss turn-on (J) | 29.4 | 20.1 | |

| dv/dt turn-off () | 8.4 | 10.7 | |

| Switching loss turn-off (J) | 5.7 | 4.7 | |

| Total switching loss (J) | 35.1 | 24.8 | |

* ± refers to the standard deviation of the value.

3. Experimental Results and Discussion

3.1. Statistic Performance

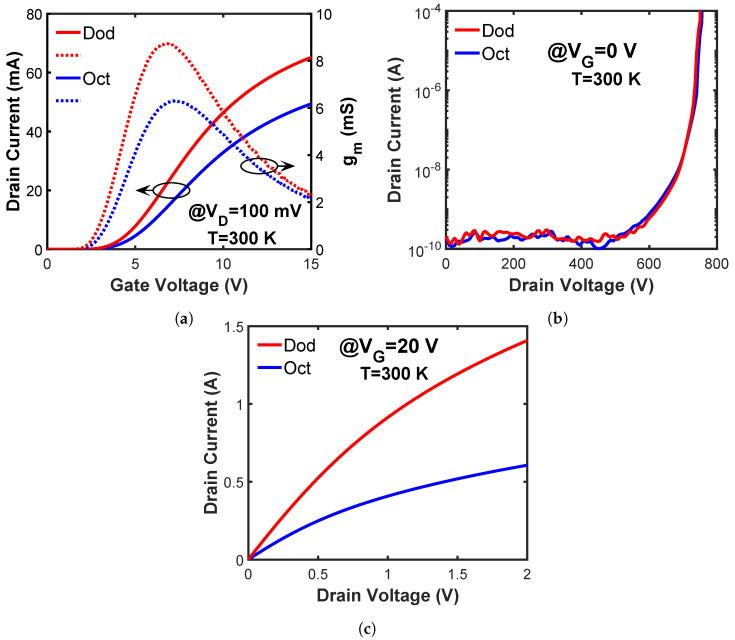

The static performance, including the transfer, blocking, and output characteristics, is measured using a Keysight 1506A power semiconductor analyzer at room temperature. The results of one MOSFET from each cell type are shown in Figure 2. The threshold voltages () of all packaged MOSFETs are extracted using the linear extrapolation method from the transfer curves, as shown in Figure 2a. The average value and the standard derivation are shown in Table 1. A minimal difference (< V) is observed between the MOSFETs with Dod and Oct cells. The transconductances () are also plotted in Figure 2a. The peak value for the Dod-cell MOSFET is 1.5× higher than the fabricated Oct-cell MOSFET, indicating a higher current-driving capability. The blocking characteristics (Figure 2b) show less than 1 nA leakage current up to 600 V for both the Dod-cell and Oct-cell MOSFETs. The breakdown voltage () is defined at the drain current of 100 . Similar average BVs and BV standard derivations are obtained for the Oct-cell and Dod-cell MOSFETs, as shown in Table 1. Therefore, the Dod cell does not degrade the blocking capability of the fabricated power MOSFET.

Figure 2.

(a) Transfer characteristics at = 100 mV (solid line: drain current vs. gate voltage; dash line: transconductance vs. gate voltage), (b) blocking characteristics at = 0 V, and (c) output characteristics at = 20 V, for the 650 V SiC power MOSFETs with Dod and Oct cells.

The output characteristics are shown in Figure 2c. A 2× higher drain current is observed on the fabricated Dod-cell MOSFET than on the Oct-cell MOSFET, which can be explained by the higher channel density and JFET density of the Dod cell. A higher channel density (total channel width in a unit cell/unit cell area) implies a larger total channel width and more current conduction within a specific die size. The channel densities for the Dod and Oct cells are calculated according to the geometry with the known cross section and cell pitch. The results are listed in Table 1. A 1.6× higher channel density is obtained for the Dod cell than the Oct cell. The higher channel density allows more current conduction for the fabricated Dod-cell MOSFET, resulting in a lower than the fabricated Oct-cell MOSFET. The higher JFET density (JFET area/unit cell area) indicates a lower JFET region resistance, which contributes to the lower [10]. The of all the measured MOSFETs is calculated at a drain–source voltage () of . The mean values and standard derivations are listed in Table 1. A 2.2× reduction in the is achieved for the Dod-cell MOSFET compared to the fabricated Oct-cell MOSFET.

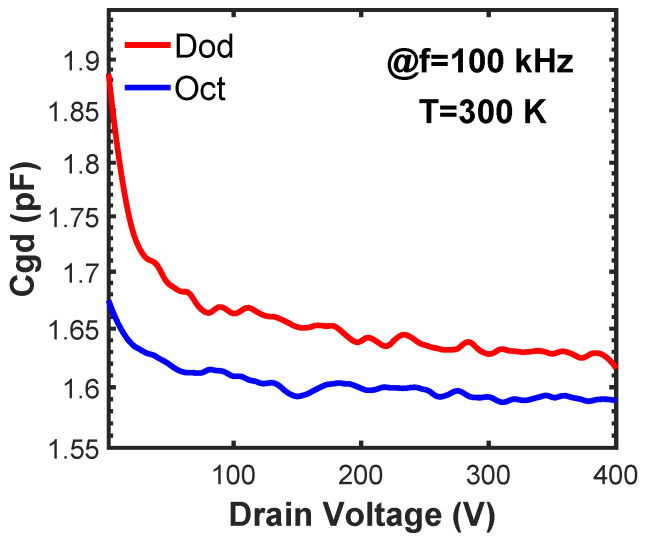

3.2. Dynamic Performance

The vs. drain voltage characteristics are shown in Figure 3. The significantly affects the dynamic behavior of SiC MOSFETs due to the well-known Miller effect [11,12]. The of a SiC planar MOSFET consists of the gate oxide capacitance on the top of the JFET region and the depletion capacitance of the JFET region and drift layer [13]. The results in Figure 3 show that the Dod-cell MOSFET has a higher than the fabricated Oct-cell MOSFET under any drain bias. Because the Dod-cell and Oct-cell MOSFETs are fabricated following the same process flow, their gate oxide thickness, JFET doping profile, and drift-layer doping profile are the same. Thus, the difference in the is caused by the different overlap areas of the gate and drain terminals (JFET region area) within a die. The calculated JFET density of the Dod cell is 1.6× higher than the Oct cell, which causes a higher of the Dod-cell MOSFET. The values at = 400 V are extracted for all the measured MOSFETs. Additionally, the HF-FOMs, which are defined as the product of and , are calculated. The HF-FOM of the Dod-cell MOSFET is 2.1× smaller than the fabricated Oct-cell MOSFET, indicating a better high-frequency performance.

Figure 3.

The of 650 V SiC MOSFETs with the Dod and the Oct cells.

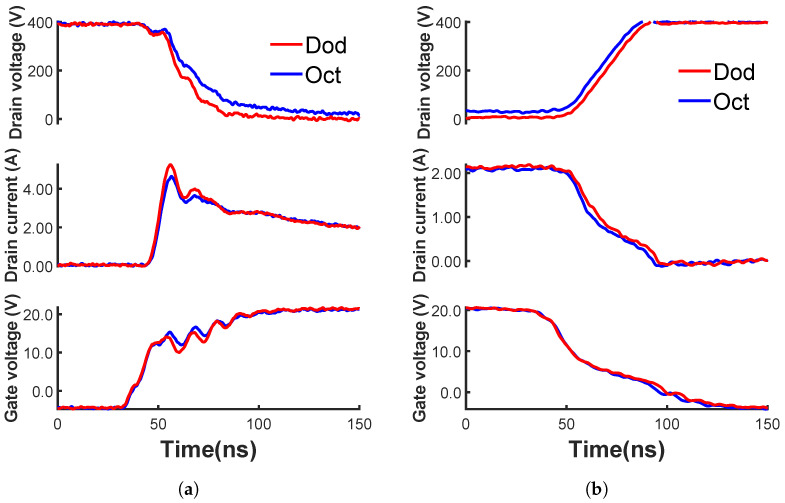

A Double-Pulse Test (DPT), which provides straightforward data on the switching behavior of SiC MOSFETs [14], is conducted to investigate the switching performance of the fabricated MOSFETs. The results are shown in Figure 4. During the turn-on process (Figure 4a), the Dod-cell MOSFET shows a shorter transient time (higher turn-on speed) than the fabricated Oct-cell MOSFET. The turn-on and turn-off dv/dt, switching energy, and total switching energy of the measured MOSFETs are extracted and listed in Table 1. The Dod-cell MOSFET has a higher dv/dt and less switching energy than the measured Oct-cell MOSFET during both the turn-on and turn-off processes. The Dod-cell MOSFET obtains a 29% reduction in total switching loss compared to the measured Oct-cell MOSFET.

Figure 4.

(a) Turn-on and (b) turn-off waveforms of the fabricated 650 V SiC power MOSFETs with the Dod and the Oct cells.

4. Conclusions

A new cell topology named the Dod cell is proposed for SiC planar power MOSFETs. The Dod cell minimizes the JFET region area to achieve a low and improves the channel density to reduce the . A low indicates a higher switching speed and makes the Dod-cell MOSFET an attractive candidate for high-frequency applications. The reduced decreases the conduction loss. The Dod cell and a recently published Oct cell (designed with minimal JFET region area) have been used for the layout design of 650 V SiC power MOSFETs. The fabricated Dod-cell MOSFET achieves a higher , but a 2.2× lower , 2.1× smaller HF-FOM, and 29% less switching losses compared with the fabricated Oct-cell MOSFET.

Acknowledgments

The authors would like to thank the Power Electronics Teams at Ford Motor Company’s Research and Innovation Centers for helpful discussions.

Abbreviations

The following abbreviations are used in this manuscript:

| SiC | Silicon Carbide |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor |

| JFET | Junction Field-Effect Transistor |

| JBSFET | Junction Barrier Schottky (JBS) diode-integrated MOSFET |

| HF-FOM | High-Frequency Figure of Merit |

| DPT | Double-Pulse Test |

Author Contributions

Conceptualization, S.Z., T.L., and A.K.A.; methodology, S.Z., T.L., and A.K.A.; investigation, S.Z. and J.F.; resources, A.S. and D.S.; data curation, S.Z.; writing—original draft preparation, S.Z.; writing—review and editing, T.L., M.H.W., and A.K.A. All authors have read and agreed to the published version of the manuscript.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

Funding Statement

This research is supported by the Block Gift Grant from the II-VI Foundation.

Footnotes

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

References

- 1.Camacho A.P., Sala V., Ghorbani H., Martinez J.L.R. A novel active gate driver for improving SiC MOSFET switching trajectory. IEEE Trans. Ind. Electron. 2017;64:9032–9042. doi: 10.1109/TIE.2017.2719603. [DOI] [Google Scholar]

- 2.Hazra S., De A., Cheng L., Palmour J., Schupbach M., Hull B.A., Allen S., Bhattacharya S. High switching performance of 1700-V, 50-A SiC power MOSFET over Si IGBT/BiMOSFET for advanced power conversion applications. IEEE Trans. Power Electron. 2015;31:4742–4754. [Google Scholar]

- 3.Kimoto T. Material science and device physics in SiC technology for high-voltage power devices. Jpn. J. Appl. Phys. 2015;54:040103. doi: 10.7567/JJAP.54.040103. [DOI] [Google Scholar]

- 4.Baliga B.J. Power semiconductor device figure of merit for high-frequency applications. IEEE Electron Device Lett. 1989;10:455–457. doi: 10.1109/55.43098. [DOI] [Google Scholar]

- 5.Wang H., Wang F., Zhang J. Power semiconductor device figure of merit for high-power-density converter design applications. IEEE Trans. Electron Devices. 2007;55:466–470. doi: 10.1109/TED.2007.910573. [DOI] [Google Scholar]

- 6.Watanabe N., Okino H., Shima A. Impact of Cell Layout on On-state and Dynamic Characteristics of N-channel SiC IGBTs; Proceedings of the 2022 IEEE 34th International Symposium on Power Semiconductor Devices and ICs (ISPSD); Vancouver, BC, Canada. 22–25 May 2022; pp. 85–88. [Google Scholar]

- 7.Agarwal A., Han K., Baliga B.J. Impact of cell topology on characteristics of 600V 4H-SiC planar MOSFETs. IEEE Electron Device Lett. 2019;40:773–776. doi: 10.1109/LED.2019.2908078. [DOI] [Google Scholar]

- 8.Agarwal A., Han K., Baliga B. Assessment of linear, hexagonal, and octagonal cell topologies for 650 V 4H-SiC inversion-channel planar-gate power JBSFETs fabricated with 27 nm gate oxide thickness. IEEE J. Electron Devices Soc. 2020;9:79–88. doi: 10.1109/JEDS.2020.3040353. [DOI] [Google Scholar]

- 9.Han K., Baliga B. The 1.2-kV 4H-SiC OCTFET: A new cell topology with improved high-frequency figures-of-merit. IEEE Electron Device Lett. 2018;40:299–302. doi: 10.1109/LED.2018.2889221. [DOI] [Google Scholar]

- 10.Liu T., Zhu S., Salemi A., Sheridan D., White M.H., Agarwal A.K. JFET Region Design Trade-Offs of 650 V 4H-SiC Planar Power MOSFETs. Solid State Electron. Lett. 2021;3:53–58. doi: 10.1016/j.ssel.2021.12.001. [DOI] [Google Scholar]

- 11.Mukunoki Y., Nakamura Y., Konno K., Horiguchi T., Nakayama Y., Nishizawa A., Kuzumoto M., Akagi H. Modeling of a silicon-carbide MOSFET with focus on internal stray capacitances and inductances, and its verification. IEEE Trans. Ind. Appl. 2018;54:2588–2597. doi: 10.1109/TIA.2018.2796587. [DOI] [Google Scholar]

- 12.Ebihara Y., Ichimura A., Mitani S., Noborio M., Takeuchi Y., Mizuno S., Yamamoto T., Tsuruta K. Deep-P encapsulated 4H-SiC trench MOSFETs with ultra low R on Q gd; Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD); Chicago, IL, USA. 13–17 May 2018; pp. 44–47. [Google Scholar]

- 13.Zhu S., Liu T., Fan J., Maddi H.L.R., White M.H., Agarwal A.K. Effects of JFET Region Design and Gate Oxide Thickness on the Static and Dynamic Performance of 650 V SiC Planar Power MOSFETs. Materials. 2022;15:5995. doi: 10.3390/ma15175995. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 14.Li X., Jiang J., Huang A.Q., Guo S., Deng X., Zhang B., She X. A SiC power MOSFET loss model suitable for high-frequency applications. IEEE Trans. Ind. Electron. 2017;64:8268–8276. doi: 10.1109/TIE.2017.2703910. [DOI] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Data Availability Statement

Not applicable.