Abstract

Silicon Carbide (SiC) is an outstanding material, not only for electronic applications, but also for projected functionalities in the realm of spin-based quantum technologies, nano-mechanical resonators and photonics-on-a-chip. For shaping 3D structures out of SiC wafers, predominantly dry-etching techniques are used. SiC is nearly inert with respect to wet etching, occasionally photoelectrochemical etching strategies have been applied. Here, we propose an electrochemical etching strategy that solely relies on defining etchable volumina by implantation of p-dopants. Together with the inertness of the n-doped regions, very sharp etching contrasts can be achieved. We present devices as different as monolithic cantilevers, disk-shaped optical resonators and membranes etched out of a single crystal wafer. The high quality of the resulting surfaces can even be enhanced by thermal treatment, with shape-stable devices up to and even beyond 1550°C. The versatility of our approach paves the way for new functionalities on SiC as high-performance multi-functional wafer platform.

Subject terms: Materials for devices, Electrical and electronic engineering

Introduction

Silicon Carbide (SiC), especially its polytype 4H-SiC, is an extraordinary material for integrating electronics1, photonics2, high-quality mechanics3 and quantum technologies on the very same chip4,5. Due to its technological breakthrough in power electronics, it is available as single crystalline high-quality wafers. When, further, optical and mechanical functionality is demanded, there is a need for highest-quality devices with three-dimensional geometries. As to optics, SiC provides the unusual opportunity of simultaneous χ(2) and χ(3) nonlinearities6,7. The current state-of-the-art photonics-on-a-chip is not integrated with traditional SiC fabrication techniques, but uses thin SiC-on-insulator technology4,8,9. As to mechanics-on-a-chip, SiC provides an outstanding intrinsic property: it has the lowest internal damping of all known materials3,9,10. Also here, device fabrication utilizes thin SiC layers on a sacrificial substrate. Given the extraordinary set of parameters of SiC, it is desirable to identify monolithic technologies for the preparation of optical and mechanical devices along with the electronic functionality. Compatibility with high-temperature protocols, for example epitaxial graphene growth11 or defect annealing12, would be beneficial.

For such applications, however, a technological prerequisite is an etching strategy that forms the desired 3D-structures monolithically out of the single-crystal wafer, while maintaining high-quality surfaces and low defect budgets. The commonly used gas etching strategies (ICP-RIE/RIE) are projective, and even ‘anisotropic’ gas etching has limited aspect ratios13–15. Further, they are prone to create surface-near point-defects. Therefore, a new process strategy is required. In an effort to increase the design space for advanced 3D geometries like cantilevers, disk-shaped resonators or membranes (cf. Fig. 1), including long-range lateral etching, we present a route based on implantation and subsequent electrochemical etching (ECE).

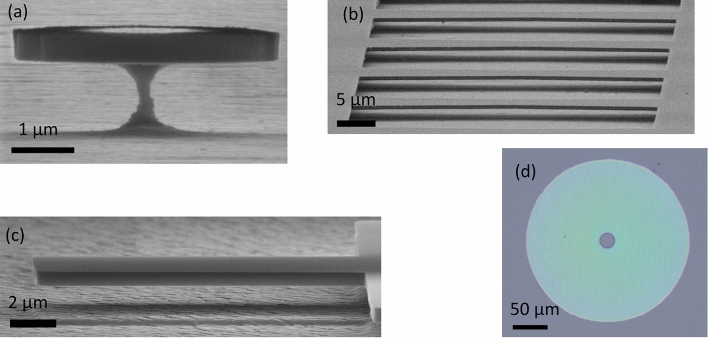

Figure 1.

Monolithically etched 3D-devices from single-crystal 4H-SiC wafer. (a) disk-shape optical resonator, (b) doubly clamped mechanical resonator, (c) single clamped mechanical resonator, (d) free-standing circular membrane (central hole is required as etching access). (a–c) SEM micrographs, (d) optical micrograph.

SiC is nearly inert and only few chemical reagents to resolve it under moderate conditions are known. Typically, both high temperatures and strong etchants are needed16. Here we choose positive charge carriers (holes, at the surface for the electrochemical attack. We opt for etching under alkaline conditions, the electrochemistry of which has extensively been studied by van Dorp17–19. In order to provide the required on the surface, a vast majority of publications uses electron–hole creation by ultraviolet light including our own previous work5,20–22. This methodology is limited because of optical constraints, in particular it has poor vertical control22. Here we favor an electrochemical strategy where -concentrations are created by appropriate doping patterns. Additional control can be gained by electric potentials. In a late stage of our investigations, we found that the etching strategy is similar to23.

Etching of SiC involves a two-step process. First, oxidation of SiC follows two possible reaction pathways for the oxidation24:

| 1 |

| 2 |

According to current knowledge, both oxidation pathways take place simultaneously, while the applied voltage determines the ratio of both25. Experimentally it is indeed reported that the dissolution valence, i.e. the number of charge carriers required to etch one formula unit of SiC is between 6 and 6.918,24. In a second step, the resulting reaction products are removed by the electrolyte, that is potassium hydroxide (KOH). The dissolution of involves the adsorption of water with the formation of hydrated silica () and an attack by hydroxyl ions to form a soluble silicate ()26,27.

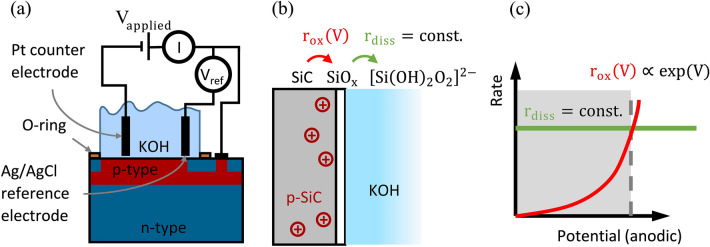

In steady state, the oxidation of SiC and the subsequent dissolution of occur with the same rate, which is our desired regime of operation, see Fig. 2. Otherwise, an overshooting of the -formation would passivate the surface and block the electrochemical process. This would result in an oscillatory behavior at higher rates, which we avoided by sticking to low reaction rates28,29.

Figure 2.

Electrochemical oxidation reactions. (a) Electrochemical etching setup. The current (I) flows via the p-SiC layer to the counter electrode. (b) Dissolution of , forming and as intermediates, subsequently forming soluble silicates. (c) Oxidation () and dissolution () rates as a function of applied voltage. The grey area indicates the voltage range suitable for steady-state etching.

This electrochemical reaction gives a handle to remove specific volumina selectively. p-doped, i.e. -rich regions can efficiently be etched as opposed to n-doped regions where, due to the lack of , etching is completely suppressed.

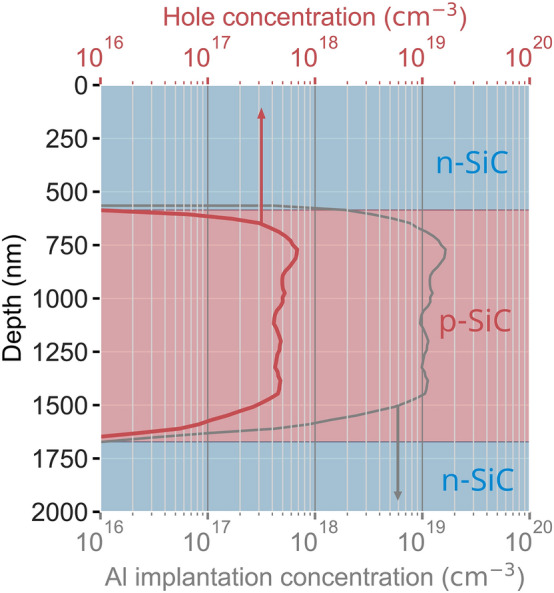

We start with a 4°-off-axis n-type wafer with an epilayer (nitrogen-doped 1016 cm−3). The required doping profiles can be defined by ion implantation, which is described in detail in the SI, detailed data can be found in30. The hole concentration profile is shown in Fig. 3, where Aluminum-implantation creates a box-like p-type profile in a depth from 550 nm to 1.6 µm. At its flank, the hole concentration drops by more than ten orders of magnitude within 50 nm, which gives hope that the etch-stop is defined within atomic precision. In order to ensure reliable n-doping of the top layer, a counter implantation with Nitrogen is performed. Subsequent annealing to 1700°C for 30 min in 900 mbar Argon-atmosphere re-establishes the crystalline lattice (locally, a carbon cap stabilizes the surface31). Note that dopant diffusion is essentially absent in the rigid SiC-lattice.

Figure 3.

Dopant-defined layers for electrochemical etching. By suitable implantation profiles for Aluminum and Nitrogen, a sharply defined p-SiC layer with an excess of positive charge carriers (holes) is defined. The hole concentration is calculated, utilizing the charge neutrality equation, assuming a compensation ratio of 0.3532, and a doping concentration dependant ionization energy ()33,34.

For the geometries in this manuscript, we used only vertical implantation profiles. The methodology can be readily extended to more complex 3D structures, when in addition, lateral patterning of the implantation is achieved, for example with robust metallic masks.

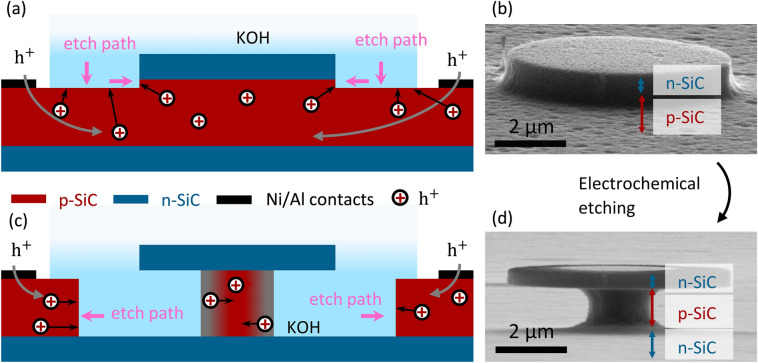

But also with laterally homogeneous doping profiles, 3D structures can be defined. For this purpose, we pattern resist masks which define a top window (electron beam lithography or similar). A projective etching of the n-type layer is performed by standard RIE / ICP-RIE techniques, such that the p-SiC layer is slightly etched. Now, the ECE is performed, which isotropically removes the p-SiC layer, see Fig. 4. A typical lateral etch velocity is 2 µm/h. Care has to be taken that during this process an uninterrupted current path through the p-type layer has to be maintained. If however, p-type areas are disconnected from the current pathway during the etching, the dissolution stops for this island. While this may occur unintendedly, this property can also be exploited for the positive (see e.g. self-limited support columns for disk-shape optical resonators in Fig. 4). In any case, maintaining intact current pathways throughout the etching process has the rank of a design principle.

Figure 4.

Electrochemical etching using dopant-defined layers. (a,b) Before ECE, areas to be removed are defined by lithography and gas etching slightly into the p-layer. Positive charge carriers (h+), required for ECE, are supplied via Ni/Al ohmic contacts. Applying anodic voltages results in (energy) band bending of the semiconductor, holes accumulate at the p-SiC/KOH interface and promote etching. (c, d) ECE removes the p-SiC layer. The etching is stopped vertically by the n-SiC layer; the lateral etching is stopped as soon as the remaining p-island is electrically unconnected. Without any applied potential, the p-SiC/KOH interface depletes of holes (due to band bending, grey area). (b,d) SEM micrographs, scale-bar: 2 µm.

Figure 1 displays a cantilever-like structure after ECE. We report one complication that arises after the ECE. Underneath the top n-type layer, in barely accessible regions, often an undesired porous p-type structure remains (goat beard), see SI. It reminds the formation of porous SiC in KOH35. It can reliably be removed by two simple techniques: either a subsequent isotropic dry etch with CF4 at 190 mTorr that is suited for well-accessible devices like cantilevers, see SI. Alternatively, high temperature annealing beyond 1000°C in 900 mbar Argon atmosphere removes this layer even in hardly accessible regions. It can be suspected that thermal oxidation has a similar effect36,37.

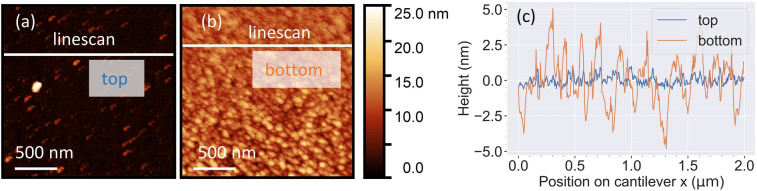

An obvious quality criterion for optical or mechanical devices is the surface roughness. In our devices, the ECE process leaves the etched surface quite smooth. The top surface of the n-SiC layer is essentially unchanged (in our experiments, rmstop = 1.46 nm, see Fig. 5a). For characterizing the bottom layer, we removed a single clamped cantilever with scotch tape and studied its surface with the AFM. The result is shown in Fig. 5b, it yields rmsbottom = 2.48 nm. Hence, both the unetched top and the freshly etched bottom surfaces have both low surface roughness.

Figure 5.

Surface characterization after ECE. AFM measurements on a cantilever (top and bottom surfaces). Statistical evaluation yields roughnesses of rmstop = 1.46 nm and rmsbottom = 2.48 nm. The scale-bar refers to 500 nm. (b) Height profiles referring to the lines indicated in (a).

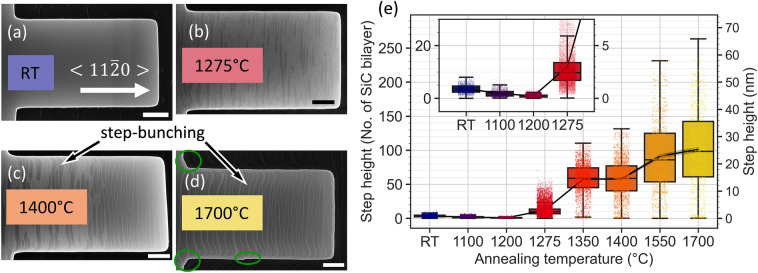

Finally, we address the question, how the presented 3D fabrication technique is compliant with further processing. Underetched devices were spin-coated with PMMA and nLof resist materials without being damaged. They also survived lift-off processes, rinsing and drying without special precautions. Remarkably, the devices are also robust with respect to high-temperature steps. In SiC, relevant spin-carrying color centers are created, converted and finally annealed out in a temperature range from 400°C to 1400°C12. The native oxide layer sublimes at temperatures above 800°C in UHV38. Epitaxial graphene fabrication in n-type 4H-SiC is performed at above 1500°C39. Unintentional implantation damage anneals out at 1600°C to 1700°C. Hence, we explored this entire temperature range with completely processed devices like cantilever structures or membranes. They were exposed to high temperature steps in Ar atmosphere (900 mbar) for 30 min and subsequently investigated with SEM (see Fig. 6a–d) and AFM (Fig. 6e). The shape of the cantilevers is maintained at least up to 1550°C. Beyond this temperature, as can be seen in Fig. 6d a visible re-arrangement occurs. It is most obvious at the lower edge, where a discontinuity has been created. Also in the lower and upper left corners, an additional faceted transition is formed, following crystalline directions. Remarkably, below 1550°C, our cantilevers provide an excellent shape stability. An analysis of the upper surface profile shows very little effect up to 1200°C. In the temperature range of 1275°C to 1350°C, pronounced terraces are formed and step bunching occurs (4° miscut) with typical step heights of the order of 10 nm, beyond 1550°C approaching towards 25 nm.

Figure 6.

Cantilever shape evolution during high-temperature annealing. (a–d) SEM micrographs of the very same cantilever after step-wise annealing at selected temperatures. Faceted reconfigurations are highlighted in green. Scale-bar: 2 µm. (e) AFM line-scans were performed in the < 110 > direction. The plot shows the analysis of the step height of this annealed cantilever as a function of annealing temperature. The SiC step height significantly increases for annealing temperatures above 1275°C. The step height is additionally given in units of SiC bilayer, 0.25 nm. The insert is a zoom emphasizing the low-temperature range.

From the contrast in the SEM micrographs, the characteristic pattern of the initiation of graphene growth becomes apparent, which forms a homogenous coverage when annealing the sample at 1700°C11. This is more than an interesting detail: epitaxial graphene provides an atomically smooth surface termination that is inert as long as oxygen plasma is avoided.

In conclusion, we present a versatile electrochemical fabrication route for generating high-quality monolithic 3D devices in SiC. The shape of the 3D structure is defined by doping profiles. The surface quality can be enhanced by high temperature annealing. While in this study, we limited ourselves to homogenous p-type layers and homogeneous n-type top layers, much more refined 3D shaping is possible. Such 3D devices, monolithically carved out of monocrystalline SiC wafers, pave the way to implement mechanical and optical monolithic devices with excellent surface properties on the SiC platform. Together with the already available electrical semiconductor functionalities, graphene electronics and spin-physics in SiC a rich toolbox can be established, unifying quantum and classical technologies on the very same chip (Supplementary Information).

Supplementary Information

Acknowledgements

Support from Patrik Schmuki and Matthias A. Popp in early stages of this work is acknowledged. Discussions with Sabine Maier about the AFM data evaluation and representation are acknowledged. Support and conduction of ion implantations by Willi Rösch are acknowledged. We further acknowledge financial support by German Research Foundation (DFG, QuCoLiMa, SFB/TRR 306, Project No. 429529648), project B03.

Author contributions

A.H. developed the etching strategy, fabricated samples and conducted the measurements. F.G. conducted the annealing experiments. M.N.M. fabricated the membrane. M.K. contributed his experience in SiC processing. H.B.W. conceived the experiment. The manuscript was written by A.H. and H.B.W. All authors discussed the results and contributed to the final manuscript.

Funding

Open Access funding enabled and organized by Projekt DEAL.

Data availability

The data that support the findings of this study is available in an open-access repository: https://doi.org/10.22000/1722.

Competing interests

The authors declare no competing interests.

Footnotes

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

The online version contains supplementary material available at 10.1038/s41598-023-46110-2.

References

- 1.She X, Huang AQ, Lucia O, Ozpineci B. Review of silicon carbide power devices and their applications. IEEE Trans. Industr. Electron. 2017;64:8193–8205. doi: 10.1109/TIE.2017.2652401. [DOI] [Google Scholar]

- 2.Lukin DM, Dory C, Guidry MA, Yang KY, Mishra SD, Trivedi R, Radulaski M, Sun S, Vercruysse D, Ahn GH, Vučković J. 4H-silicon-carbide-on-insulator for integrated quantum and nonlinear photonics. Nat. Photon. 2020;14(5):330–334. doi: 10.1038/s41566-019-0556-6. [DOI] [Google Scholar]

- 3.Ghaffari S, Chandorkar SA, Wang S, Ng EJ, Ahn CH, Hong V, Yang Y, Kenny TW. Quantum limit of quality factor in silicon micro and nano mechanical resonators. Sci. Rep. 2013;3:1–7. doi: 10.1038/srep03244. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 4.Lukin DM, Guidry MA, Vučković J. Integrated quantum photonics with silicon carbide: Challenges and prospects. PRX Quantum. 2020;1:020102. doi: 10.1103/PRXQuantum.1.020102. [DOI] [Google Scholar]

- 5.Crook AL, Anderson CP, Miao KC, Bourassa A, Lee H, Bayliss SL, Bracher DO, Zhang X, Abe H, Ohshima T, Hu EL. Purcell enhancement of a single silicon carbide color center with coherent spin control. Nano Lett. 2020;20(5):3427–3434. doi: 10.1021/acs.nanolett.0c00339. [DOI] [PubMed] [Google Scholar]

- 6.Sato H, Abe M, Shoji I, Suda J, Kondo T. Accurate measurements of second-order nonlinear optical coefficients of 6H and 4H silicon carbide. JOSA B. 2009;26:1892–1896. doi: 10.1364/JOSAB.26.001892. [DOI] [Google Scholar]

- 7.De Leonardis F, Soref RA, Passaro V. Dispersion of nonresonant third-order nonlinearities in Silicon Carbide. Sci. Rep. 2017;7:1–12. doi: 10.1038/srep40924. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 8.Lukin, D. M., et al. Two-emitter multimode cavity quantum electrodynamics in thin-film silicon carbide photonics. Physical Review X13(1), 011005 (2023).

- 9.Hamelin B, Yang J, Daruwalla A, Wen H, Ayazi F. Monocrystalline silicon carbide disk resonators on phononic crystals with ultra-low dissipation bulk acoustic wave modes. Sci. Rep. 2019;9:1–8. doi: 10.1038/s41598-019-54278-9. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 10.Heinrich, S. M. & Dufour, I. Fundamental Theory of Resonant MEMS Devices, in Resonant MEMS, John Wiley & Sons, Ltd, p. 1–28 (2015).

- 11.Emtsev KV, Bostwick A, Horn K, Jobst J, Kellogg GL, Ley L, McChesney JL, Ohta T, Reshanov SA, Röhrl J, Rotenberg E. Towards wafer-size graphene layers by atmospheric pressure graphitization of silicon carbide. Nat. Mater. 2009;8(3):203–207. doi: 10.1038/nmat2382. [DOI] [PubMed] [Google Scholar]

- 12.Rühl M, Ott C, Götzinger S, Krieger M, Weber HB. Controlled generation of intrinsic near-infrared color centers in 4H-SiC via proton irradiation and annealing. Appl. Phys. Lett. 2018;113:122102. doi: 10.1063/1.5045859. [DOI] [Google Scholar]

- 13.Boyd GD, Coldren LA, Storz FG. Directional reactive ion etching at oblique angles. Appl. Phys. Lett. 1980;36:583–585. doi: 10.1063/1.91554. [DOI] [Google Scholar]

- 14.Takahashi S, Suzuki K, Okano M, Imada M, Nakamori T, Ota Y, Ishizaki K, Noda S. Direct creation of three-dimensional photonic crystals by a top-down approach. Nat. Mater. 2009;8:721. doi: 10.1038/nmat2507. [DOI] [PubMed] [Google Scholar]

- 15.Frye, C. D., et al. High temperature isotropic and anisotropic etching of silicon carbide using forming gas. J. Vacuum Sci. Technol. A39 (2021).

- 16.Zhuang D, Edgar JH. Wet etching of GaN, AlN, and SiC: a review. Mater. Sci. Eng. R. Rep. 2005;48:1–46. doi: 10.1016/j.mser.2004.11.002. [DOI] [Google Scholar]

- 17.van Dorp DH, Weyher JL, Kelly JJ. Anodic etching of SiC in alkaline solutions. J. Micromech. Microeng. 2007;17:S50. doi: 10.1088/0960-1317/17/4/S04. [DOI] [Google Scholar]

- 18.Van Dorp DH, Kelly JJ. Photoelectrochemistry of 4H–SiC in KOH solutions. J. Electroanal. Chem. 2007;599:260–266. doi: 10.1016/j.jelechem.2006.03.002. [DOI] [Google Scholar]

- 19.Van Dorp, D. H. Etching of wide-bandgap chemically resistant semiconductors: An electrochemical study, Utrecht University, (2008).

- 20.Rysy S, Sadowski H, Helbig R. Electrochemical etching of silicon carbide. J. Solid State Electrochem. 1999;3:437–445. doi: 10.1007/s100080050179. [DOI] [Google Scholar]

- 21.Shor JS, Kurtz AD, Grimberg I, Weiss BZ, Osgood RM. Dopant-selective etch stops in 6H and 3C SiC. J. Appl. Phys. 1997;81:1546–1551. doi: 10.1063/1.363890. [DOI] [Google Scholar]

- 22.Zhao F, Islam MM, Huang C-F. Photoelectrochemical etching to fabricate single-crystal SiC MEMS for harsh environments. Mater. Lett. 2011;65:409–412. doi: 10.1016/j.matlet.2010.10.034. [DOI] [Google Scholar]

- 23.Adachi K, Watanabe N, Okamoto H, Yamaguchi H, Kimoto T, Suda J. Single-crystalline 4H-SiC micro cantilevers with a high quality factor. Sens. Actuators A Phys. 2013;197:122–125. doi: 10.1016/j.sna.2013.04.014. [DOI] [Google Scholar]

- 24.Shor JS, Kurtz AD. Photoelectrochemical etching of 6 H-SiC. J. Electrochem. Soc. 1994;141:778. doi: 10.1149/1.2054810. [DOI] [Google Scholar]

- 25.Leitgeb M, Zellner C, Hufnagl C, Schneider M, Schwab S, Hutter H, Schmid U. Stacked layers of different porosity in 4H SiC substrates applying a photoelectrochemical approach. J. Electrochem. Soc. 2017;164:E337. doi: 10.1149/2.1081712jes. [DOI] [Google Scholar]

- 26.Cook LM. Chemical processes in glass polishing. J. Non-Cryst. Solids. 1990;120:152–171. doi: 10.1016/0022-3093(90)90200-6. [DOI] [Google Scholar]

- 27.Glembocki OJ, Palik ED, De Guel GR, Kendall DL. Hydration model for the molarity dependence of the etch rate of Si in aqueous alkali hydroxides. J. Electrochem. Soc. 1991;138:1055. doi: 10.1149/1.2085715. [DOI] [Google Scholar]

- 28.Leitgeb M, Pfusterschmied G, Schwarz S, Depuydt B, Cho J, Schmid U. Communication—current oscillations in photoelectrochemical etching of monocrystalline 4h silicon carbide. ECS J. Solid State Sci. Technol. 2021;10:073003. doi: 10.1149/2162-8777/ac10b3. [DOI] [Google Scholar]

- 29.Föll H, Leisner M, Cojocaru A, Carstensen J. Self-organization phenomena at semiconductor electrodes. Electrochimica Acta. 2009;55:327–339. doi: 10.1016/j.electacta.2009.03.076. [DOI] [Google Scholar]

- 30.Hochreiter, A. & Weber, H. B., Research data for the manuscript: Electrochemical etching strategy for shaping monolithic 3D structures from 4H-SiC wafers. 10.22000/1722 (2023). [DOI] [PubMed]

- 31.Negoro Y, Katsumoto K, Kimoto T, Matsunami H. Electronic behaviors of high-dose phosphorus-ion implanted 4H–SiC (0001) J. Appl. Phys. 2004;96:224–228. doi: 10.1063/1.1756213. [DOI] [Google Scholar]

- 32.Weiße J, Hauck M, Krieger M, Bauer AJ, Erlbacher T. Aluminum acceptor activation and charge compensation in implanted p-type 4H-SiC. AIP Adv. 2019;9:055308. doi: 10.1063/1.5096440. [DOI] [Google Scholar]

- 33.Weisse J., et al. Analysis of compensation effects in aluminum-implanted 4H-SiC devices. Materials Science Forum (2018).

- 34.Rambach M, Bauer AJ, Ryssel H. Electrical and topographical characterization of aluminum implanted layers in 4H silicon carbide. Phys. Status Solidi b. 2008;245(7):1315–1326. doi: 10.1002/pssb.200743510. [DOI] [Google Scholar]

- 35.Zangooie S, Arwin H. Surface, pore morphology, and optical properties of porous 4H-SiC. J. Electrochem. Soc. 2001;148:G297. doi: 10.1149/1.1368109. [DOI] [Google Scholar]

- 36.Shor JS, Osgood RM, Kurtz AD. Photoelectrochemical conductivity selective etch stops for SiC. Appl. Phys. Lett. 1992;60:1001–1003. doi: 10.1063/1.106502. [DOI] [Google Scholar]

- 37.Shin MW, Song JG. Study on the photoelectrochemical etching process of semiconducting 6H–SiC wafer. Mater. Sci. Eng. B. 2002;95:191–194. doi: 10.1016/S0921-5107(02)00163-0. [DOI] [Google Scholar]

- 38.Powers JM, Somorjai GA. The surface oxidation of alpha-silicon carbide by O2 from 300 to 1373 K. Surf. Sci. 1991;244:39–50. doi: 10.1016/0039-6028(91)90167-Q. [DOI] [Google Scholar]

- 39.Pierucci D, Brumme T, Girard J-C, Calandra M, Silly MG, Sirotti F, Barbier A, Mauri F, Ouerghi A. Atomic and electronic structure of trilayer graphene/SiC (0001): Evidence of strong dependence on stacking sequence and charge transfer. Sci. Rep. 2016;6:33487. doi: 10.1038/srep33487. [DOI] [PMC free article] [PubMed] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Supplementary Materials

Data Availability Statement

The data that support the findings of this study is available in an open-access repository: https://doi.org/10.22000/1722.